MOS transistor array type multi-system and decimal bit weight subtracter

A MOS tube and multi-ary system technology, applied in the computer field, can solve the problems of slow development and achieve the effect of effective hardware support

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

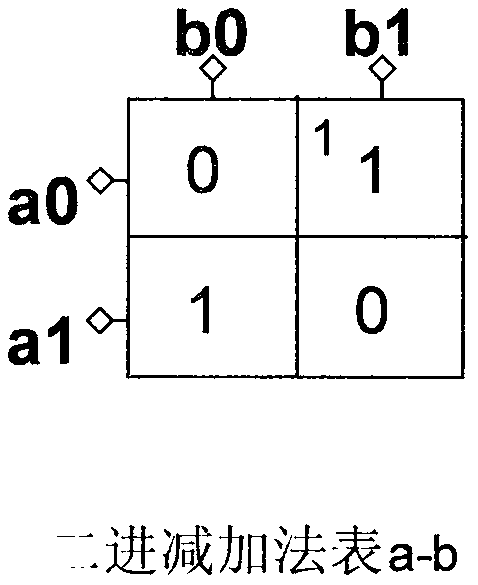

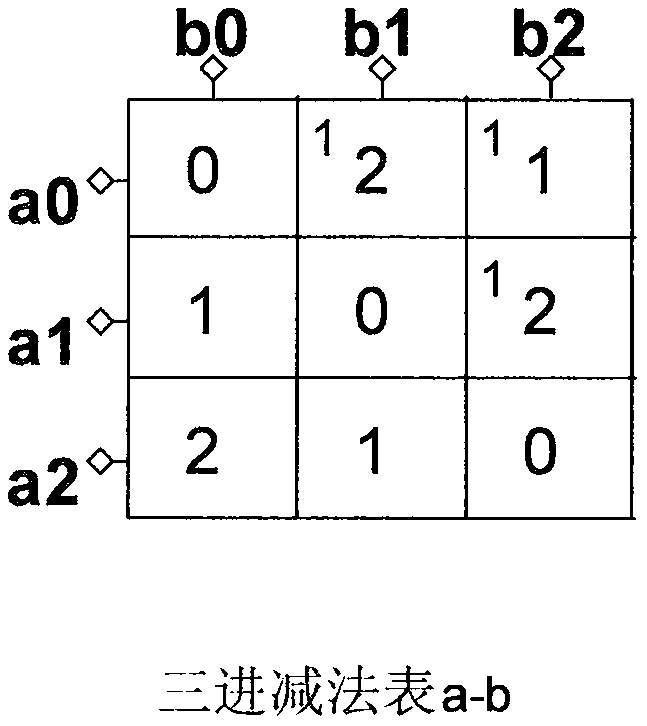

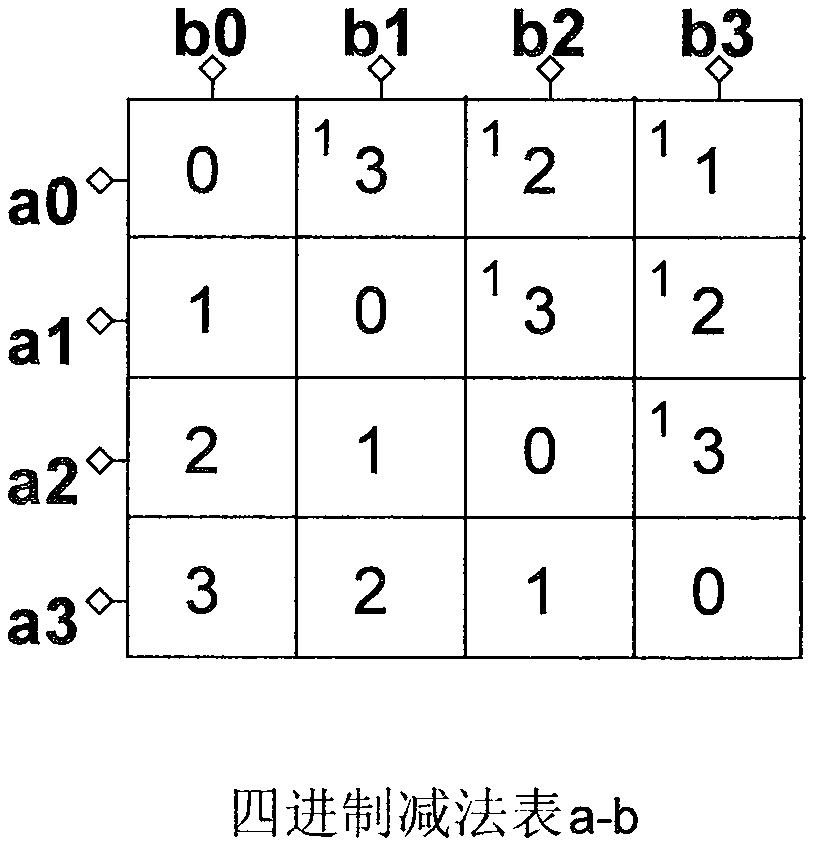

[0076] refer to figure 2 , image 3 , using the circuits of four patent applications 201711119713.x "Quantitative Logic Multi-ary Arithmetic Operator Fuyi Fractal Integrated Unit Circuit" as the basic unit, the MOS tubes of the logic operation part of each unit are arranged in a square array to form the following A 2×2 square matrix based on base 2, the row line of the square matrix is composed of the gates of the MOS transistors on the same row connected to each other, and the column line of the square matrix is composed of the drains of the MOS transistors on the same column. , the 2 row lines of the square matrix are used as the bit weight input terminals of one group of bit weight inputs, and the 2 column lines of the square matrix are used as the bit weight input terminals of another group of input. The output is the source of each MOS transistor, and each source output mark is arranged with the number of the bit weight line to which the gate and drain of the MOS tra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More