Multi-value amplitude weight variable compensation device of quantification logic

A quantizer and amplitude-weighted technology, applied in the computer field, can solve problems such as slow development, and achieve the effect of reliable implementation, rich operation relationship and output.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

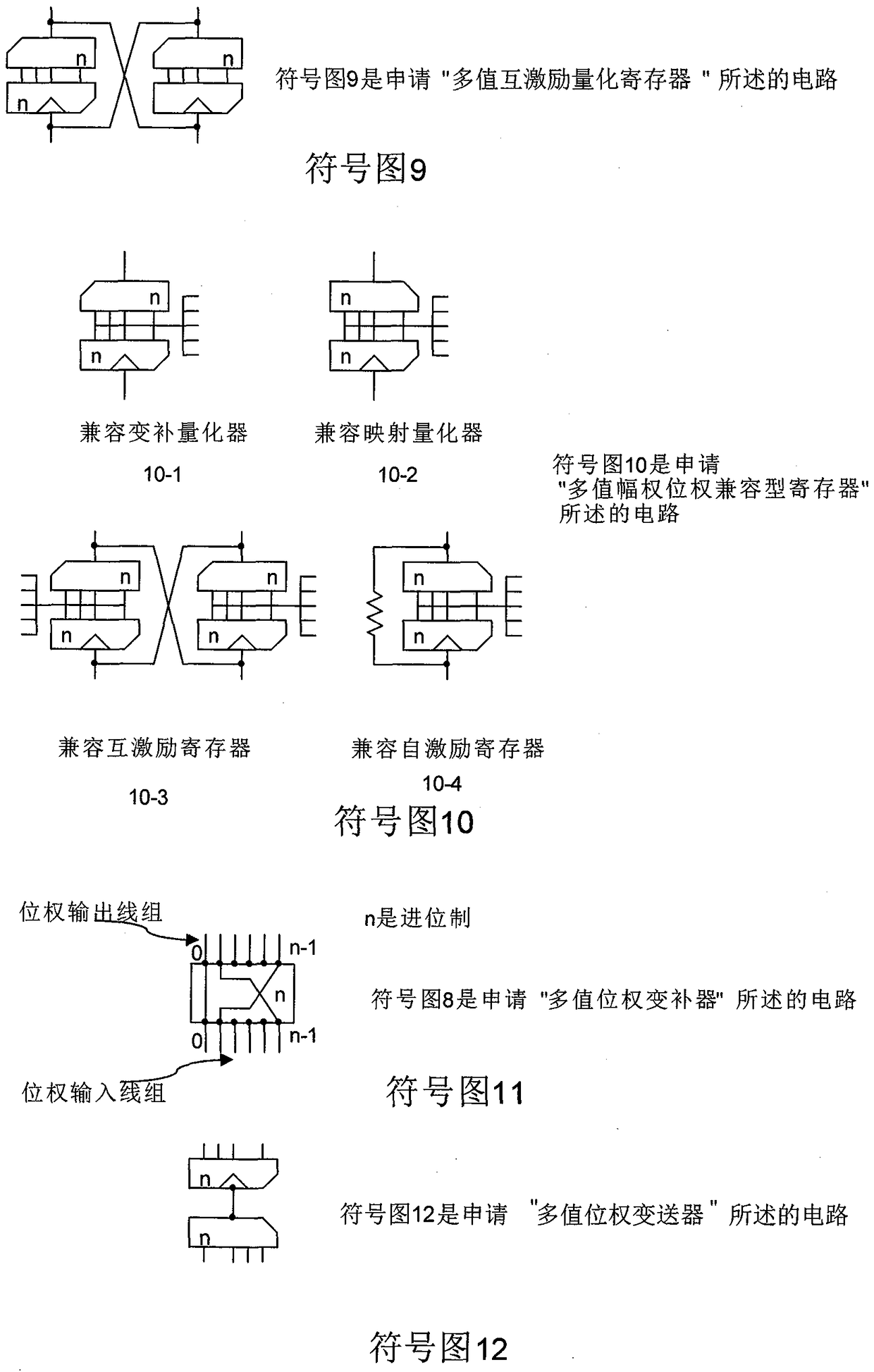

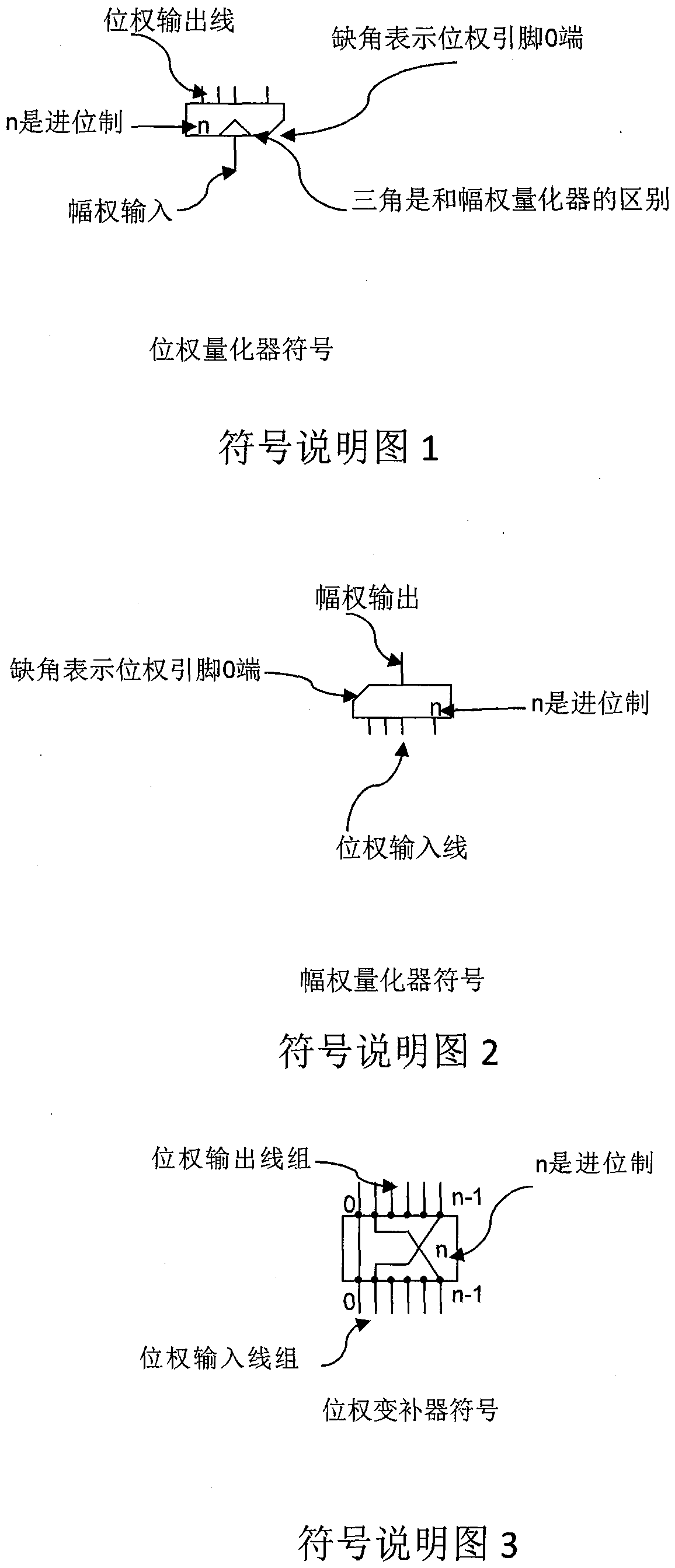

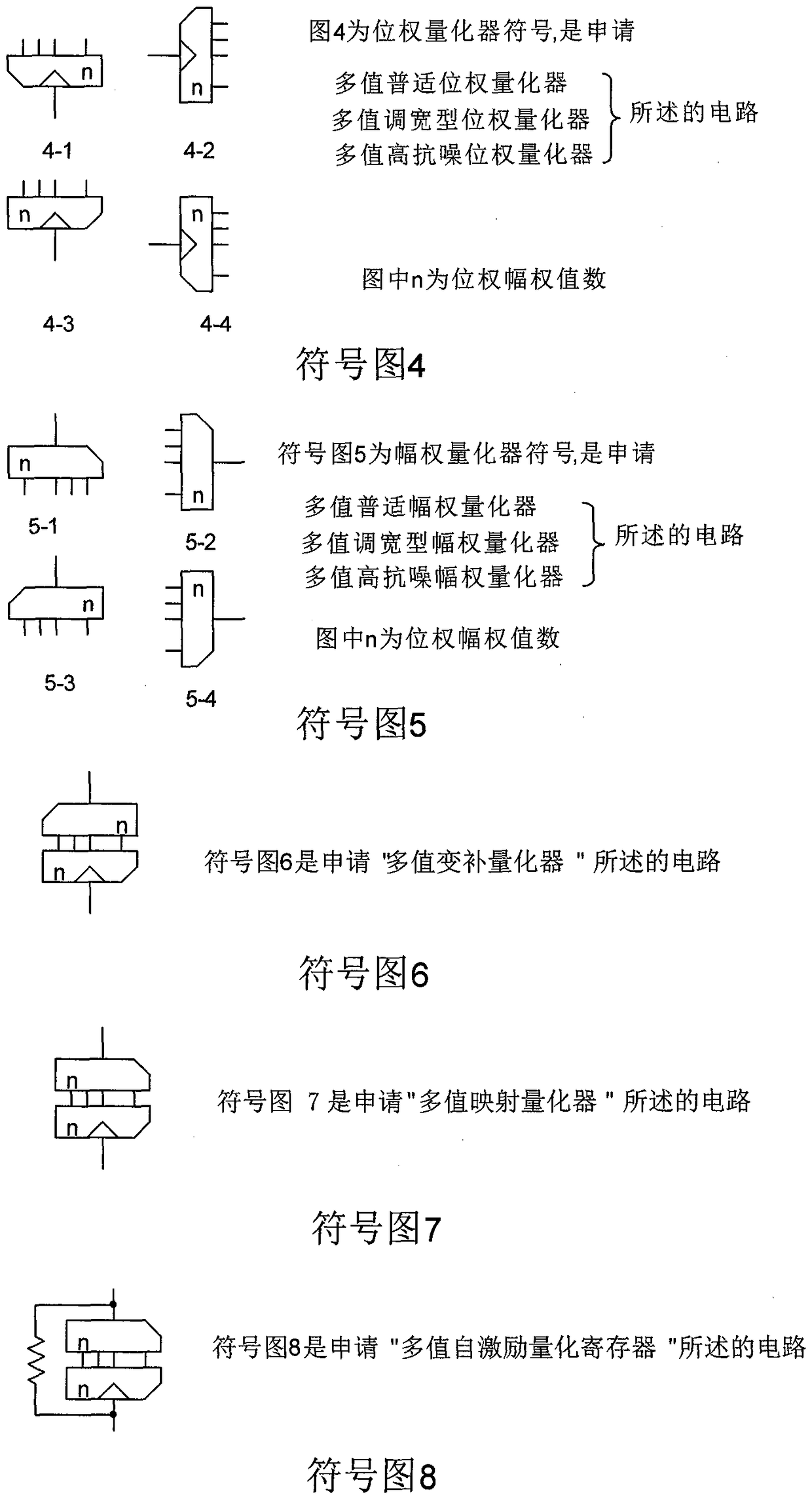

Image

Examples

Embodiment Construction

[0050] refer to image 3, use a ternary weight quantizer and a ternary weight quantizer to connect to form a ternary weight changer; the ternary weight quantizer has bit weight lines W0, W1, W2, and the ternary weight quantizer has bit The weight lines F0, F1, and F2 are directly connected to the 0-bit weight lines W0 and F0 of the three-value bit weight quantizer and the three-value amplitude weight quantizer, and the other bit weight lines are connected according to the serial number reversal. The connection method is: W1 to F2 , W2 is connected to F1, the amplitude weight input terminal of the three-valued amplitude weight quantizer is used as the input terminal of the compensator, and the amplitude weight output terminal of the three-valued amplitude weight quantizer is used as the output terminal of the compensator.

[0051] refer to image 3 , use a four-value bit weight quantizer and a four-value amplitude weight quantizer to connect to form a four-value amplitude weig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More