MOS (Metal Oxide Semiconductor) tube grid control transmission type multi-system and decimal bit weight multiplier

A MOS tube and gate control technology, applied in the computer field, can solve problems such as slow development and achieve the effect of effective hardware support

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

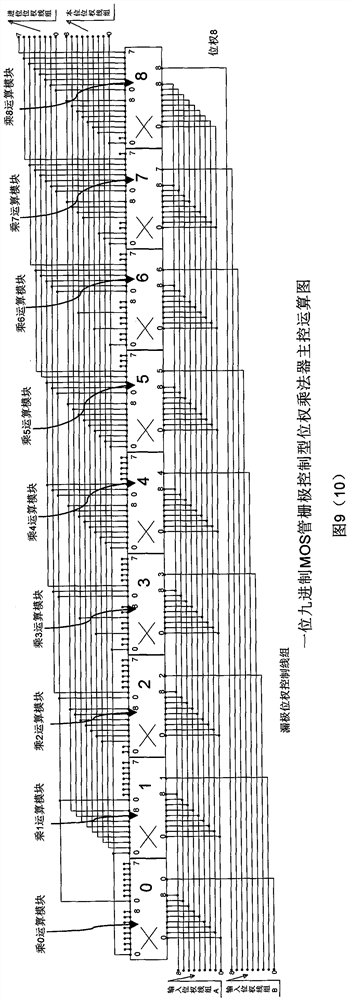

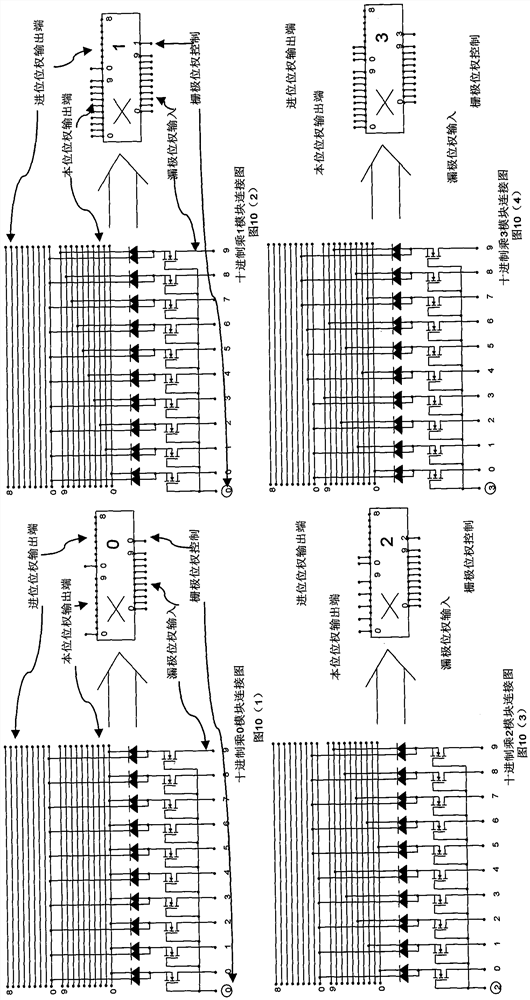

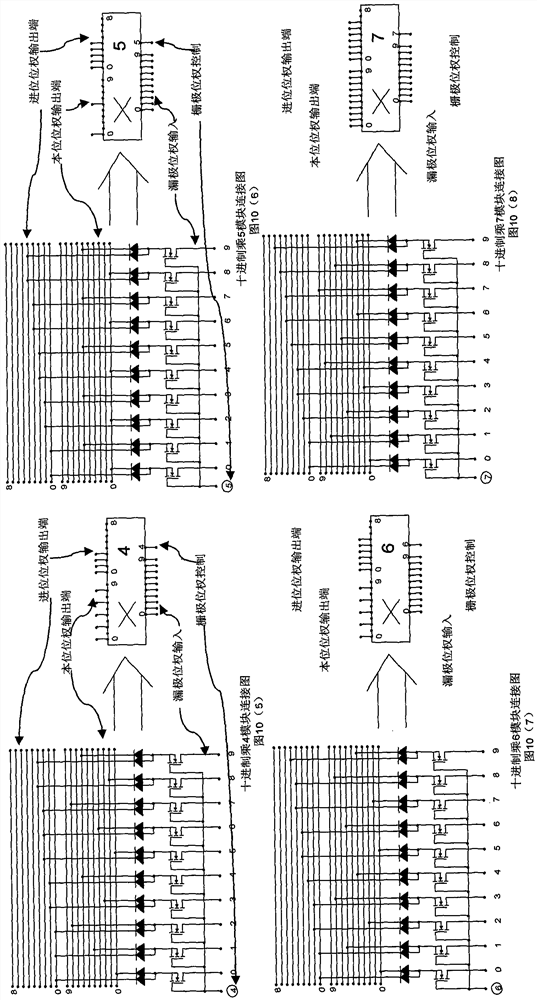

[0119] refer to figure 2 (1), 2(2), 2(3), use the unit circuit described in claim 3 in the multi-ary system arithmetic operator of quantization logic of two patent applications 201711119713.x to form two fractal integrated unit circuits MOS tube gate control module, multiplied by 0 module, multiplied by 1 module. Multiply by 0 module by figure 2 The method described in (1) and figure 1 (1) In the multiplication table, the input and output bit weight information are correspondingly connected to the input and output bit weight bus. Multiply by 1 module according to figure 2 The method described in (2) and figure 1(1) In the multiplication table, the input and output bit weight information are correspondingly connected to the input and output bit weight bus. Finally follow figure 2 (3) The method of multiplying 0 module, multiplying the input and output bus of 1 module is connected together as the bit weight input and output of the multiplier according to the line numbe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More