Width adjustment type self-excitation quantization register of quantification logic

A current-type, self-exciting technology, applied in the computer field, can solve problems such as slow development, and achieve the effect of reliable implementation, rich operation relationship and output.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

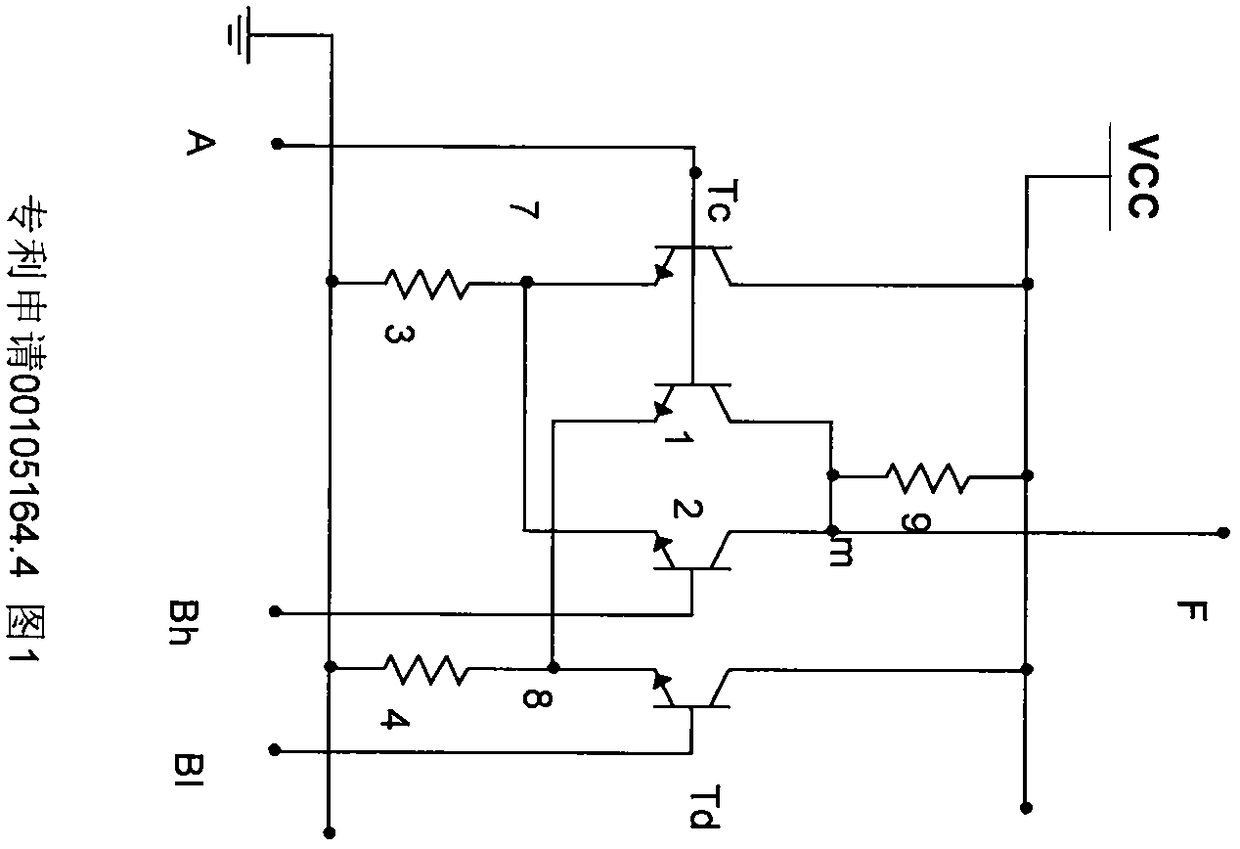

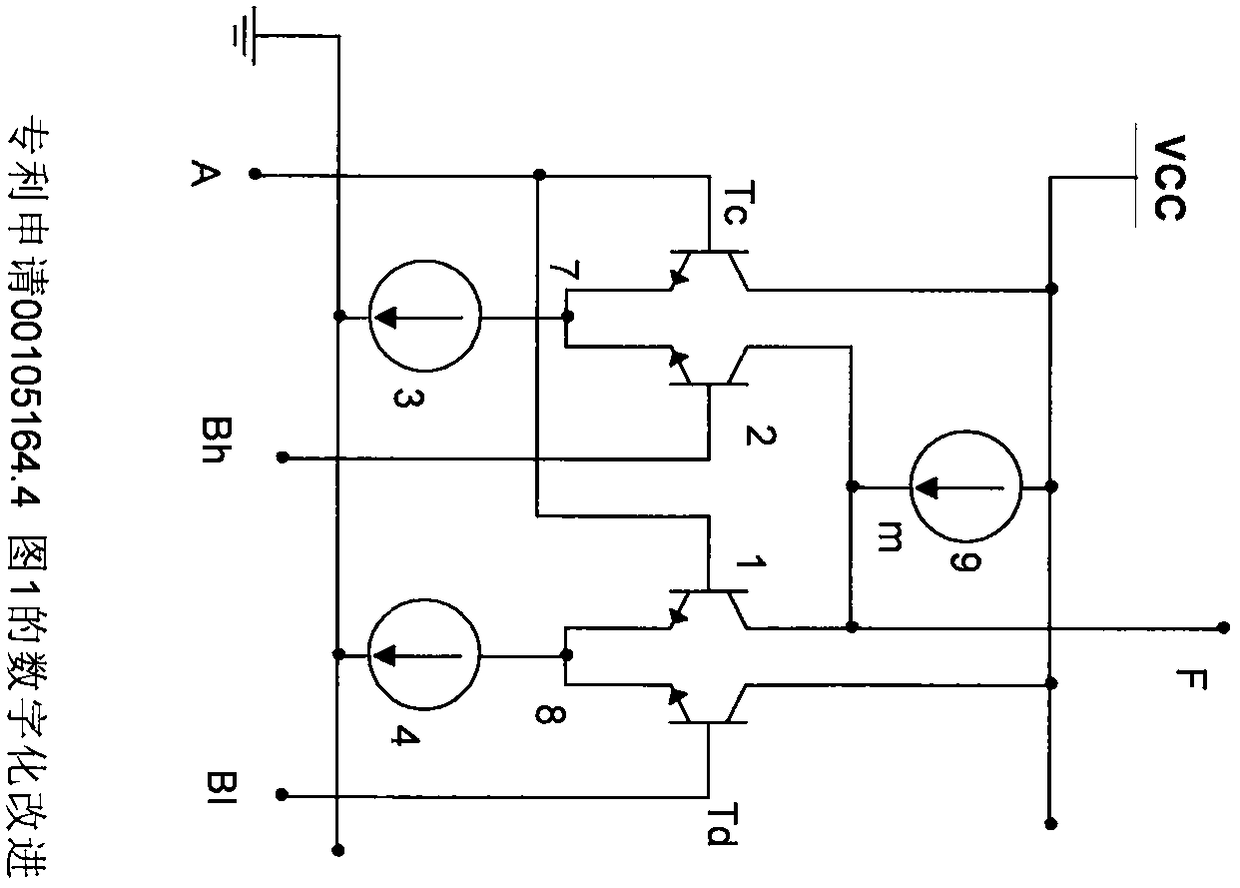

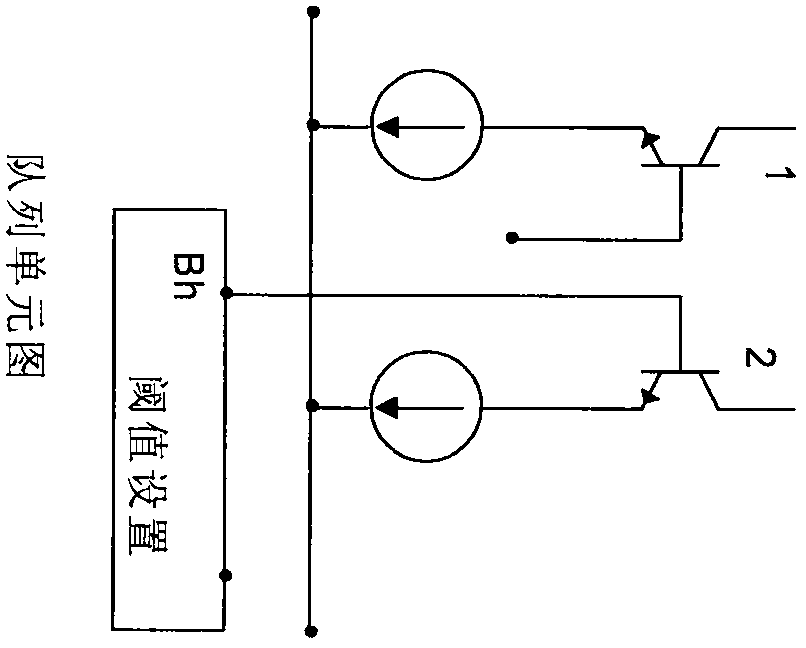

[0051] refer to Figure 5 , with a image 3 The unit circuit is used as a queue circuit ① and the transistors Tc and Td are connected at both ends of the queue circuit, and the emitter of the transistor Tc is connected to one end of the queue ① The emitter of the unit transistor 2 is coupled through Ie, and the emitter of the transistor Td is connected to The emitter of the transistor 1 at one end of the queue is connected through Ie coupling; then the collector of the transistor 1 in the queue ① and the collector of the transistor Ta are connected together to form a node G, and the collector of the transistor 2 in the queue ① and the transistor Td The collectors of the transistors are connected together to form the node V, the base of the transistor 1 in the queue ① and the base of the transistor Tc are connected together to form a read-write terminal node, the node V is connected to the positive pole of the power supply, and the node G is connected to the transistor T1 , T2...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap