A cache control method, system, storage medium, computer equipment and application

A cache control and caching technology, applied in the field of data exchange, can solve the problems of low bandwidth utilization, data packet processing delay, limit packet unit anti-flow, burst, etc., to reduce time-consuming data movement, improve bandwidth utilization, The effect of reducing waiting time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0087]In order to make the objectives, technical solutions and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the embodiments. It should be understood that the specific embodiments described herein are only used to explain the present invention, but not to limit the present invention.

[0088] In view of the problems existing in the prior art, the present invention provides a cache control method, system, storage medium, computer equipment and application. The present invention is described in detail below with reference to the accompanying drawings.

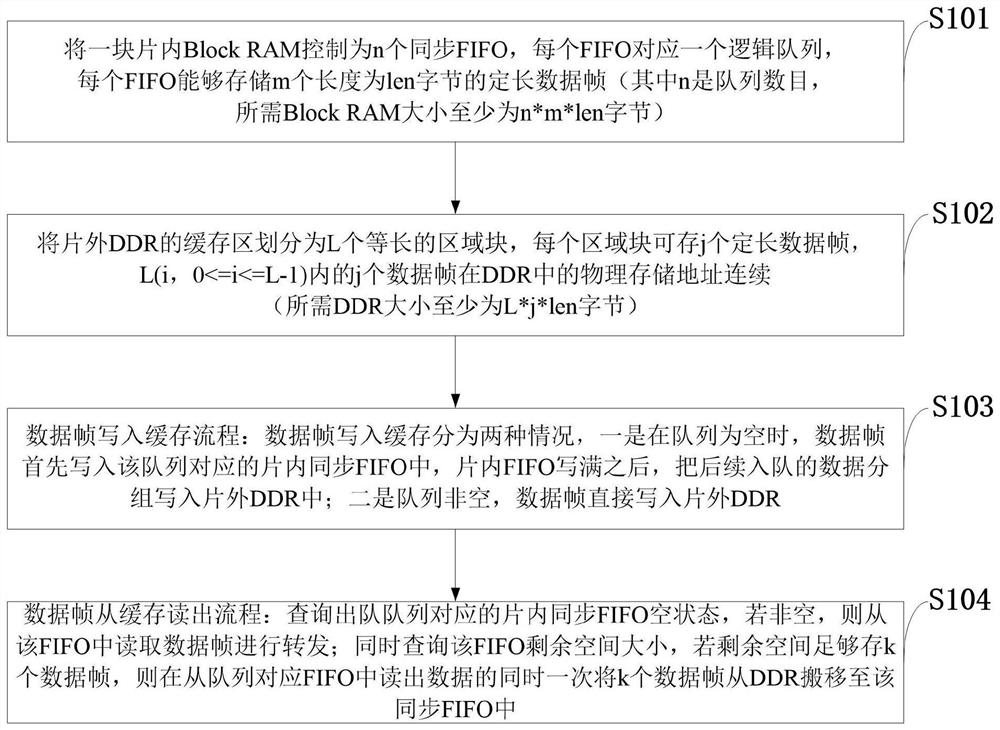

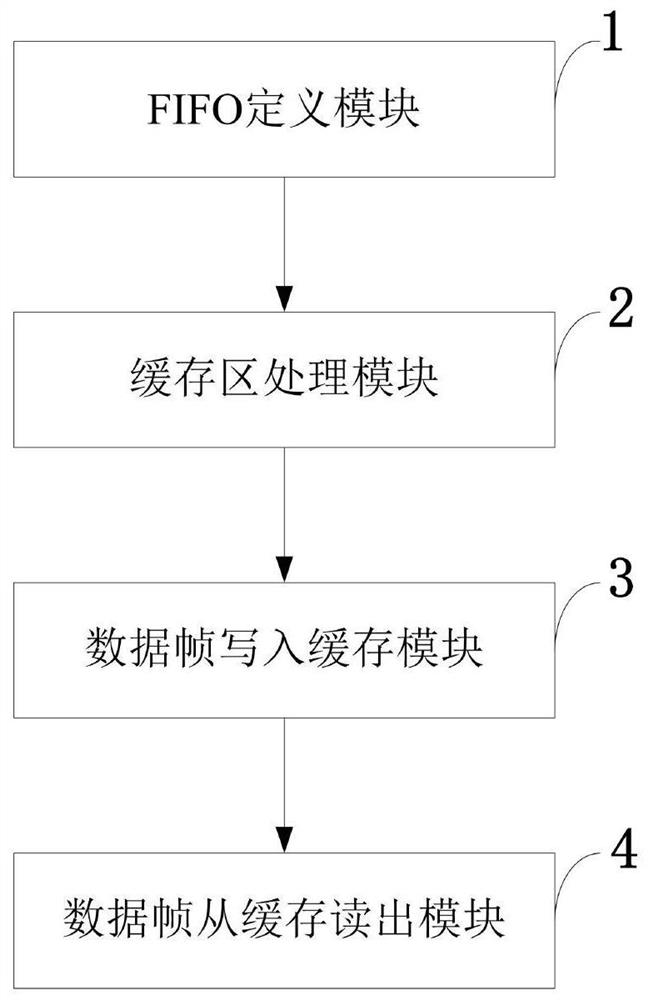

[0089] like figure 1 As shown, the cache control method provided by the present invention includes the following steps:

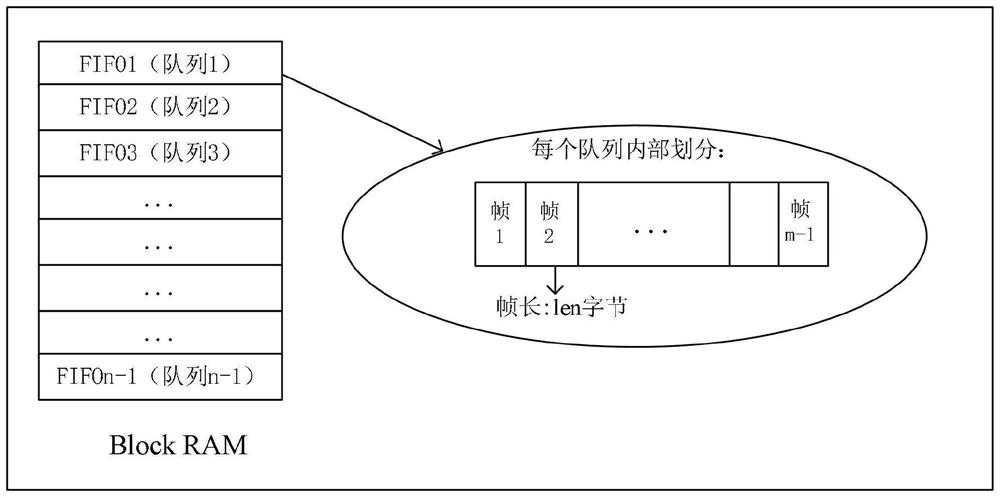

[0090] S101: Control an on-chip Block RAM into n synchronous FIFOs, each FIFO corresponds to a logical queue, and each FIFO can store m fixed-length data frames with a length of len bytes (where n is the number of queues, the req...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More