Patents

Literature

1423 results about "Reading (computer)" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Reading is an action performed by computers, to acquire data from a source and place it into their volatile memory for processing. Computers may read information from a variety of sources, such as magnetic storage, the Internet, or audio and video input ports. Reading is one of the core functions of a Turing machine.

Associative database scanning and information retrieval

InactiveUS7181437B2Threshold may be loweredRaise the importanceData processing applicationsInput/output to record carriersMass storageExact match

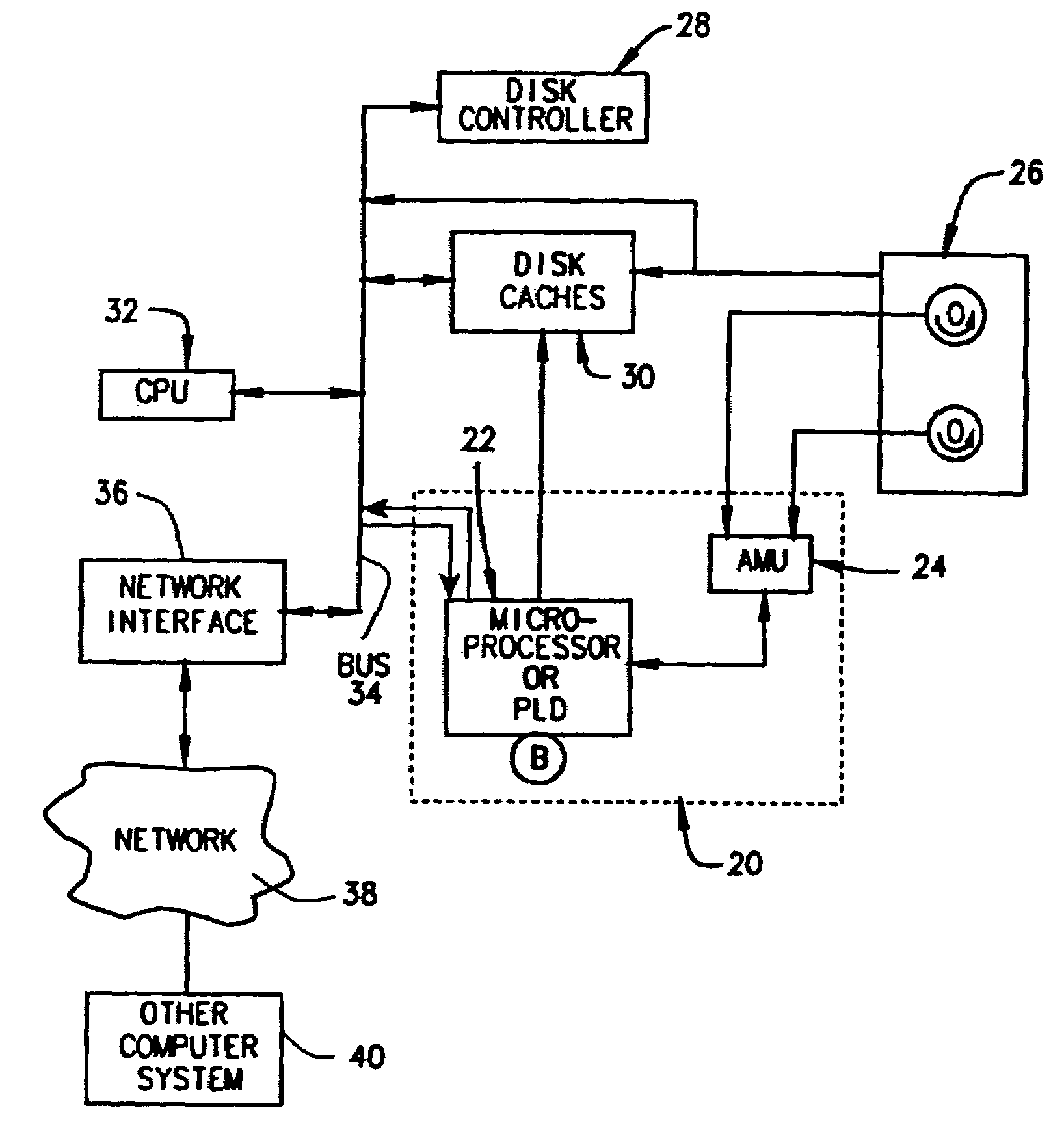

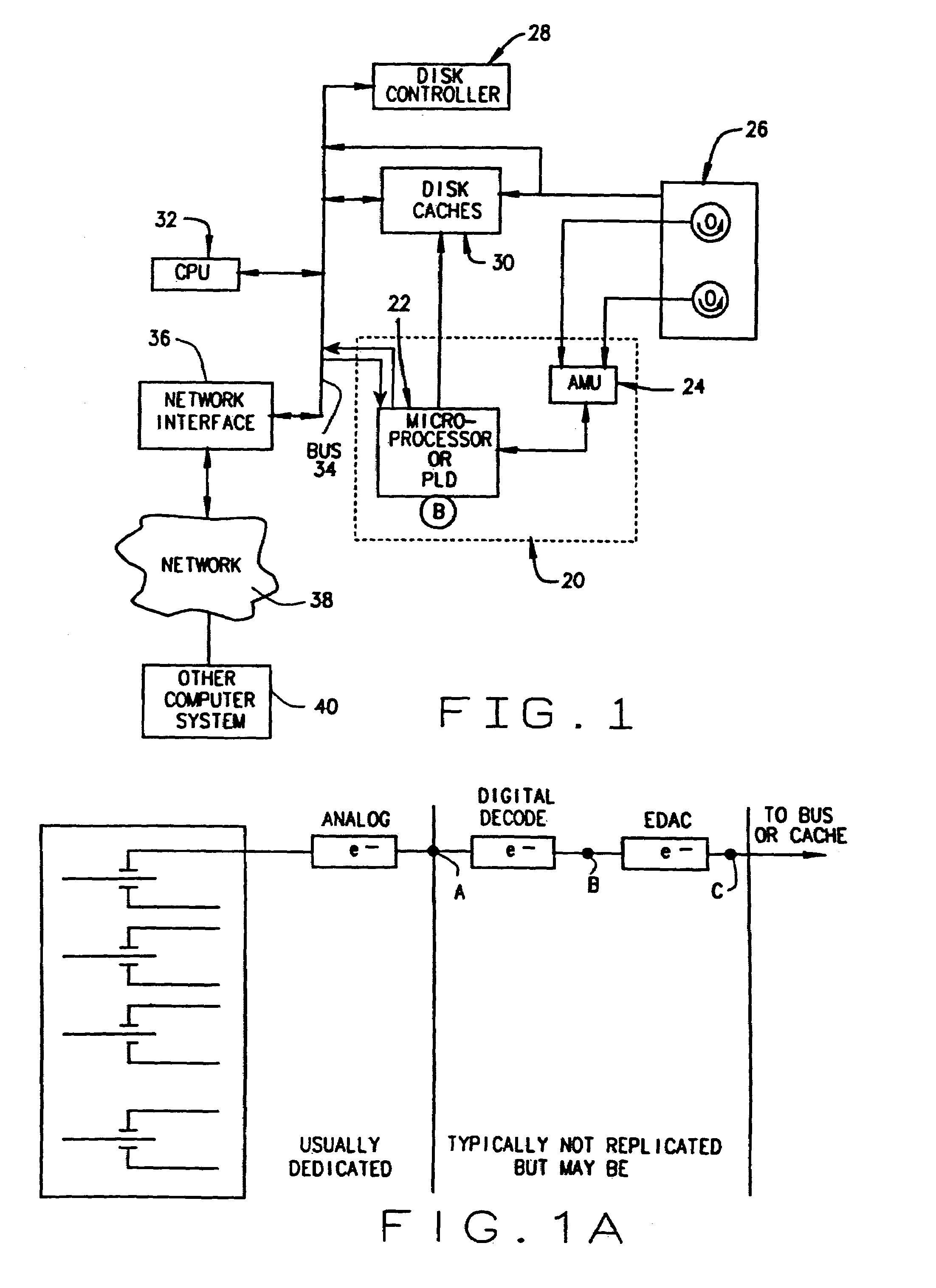

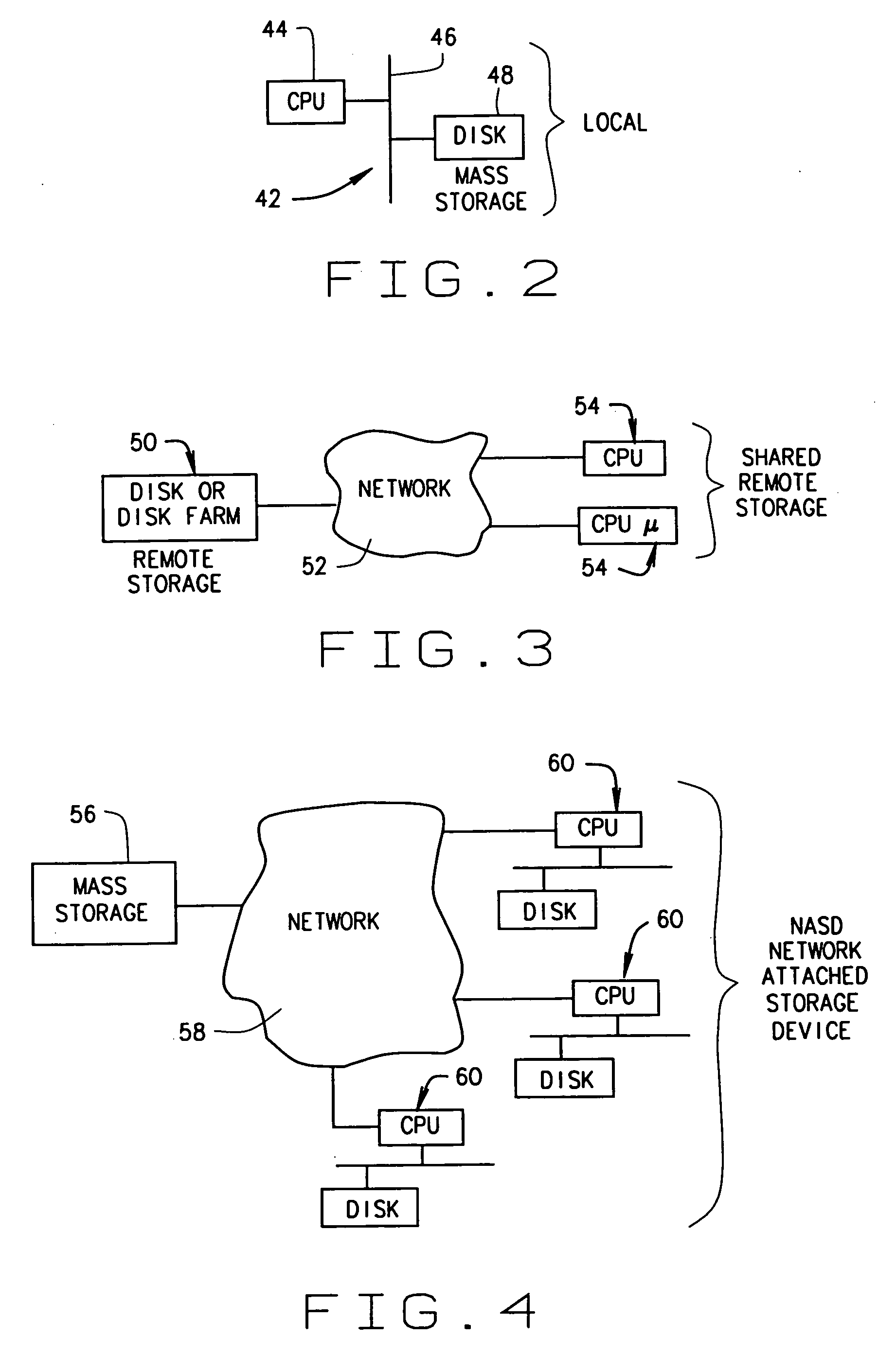

A method and device are disclosed for an associative and approximate, analog or digital scanning of databases that allows for the asynchronous accessing of data from a mass storage medium. The invention includes providing dedicated analog and digital circuitry and decision logic at the mass storage medium level for determining a key identifying the data of interest, continuously comparing the key to a signal generated from a reading of the data from the mass storage medium with an approximate or exact matching circuit to determine a pattern match, determining a correlation value between the key and the data as it is read in a continuous fashion, and determining a match based upon a preselected threshold value for the correlation value. The pattern matching technique eliminates any need to compare data based on its intrinsic structure or value, and instead is based on an analog or digital pattern. The key and data may be either analog or digital. This device and method may be provided as part of a stand-alone computer system, embodied in a network attached storage device, or can otherwise be provided as part of a computer LAN or WAN.

Owner:IP RESERVOIR

Multi-thread parallel processing method based on multi-thread programming and message queue

ActiveCN102902512AFast and efficient multi-threaded transformationReduce running timeConcurrent instruction executionComputer architectureConcurrent computation

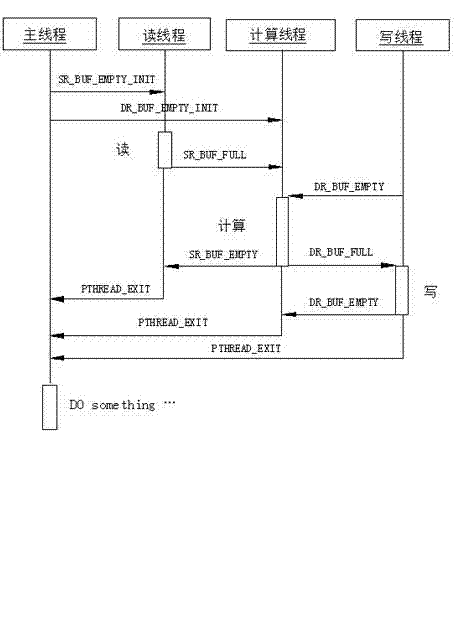

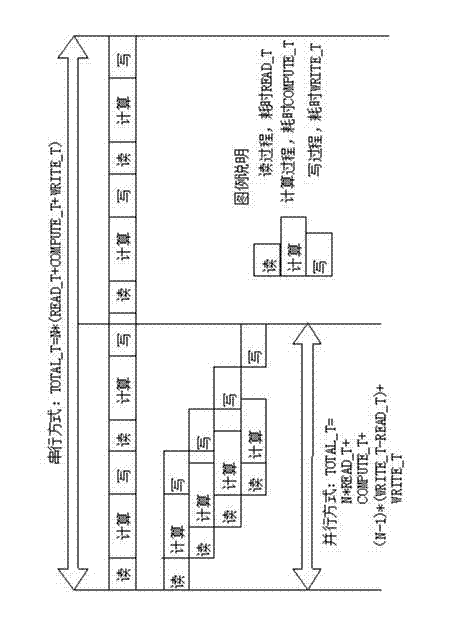

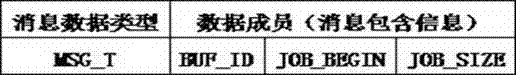

The invention provides a multi-thread parallel processing method based on a multi-thread programming and a message queue, belonging to the field of high-performance computation of a computer. The parallelization of traditional single-thread serial software is modified, and current modern multi-core CPU (Central Processing Unit) computation equipment, a pthread multi-thread parallel computing technology and a technology for realizing in-thread communication of the message queue are utilized. The method comprises the following steps of: in a single node, establishing three types of pthread threads including a reading thread, a computing thread and a writing thread, wherein the quantity of each type of the threads is flexible and configurable; exploring multi-buffering and establishing four queues for the in-thread communication; and allocating a computing task and managing a buffering space resource. The method is widely applied to the application field with multi-thread parallel processing requirements; a software developer is guided to carry out multi-thread modification on existing software so as to realize the optimization of the utilization of a system resource; and the hardware resource utilization rate is obviously improved, and the computation efficiency of software and the whole performance of the software are improved.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

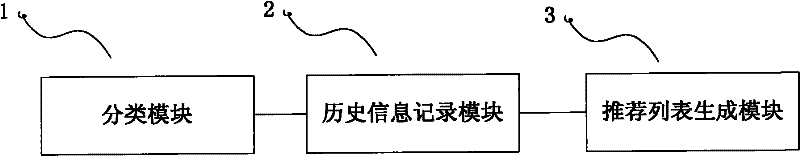

Recommendation list generation method, device, media server, client and method

ActiveCN102236669AImprove experienceFind quicklySpecial data processing applicationsReading (computer)Media server

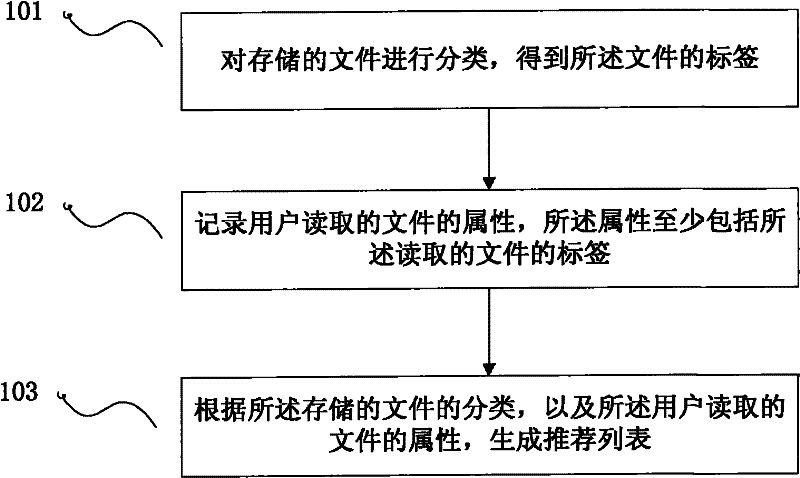

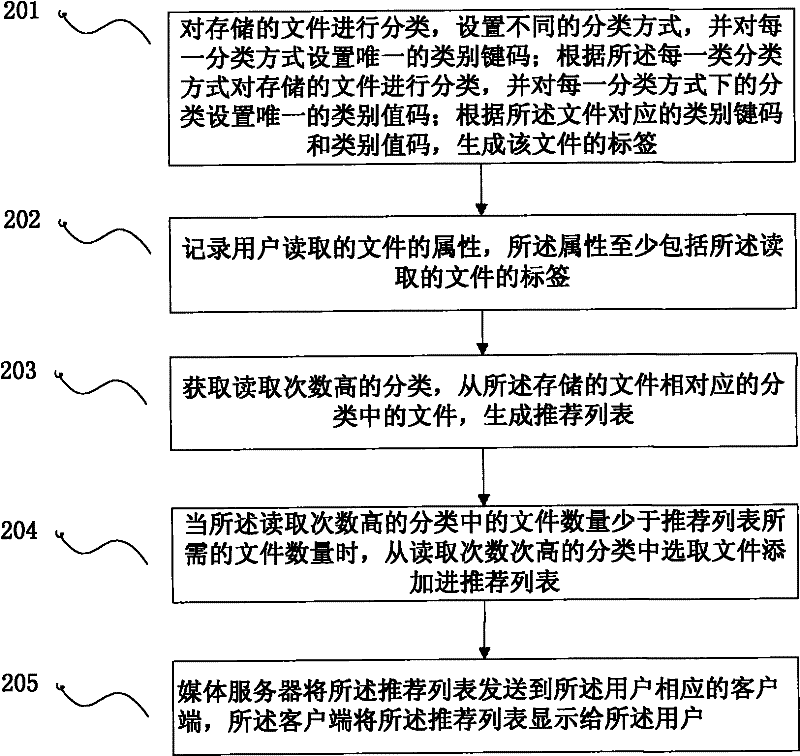

The invention discloses a recommendation list generation method, a recommendation list generation device, a media server, a client and a method, and belongs to the technical field of computers. The embodiment of the invention generates a recommendation list according to files in classes with higher user reading frequency for the file reading records of a user. In the embodiment, the likes and dislikes of the user can be learned according to the file reading records of the user, thereby generating the recommendation list for the files in the favorite classes of the user. Compared with the conventional single recommendation list way, the embodiment of the invention can be closer to the likes and dislikes of the user, improve user experiences, increase the hit rate, enable the user to more rapidly find own interested files and solve the problems of poor experiences and wasting of system resources and network resources caused by the random clicking of the user.

Owner:TENCENT TECH (SHENZHEN) CO LTD

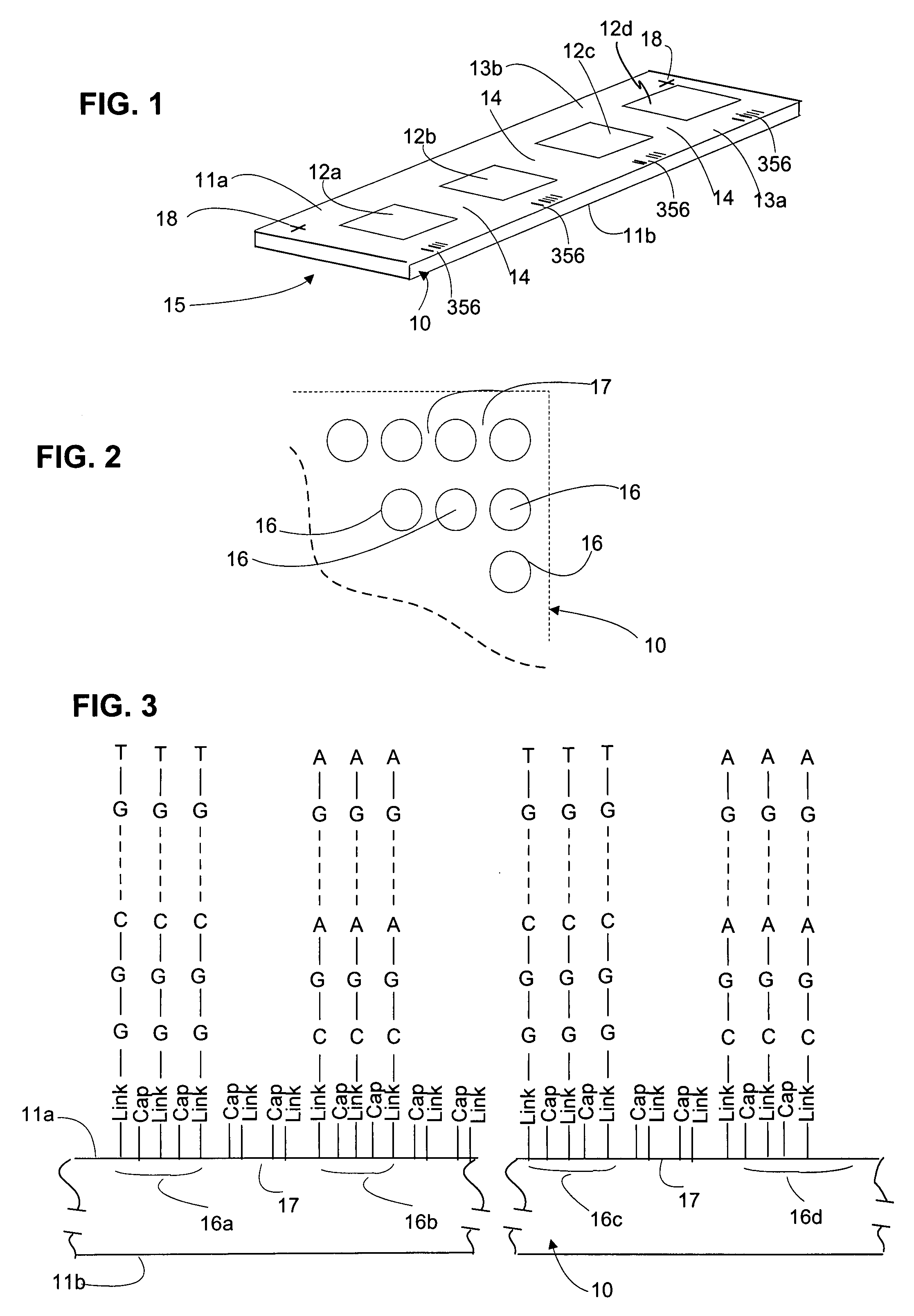

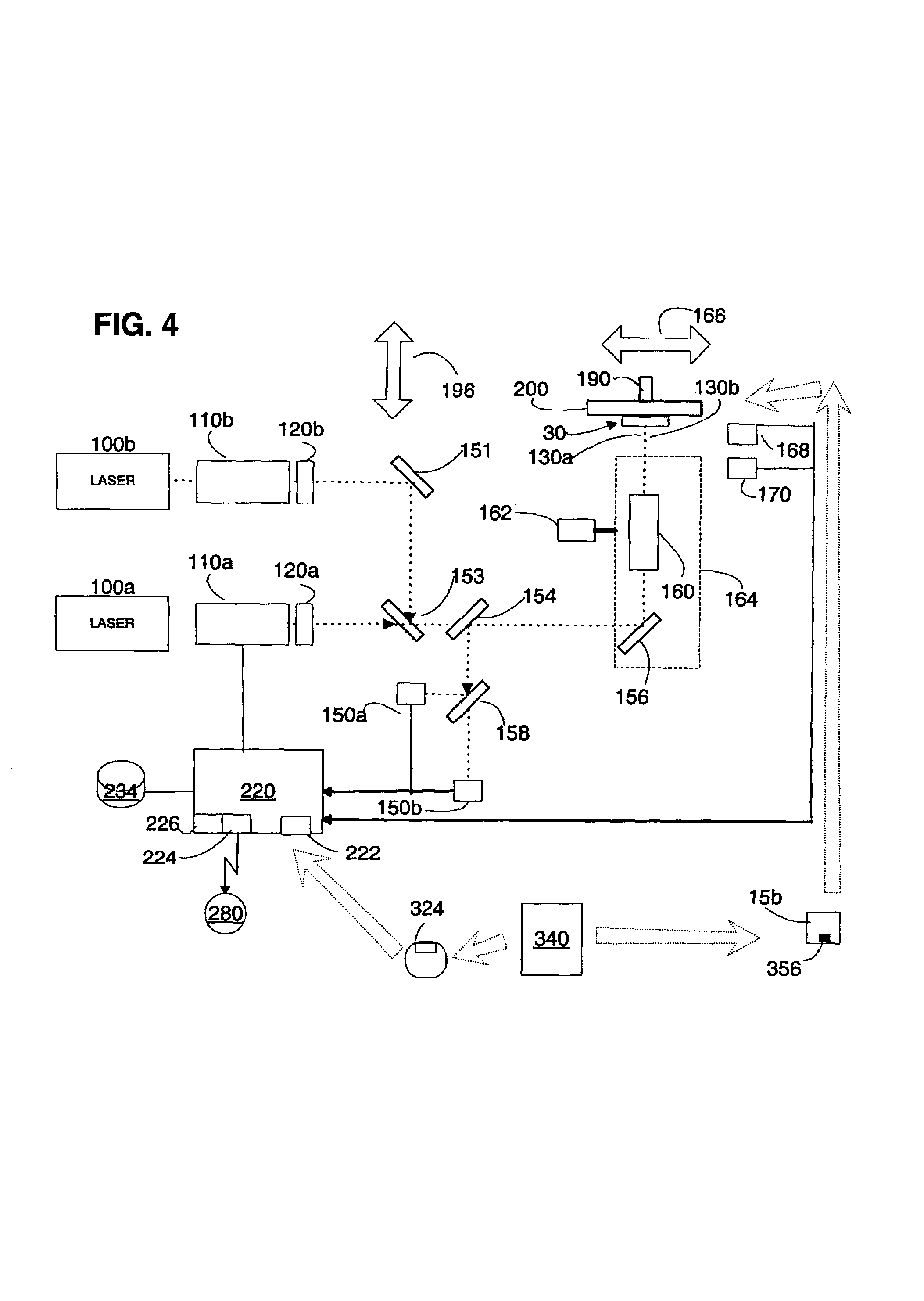

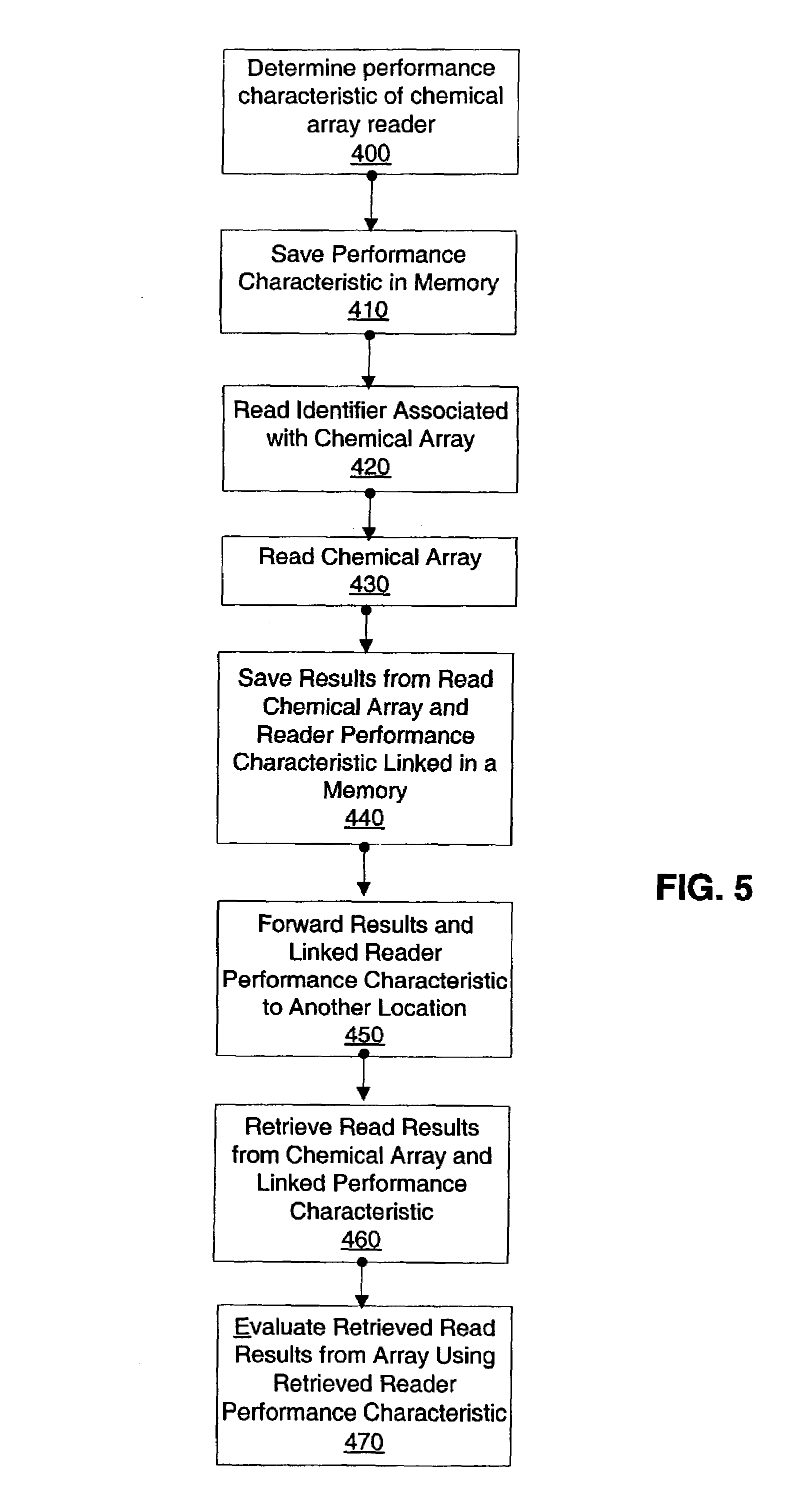

Chemical array reading

InactiveUS7269518B2Reduce misunderstandingEasy to implementBioreactor/fermenter combinationsMaterial nanotechnologyParallel computingComputer program

A method in which a chemical array is read on an array reader and the results saved in a memory linked with a performance characteristic of the array reader. Alternatively or additionally results from reading an array and a linked performance characteristic of a reader which performed the reading are retrieved from a memory. Computer program products and apparatus are also provided.

Owner:AGILENT TECH INC

Automatic patent claim reader and computer-aided claim reading method

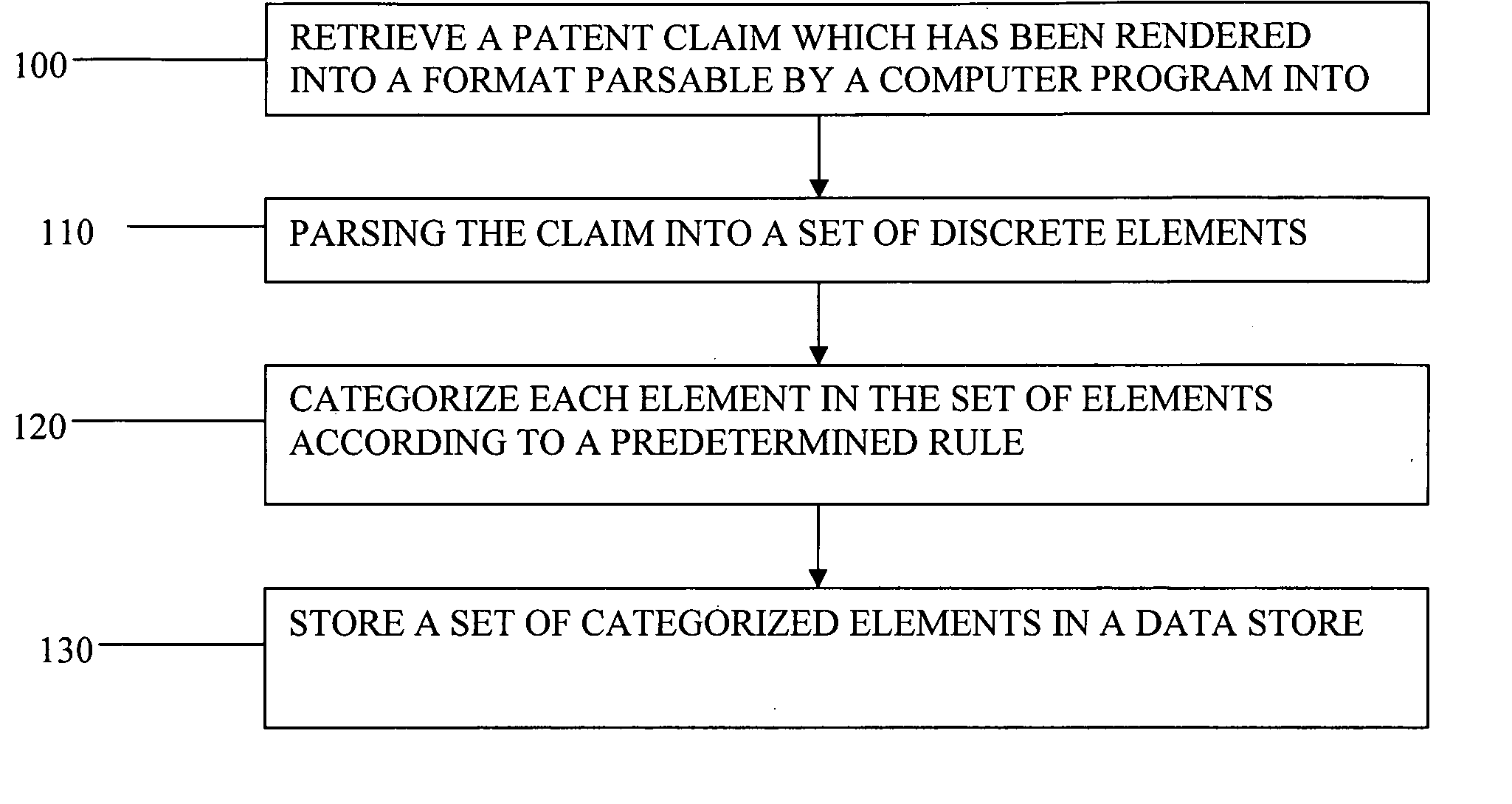

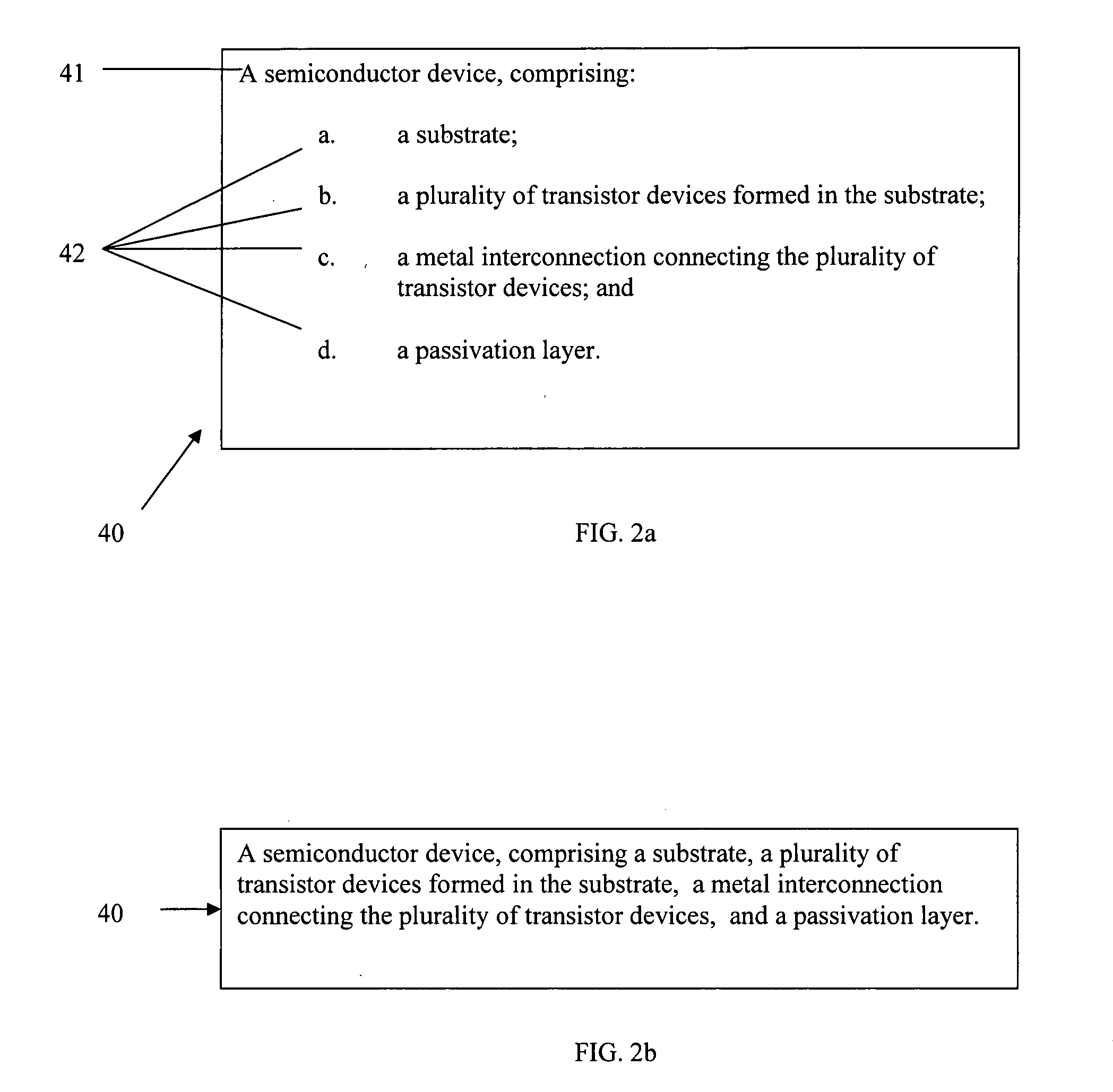

A method of analyzing a claim in a patent or patent application is disclosed, comprising retrieving a patent claim which has been rendered into a format parsable by a computer program into a computer memory; parsing the claim into a set of discrete elements; categorizing each element in the set of elements according to a predetermined rule; and storing a set of categorized elements in a data store. A parsing program executable in a computer may be used to parse the patent claim and, optionally, to identify one or more keyword sets in the parsed claim. A rating program may also be used to assign a rating weight to each categorized element. It is emphasized that this abstract is provided to comply with the rules requiring an abstract which will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or meaning of the claims.

Owner:TAIWAN SEMICON MFG CO LTD

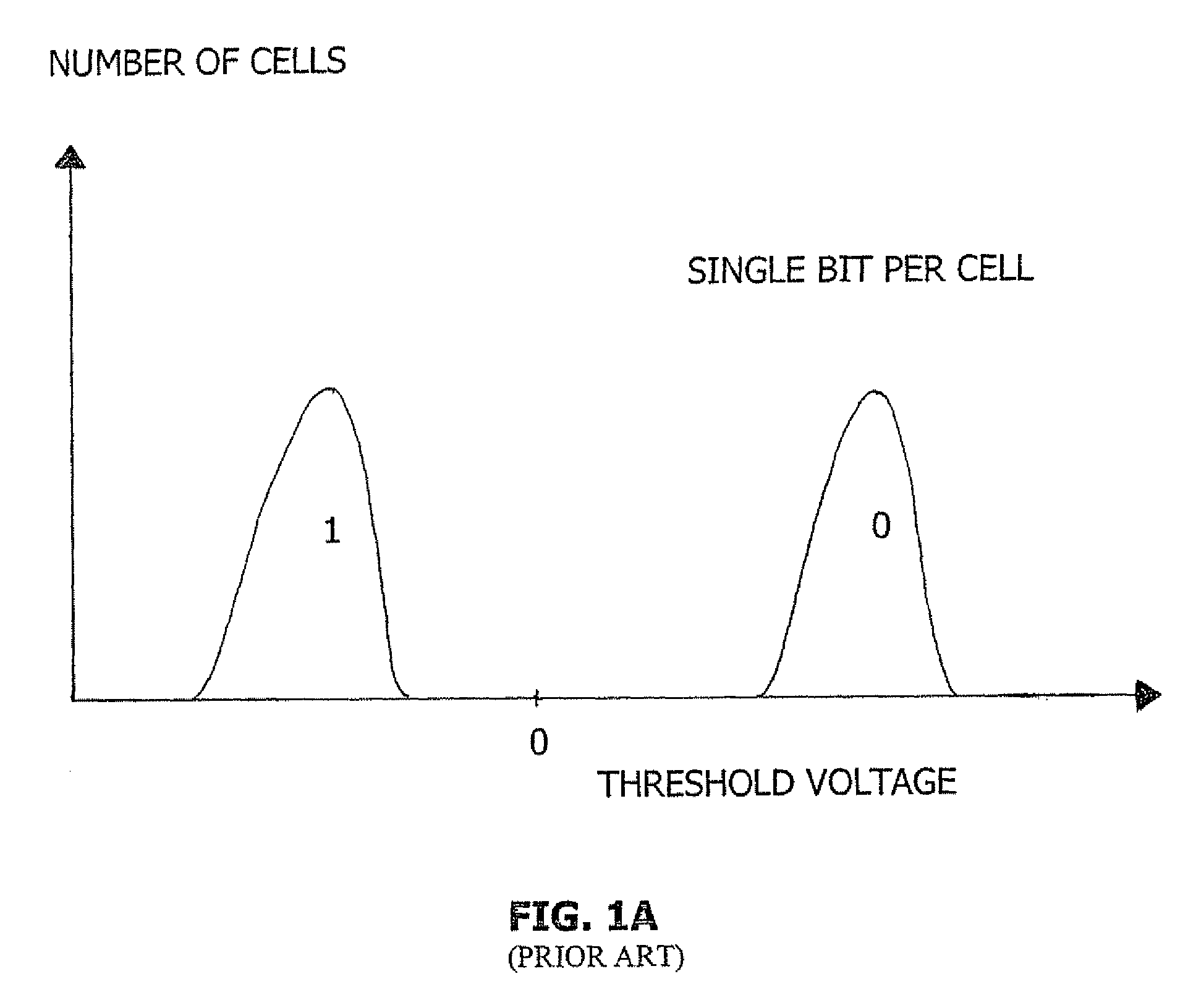

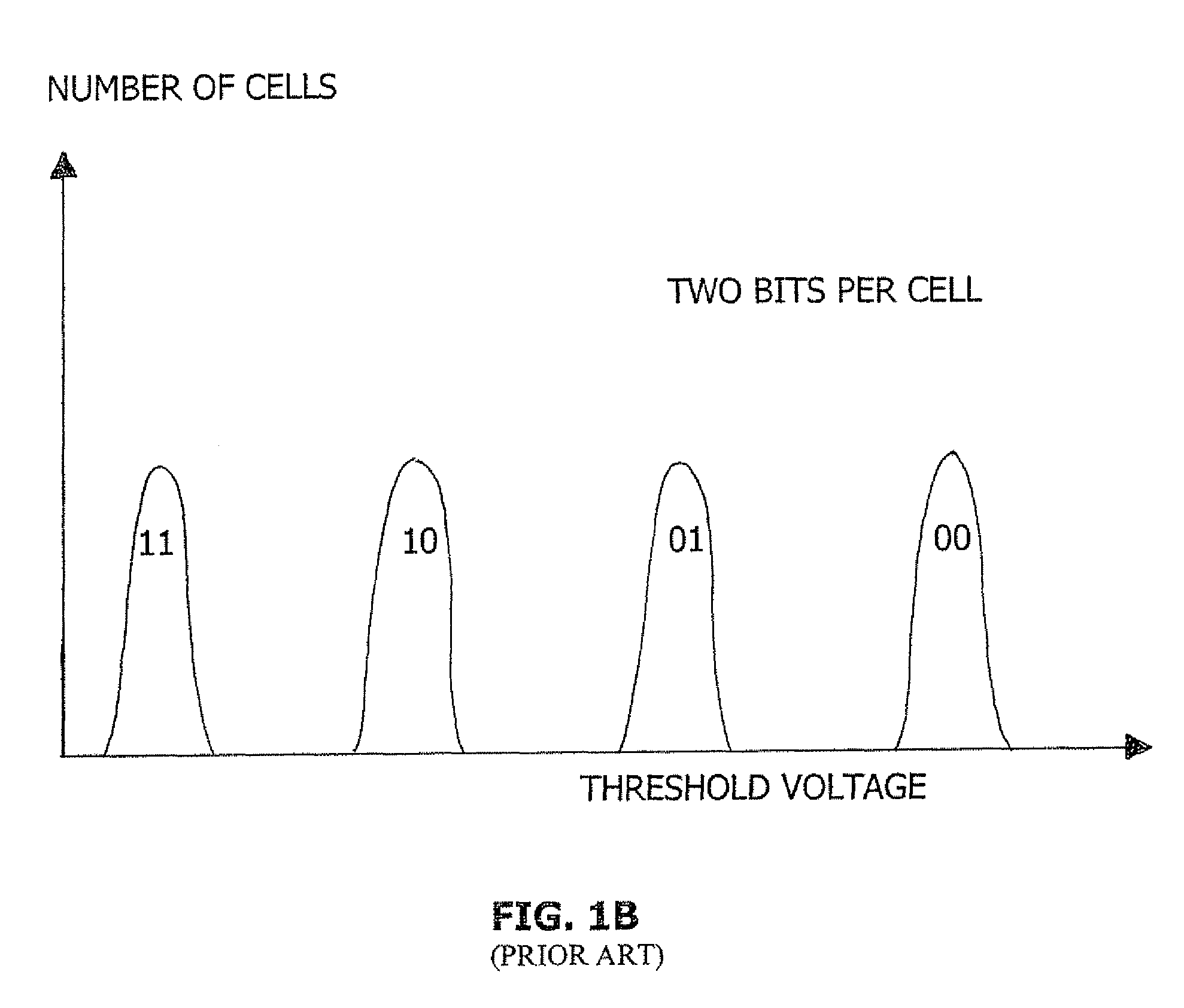

Method for recovering from errors in flash memory

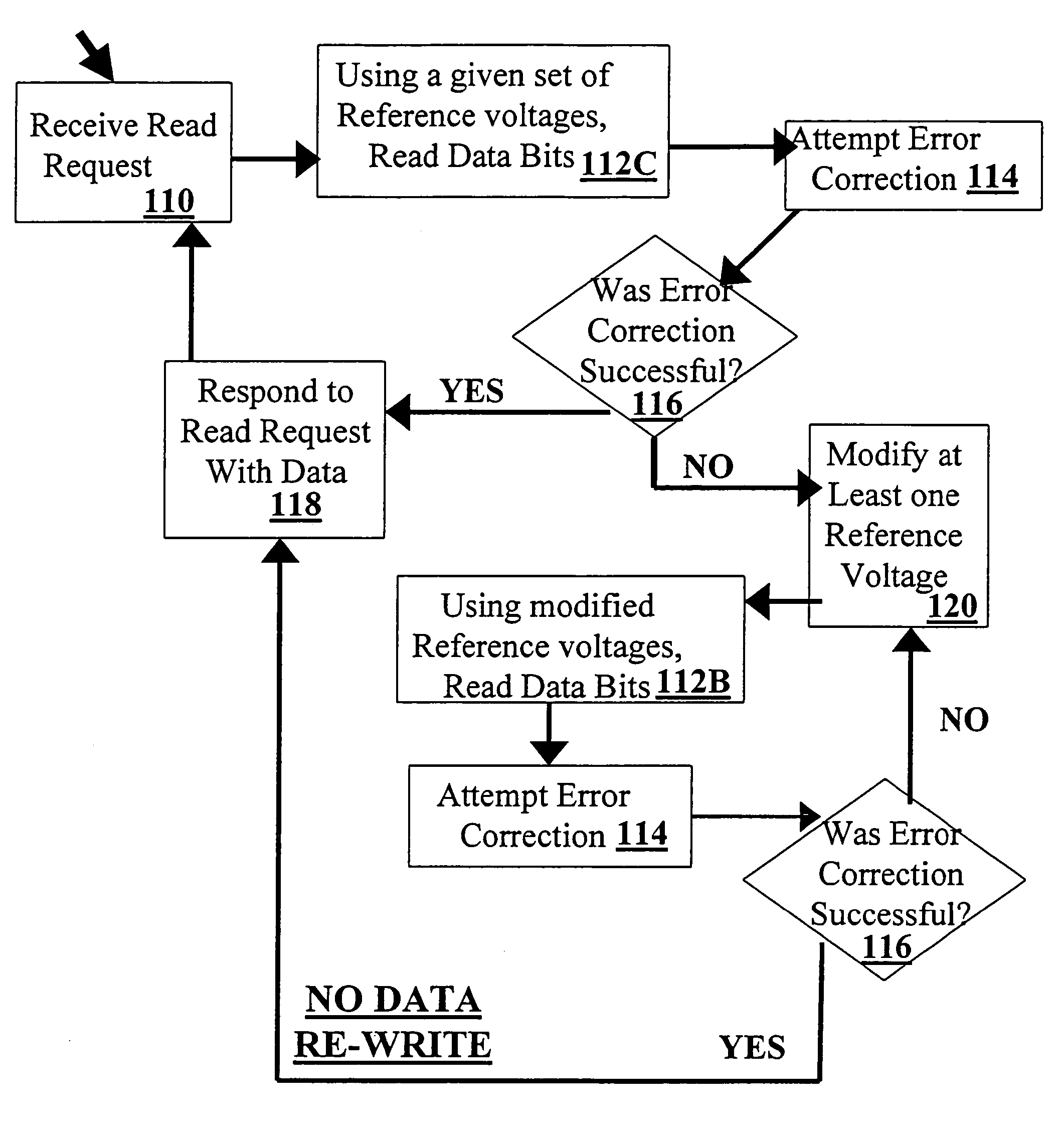

Methods, devices and computer readable code for reading data from one or more flash memory cells, and for recovering from read errors are disclosed. In some embodiments, in the event of an error correction failure by an error detection and correction module, the flash memory cells are re-read at least once using one or more modified reference voltages, for example, until a successful error correction may be carried out. In some embodiments, after successful error correction a subsequent read request is handled without re-writing data (for example, reliable values of the read data) to the flash memory cells in the interim. In some embodiments, reference voltages associated with a reading where errors are corrected may be stored in memory, and retrieved when responding to a subsequent read request. In some embodiments, the modified reference voltages are predetermined reference voltages. Alternatively or additionally, these modified reference voltages may be determined as needed, for example, using randomly generated values or in accordance with information provided by the error detection and correction module. Methods, devices and computer readable code for reading data for situations where there is no error correction failure are also provided.

Owner:WESTERN DIGITAL ISRAEL LTD

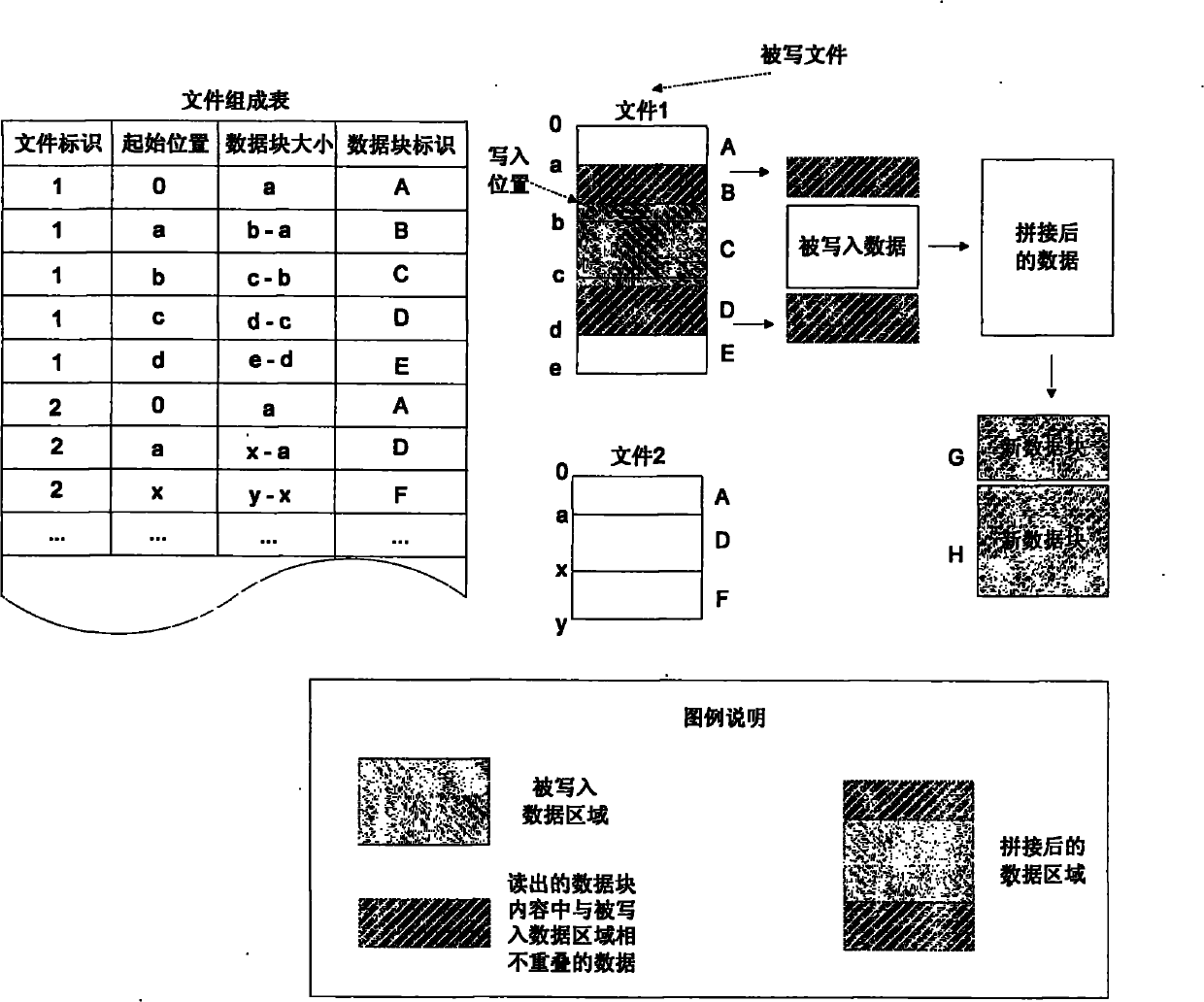

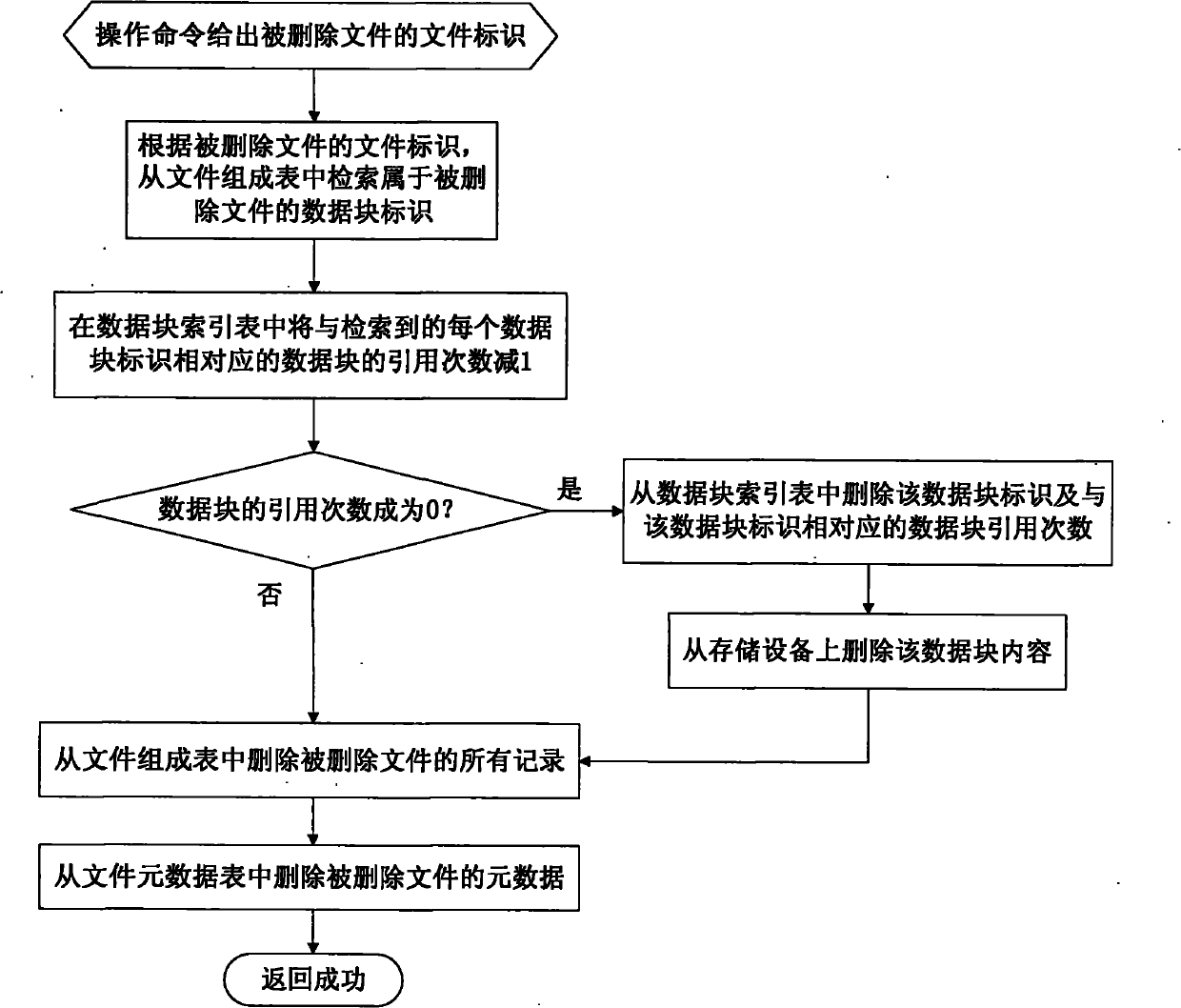

Method for deleting duplicated data in file system in real time

InactiveCN101908073ASave storage spaceImprove processing efficiencySpecial data processing applicationsDatasheetEmbedded database

The invention relates to a method for deleting duplicated data in a file system in real time, and belongs to the technical field of computer data storage. In a file system establishment stage, a file metadata table, a data block index and a file constitution table are set in an embedded database; and in a file system operation stage, operating commands initiated to the file system by applications are received and responded through a file system driver, and include establishing a new file, writing data to an existing file, reading data from the existing file and deleting the existing data. The method simultaneously supports fixed-length and variable-length file blocking methods, and can delete the duplicated data in the file system in real time, save storage space and improve the utilization efficiency of storage equipment; and the process of deleting the duplicated data is completely transparent to the applications and a user, the file operation of various conventional applications is seamlessly compatible, and almost all negative effects on the user experience are avoided.

Owner:TSINGHUA UNIV

Method and apparatus for read error recovery

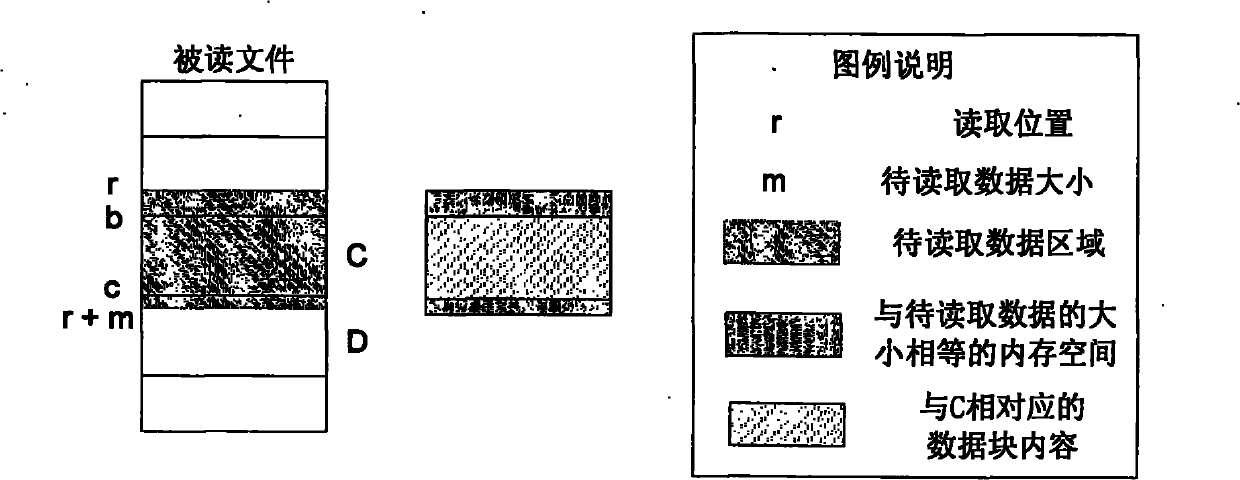

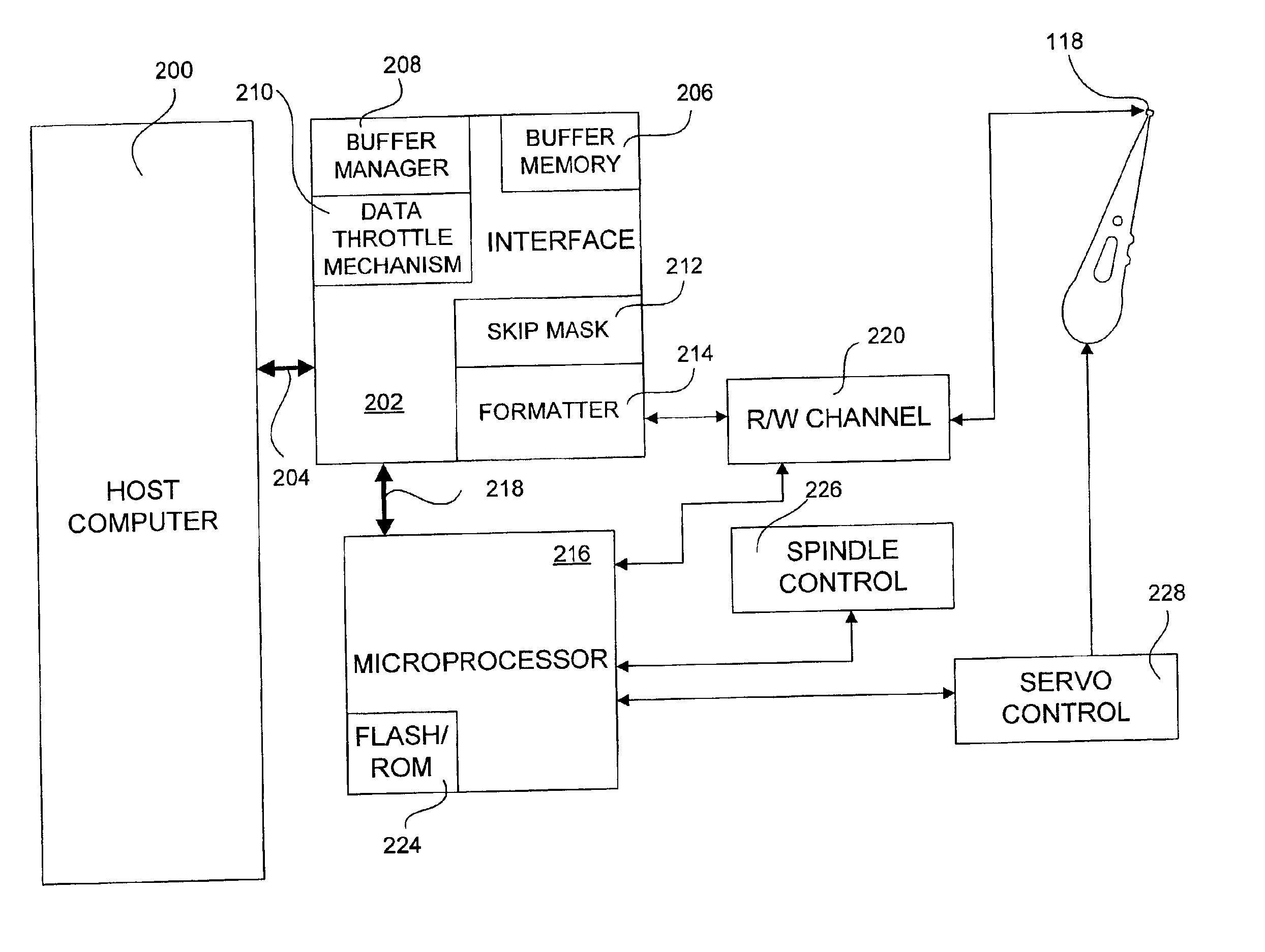

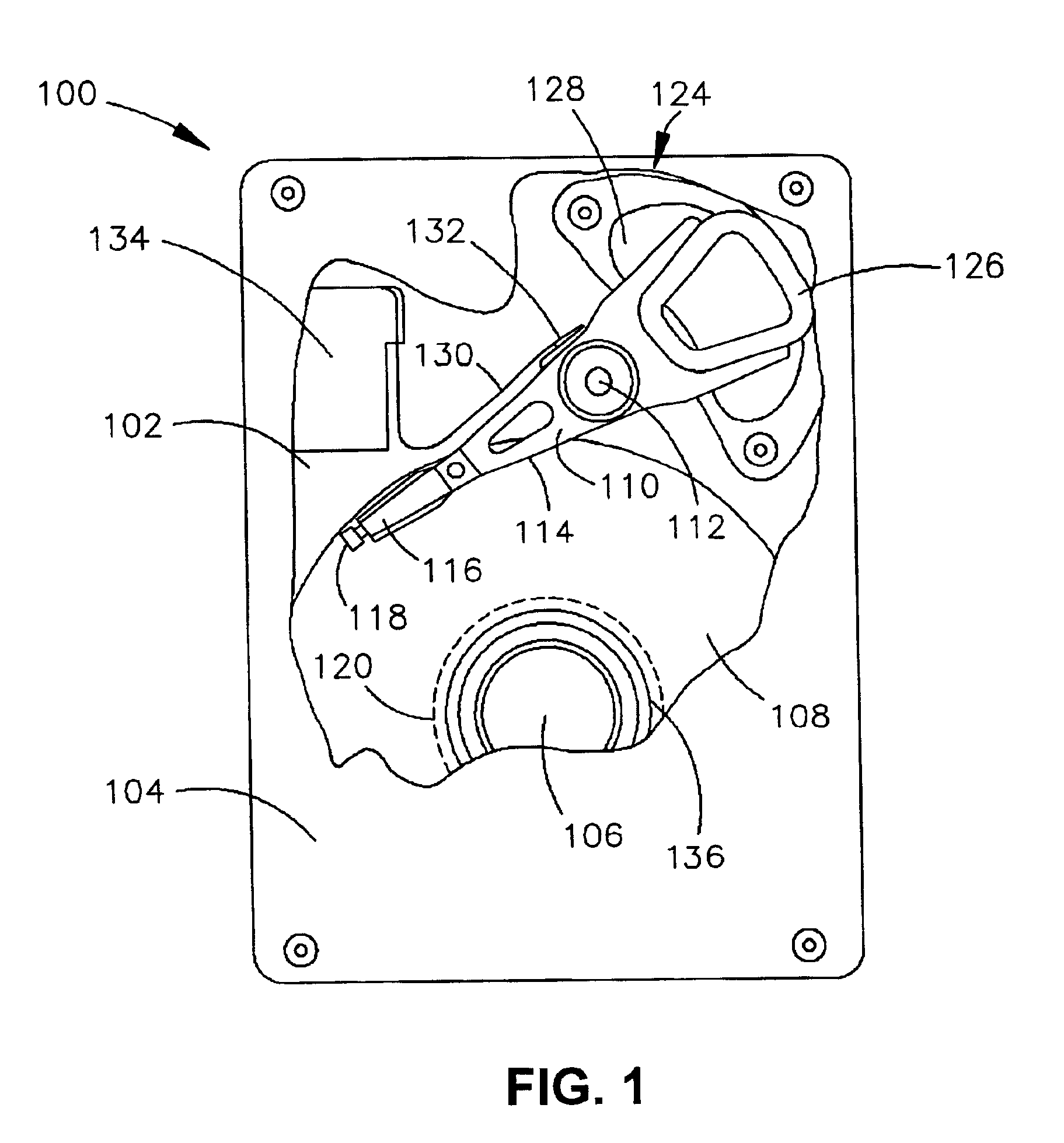

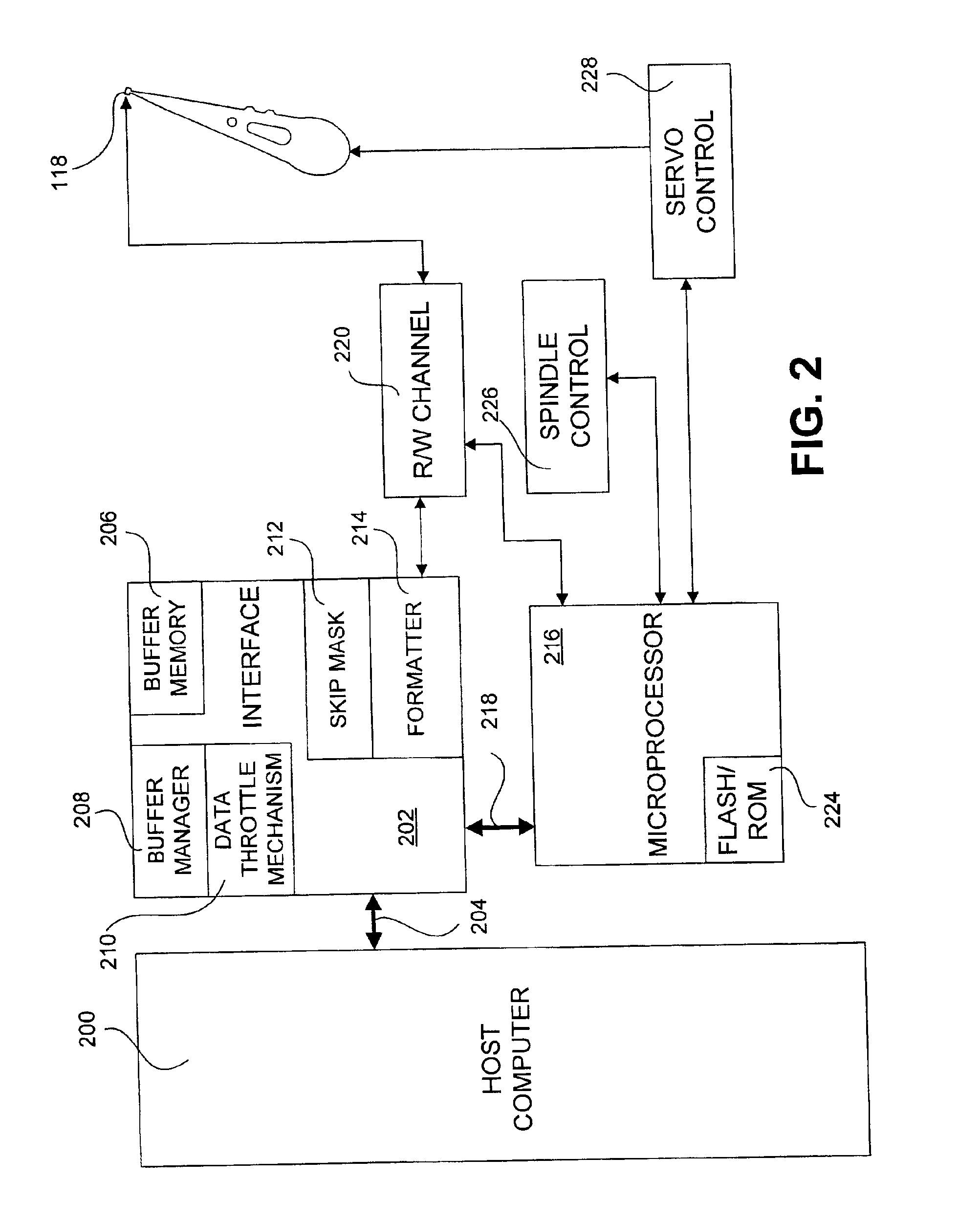

InactiveUS6862151B2Prevents overrun and underrun conditionInput/output to record carriersFilamentary/web record carriersData limitationsData transmission

A procedure for reading data stored on a data storage disc in a disc drive is disclosed. The procedure involves reading data from one or more sectors on the data storage disc after an error occurred while initially reading the sector(s) pursuant to a read command issued by a host computer. During the initial read, the procedure logs information pertaining to the sector(s) on the disc where an error occurred. The logged information is then used during the procedure to retrieve data from the sector(s) in a single revolution of the disc. The procedure uses a skip mask, a vector buffer management list and a data throttling mechanism to administer a transfer of data from a disc to a host computer via a data buffer.

Owner:SEAGATE TECH LLC

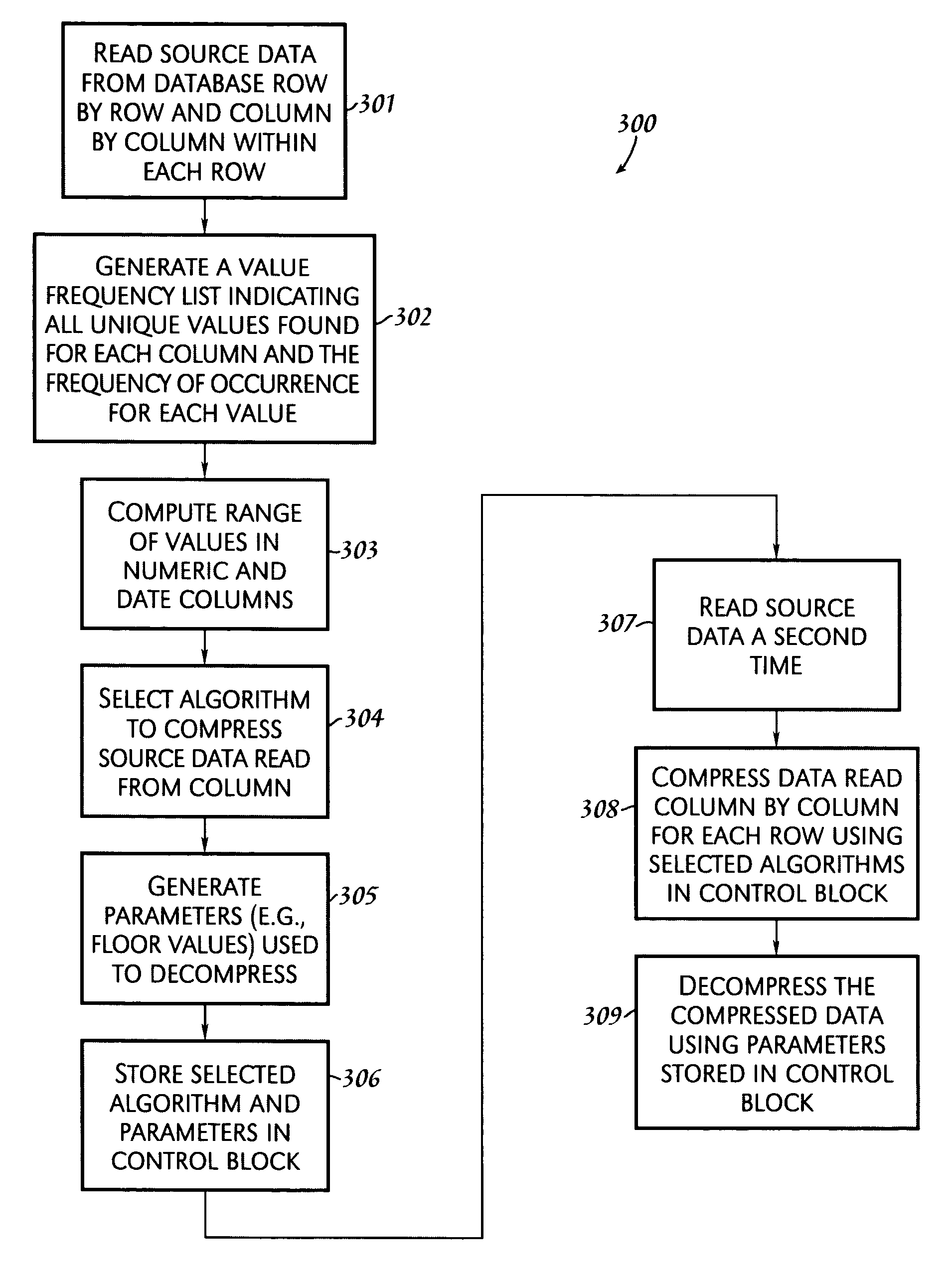

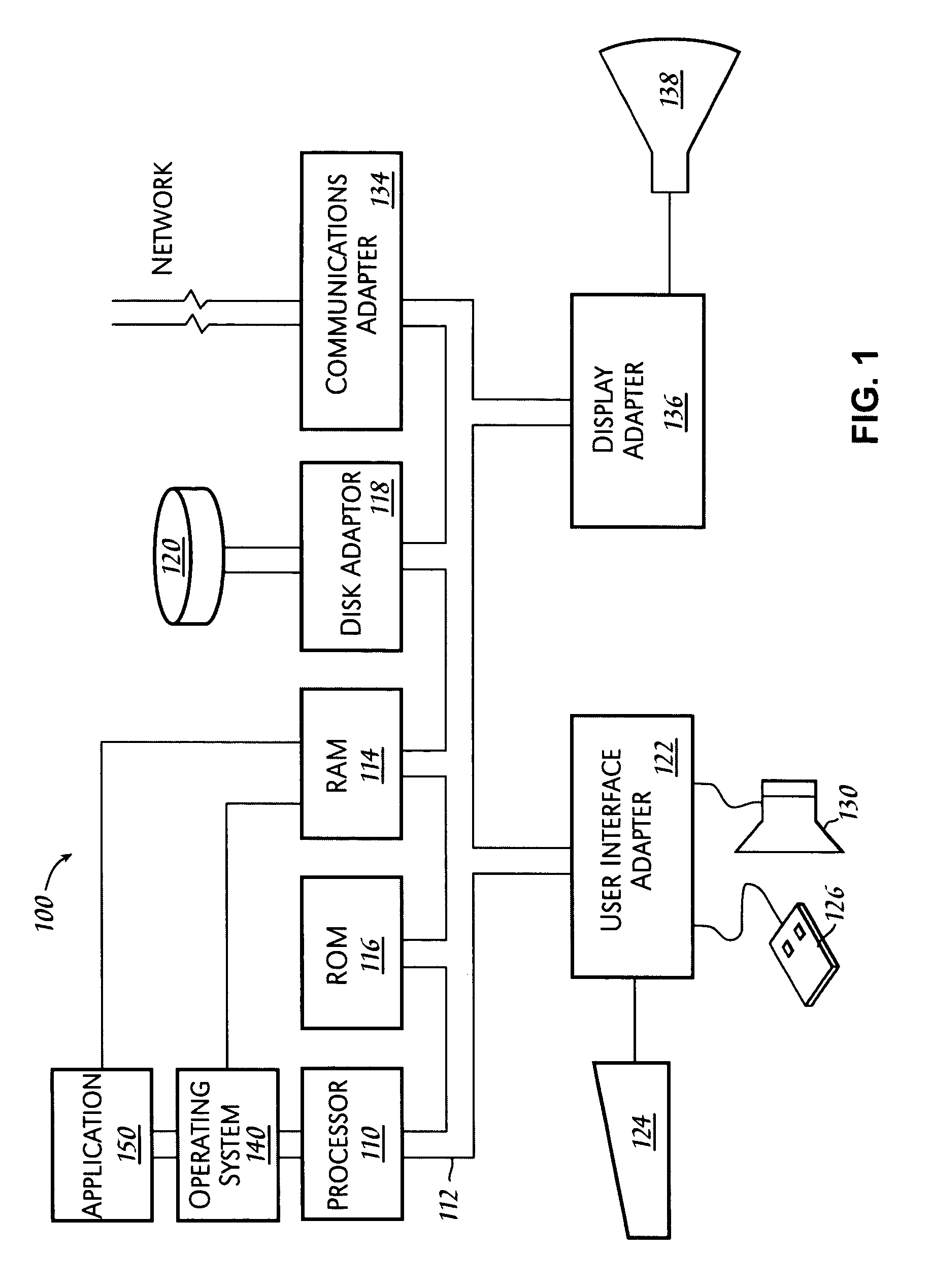

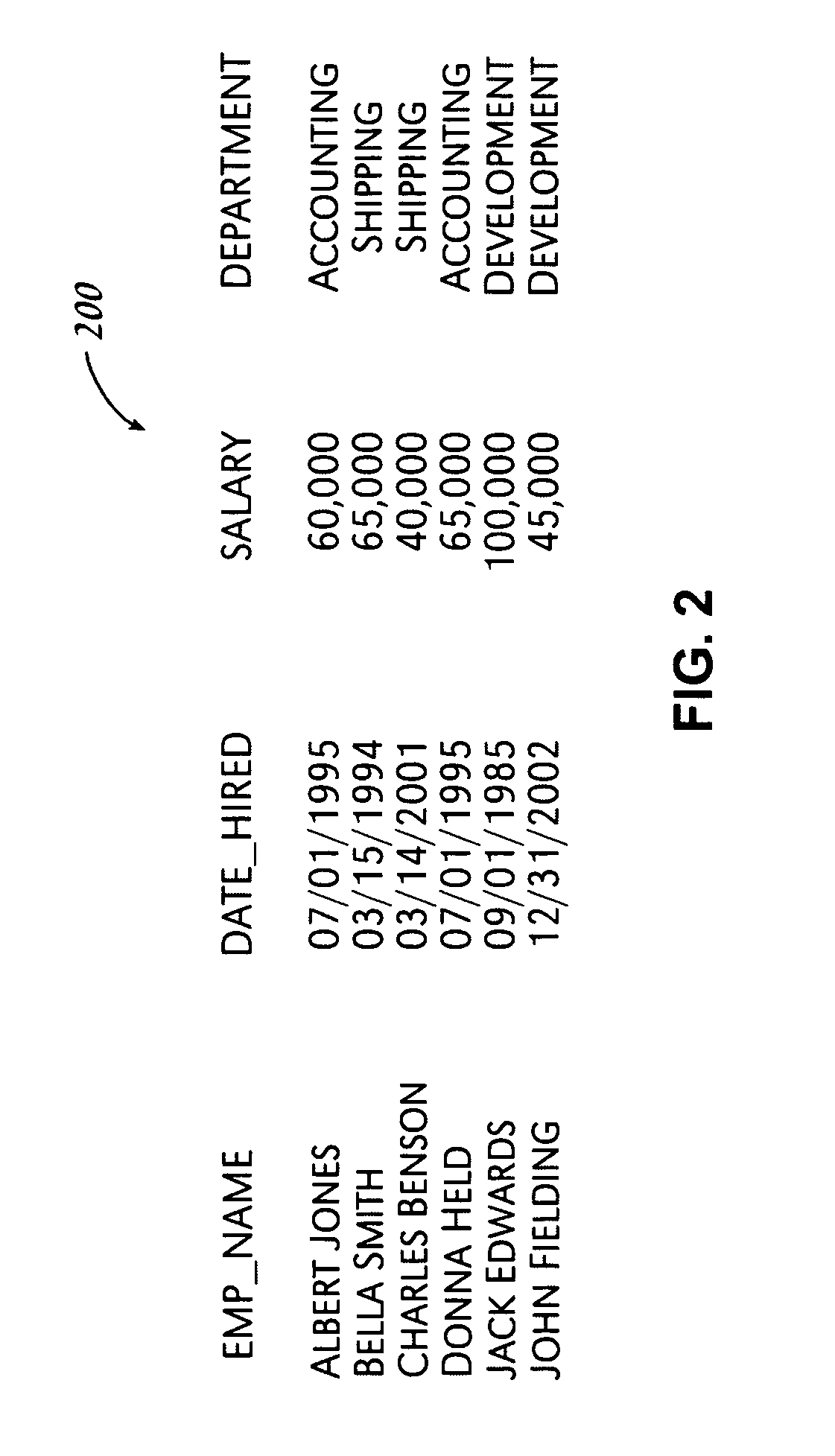

Selecting various algorithms to compress columns of analytic data in a read-only relational database in a manner that allows decompression of the compressed data using minimal system resources

InactiveUS7590641B1Digital data processing detailsRelational databasesAnalysis dataRelational database

A method, computer program product and system for balancing compression efficiency against access performance. Source data is read from a database row by row and column by column within each row. Algorithm(s) are selected to compress the data read for each column. Algorithms are selected in a manner that closely maximizes the amount of data stored in a given amount of disk space but requires minimal system resources to decompress the compressed data. These algorithms are stored in a control block. Further, parameters that allow the read data to be stored in a compressed manner efficiently are stored in the control block. Upon a second reading of the source data, data is compressed column by column using the appropriate algorithms and parameters. The compressed data may then be decompressed using the appropriate algorithms and parameters. In this manner, a better balance may be realized between compression efficiency and access performance.

Owner:QD TECH

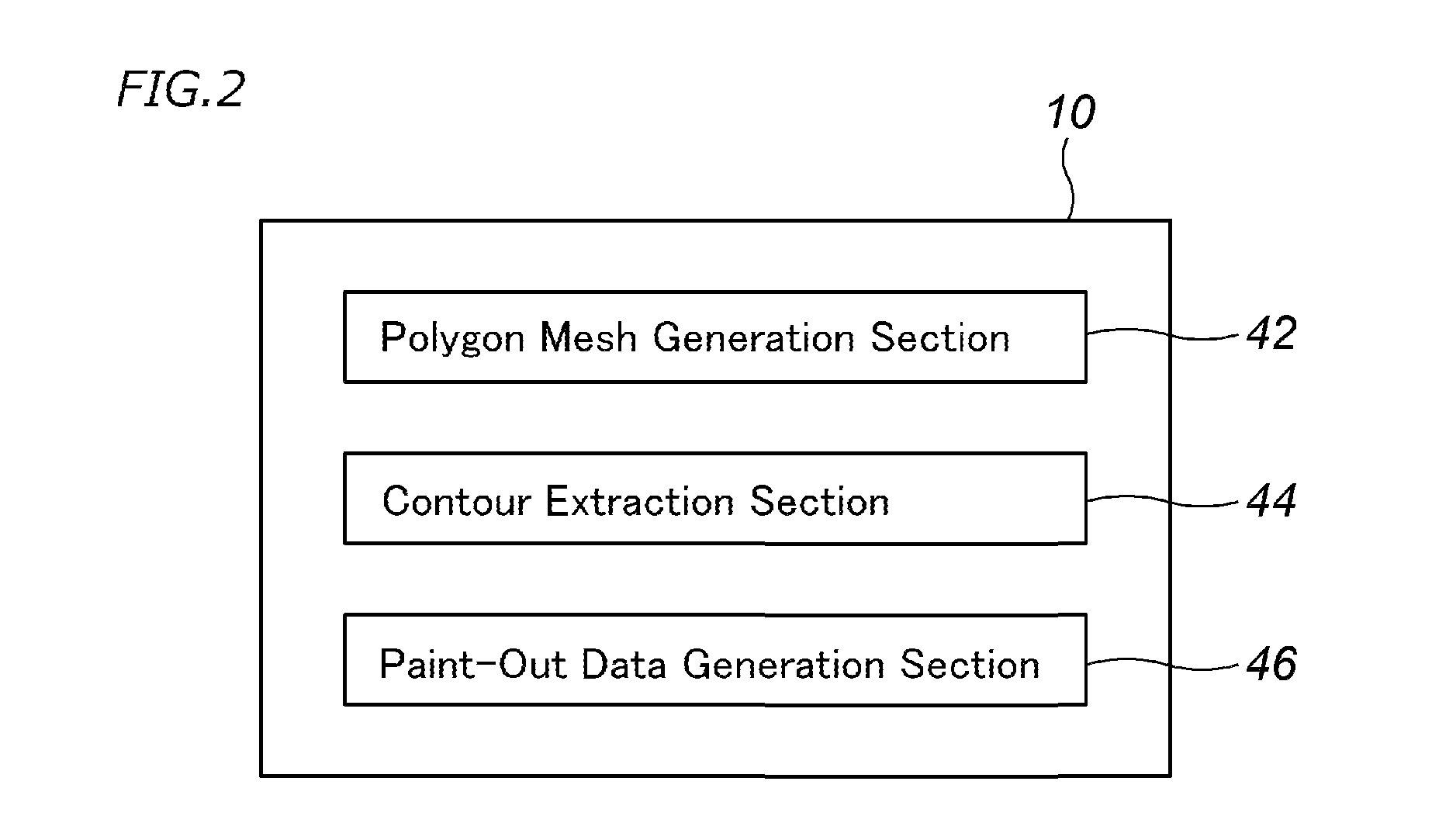

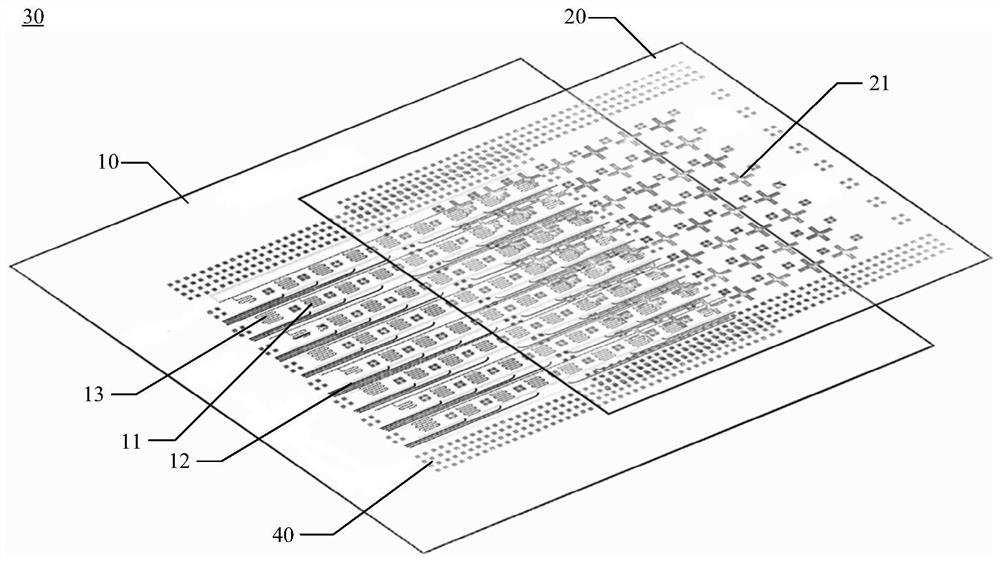

Slice data generation device, slice data generation method, and non-transitory computer-readable storage medium storing computer program that causes computer to act as slice data generation device or to execute slice data generation method

A slice data generation device generates slice data representing a cross-section obtained as a result of cutting a three-dimensional model and includes a reading section that reads information on a polygon mesh, a change section that changes phase information on the read polygon mesh such that a contour polyline that represents a contour obtained as a result of slicing the polygon mesh read by the reading section into round slices is capable of being acquired, a correction section that acquires the contour polyline from the polygon mesh, the phase information on which has been changed by the change section, and corrects the acquired contour polyline such that an area inside the acquired contour polyline is capable of being painted out; and a paint-out data generation section that paints out the area inside the contour polyline corrected by the correction section.

Owner:ROLAND DG CORP

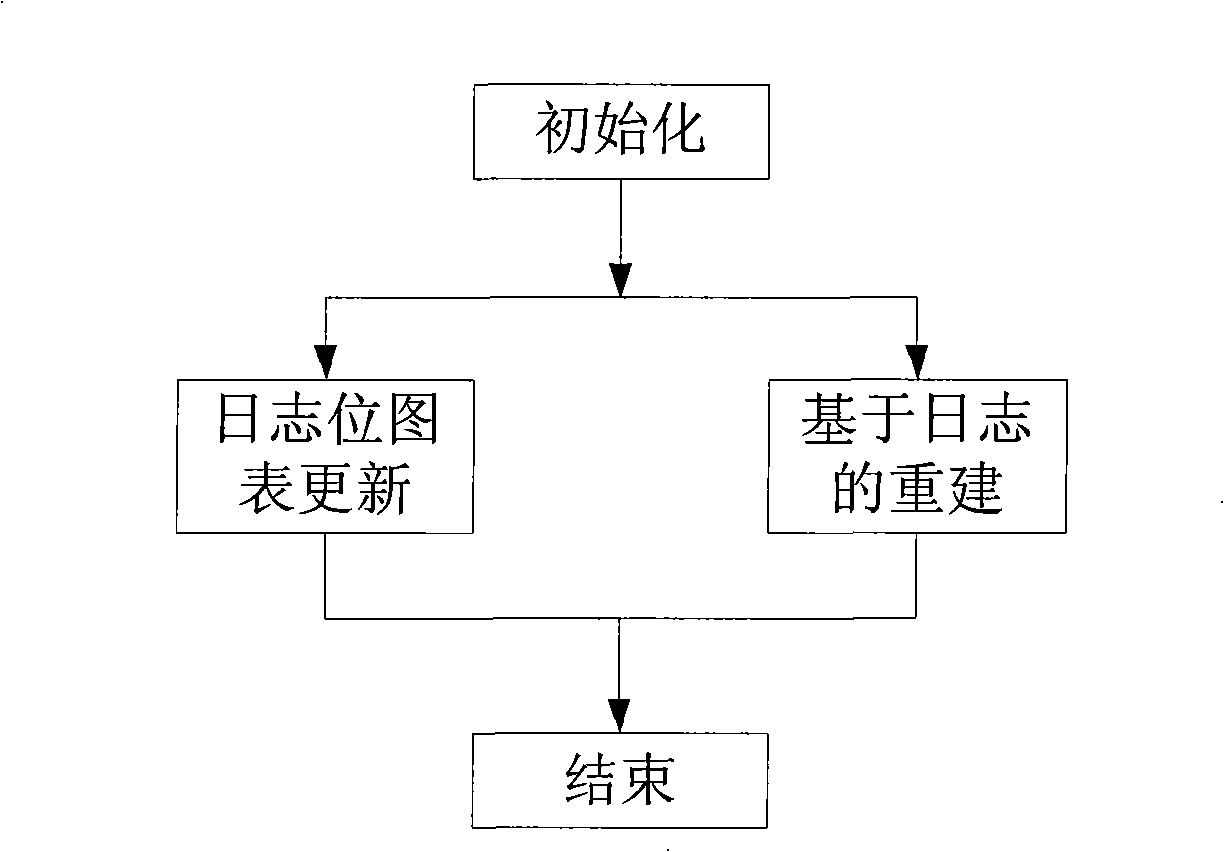

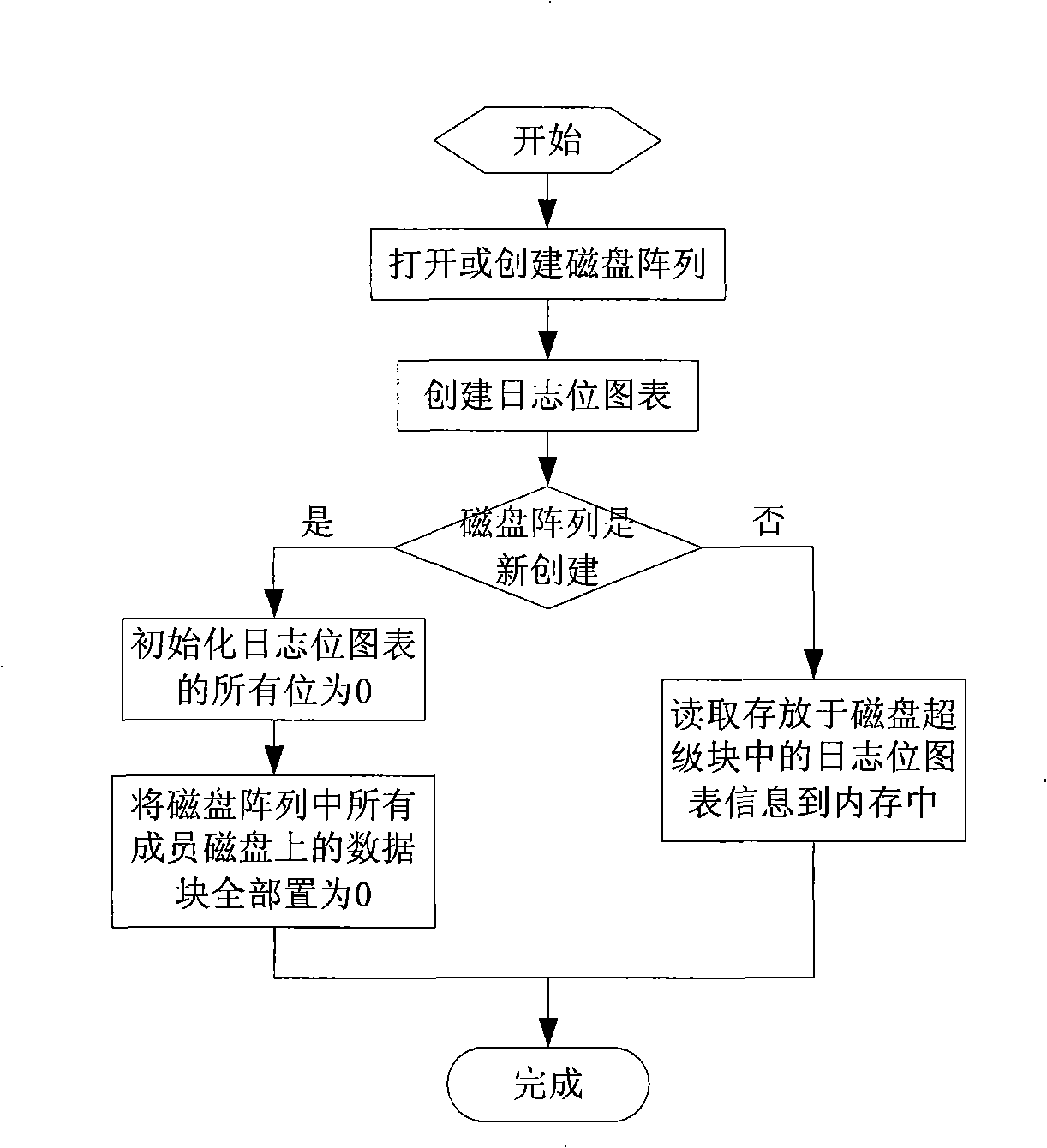

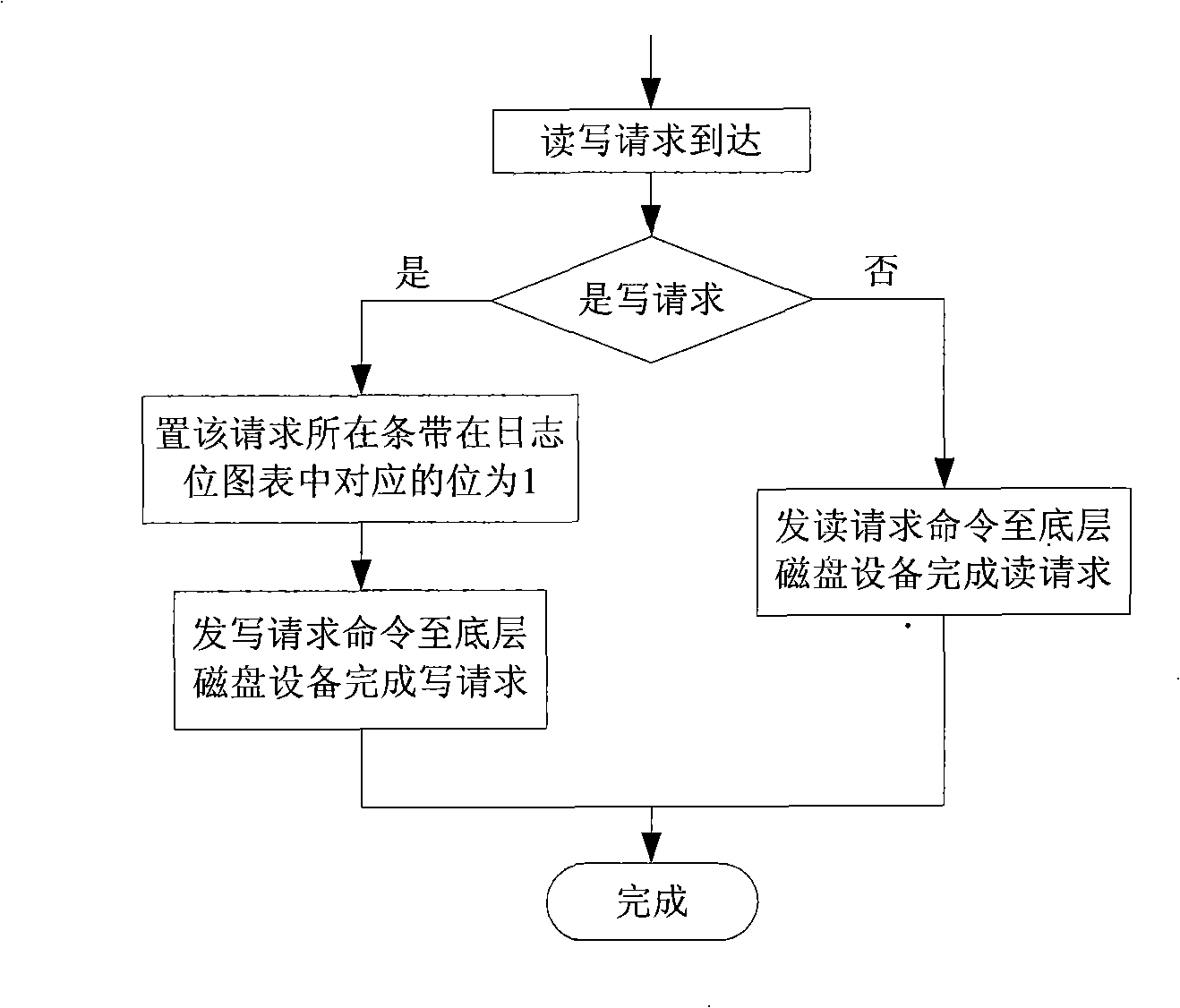

Method for rebuilding data of magnetic disk array

InactiveCN101329641AImprove performanceImprove usabilityRedundant operation error correctionVisit timeReconstruction method

The invention relates to a disk array data reconstruction method which pertains to a computer data storage method and solves the problem that the existing disk array data reconstruction method takes too much time and affects the reading and writing performances and reliability of a storage system. A disk array of the invention is provided with a main control module, reading and writing processing modules and a reconstruction module and comprises the steps of initialization, diary pot diagram update, reconstruction based on diaries and finishing. The method instructs data reconstruction process by the real-time monitoring of disk space using status of the disk array; when space that is not accessed is reconstructed, the only requirement is to write 0 in all corresponding data blocks newly added into a disk, thus greatly reducing physical disk visiting time brought by reconstruction, increasing reconstruction speed and reducing the response time of user access; the reconstruction method does not change the reconstruction procedure or the distribution manner of disk array data, can conveniently optimize various traditional disk array data reconstruction methods and is applicable to the construction of storage systems with high performance, high usability and high reliability.

Owner:HUAZHONG UNIV OF SCI & TECH

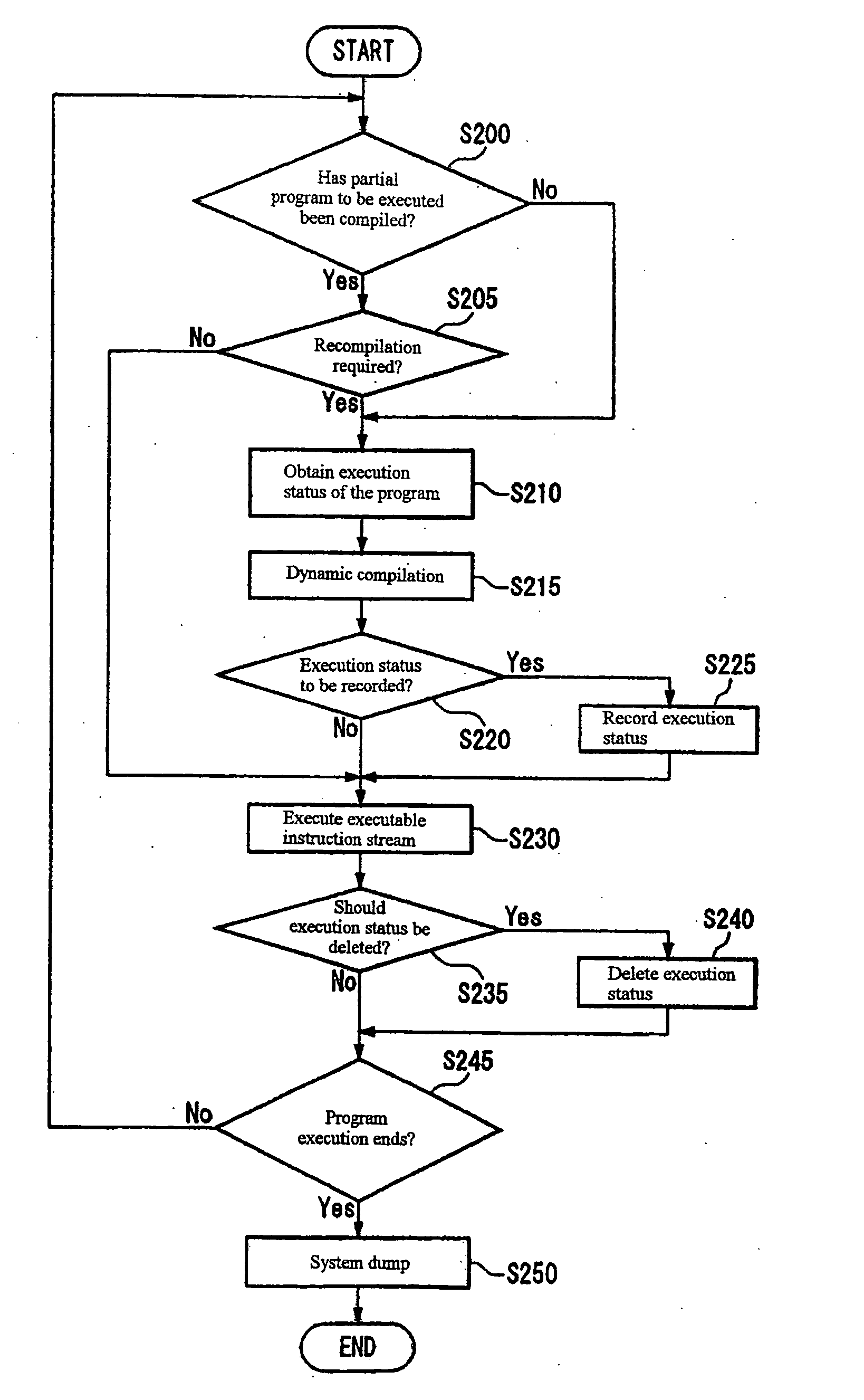

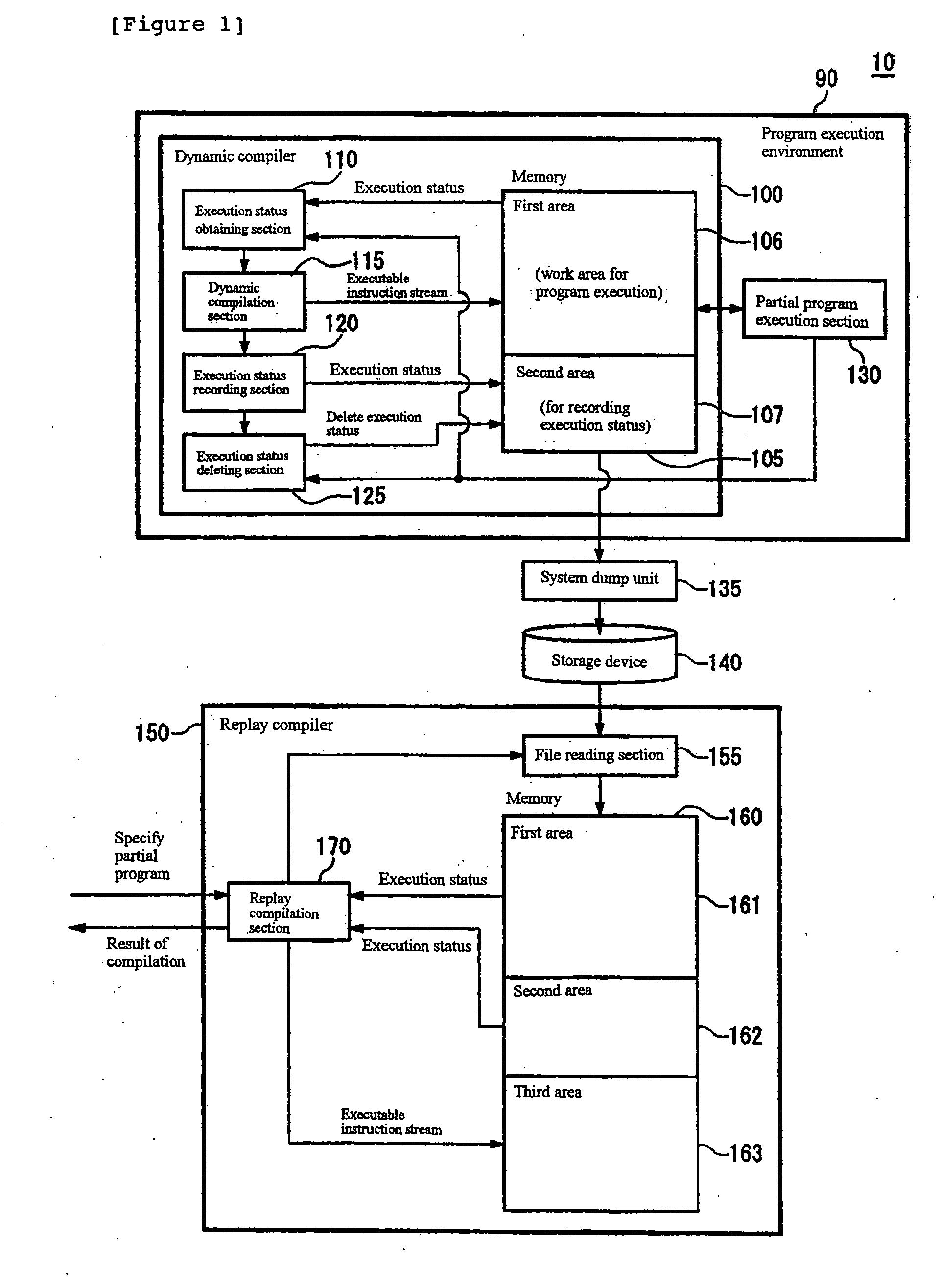

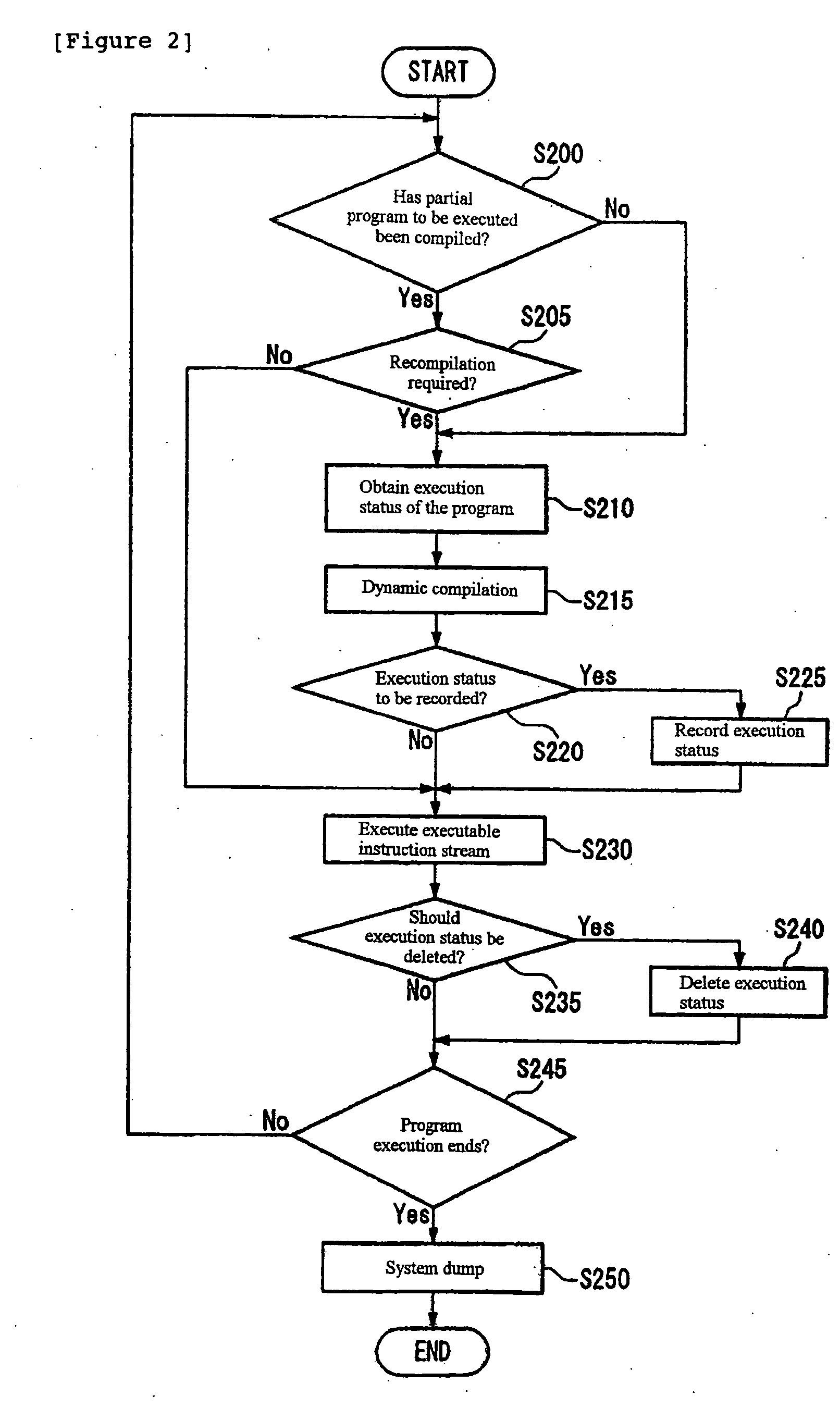

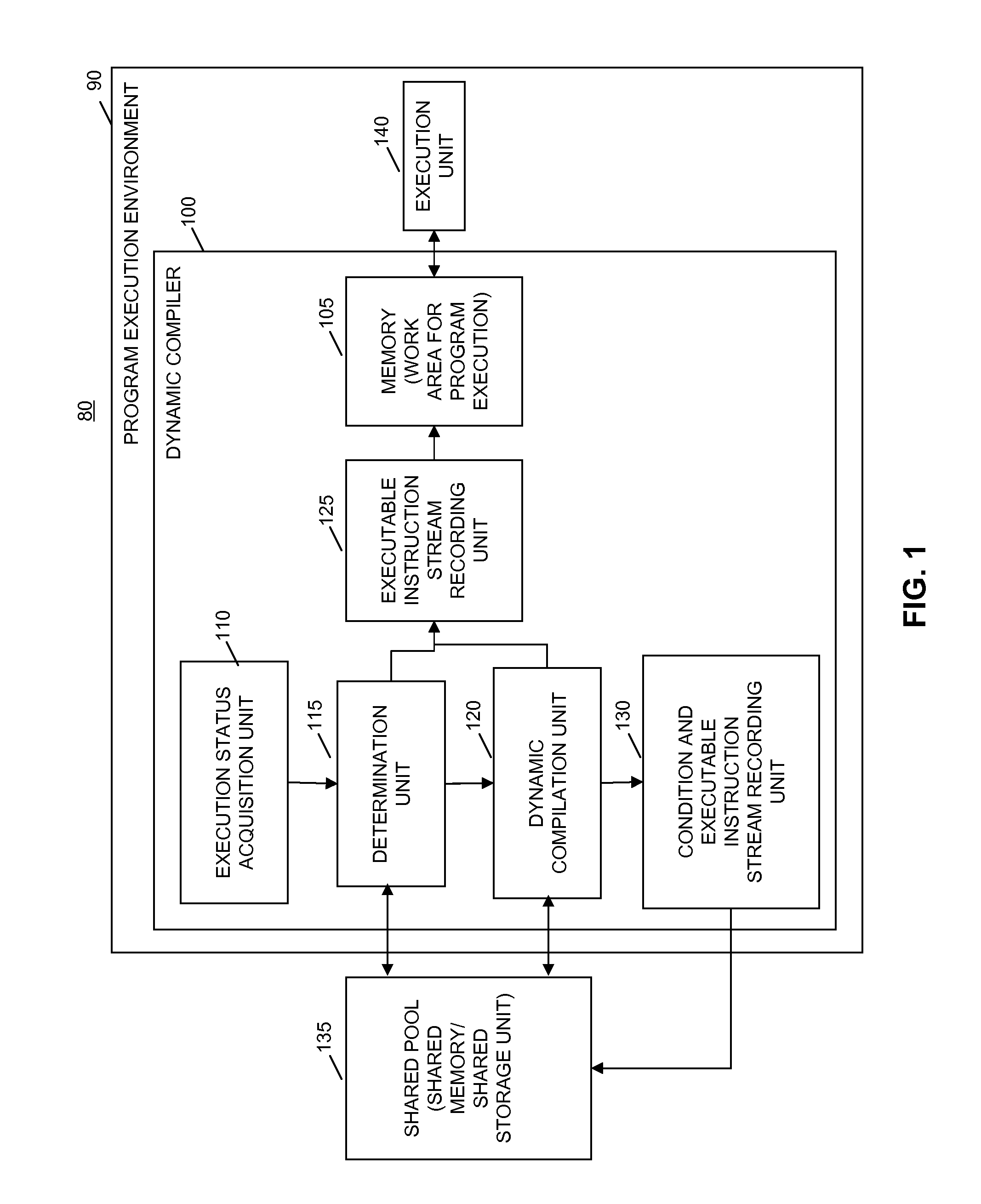

Compiler, dynamic compiler, and replay compiler

InactiveUS20050177821A1Easy to debugError detection/correctionProgram controlDynamic compilationInstruction stream

The same executable instruction stream as an executable instruction stream generated by a dynamic compiler is reproduced to facilitate debugging of the dynamic compiler. Provides compiler program for computer functioning as: an execution status obtaining section for obtaining an execution status of the program; a dynamic compilation section for compiling one of the partial programs to be executed during execution of the program; an execution status recording section for recording the execution status in a memory area allocated on a memory of the computer; a file reading section for reading a file containing contents of the memory area allocated on the memory; and a replay compilation section for compiling the one partial program on the basis of the execution status obtained from the file to generate the same executable instruction stream as the executable instruction stream generated by the dynamic compilation section during the execution of the program.

Owner:IBM CORP

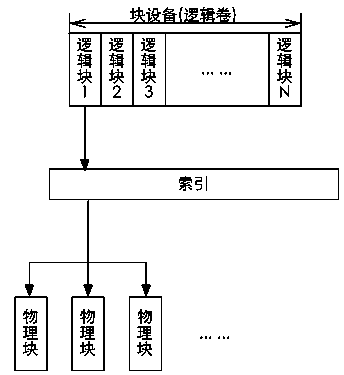

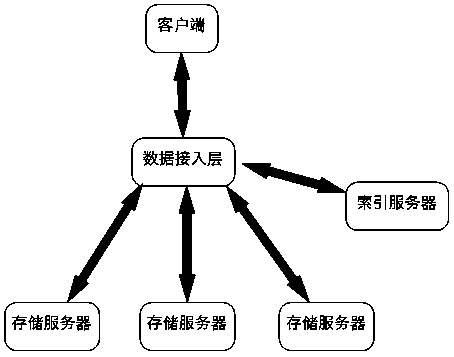

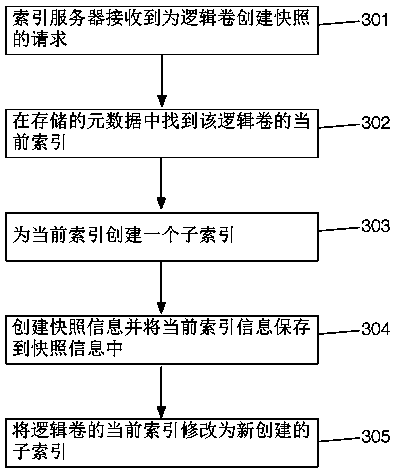

Distributed storage method and system of block device

ActiveCN103870202AHighly reliable dataAvoid single point of failure problemsInput/output to record carriersProtocol processingIndexing Service

The invention is applicable to the storage field, particularly relates to distributed storage systems and discloses a distributed storage method and system of a block device. The method comprises defining the storage space of the block device as a logical volume and segmenting the logical volume into N logical blocks in a fixed size; actually storing the logical blocks in a plurality of physical storages, and associating the mapping relations of the logical blocks and a plurality of corresponding physical storage addresses through indexing. The system comprises a data access layer, an index server and a storage server, wherein the data access layer processes a read-write request of the block device on the basis of an iSCSI (Internet small computer system interface) protocol; after analyzing the protocol, the data access layer obtains the actual physical storage position of the logical block involved in the request from the index server; after receiving the request, the index server queries associated indexes to find a corresponding storage server and feeds information back to the data access layer; after receiving information fed back by the index server, the data access layer accesses the storage server to complete subsequent data reading and writing tasks.

Owner:UCLOUD TECH CO LTD

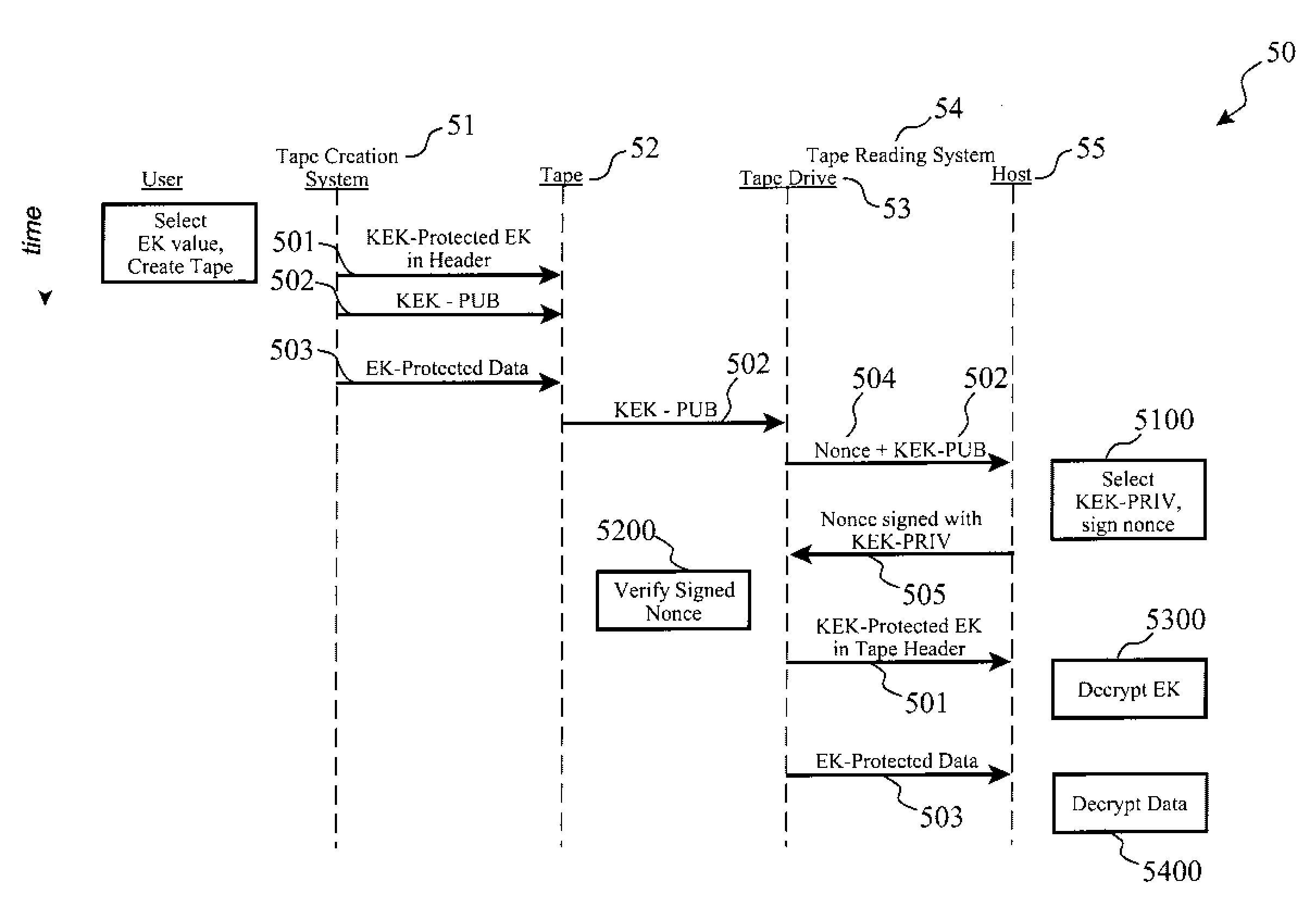

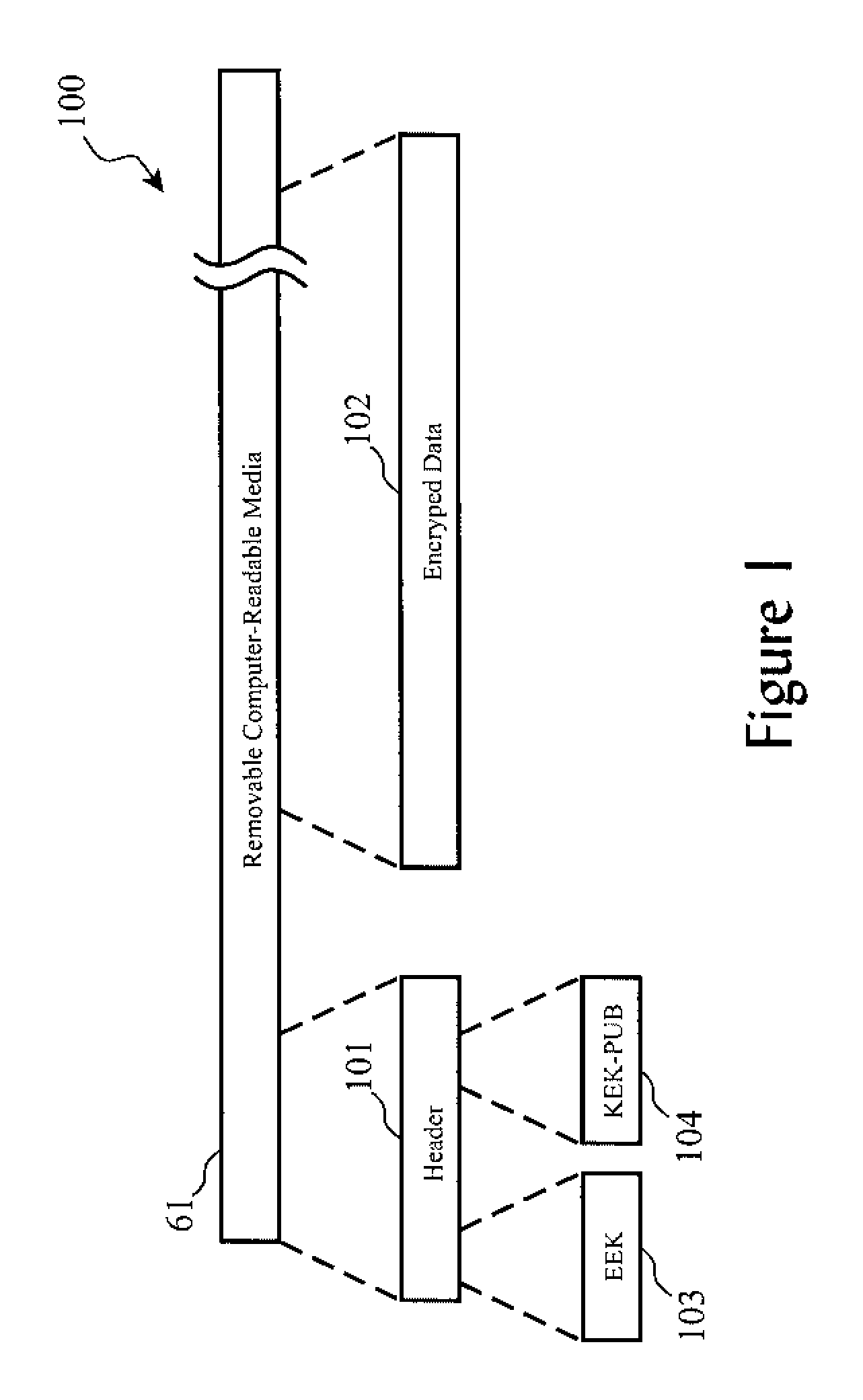

Encrypted Tape Access Control via Challenge-Response Protocol

InactiveUS20080123863A1Easy to useDifficult to automateKey distribution for secure communicationPublic key for secure communicationMagnetic tapeKey Wrap

Access to encrypted data on a removable computer media such as a computer tape is controlled via a uniquely-structured header on the medium having a symmetrical key wrapped by asymmetrical encryption plus a public key associated with the asymmetrical encryption. The data on the medium is encrypted using the symmetrical key. Prior to automated reading of the data by a reader, a challenge is issued to a host system including the public key and preferably a nonce value. The host responds by signing the nonce using a private key associated with the public key in order to prove it has rights to decrypt the data. The symmetrical key is unwrapped using the private key, and finally the unwrapped symmetrical key is used to decrypt the data on the medium, thereby allowing automated reading of the tape data without the need or risk of two administrators sharing a symmetrical key value.

Owner:IBM CORP

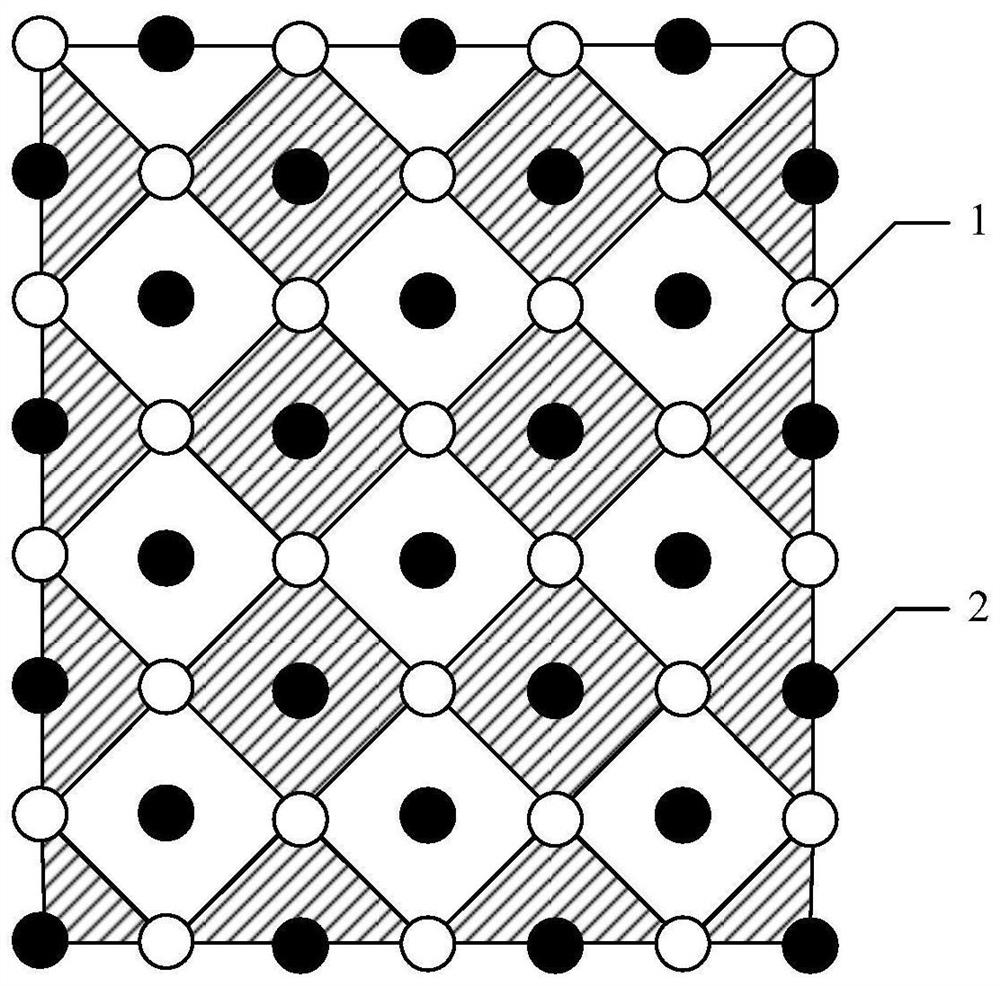

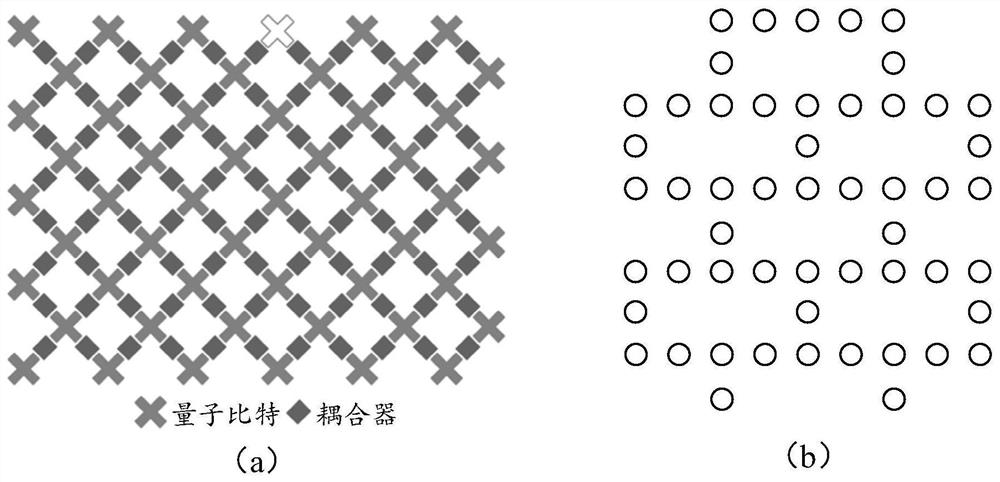

Quantum chip, quantum processor and quantum computer

ActiveCN111967603AImprove adaptabilityImprove coherenceQuantum computersNanoinformaticsQuantum technologyBit array

Owner:TENCENT TECH (SHENZHEN) CO LTD

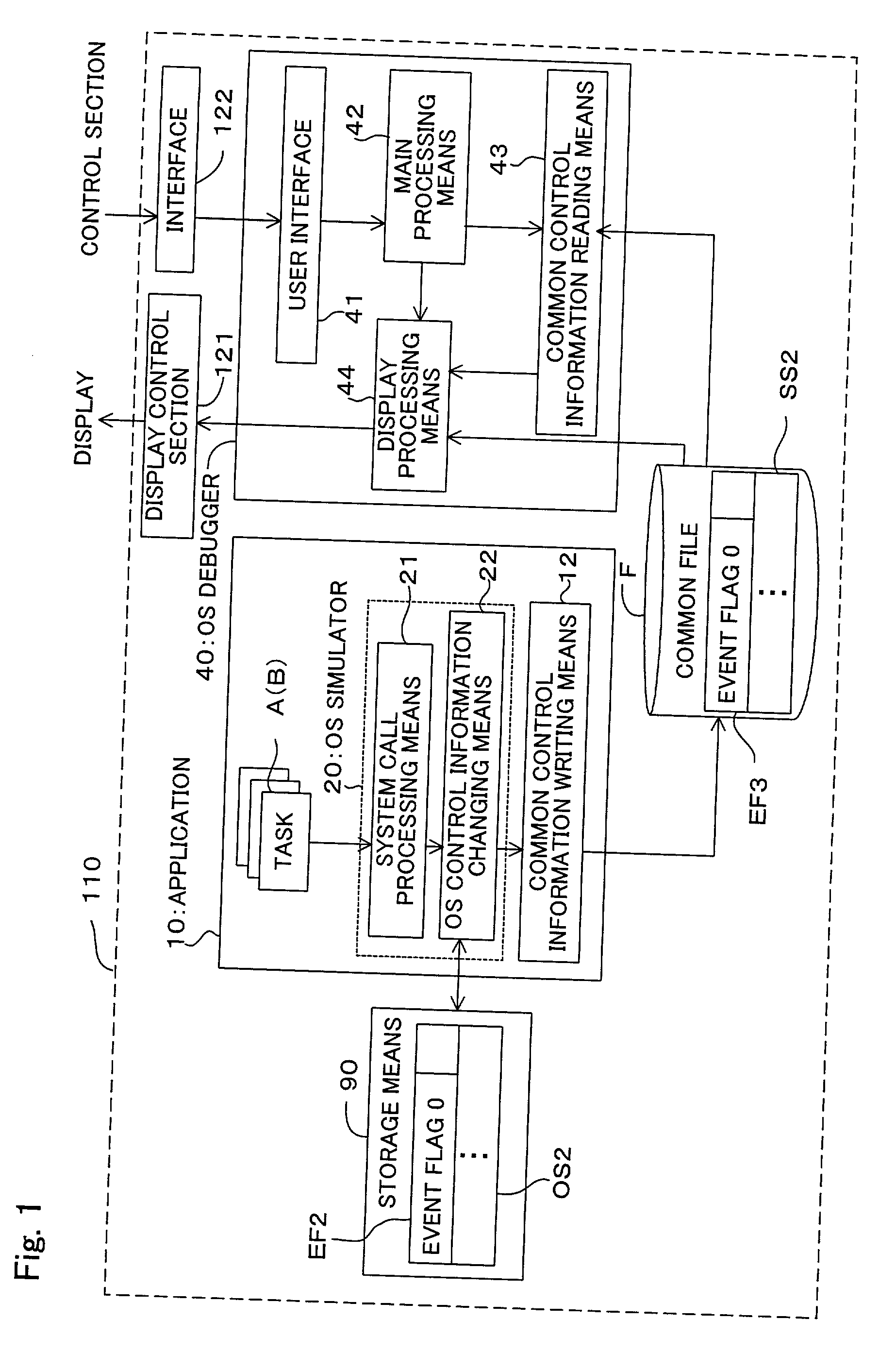

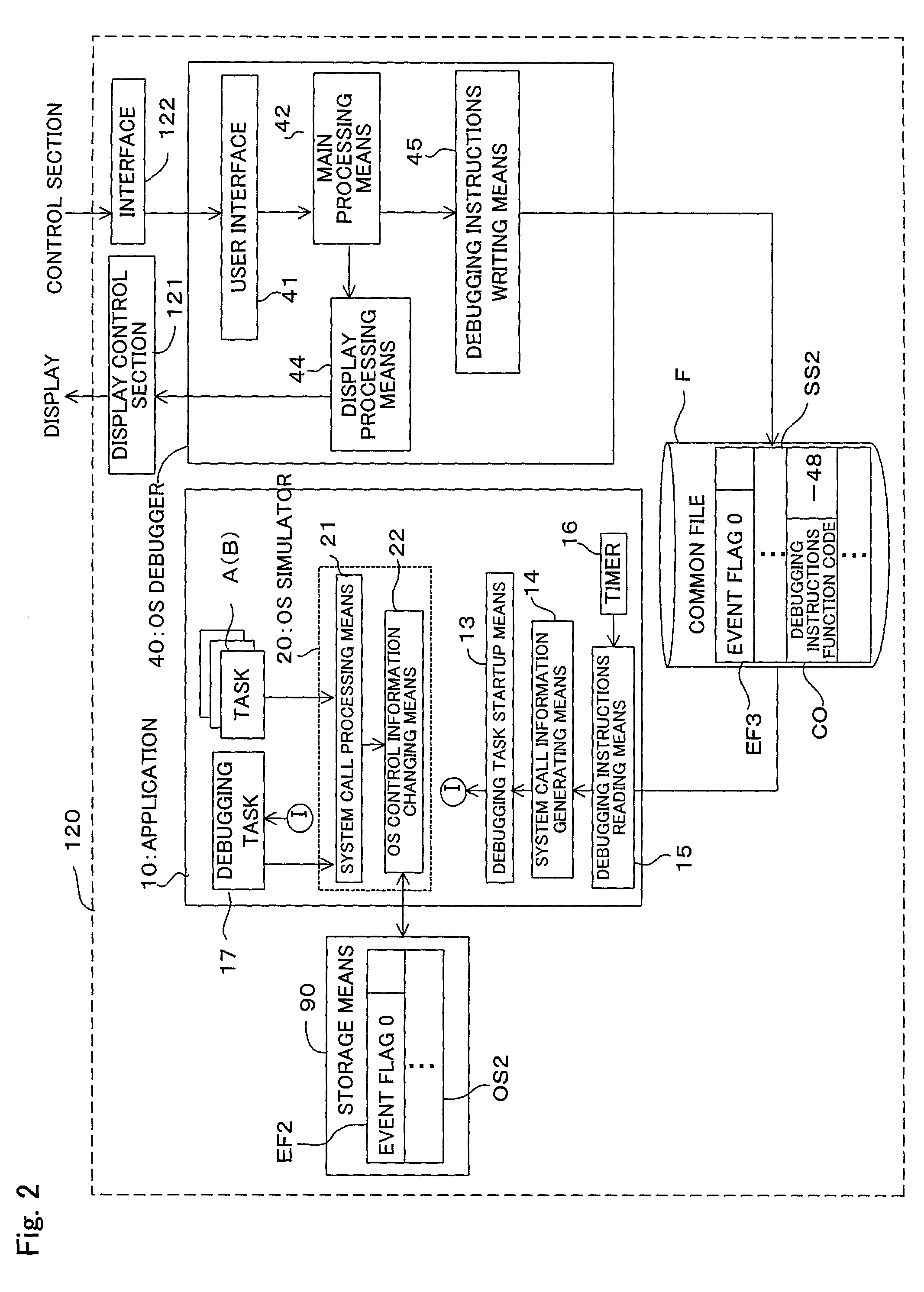

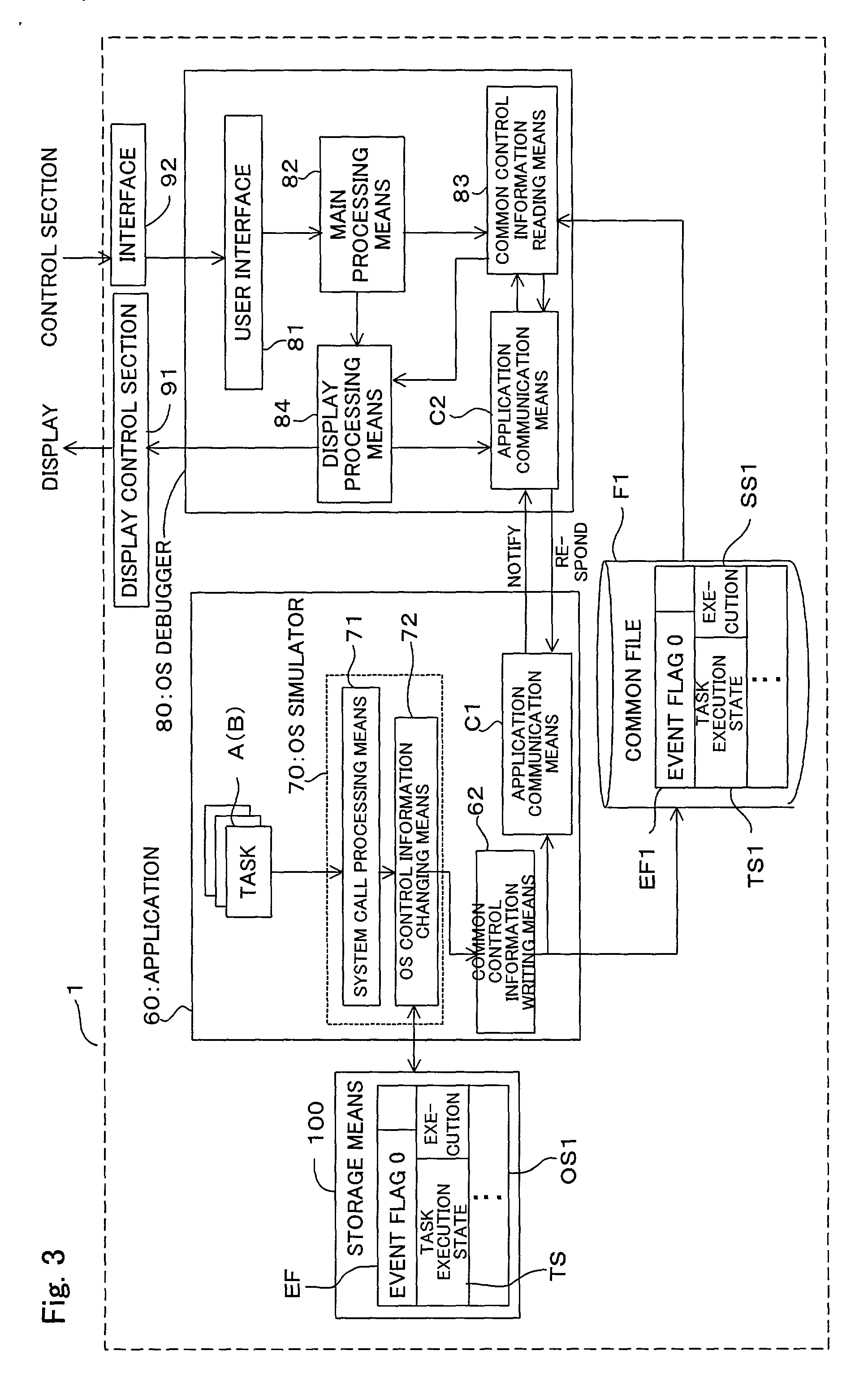

Debugging supporting apparatus, debugging supporting method and recording medium readable by computer with its programs recorded thereon

InactiveUS20010027387A1Efficient debugEfficient debuggingSoftware testing/debuggingProgram controlApplication softwareDebugger

Disclosed are a debugging supporting apparatus, a debugging supporting method and its recording medium so constituted that even if an application developed in a simulation environment by OS simulator stops, OS control information can be referred to at that moment. The debugging supporting apparatus comprises a common file that is shared between the application and the OS debugger and which records common control information including the same data as item forming OS control information, writing means for writing specific item of the OS control information stored in the storage means on the common file as common control information, and reading means for reading out the common control information stored in the common file.

Owner:PANASONIC CORP

Information search system, method and program

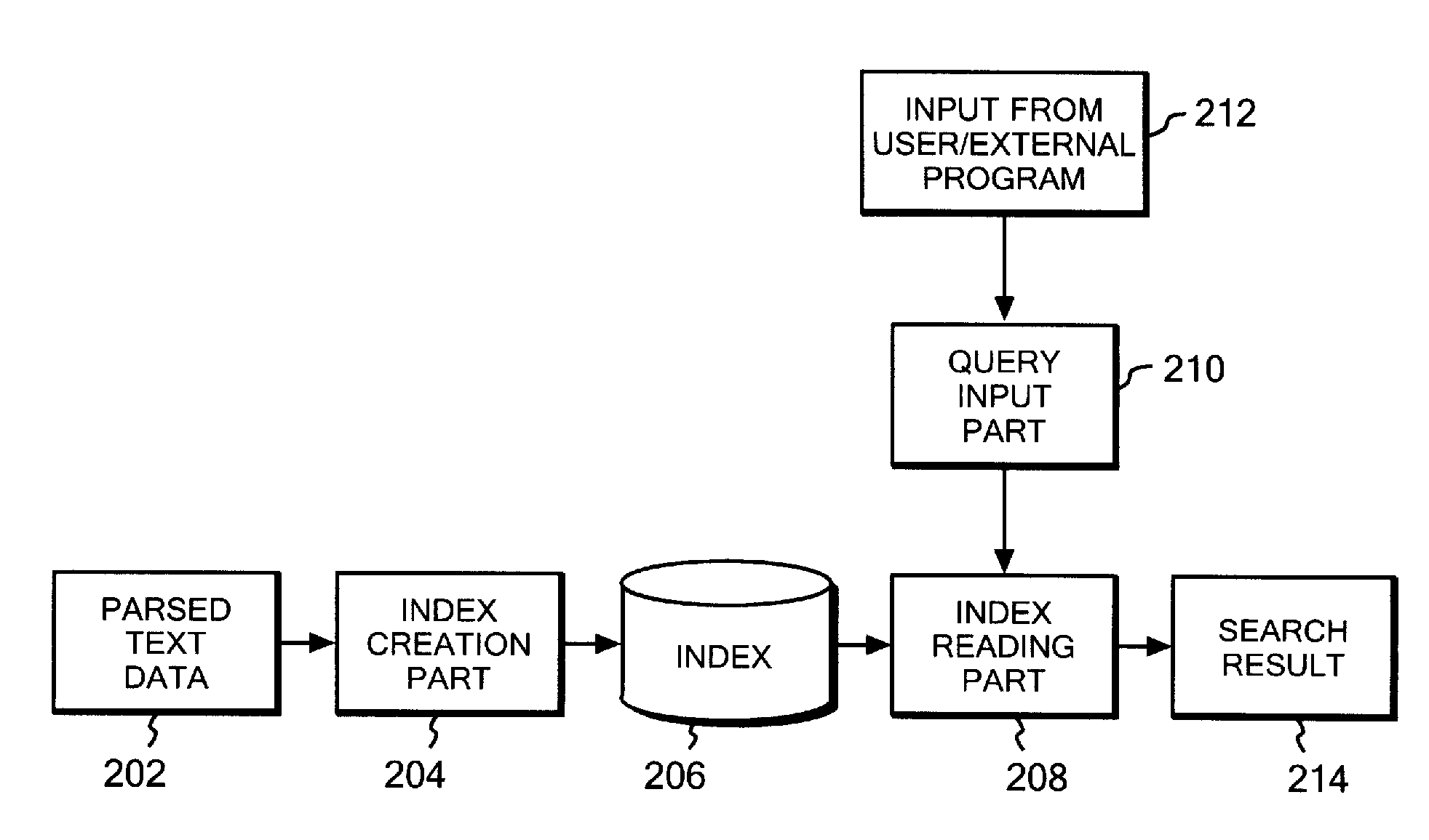

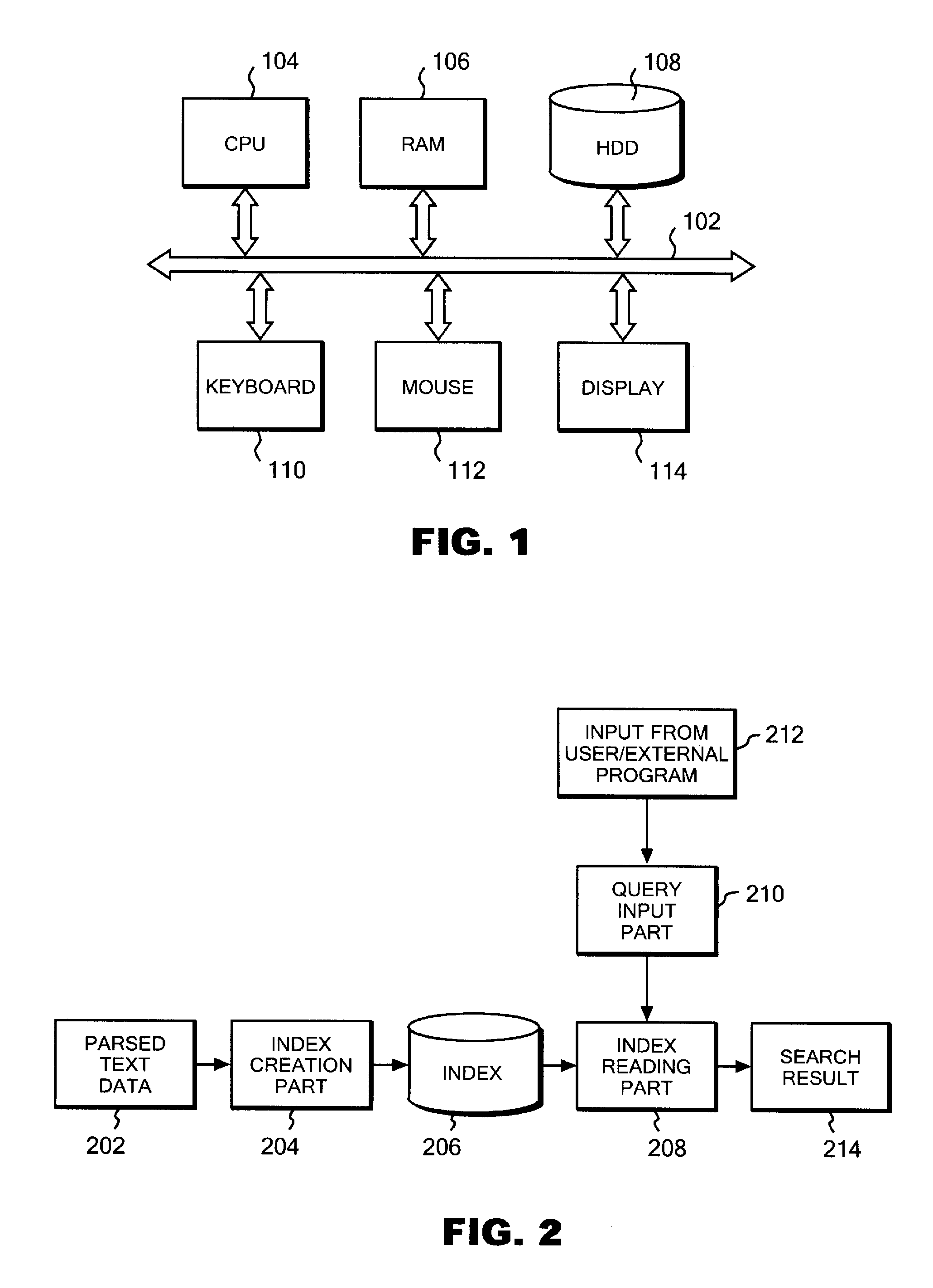

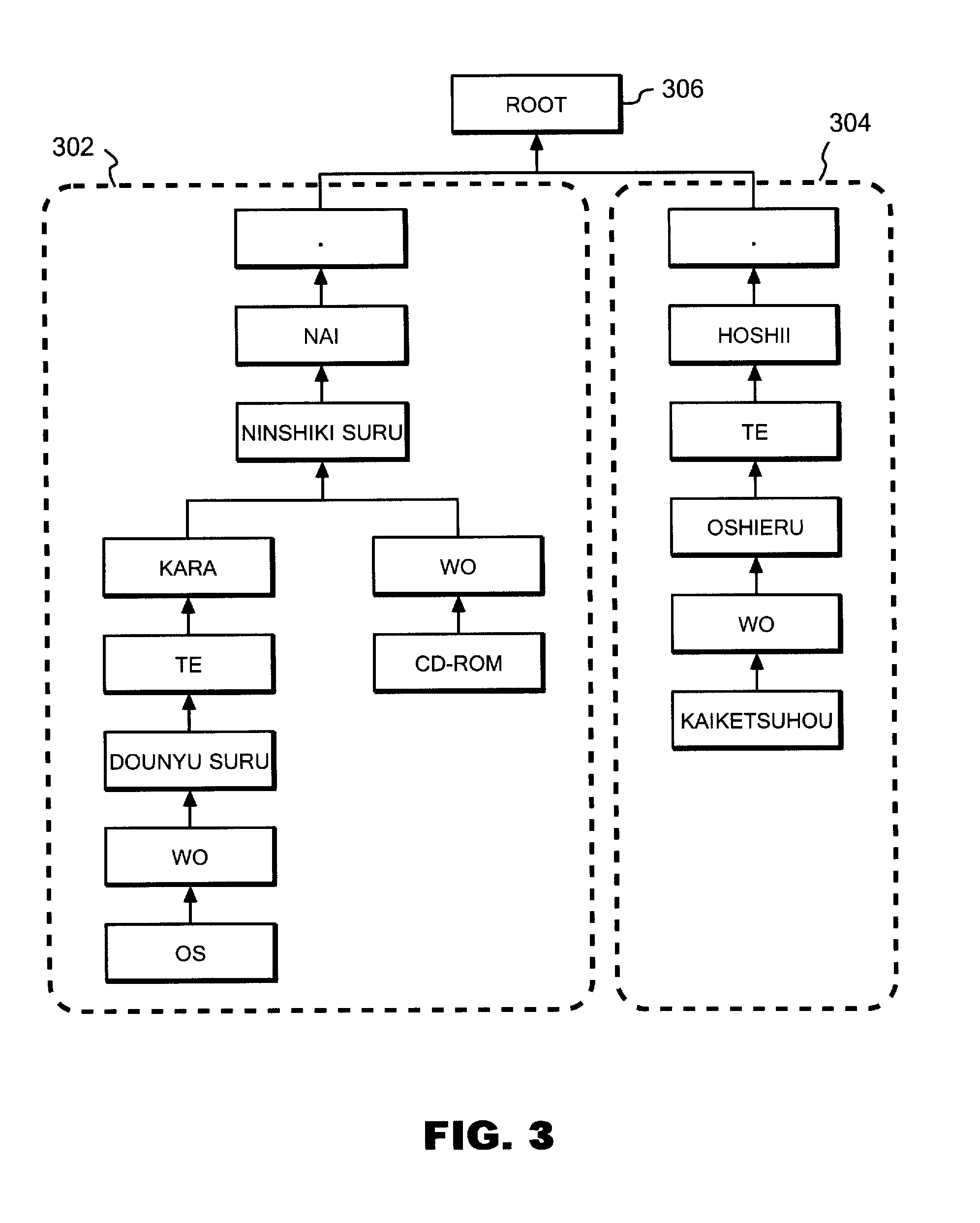

InactiveUS20090222407A1Increase speedHigh-speed searchDigital data information retrievalDigital data processing detailsPattern matchingEngineering

A system, method and computer program product for searching at high speed for documents matching a dependency pattern from document data containing a large volume of text documents. The system includes a storage device for storing, index storage means for storing in the storage device occurrence information, receiving means for receiving information, reading means for reading from the index storage means, and searching means for comparing occurrence information. The method and computer program product include the steps of storing in the storage device, receiving information, reading from the storage device, comparing occurrence information, and searching. The computer program product includes instructions to execute the steps of storing each of the plurality of document data in the storage device, storing in the storage device occurrence information.

Owner:IBM CORP

Magnetic multilayer film with geometrical shape and preparation method and application thereof

ActiveCN101221849AEasy to controlEasy to driveRecord information storageMagnetic film to substrate applicationMagnetic storageRandom access memory

The invention relates to a magnetic multiplayer film with geometric shape, comprising all layers of a magnetic multiplayer film unit deposited on a substrate, wherein the cross section of the magnetic multiplayer film unit is polygonal closing ring shaped, magnetic moments or magnetic fluxes of film layers with ferromagnetism in the magnetic multiplayer film unit become in a clockwise or counter clockwise closing state; the invention also comprises a metal core arranged on the geometric center of the polygonal closed ring shaped magnetic multiplayer film, wherein the cross section of the metal core is a corresponding polygon; the invention also relates to a magnetic storage made of the magnetic multiplayer film which comprises(or does not comprise) the metal core; in the invention, the closing shape magnetic multiplayer film is prepared based on the micro processing method; the closing with(or without) metal core polygonal closing ring shaped magnetic multiplayer film is widely applicable to devices which takes the magnetic multiplayer film such as magnetic random access memory, computer magnetic reading head, magneto-dependent sensor, magnetic logic device and self-rotation transistor, etc. as the core.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

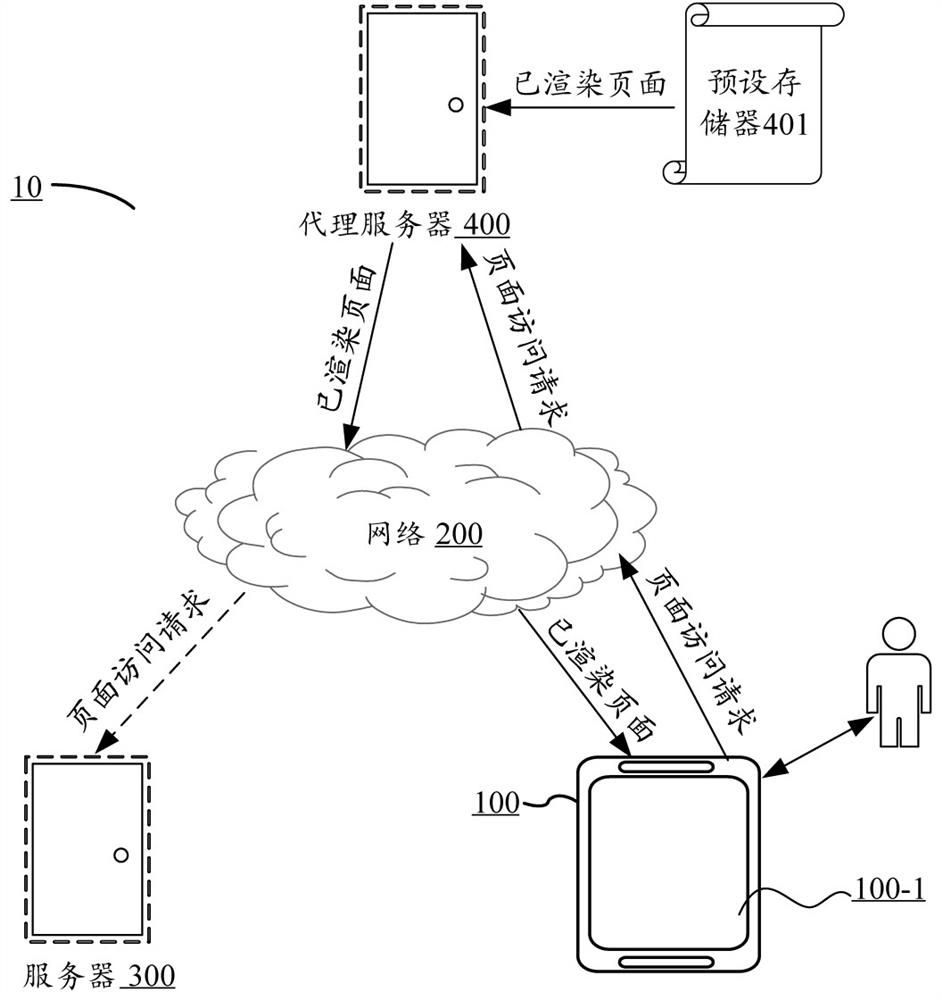

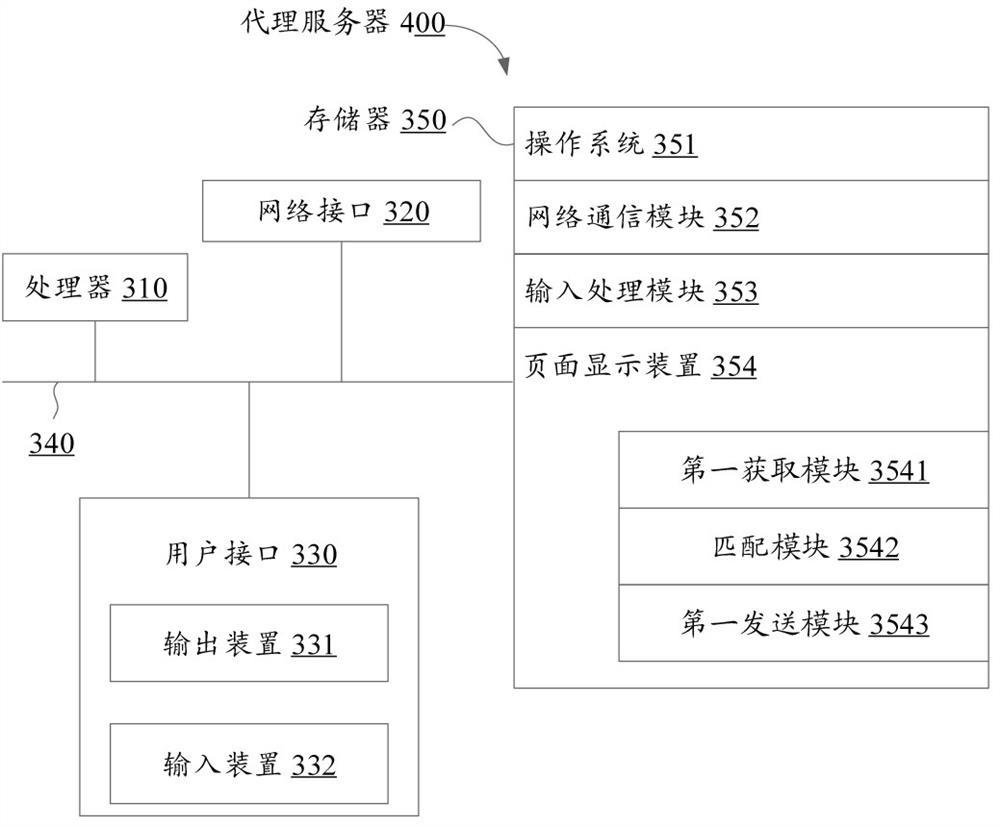

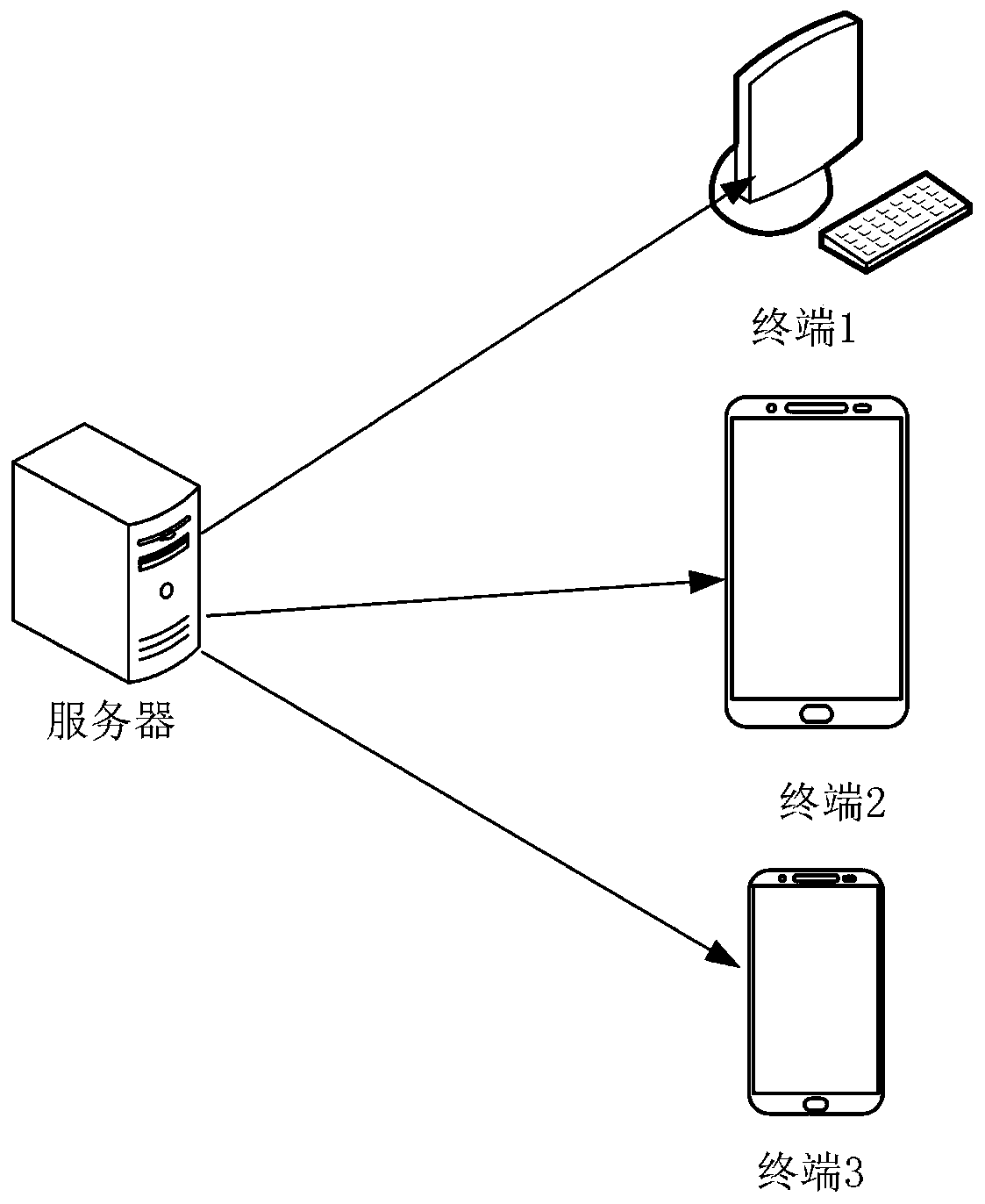

Page display method, device and equipment and computer readable storage medium

ActiveCN111708600AImprove experienceReduce readWebsite content managementExecution for user interfacesComputer hardwareEngineering

The embodiment of the invention provides a page display method, device and equipment and a computer readable storage medium, and relates to the technical field of clouds, and the method comprises thesteps: enabling a proxy server to obtain a page access request when a client sends the page access request to a server, wherein the page access request comprises a page identifier; matching a renderedpage corresponding to the page identifier in a preset memory; and taking the rendered page as an access result of the page access request, and sending the access result to the client, so as to enablethe client to display the rendered page. Through the embodiment of the invention, the reading and rendering time during page access can be greatly shortened, the white screen display time is shortened, and the user experience is improved.

Owner:TENCENT TECH (SHENZHEN) CO LTD

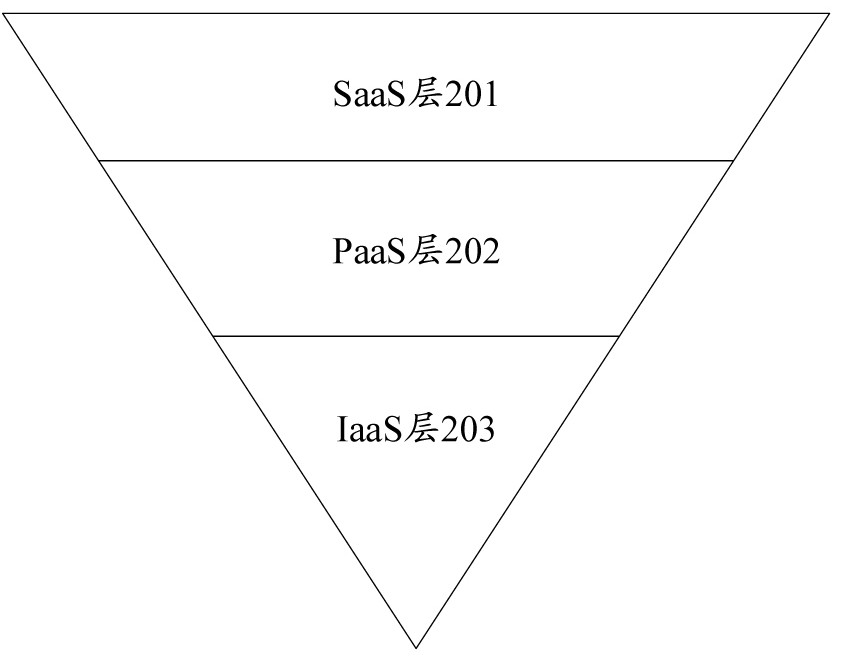

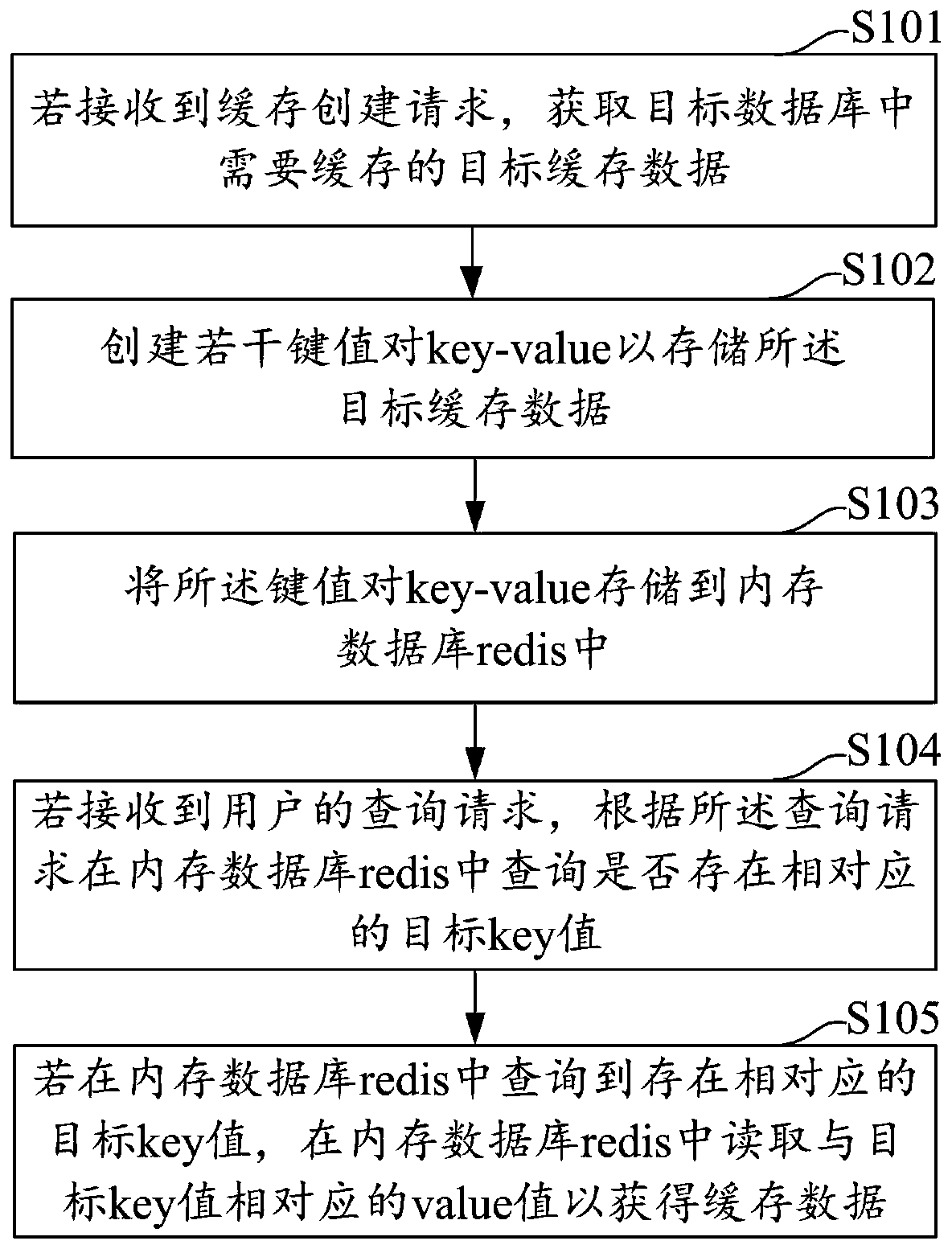

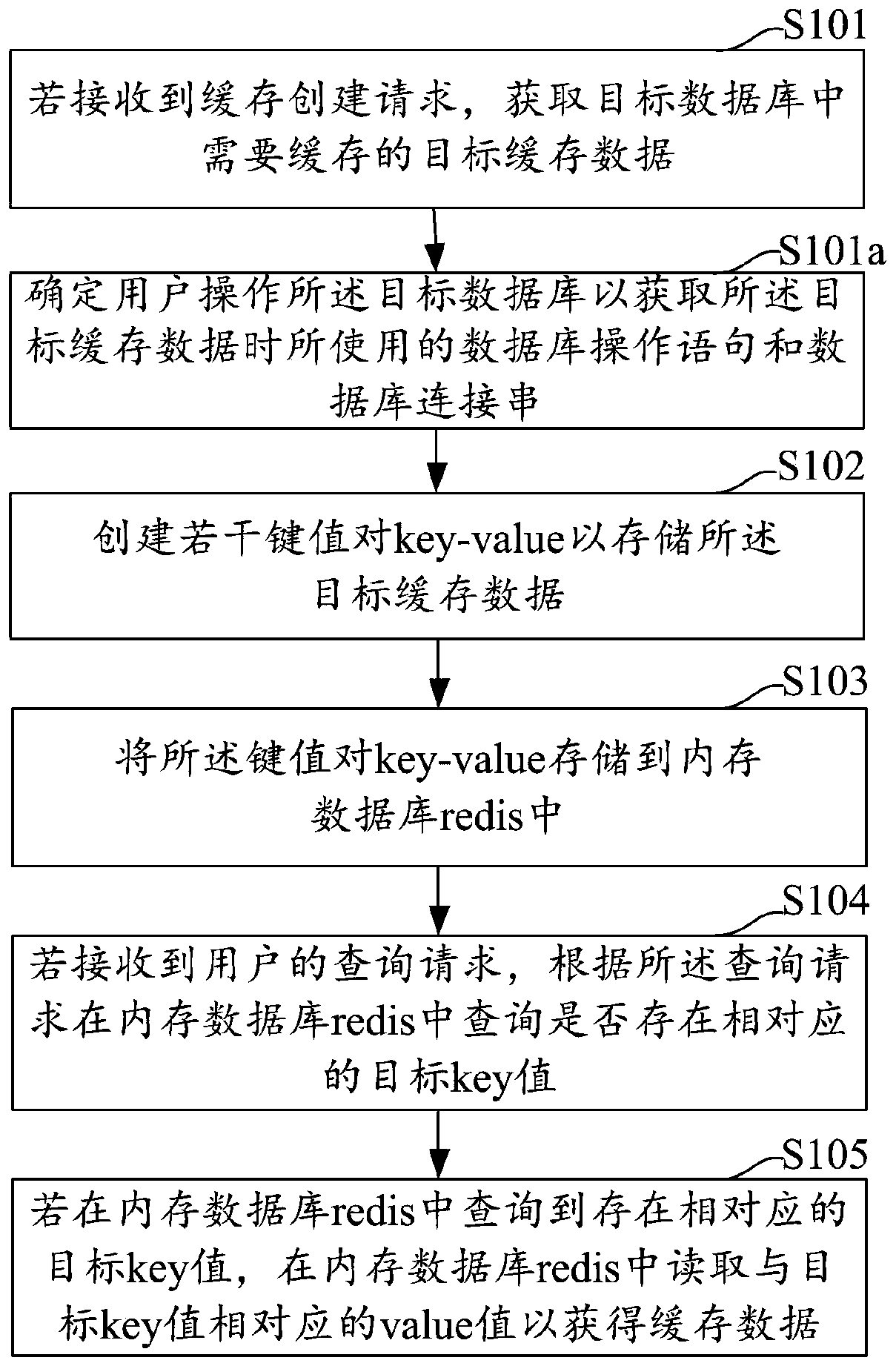

Cache processing method and device, computer equipment and storage medium

PendingCN111190928AImprove reading efficiencyReduce read frequencyDigital data information retrievalSpecial data processing applicationsIn-memory databaseEngineering

The embodiment of the invention discloses a cache processing method and device, computer equipment and a storage medium, and the method comprises the steps: obtaining target cache data needing to be cached in a target database if a cache creation request is received; creating a plurality of key-value pairs to store the target cache data; storing the key-value pairs into a memory database redis; ifa query request of a user is received, querying whether a corresponding target key value exists in the memory database redis or not according to the query request; and if the corresponding target keyvalue is inquired in the memory database redis, reading a value corresponding to the target key value in the memory database redis to obtain cache data. The cache processing method is provided basedon data processing, the data reading efficiency can be improved, the reading frequency of a remote database is reduced, and the working pressure of the remote database is relieved.

Owner:PINGAN PUHUI ENTERPRISE MANAGEMENT CO LTD

Adaptive data loading method for heterogeneous cluster storage

InactiveCN104270402ALoad regulationInput/output to record carriersData switching networksParallel computingComputerized system

The invention discloses an adaptive data loading method for heterogeneous cluster storage, and belongs to the field of computer system storage. The method comprises the following specific steps: (1) basic load balance: at the initial establishment of a system, distributing data on each node of clusters according to the maximum load capacity of each node; (2) adaptive distributed incremental load balance: during running of the system, collecting the resource occupation situation of each node in real time, and adjusting a data distribution situation adaptively and dynamically; and (3) distributing data loads among the clusters in a balanced manner at the initial establishment of the system by considering the load size of data as identical and taking the performance of a heterogeneous server as a weight through a weight-based hash method. The method is suitable for processing heterogeneous data loads in a high-stress, high-concurrent-reading-writing, multi-user and heterogeneous large-scale distributed storage system, and adaptively adjusting the distribution of data among servers according to loads.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

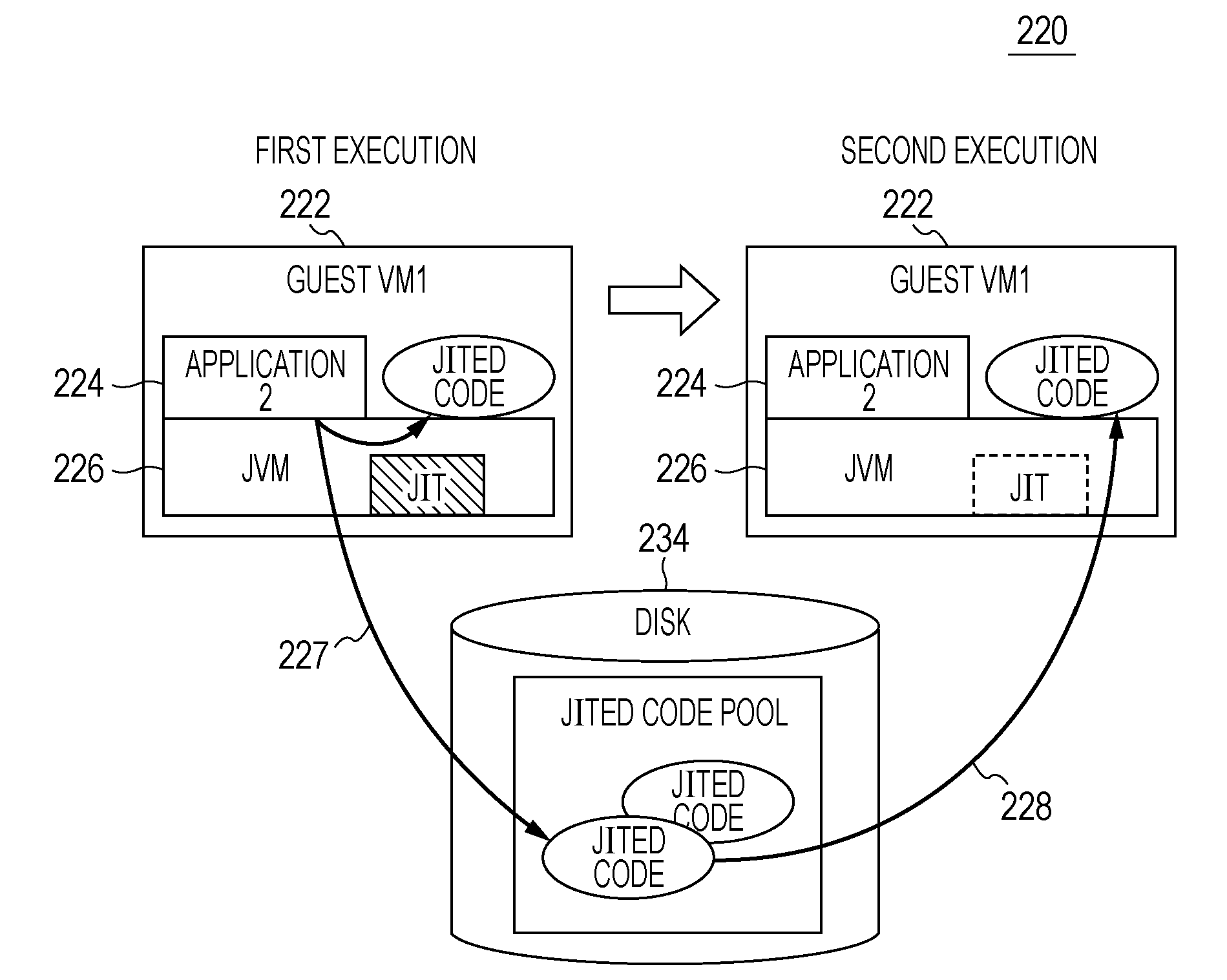

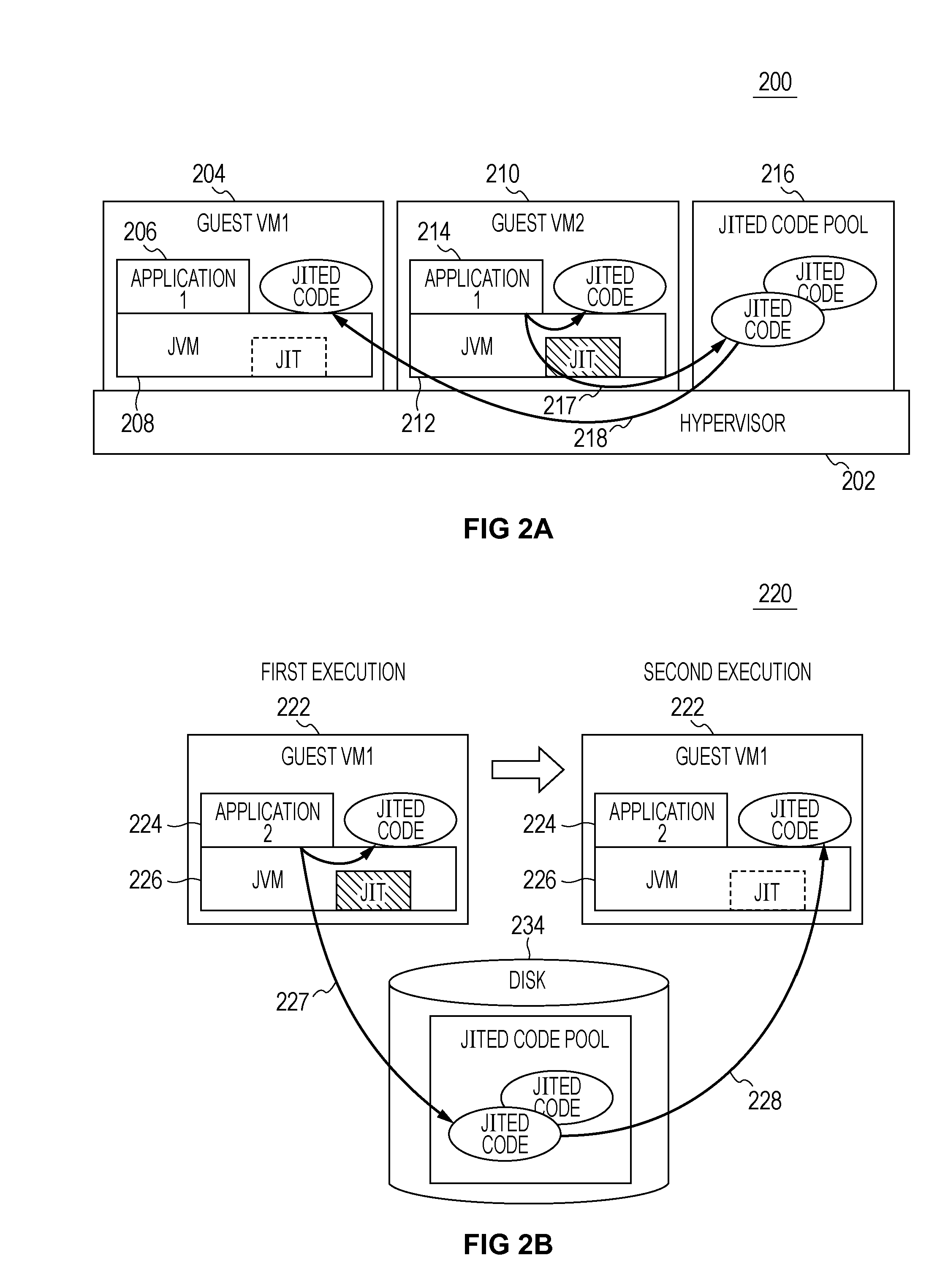

Dynamic compiler program, dynamic compiling method and dynamic compiling device

InactiveUS20110246974A1Low reusabilitySoftware engineeringProgram controlDynamic compilationSoftware engineering

A dynamic compiler program product, method, and device for sequentially compiling a partial computer program in a computer. The program product causes the computer to function as: an execution status acquisition unit for acquiring respective values of one or more pieces of current execution status information; a determination unit for reading, from the shared pool, the second list of the conditions associated with an executable instruction stream generated by compiling a partial program that is the same as a partial program to be compiled and determining whether respective values of corresponding pieces of current execution status information satisfy the conditions; and a dynamic compilation unit for generating an executable instruction stream by compiling the partial program to be compiled on the condition that a result of determination made by the determination unit is negative.

Owner:IBM CORP

Virtualization technology-based cloud computing security terminal

InactiveCN104125251AHigh strengthRealize two-way data backupTransmissionHuman–machine interfaceOperational system

The invention discloses a virtualization technology-based cloud computing security terminal, which comprises a virtualization technology-based cloud computing terminal key, which is characterized in that the hardware part of the cloud computing terminal key comprises a cloud computing security terminal; and a software part is also included and comprises an operation system arranged on a virtualization operation platform. A clean, sealed, comprehensive and dedicated operation system which can realize two-way data backup is provided for the cloud computing terminal. Virtualization is carried out on all tools and applications of the cloud computing operation on the dedicated human-computer interface provided by the dedicated operation system. Self explosion and self destruction are carried out on the cloud computing terminal in the cases of illegal access, reading, copying and interception of data and the system. the invention provides a cloud computing security terminal which is high in strength and applicable to the government, the financial department, the military department and the political science and law department. The terminal can serve as an intelligent Key to be connected onto other intelligent online electronic device for use, can also be equipped with a display device, an input device and an internet device to serve as a special cloud computer and has wide market application prospects.

Owner:华茂云天科技(北京)有限公司

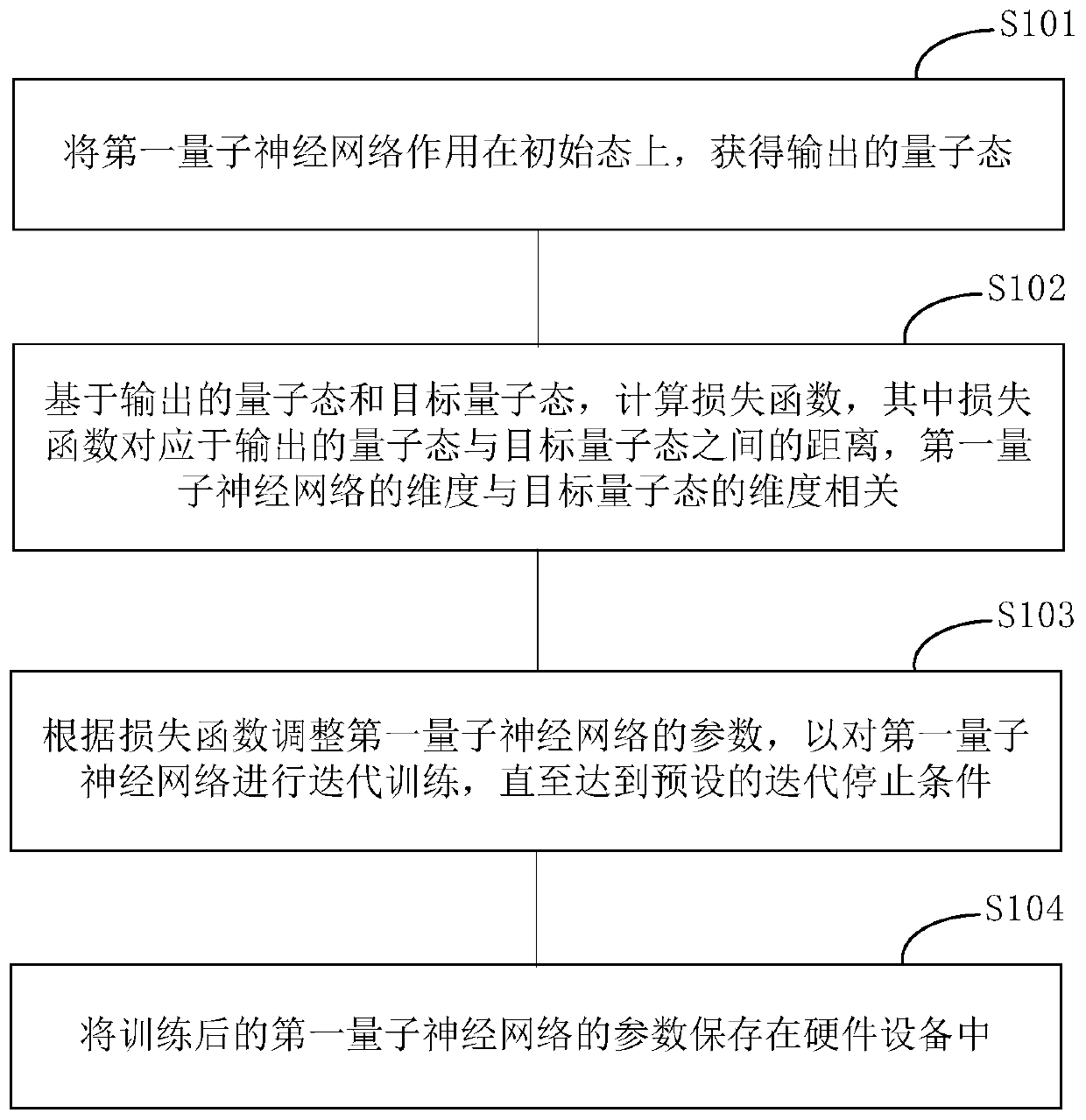

Quantum data storage method and device, quantum data reading method and device and computing equipment

ActiveCN111563186AImplement storageQuantum computersOther databases indexingComputational physicsComputer science

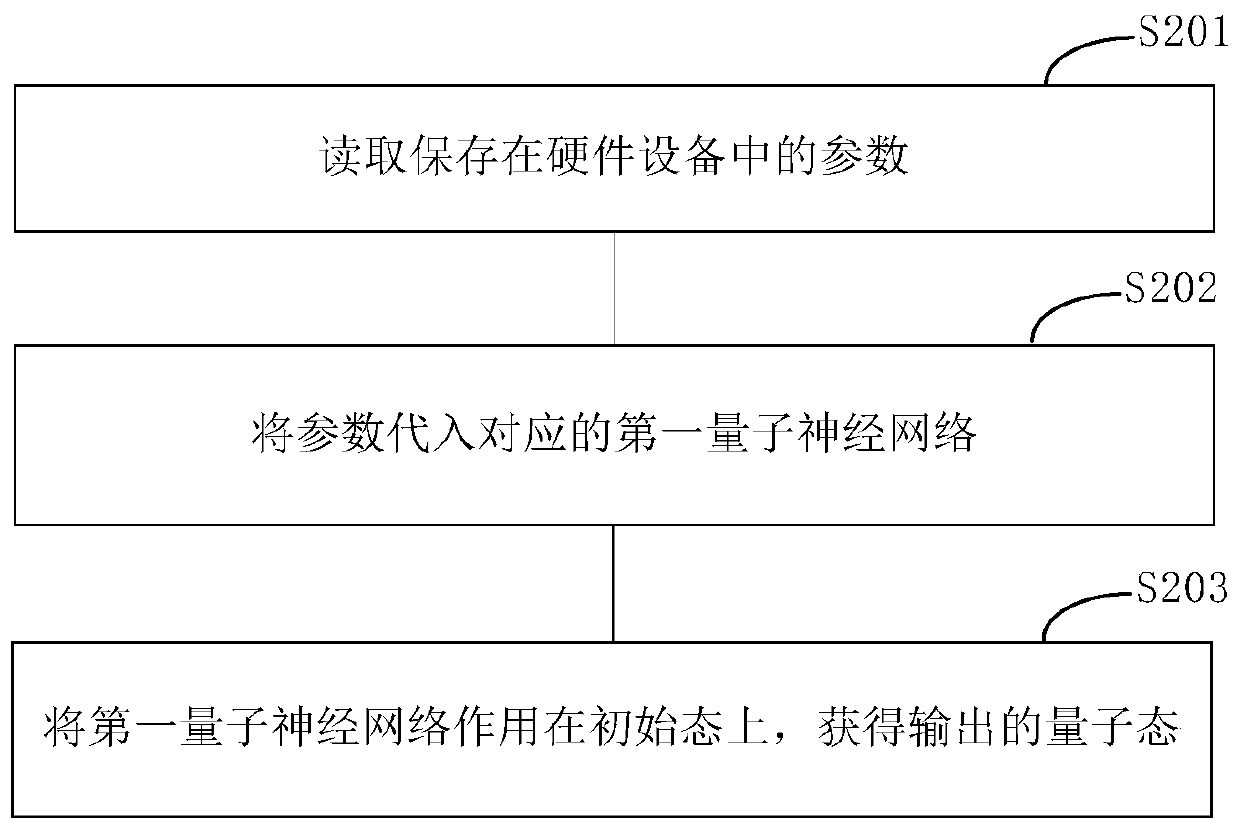

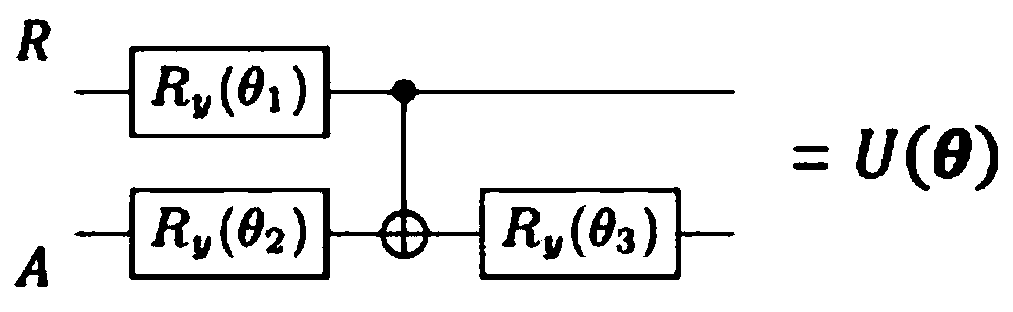

The invention discloses a quantum data storage method and device, a quantum data reading method and device and computing equipment, and relates to the field of quantum computers. The quantum data storage method comprises the following steps: acting a first quantum neural network on an initial state to obtain an output quantum state; calculating a loss function based on a target quantum state and the quantum state output by the first quantum neural network, whereinthe dimension of the first quantum neural network is related to the dimension of the target quantum state, and the loss function corresponds to the distance between the target quantum state and the quantum state output by the first quantum neural network; adjusting parameters of the first quantum neural network according to the loss function so as to carry out iterative training on the first quantum neural network until a preset iterative stop condition is reached; and storing the trained parameters of the first quantum neuralnetwork in hardware equipment. According to the embodiment of the invention, storage of quantum data can be realized.

Owner:BEIJING BAIDU NETCOM SCI & TECH CO LTD

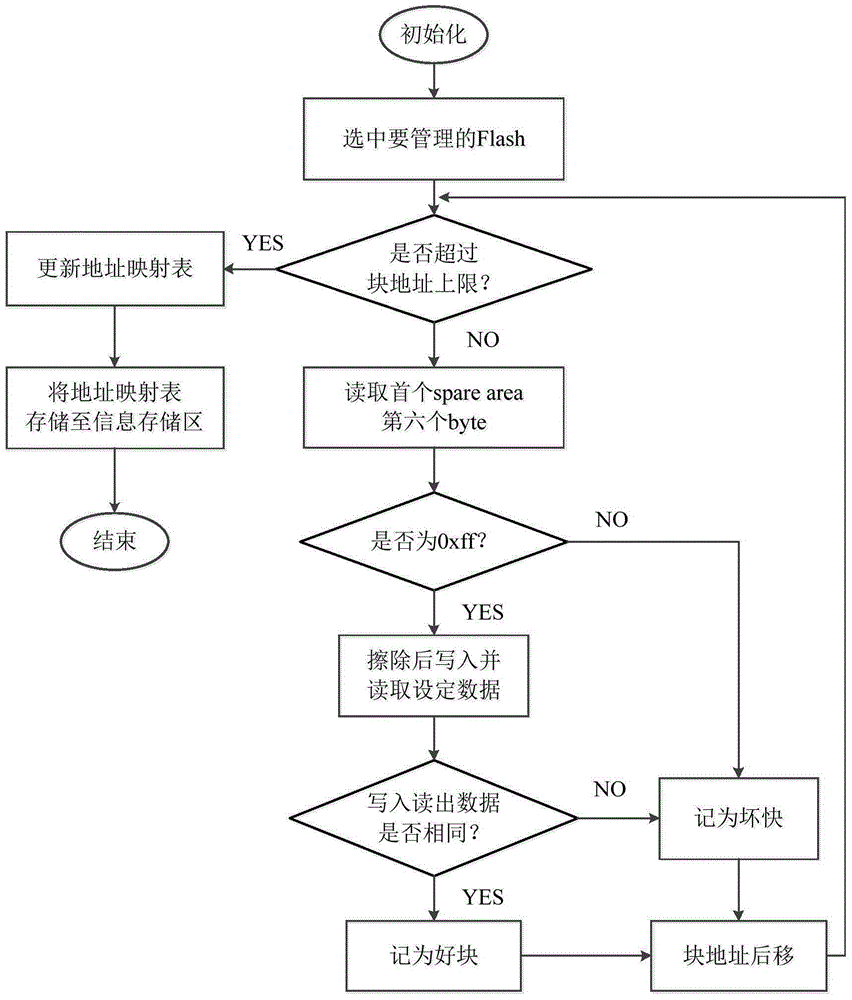

NAND Flash fault tolerant system based on FPGA (Field Programmable Gate Array)

ActiveCN105702300ASolve bad block detection and management problemsImprove storage performanceStatic storageAddress mappingField-programmable gate array

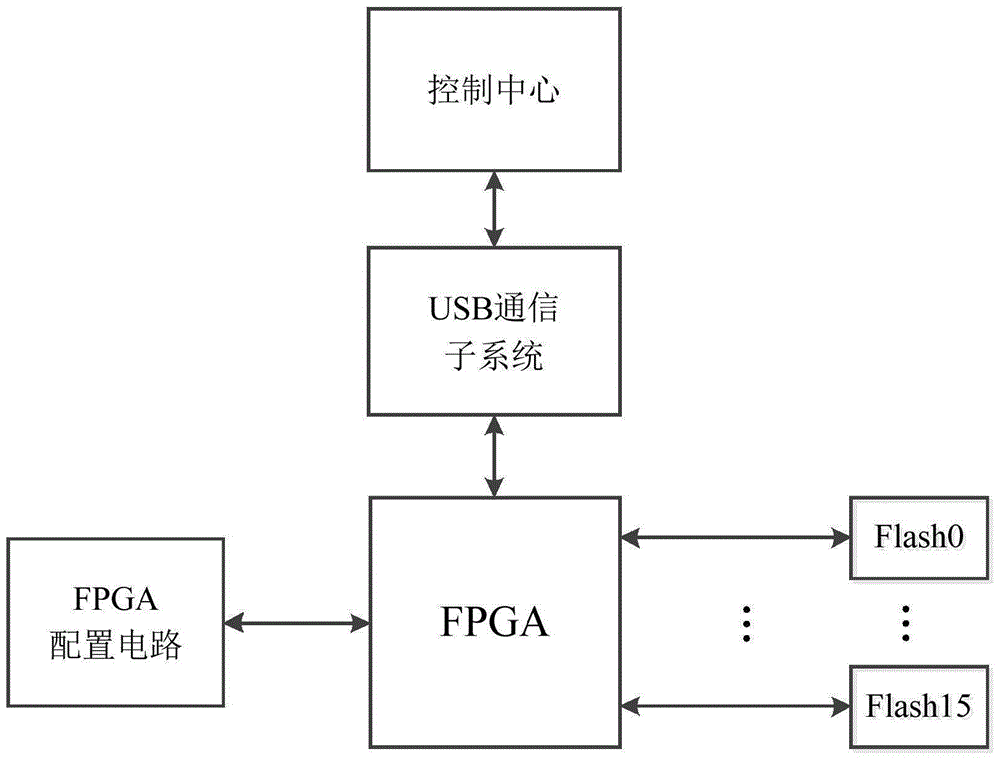

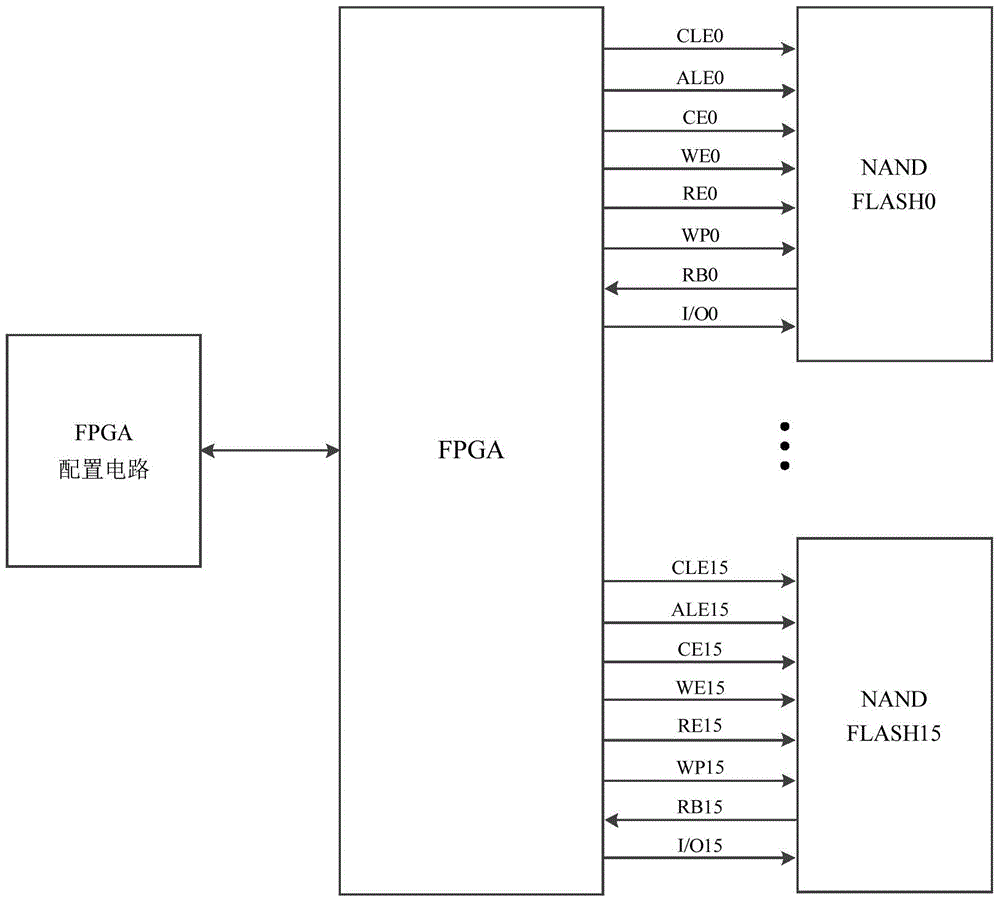

The invention discloses an NAND Flash fault tolerant system based on an FPGA (Field Programmable Gate Array). The NAND Flash fault tolerant system comprises a Flash bad block management subsystem, a USB (Universal Serial Bus) communication subsystem and an upper computer, wherein the Flash bad block management subsystem consists of the FPGA and a Flash array, and is used for detecting factory bad blocks by querying a flag bit of Flash in a spare area, querying return states of a reading operation, a writing operation and an erasing operation to detect lost bad blocks, and recording addresses of all the bad blocks. The Flash is partitioned into three logical areas, namely, a mapping good block area, a bad block area and an information storage area respectively, and an address mapping table is built and stored in the information storage area. The FPGA serves as a core controller, is communicated with the upper computer through the USB communication subsystem, and can receive a control instruction sent by the upper computer and upload data. A usage condition, including a space size of the good block area, a data storage status and the like of a current NAND Flash array can be queried through the upper computer; automatic detection can be performed to update the address mapping table; and stored data in the Flash array can be read, and data can be stored in the Flash array.

Owner:ZHEJIANG UNIV

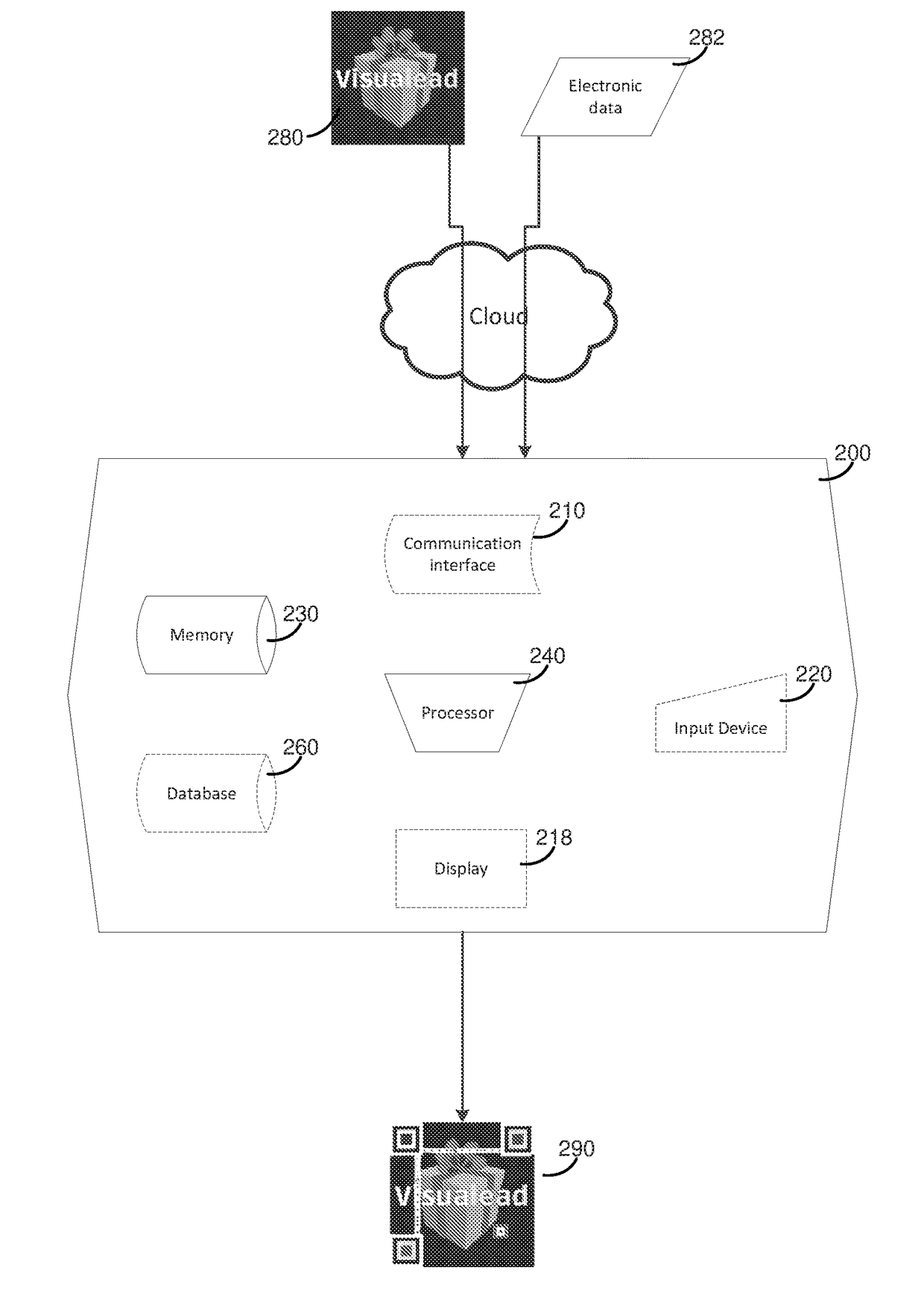

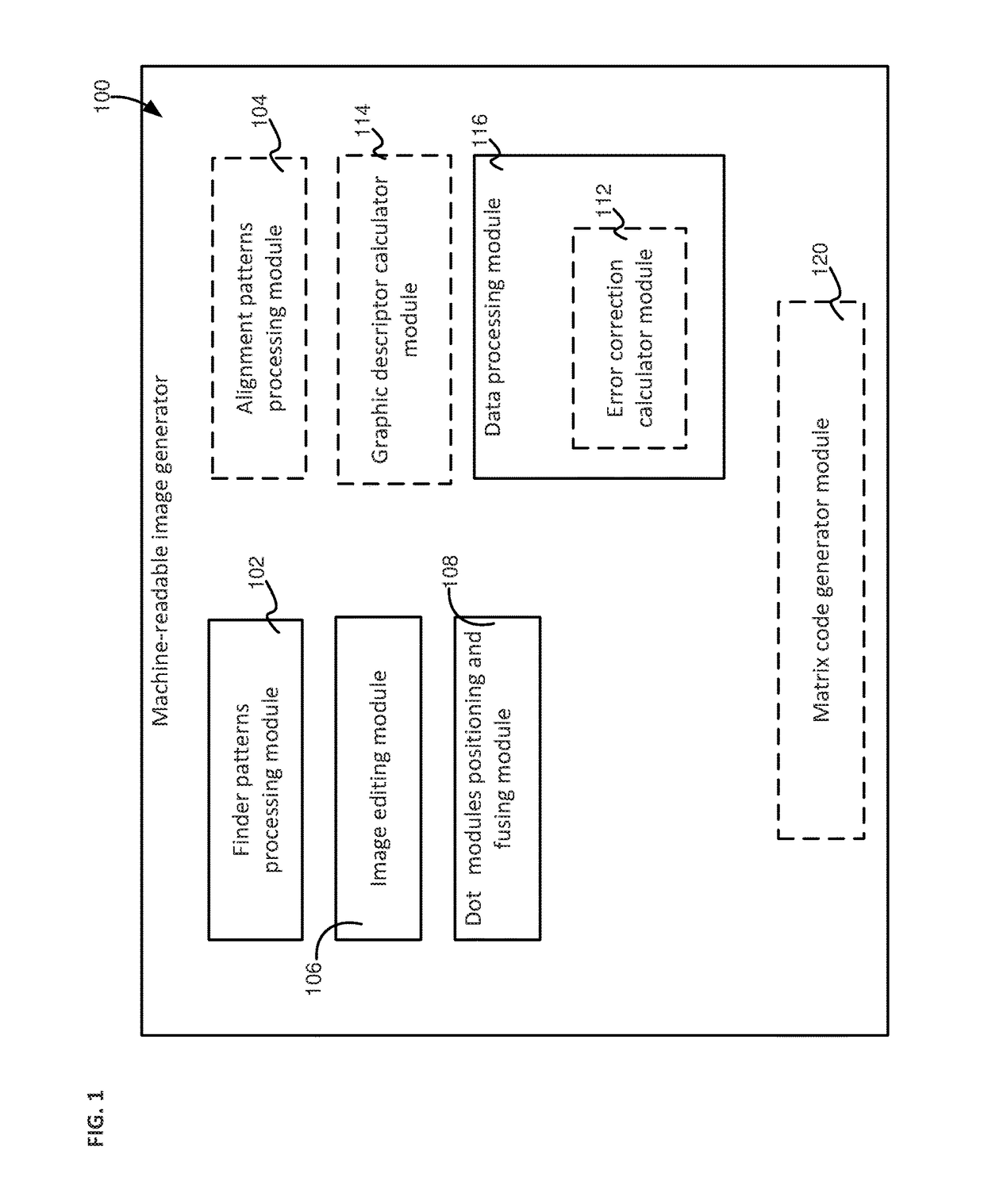

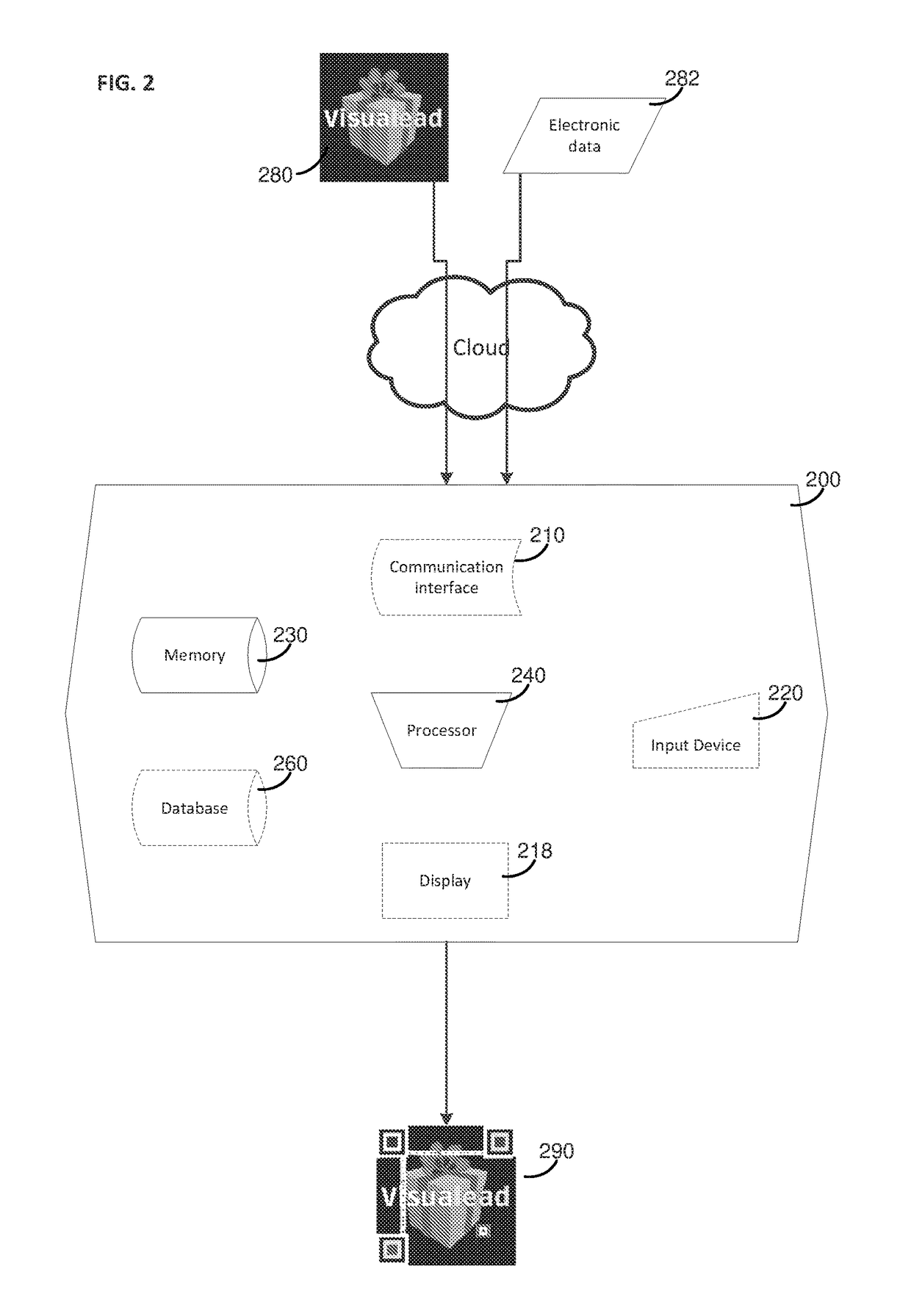

Machine-readable image encoding data

ActiveUS20170357884A1High capacityEasy and accurate extractionRecord carriers used with machinesGraphicsComputer science

There is provided a non-transitory computer readable storage medium tangibly embodying a machine-readable image having data encoded therein and embedded with a graphic, the machine-readable image adapted to be detected by a reader for decoding said encoded data, including: the graphic associated with an image descriptor calculated based on a chosen area of the graphic, the image descriptor being used in a reading process of said machine-readable image; a plurality of function patterns; and a plurality of dot modules having decoded values corresponding to at least said encoded data, the dot modules being positioned in one or more encoding regions of the machine-readable image relative to the function patterns and the chosen area of the graphic.

Owner:ALIBABA GRP HLDG LTD

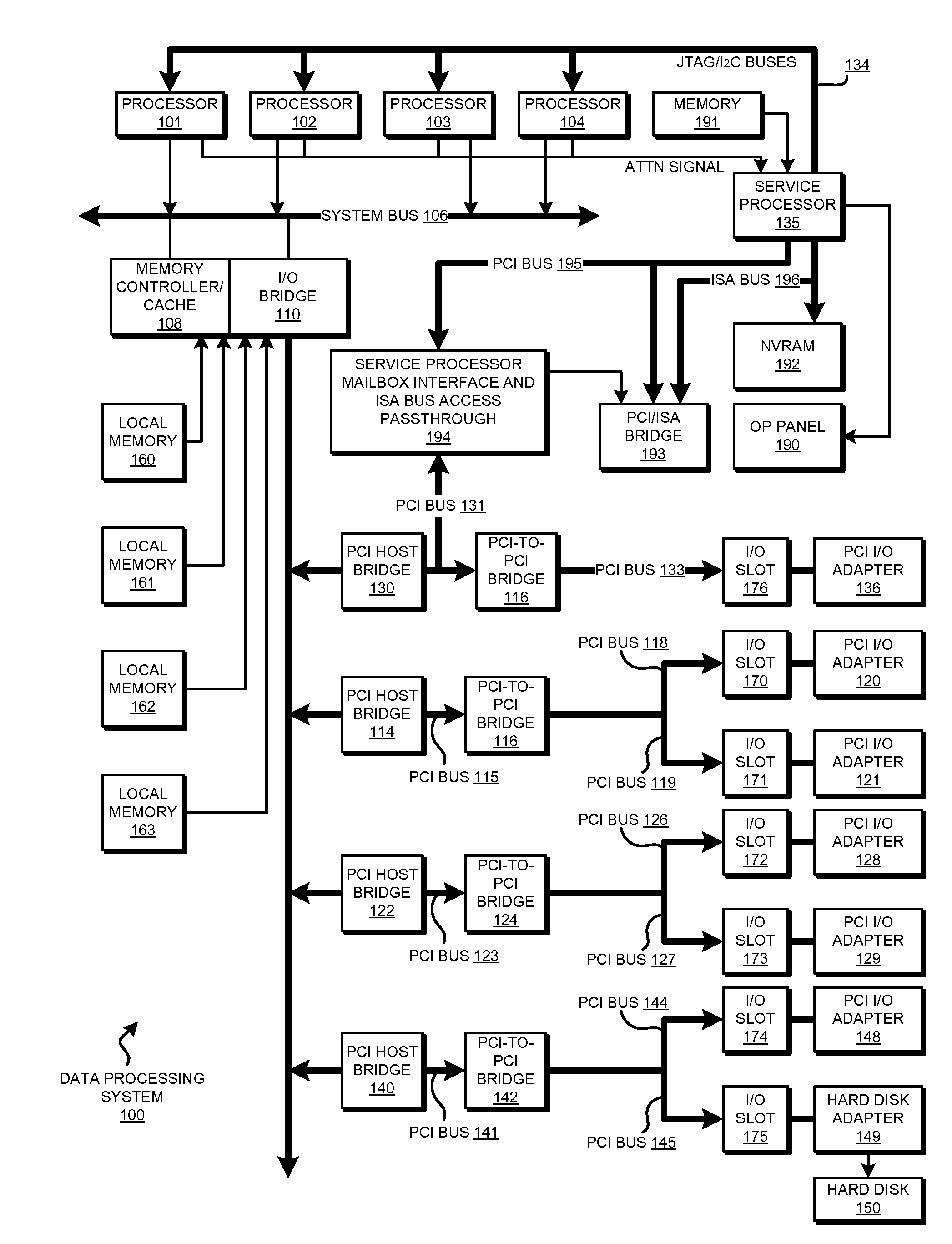

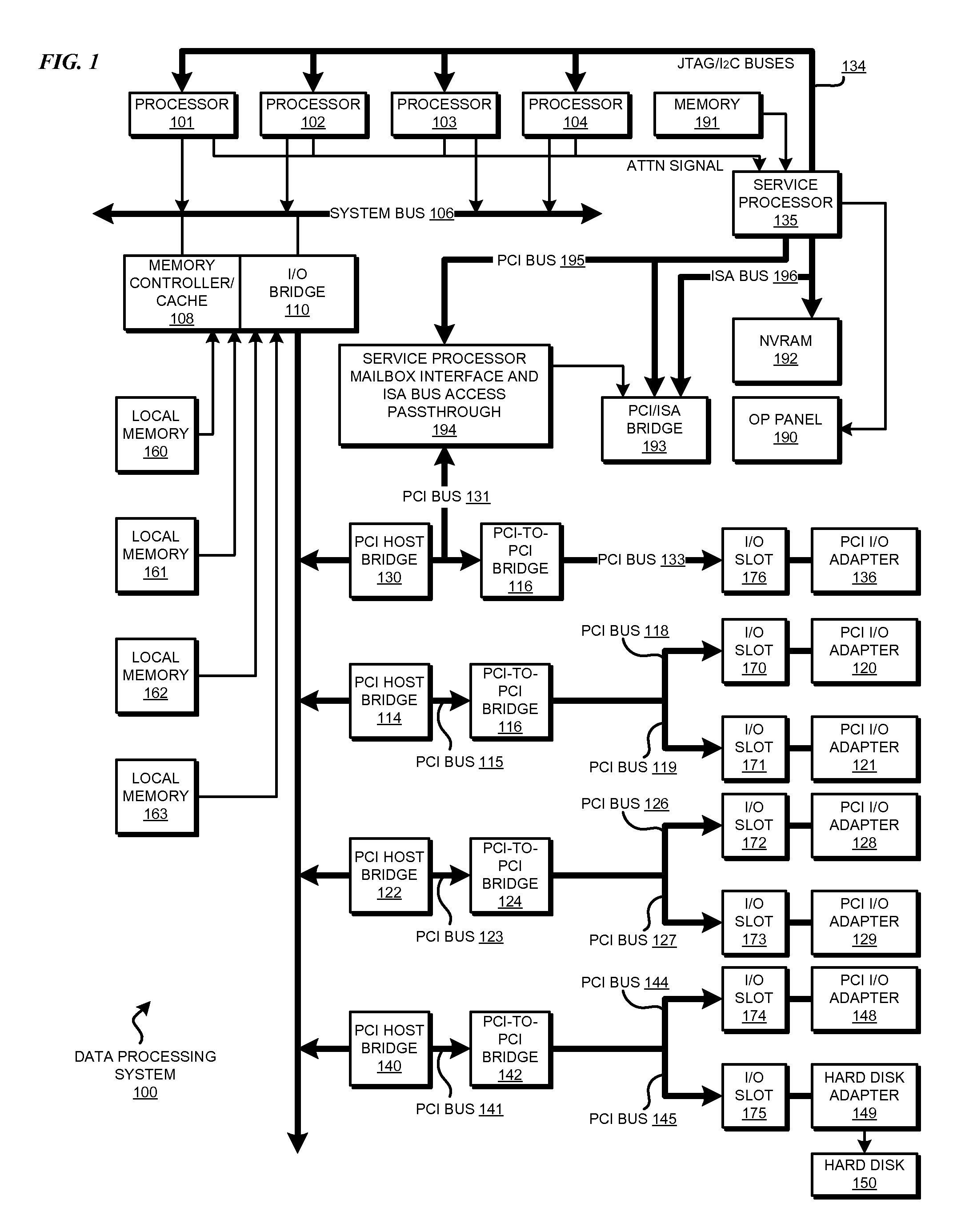

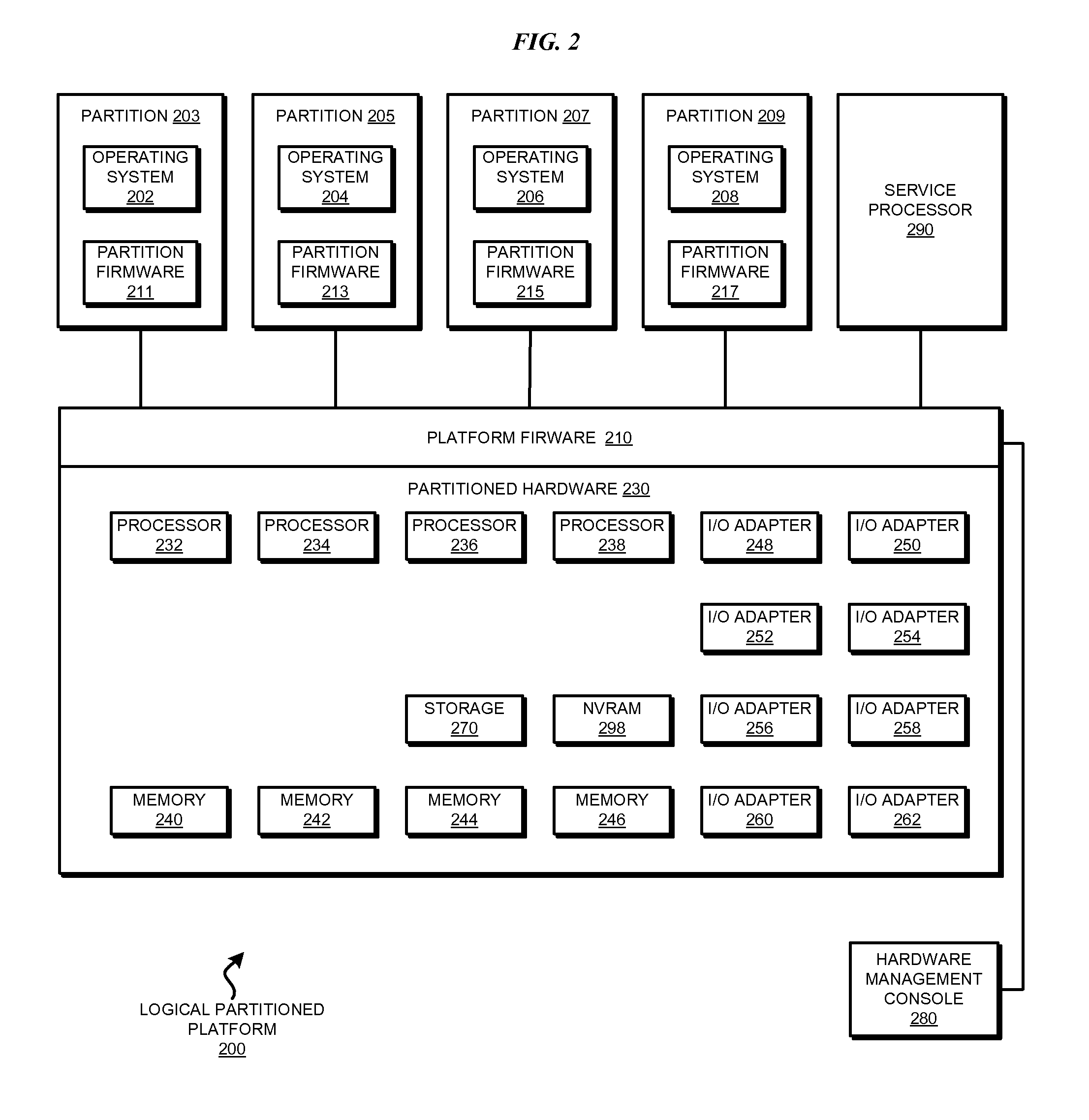

Migrating memory data between partitions

InactiveUS20090307456A1Memory adressing/allocation/relocationProgram controlComputer hardwareApplication software

A method, system, and computer usable program product for migrating memory data between partitions are provided in the illustrative embodiments. All or a portion of a memory data of the source partition is written to a data storage unit, which may be a shared paging space, or a shared area of a data storage unit other than a paging space. The writing uses a first data communication path configured for paging the memory data. The portion of the memory data from the data storage unit is read at a destination partition. The reading uses a second data communication path configured for paging a second memory data. The read portion of the memory data may be used for executing a migrated application. The writing and reading may use a third and a fourth data communication paths respectively that may be configured for paging memory data to the shared area.

Owner:IBM CORP

Image data processing method and device, computer equipment and storage medium

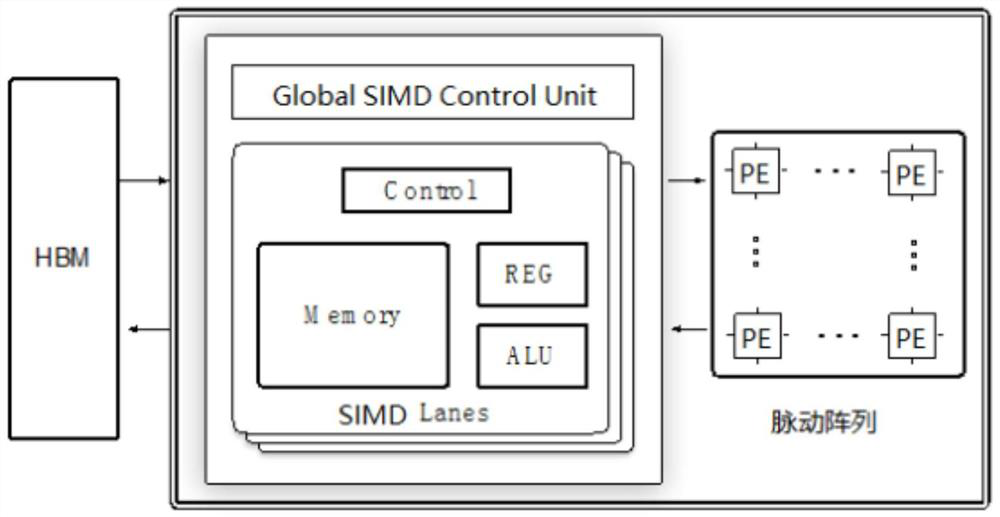

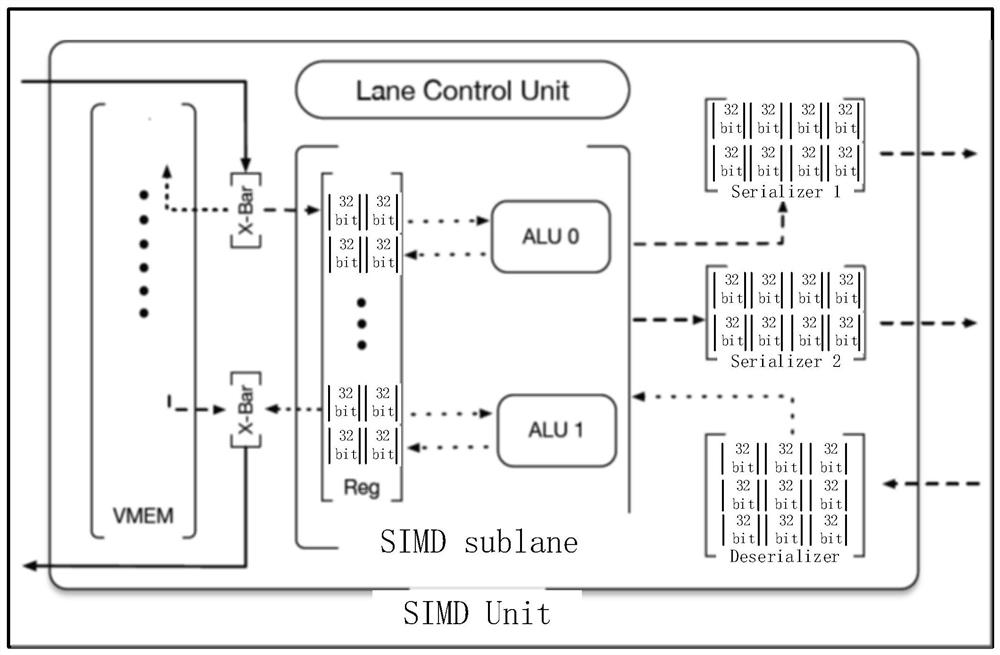

PendingCN111897579AAvoid CatonImprove processing efficiencyImage memory managementConcurrent instruction executionData packOccurrence data

The invention relates to an image data processing method, which comprises the steps of obtaining image data of N to-be-processed images, and the image data of each to-be-processed image comprising C parts of image channel data; storing the image data into C storage areas of a local memory, wherein N storage units in each storage area store one piece of image channel data of N to-be-processed images respectively; when a data reading instruction occurs, determining a historical address according to a current address carried by the data reading instruction, thereby reading target image channel data from a local memory based on the storage address; arranging the read target image channel data in the form of a two-dimensional matrix, enabling the data corresponding to the same channel to be inthe same matrix row, and enabling the data corresponding to the same to-be-processed image in the adjacent matrix rows to be distributed in two adjacent matrix columns; and sequentially transmitting each column of data arranged in a two-dimensional matrix form to the pulsation array according to a time sequence for operation to obtain an operation result. By adopting the method, the data processing efficiency can be improved.

Owner:TENCENT TECH (SHENZHEN) CO LTD

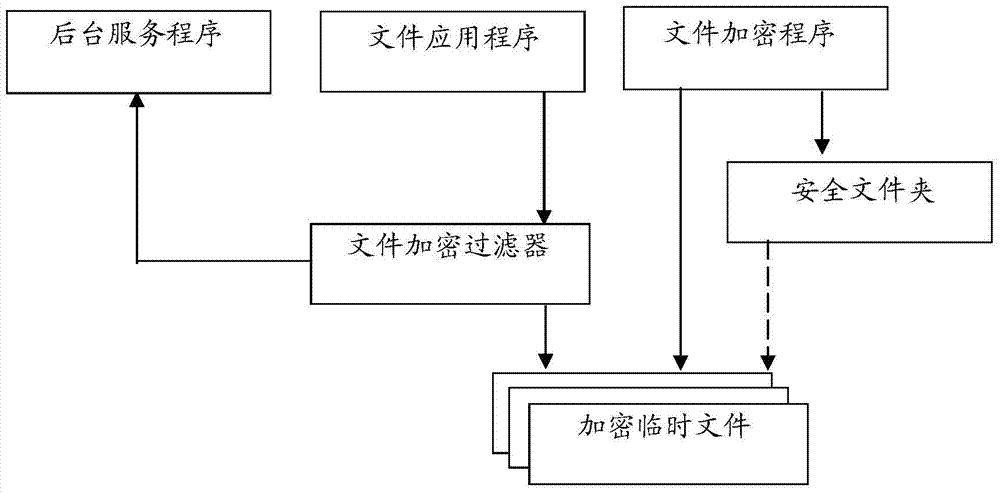

File encryption system

The invention relates to a file encryption system, comprising a safety folder, a file encryption program and a file encryption filter. The file encryption program generates a temporary file, namely an encrypted temporary file, corresponding to an opened file on a permanent storage medium of a computer in a form of a ciphertext when a user opens a currently browsed file in currently browsed safety folder by using a cursor through a human-computer interface of the file encryption program in a double-click manner; a new temporary file, namely an encrypted temporary file, which relates to file content of the selected opened file and is generated in the process that a file application program processes the opened file, also exists in the form of the ciphertext; the file encryption filter automatically carries out corresponding decryption and encryption treatment on the file content when the file application program carries out reading and writing operations on the encrypted temporary files. Thus, leakage of sensitive information due to the fact that the file content of the opened file exists on the permanent storage medium in a form of a cleartext is avoided.

Owner:WUHAN UNIV OF TECH

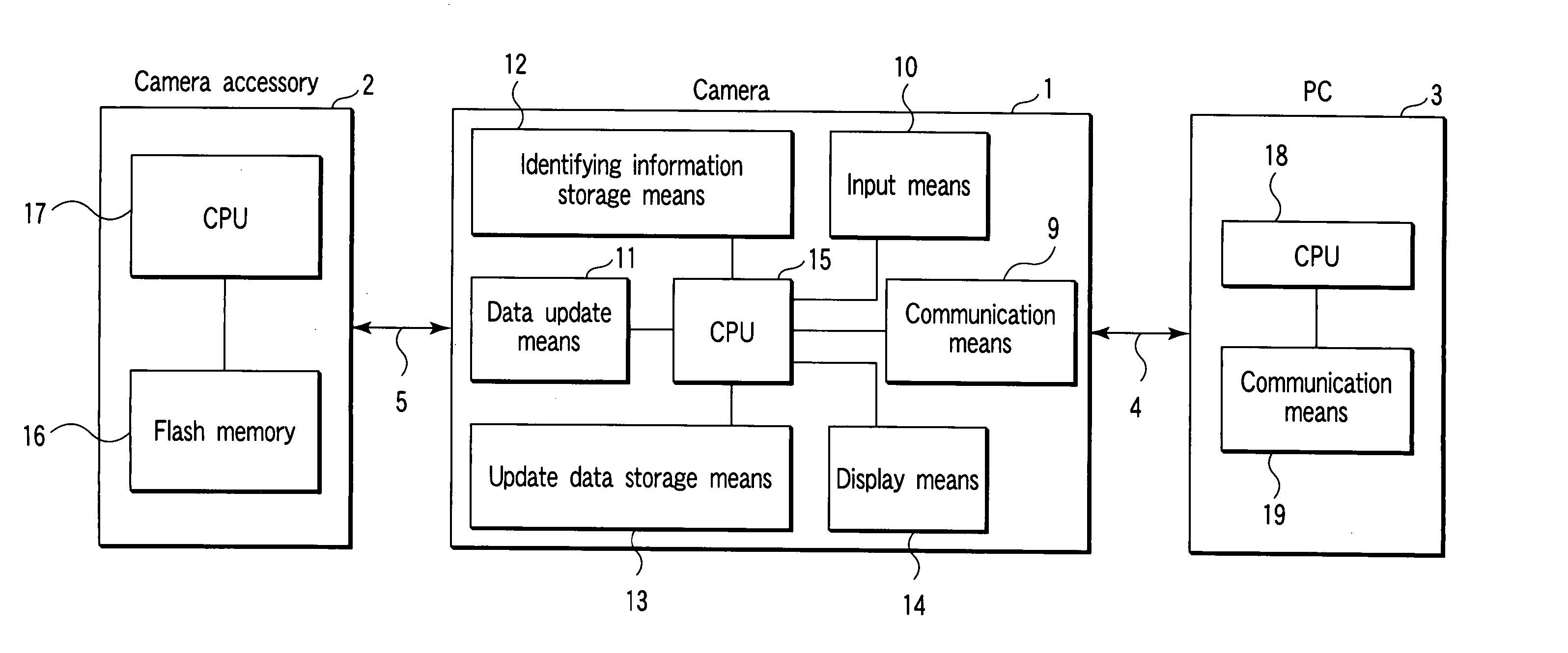

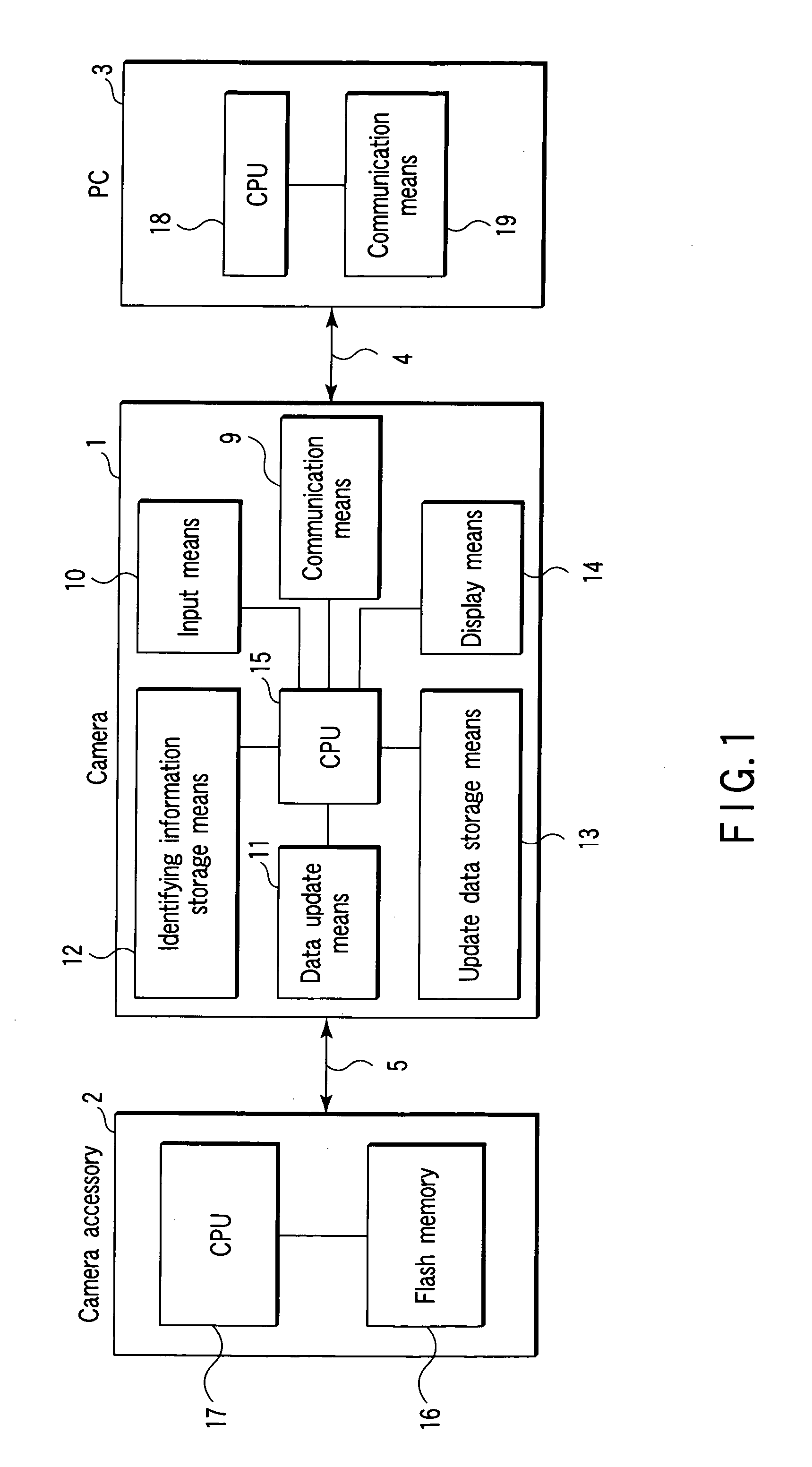

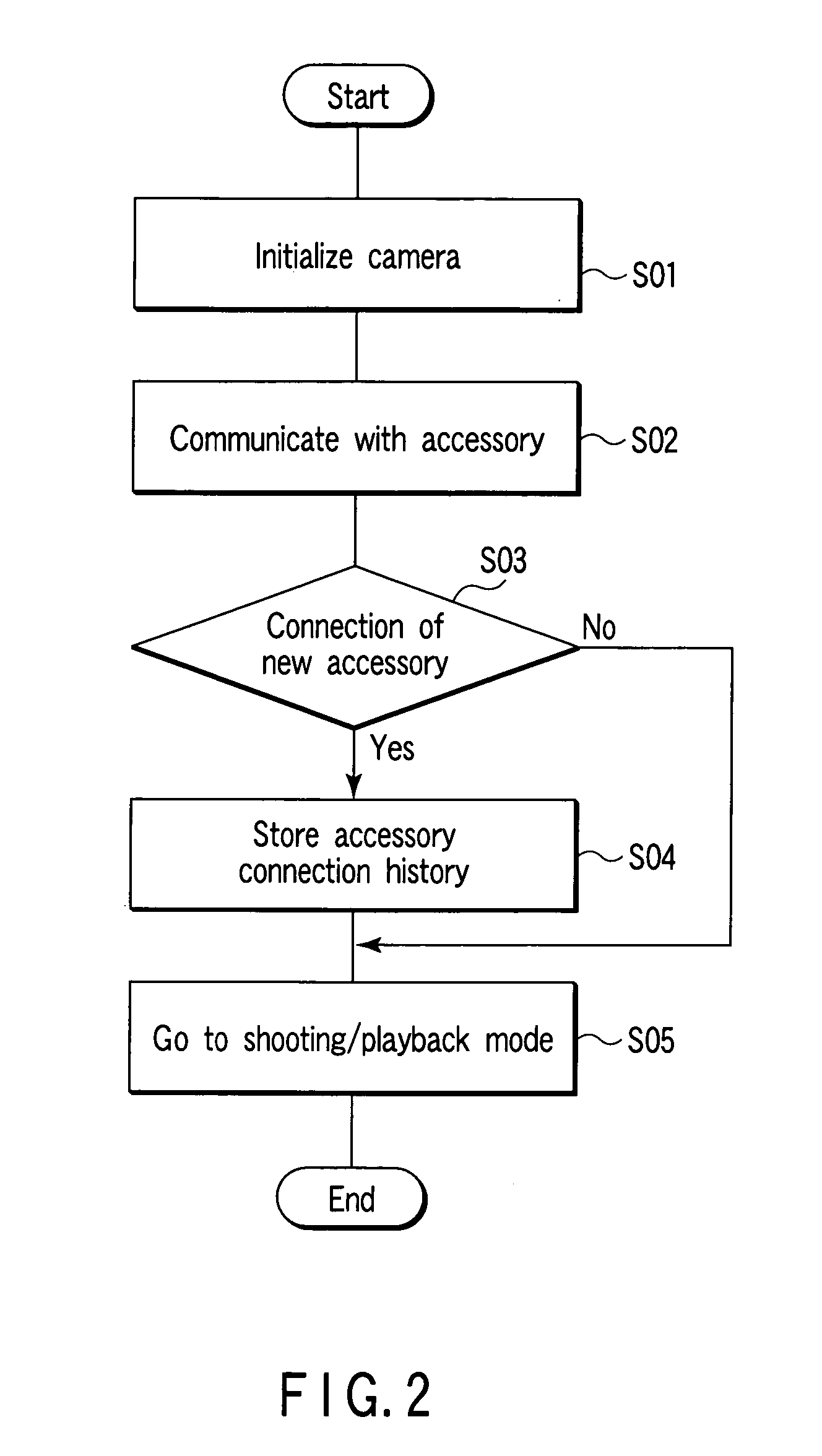

Data rewriting apparatus and data rewriting method

A data rewriting apparatus which connects with a peripheral device and updates data stored in storage means provided in the peripheral device, includes identifying information storage means for storing identifying information which identifies the peripheral device and the data stored in the storage means in the peripheral device for each of a plurality of peripheral devices of different types, communication means for receiving together update data to update the data stored in the storage means, from a host computer connected with the data rewriting apparatus, update data storage means for storing the update data inputted together by the communication means, and data update means for reading, from the update data storage means, the update data corresponding to the peripheral device connected to the data rewriting apparatus, and updating the data stored in the storage means of the peripheral device.

Owner:OLYMPUS CORP