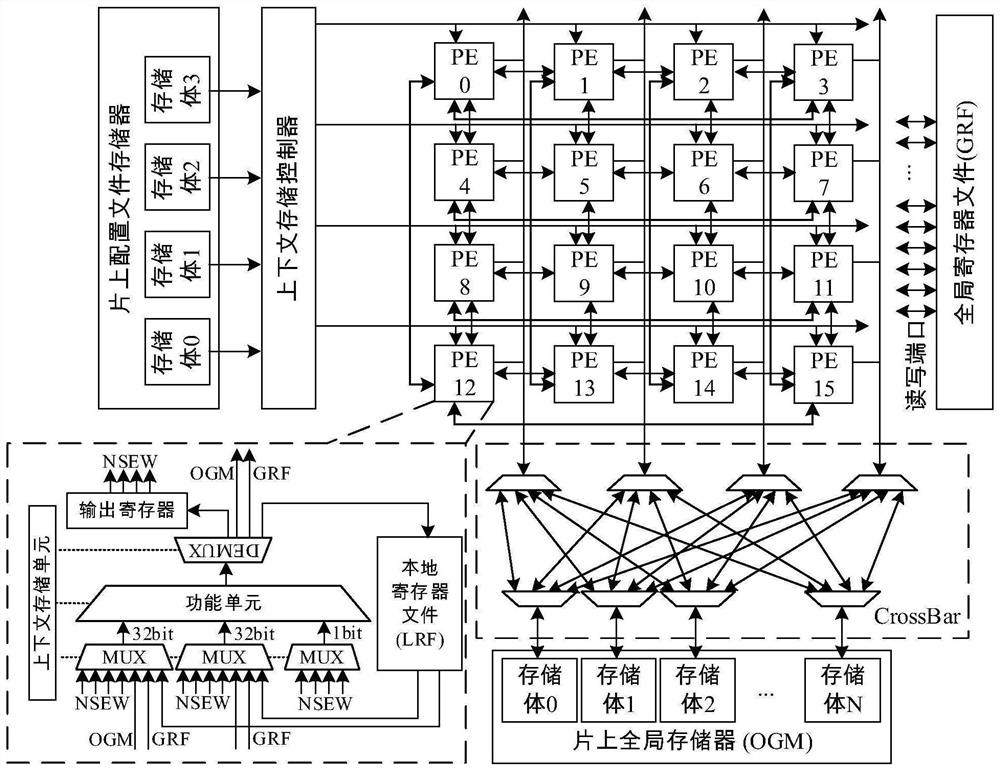

Data reuse memory access conflict elimination method for coarse-grained reconfigurable structure

A coarse-grained, data technology, applied in the field of coarse-grained reconfigurable structure compilers, which can solve the problem of not considering reducing the number of memory access operations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0089] The following describes the preferred embodiments of the present application with reference to the accompanying drawings to make the technical content clearer and easier to understand. The present application can be embodied in many different forms of embodiments, and the protection scope of the present application is not limited to the embodiments mentioned herein.

[0090] The idea, specific structure and technical effects of the present application will be further described below in order to fully understand the purpose, features and effects of the present application, but the protection of the present application is not limited thereto.

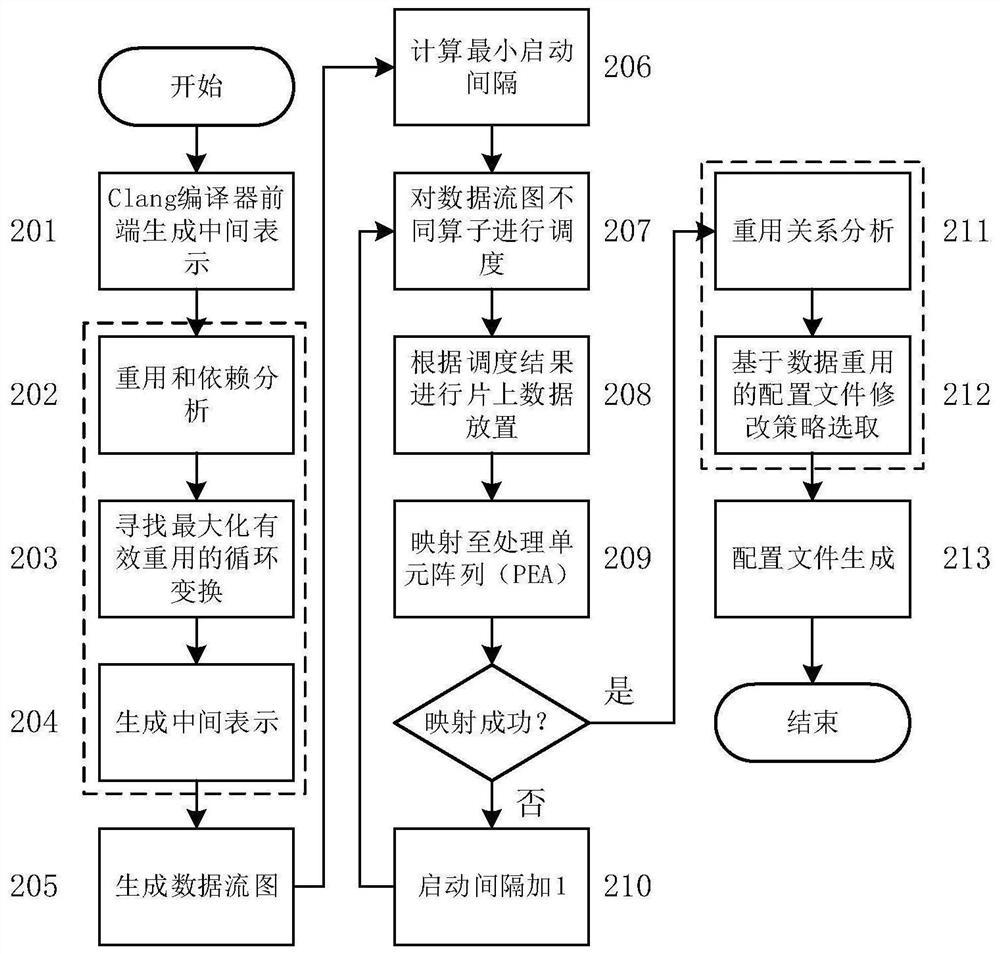

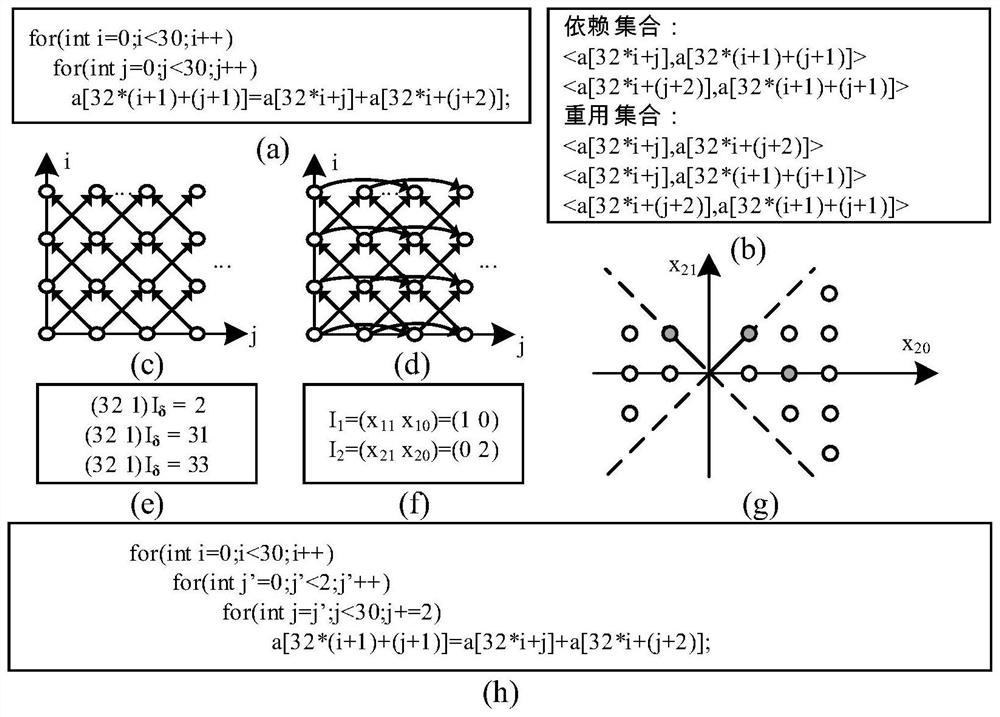

[0091] Such as figure 2 As shown, the schematic diagram of the compiler back-end process of an embodiment of the present application, wherein,

[0092] Step 201, using the CGRA compiler front end based on LLVM (Low Level Virtual Machine) to compile the loop kernel part of the source program into an intermediate representation (in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More