Method and system for automatic schedule logic simulation and code coverage rate analysis

A code coverage and logic simulation technology, applied in the field of automatic scheduling logic simulation and code coverage analysis, can solve the problems of manual participation, the inability of logic verification personnel to be liberated, and the difficulty of unifying the execution process.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

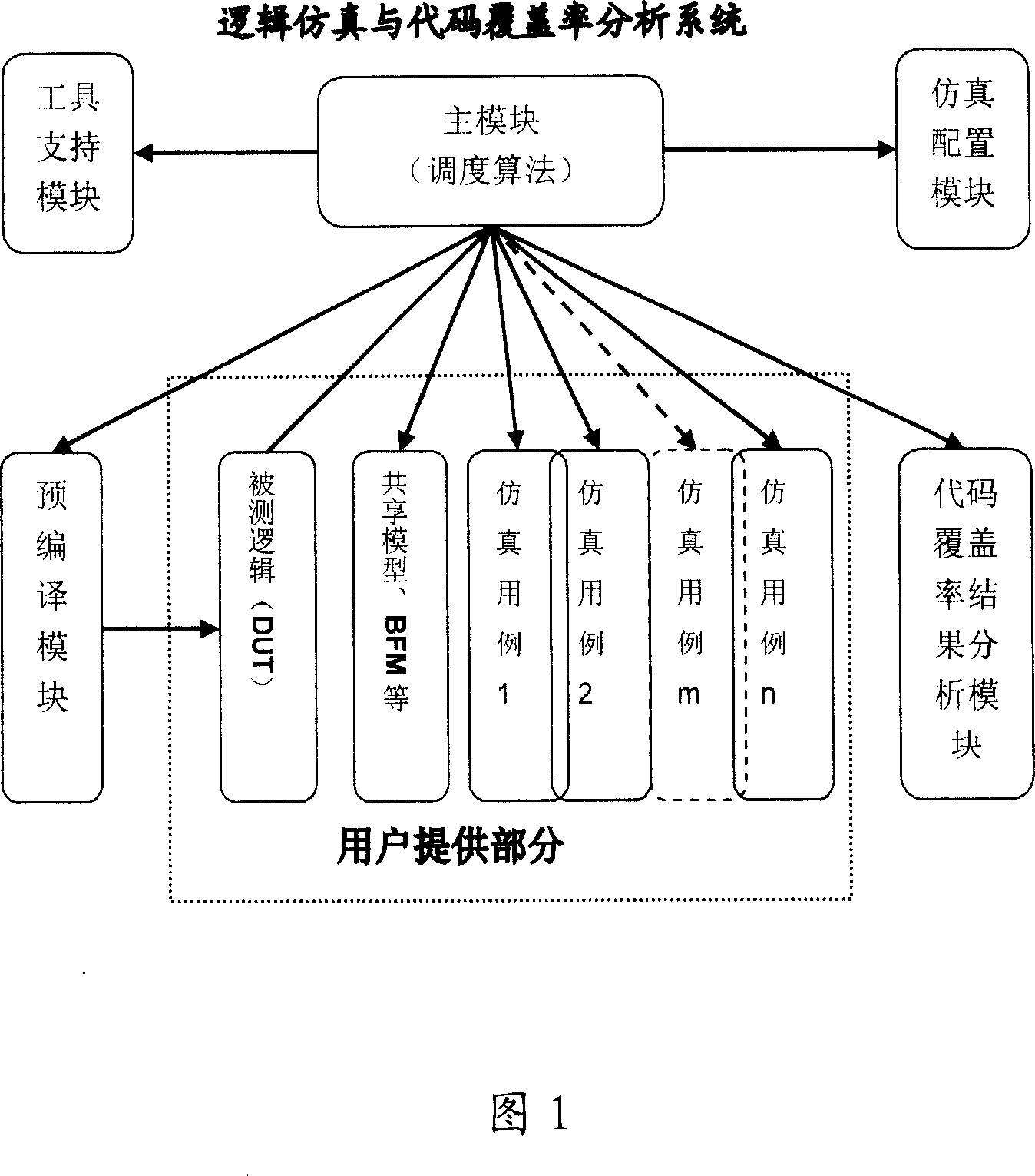

[0050] Fig. 1 is a schematic structural diagram of the logic simulation and code coverage analysis system of the present invention, and the dotted line box is "user-supplied part".

[0051] As shown in the figure, the main module mainly realizes the configuration of some environment variables and the scheduling function of each sub-module.

[0052] The tool support module provides some typical functions that need to be used in scheduling logic simulation and code coverage analysis, and is scheduled by the main module; for example: support users to freely choose whether to start code coverage analysis, support automatic search for logic code files And allows users to adjust the logic files that need coverage analysis according to specific needs, supports automatic search of simulation use case sets and adjusts the simulation use cases that need to be executed in this simulation according to user specific needs, supports selection of simulation compilation process, and supports a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com