Method of reducing clock differential in a data processing system

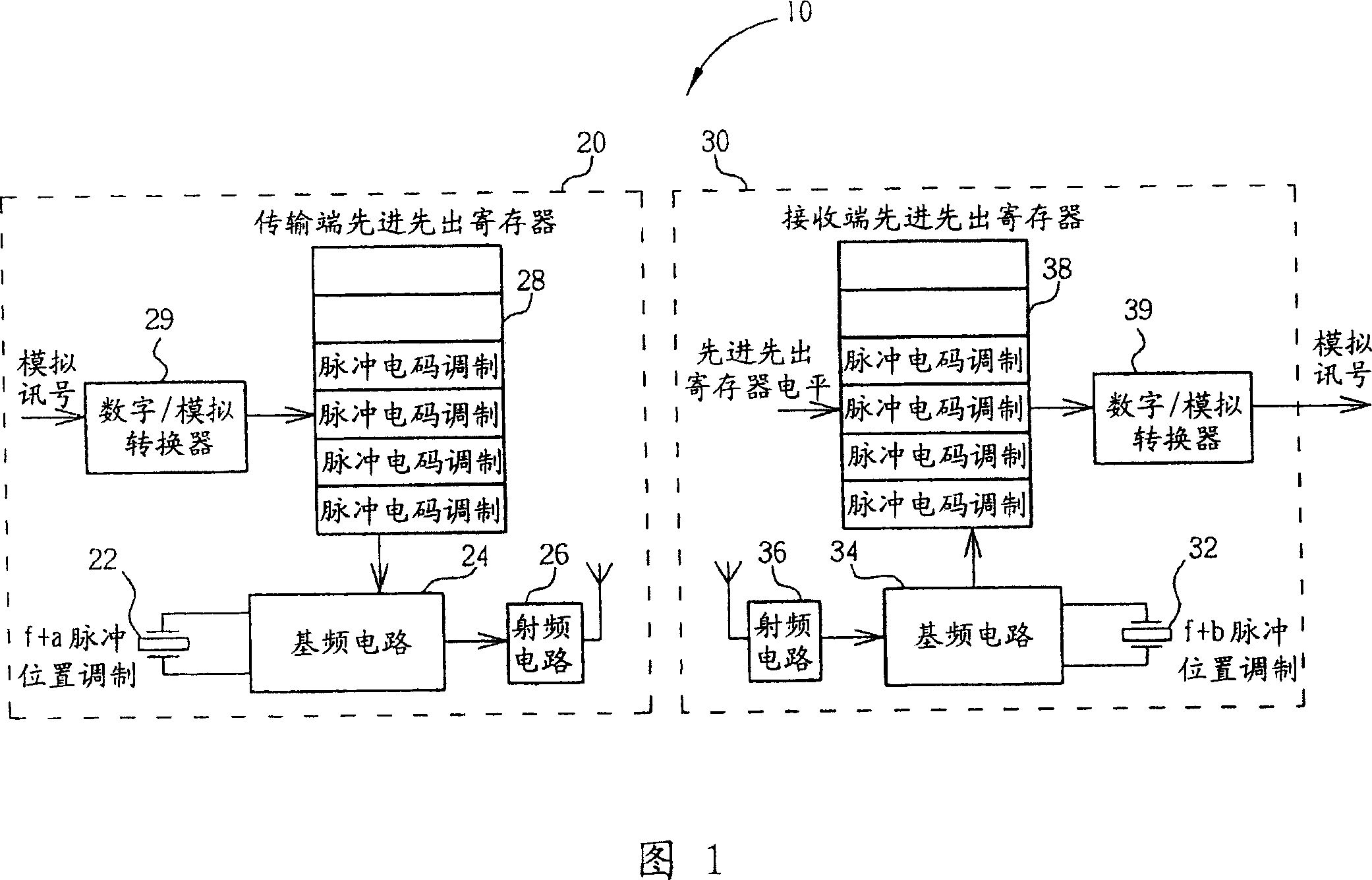

A data processing system and data sample technology, which is applied in the direction of electrical digital data processing, digital transmission system, data conversion, etc., can solve the problems of the receiving end 30 being too late to process, insufficient buffer, and buffer overflow.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

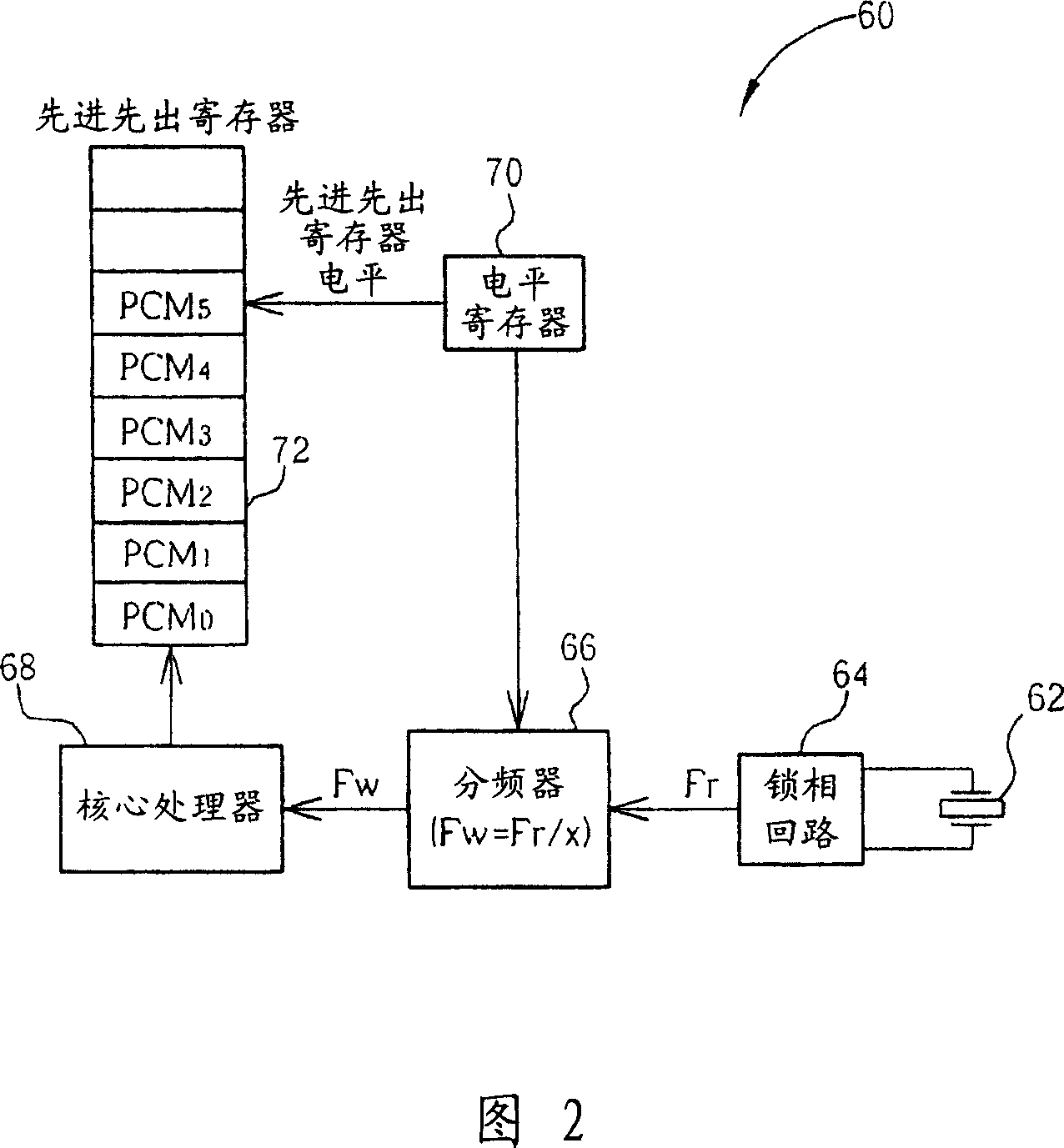

[0032] Please refer to Figure 2. FIG. 2 is a functional block diagram of the data processing system 60 of the present invention. The data processing system 60 improves the synchronization problem of a data system between the transmitting end and the receiving end in the prior art, and can be implemented at the transmitting end or the receiving end of a data processing system to avoid buffer shortage and overflow problems. For the sake of convenience, the following only describes the implementation of the data processing system 60 at the receiving end, and the situation at the transmitting end can be implemented and utilized only with a slight adjustment.

[0033] In the data processing system 60 , a quartz oscillator 62 is used to provide an initial frequency, and then a phase-locked loop (PLL) 64 is used to shift the phase to generate a reference frequency Fr for a frequency divider 66 . The frequency divider 66 divides the reference frequency Fr by the divisor x to generate...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More