System and method for performing locked operations

A locking operation, non-locking technology, applied in multi-programming devices, program control design, instruments, etc., can solve problems that affect processor performance and cannot operate effectively

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

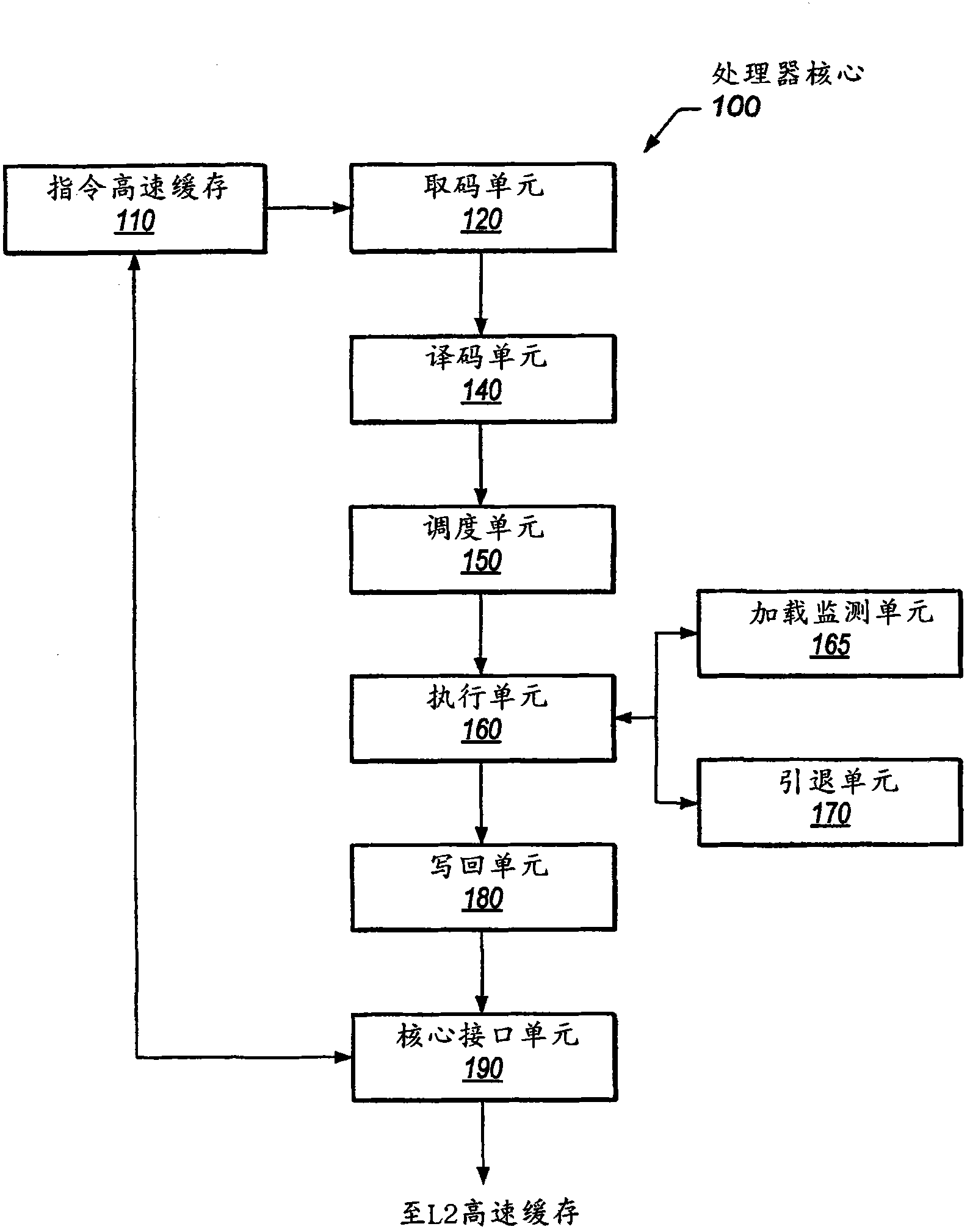

[0014] figure 1 is a block diagram of various processing components of an example processor core 100 according to an embodiment. As shown in the figure, the processor core 100 may include an instruction cache 110, a code fetch (fetch) unit 120, an instruction decode unit (DEC) 140, a scheduling unit 150, an execution unit 160, a load monitoring unit 165, a retirement unit 170 , writeback unit 180 and core interface unit 190 .

[0015] During operation, the code fetch unit 120 fetches instructions from the instruction cache 110 inside the processor core 100, such as the L1 cache. The code fetch unit 120 provides the fetched instructions to the DEC 140 . The DEC 140 decodes the instruction and stores it in a buffer until the decoded instruction is ready to be dispatched to the execution unit 160 . DEC 140 will describe Figure 5 will be explained further.

[0016] Dispatch unit 150 provides instructions to execution unit 160 for execution. In a specific embodiment, the sch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com