Using interrupted through-silicon-vias in integrated circuits adapted for stacking

A technology of integrated circuits and vias, applied in circuits, electrical components, electronic switches, etc., to solve the problems of indistinguishable chips and power loss.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

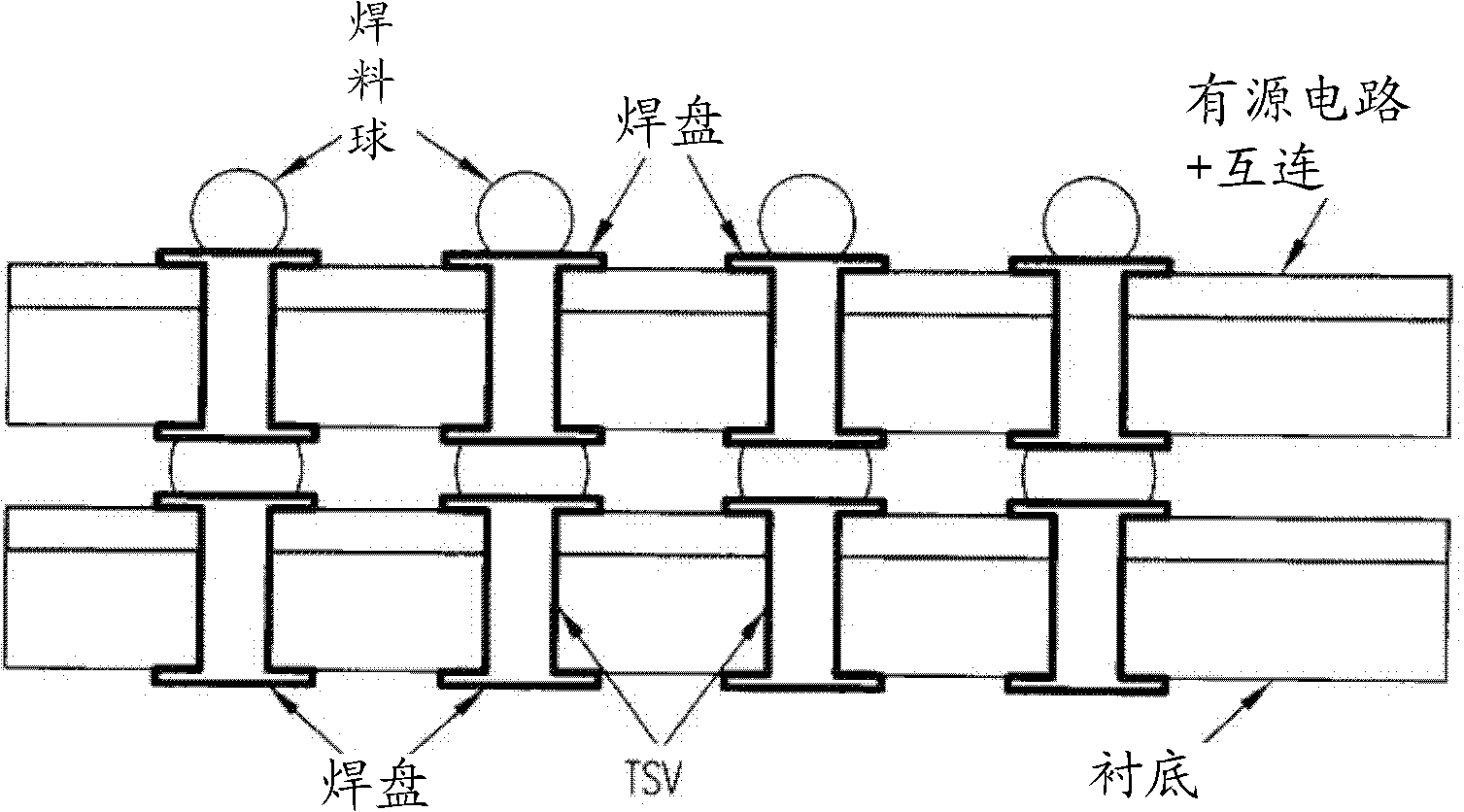

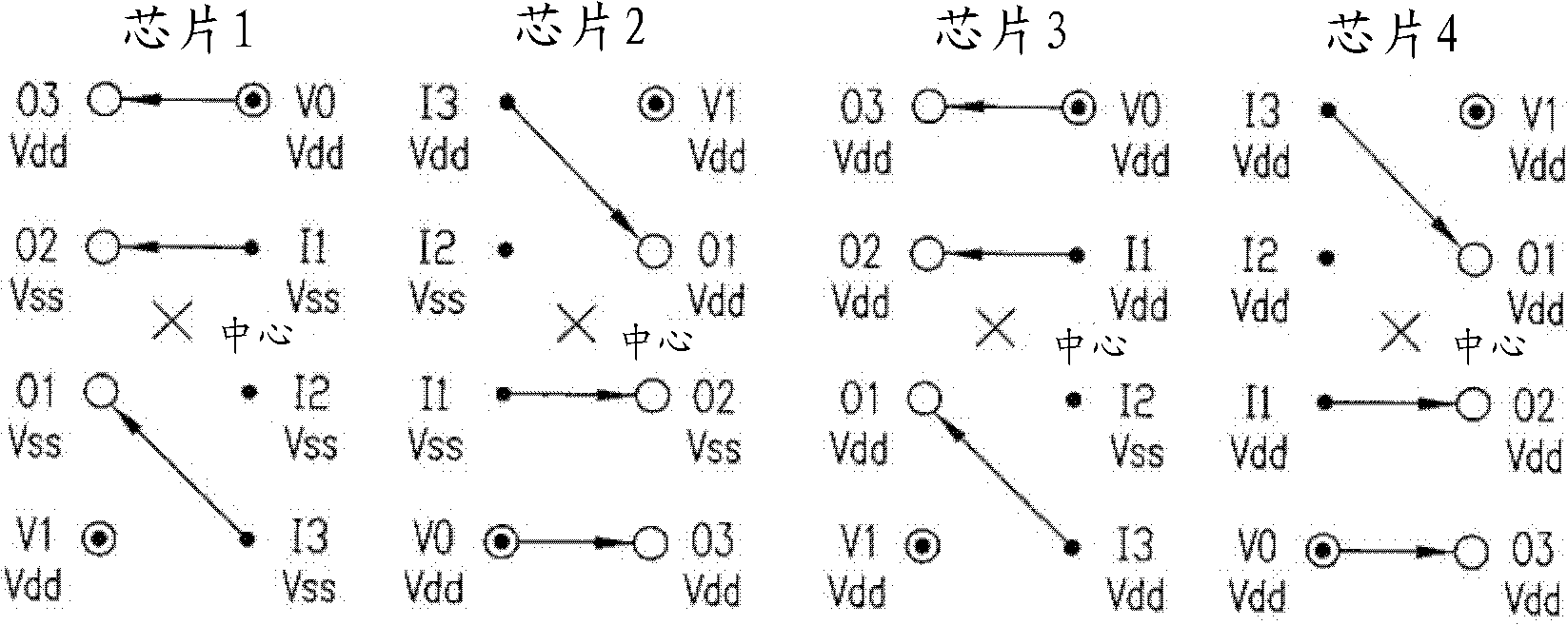

[0024] Exemplary embodiments of the present invention use discontinuous TSVs that provide series connection through successive integrated circuit die in a stack without the need to rotate the die. With discontinuous TSVs, the connection between the bottom and top pads is broken to allow connections other than direct (non-discontinuous) vertical connections.

[0025] image 3 An example of stacked chips interconnected with discontinuous TSVs according to the invention is shown, which provides connections that are not direct vertical connections. The TSVs at A are conventional non-interrupted vertical connections between pads on the bottom surface of the die and the top metal layer, and the TSVs at B, C, and D are interrupted TSVs.

[0026] There are multiple conductive layers within the active circuitry and interconnect areas of the chip. Current logic processes have 9 or more layers of metal interconnects. The top metal layer is denoted here as metal n and the bottom layer ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More