Multi-core processor sytem, control program, and control method

A technology of multi-core processors and control methods, which is applied in the directions of multi-program device, program control design, program startup/switching, etc., can solve the problems of interrupt response delay and achieve the effect of high-speed response time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

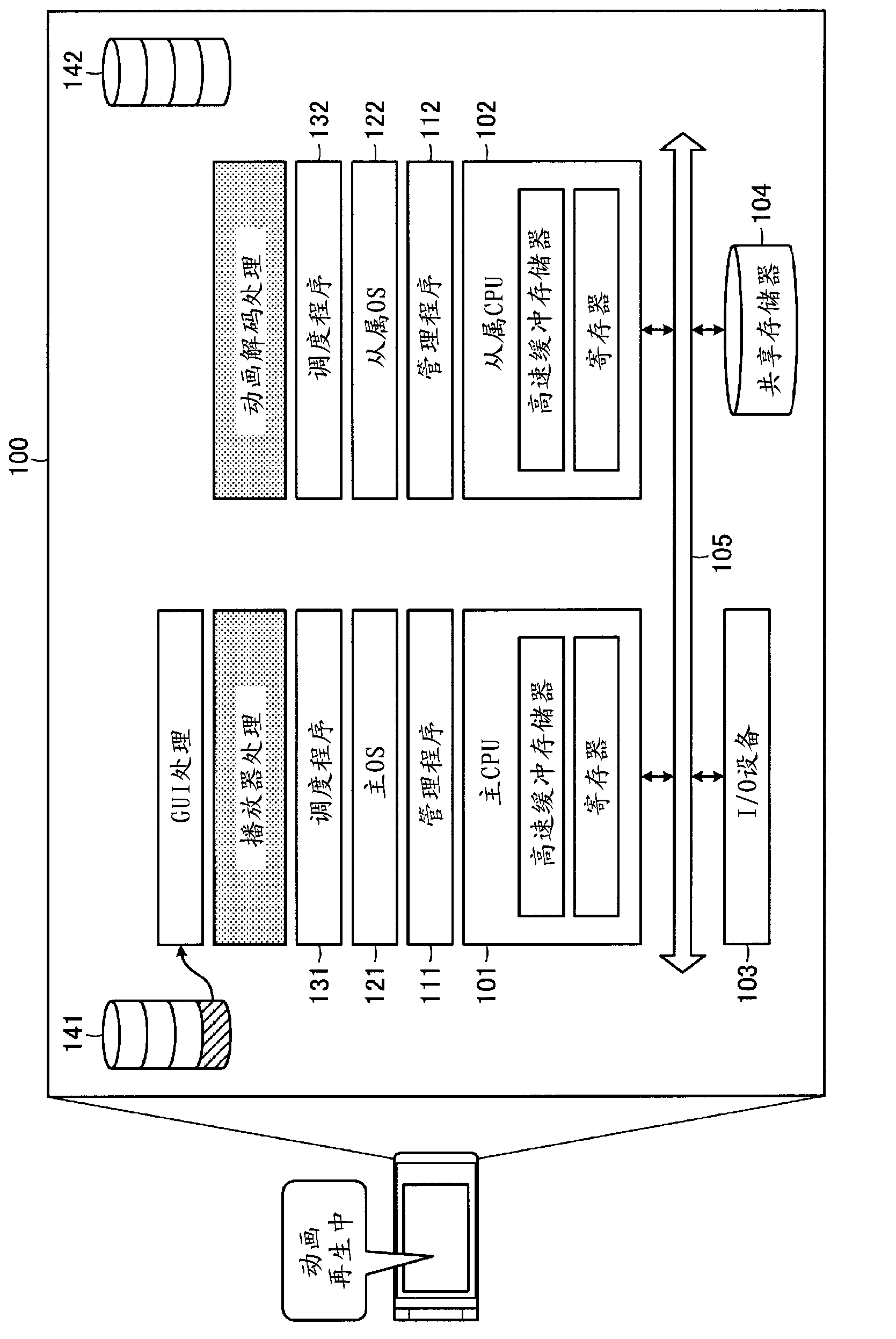

Embodiment 1)

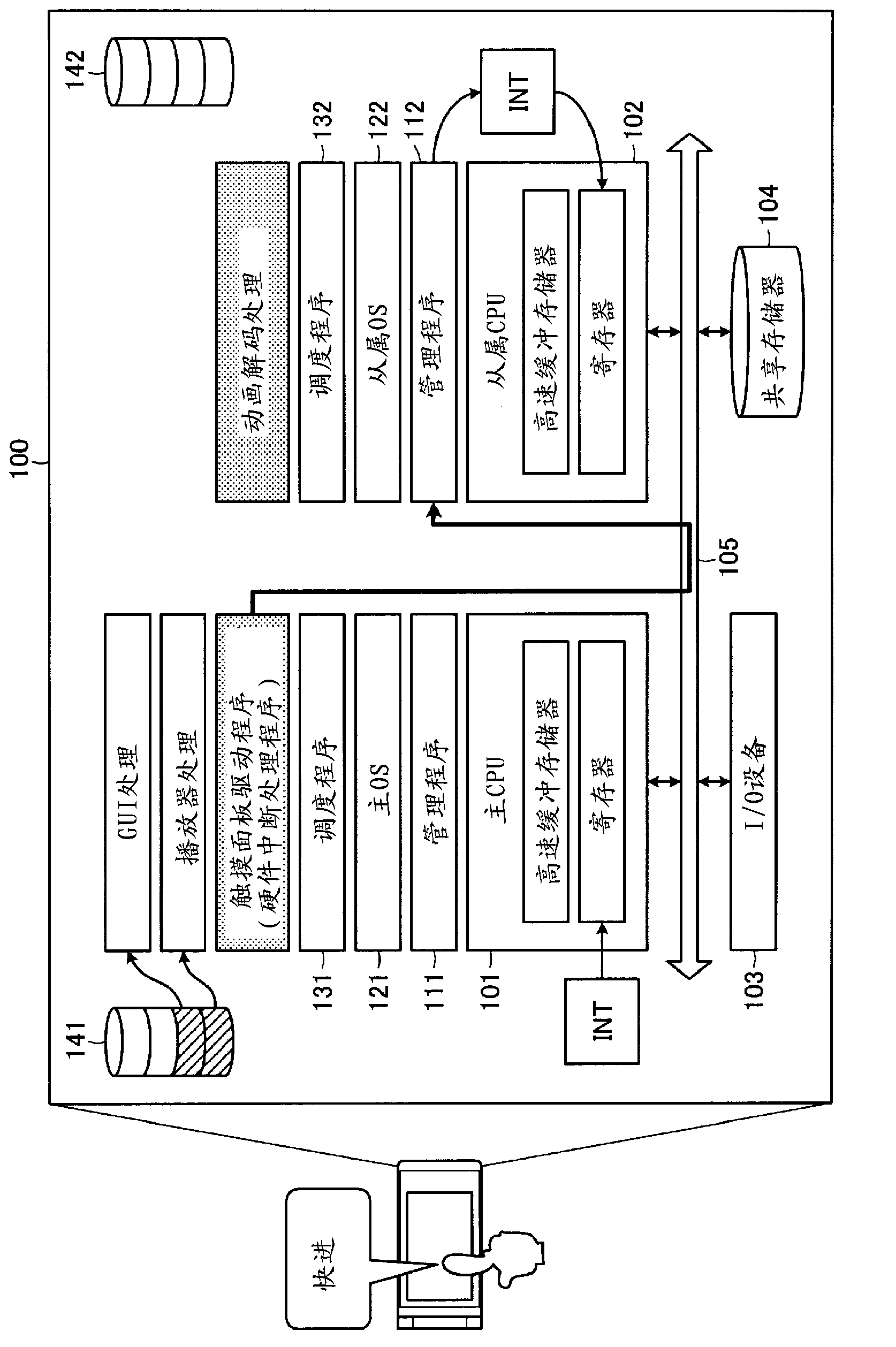

[0060] Figure 7 It is an explanatory drawing showing Example 1. First, (1) when a hardware interrupt request is issued to the main CPU 101 via the I / O device 103 , the main OS 121 (2) immediately withdraws the task A being executed by the main CPU 101 .

[0061] Then, the main OS 121 ( 3 ) executes the hardware interrupt processing program of the hardware interrupt request. Then, the main OS 121 uses the process table 151 to specify the CPU assigned the task of receiving the interrupt by the software interrupt handler called by the hardware interrupt handler. Here, the task that received the interrupt is defined as task B, and the slave CPU 102 is specified as the CPU to which task B is assigned. Then, master OS 121 ( 4 ) notifies slave CPU 102 of a software interrupt request through interprocessor interrupt communication.

[0062] The hypervisor 112 monitors the interprocessor communication and detects the software interrupt request. When the hypervisor 112 detects a sof...

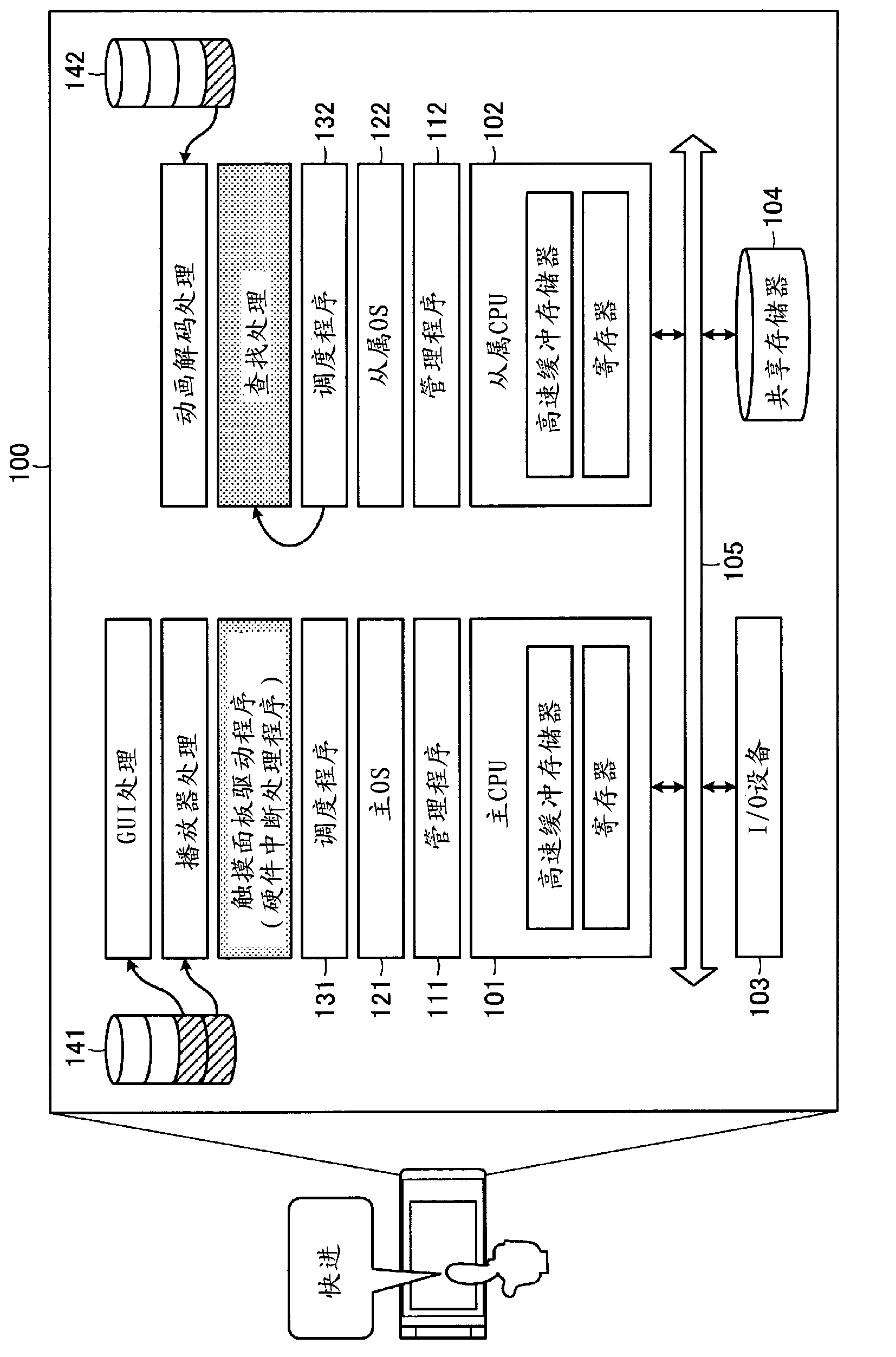

Embodiment 2)

[0074] In the second embodiment, it is explained that based on whether the task in execution is allowed to be interrupted, it is judged that a software interrupt handler with a high priority is executed immediately, or that the software interrupt handler is executed when the task in execution ends or a task is switched. example.

[0075] Here, in the second embodiment, when the task being executed does not allow interruption, the flag indicating whether the task being executed has ended or whether a task switching has occurred is set to ProcessID. If the ProcessID is 0, it means that the task is being executed; if the ProcessID is 1, it means that the task being executed has ended or a task switch has occurred.

[0076] Figure 10 It is an explanatory diagram showing an example of the use case table of the second embodiment. In the use case table 1000, there is information indicating for each function whether to forcibly execute processing at the time of interruption, inform...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More