Apparatus and method for controlling rounding when performing floating point operation

A floating-point and rounding technology, which is applied in computing, instruments, and electrical digital data processing, etc., can solve the problems affecting the performance of the processing circuit system, the performance of floating-point division operations cannot be guaranteed, and the increase in the cost and complexity of the processing circuit system

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] Before discussing the embodiments with reference to the accompanying drawings, the following description of the embodiments is provided.

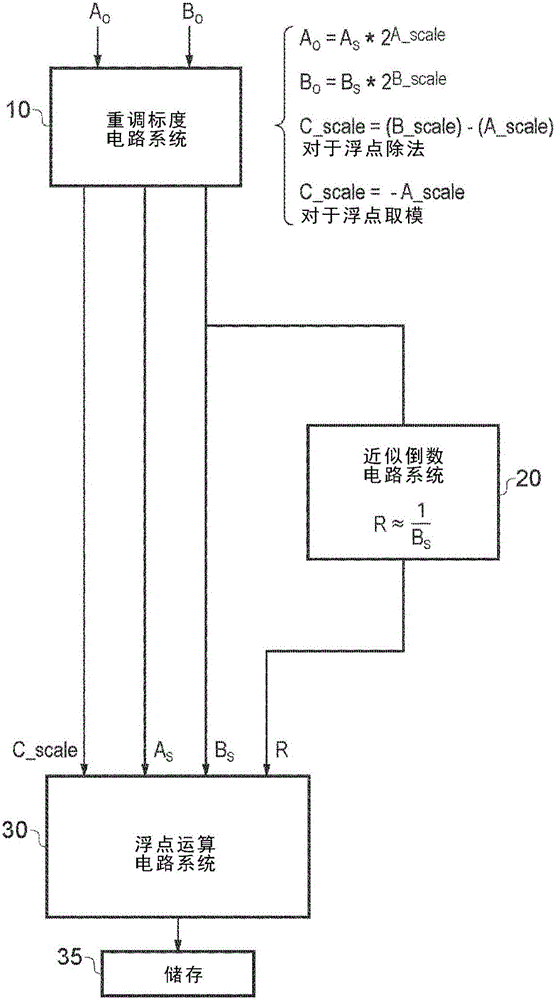

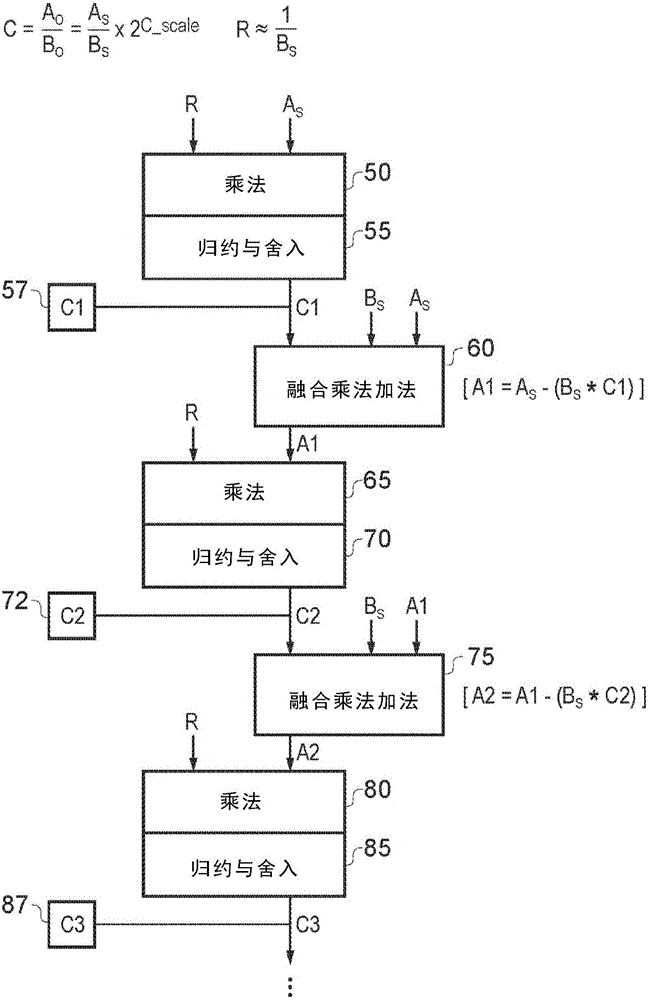

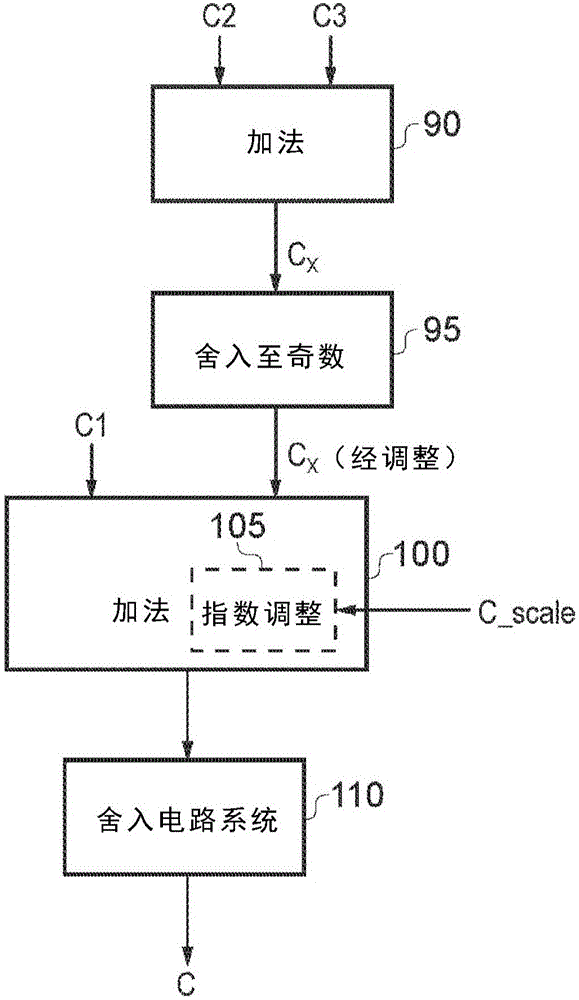

[0020] According to one embodiment, an apparatus is provided that includes argument reduction circuitry for performing an argument reduction operation. Additionally, reduction and rounding circuitry is provided to generate a modified floating point value from the provided floating point value for input to the argument reduction circuitry. The reduction and rounding circuitry modifies the significand of the provided floating point value based on a specified value N to produce a truncated significand with the specified rounding applied. The truncated significand is N bits shorter than the significand of the provided floating point value and is used as the significand of the modified floating point value. The specified value N is chosen such that an argument reduction operation performed using the modified floating-point value suppress...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com