VLSI (Very Large Scale Integration) layout design method for solving given border constraint

A technology of layout design and border, applied in CAD circuit design, calculation, special data processing applications, etc., can solve problems such as difficult to solve directly, large scale, etc., to meet the needs of layout planning and design, and effectively and practically the effect of layout planning results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

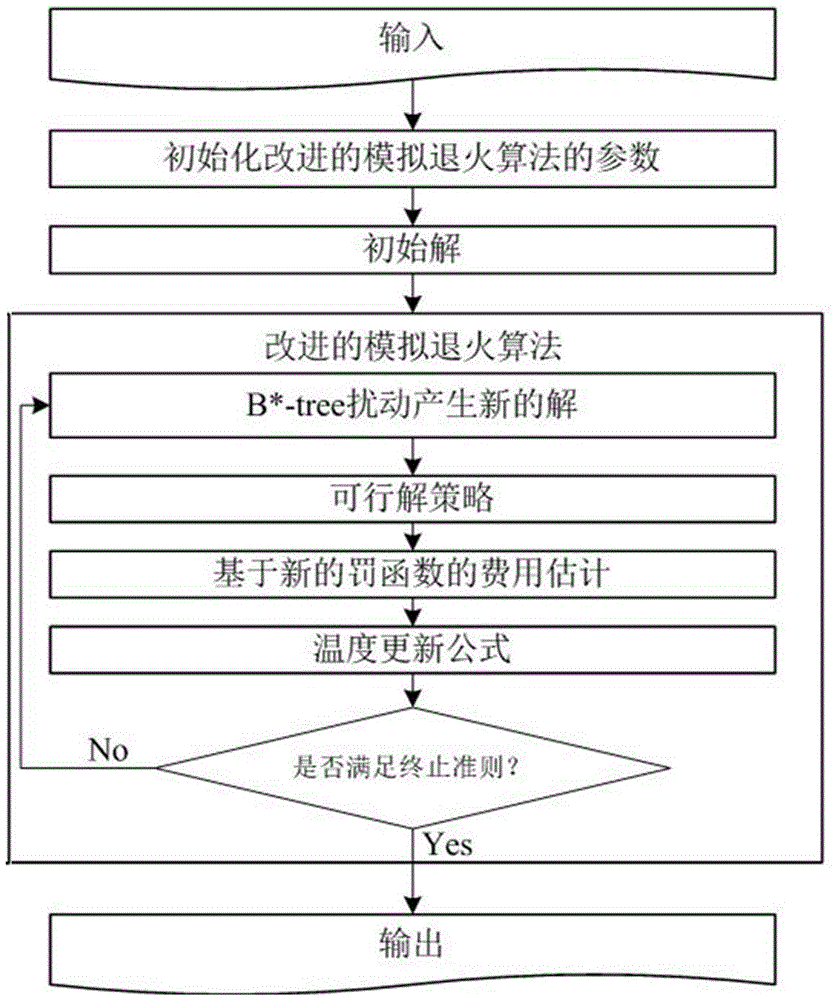

[0062] The technical solution of the present invention will be specifically described below in conjunction with the accompanying drawings.

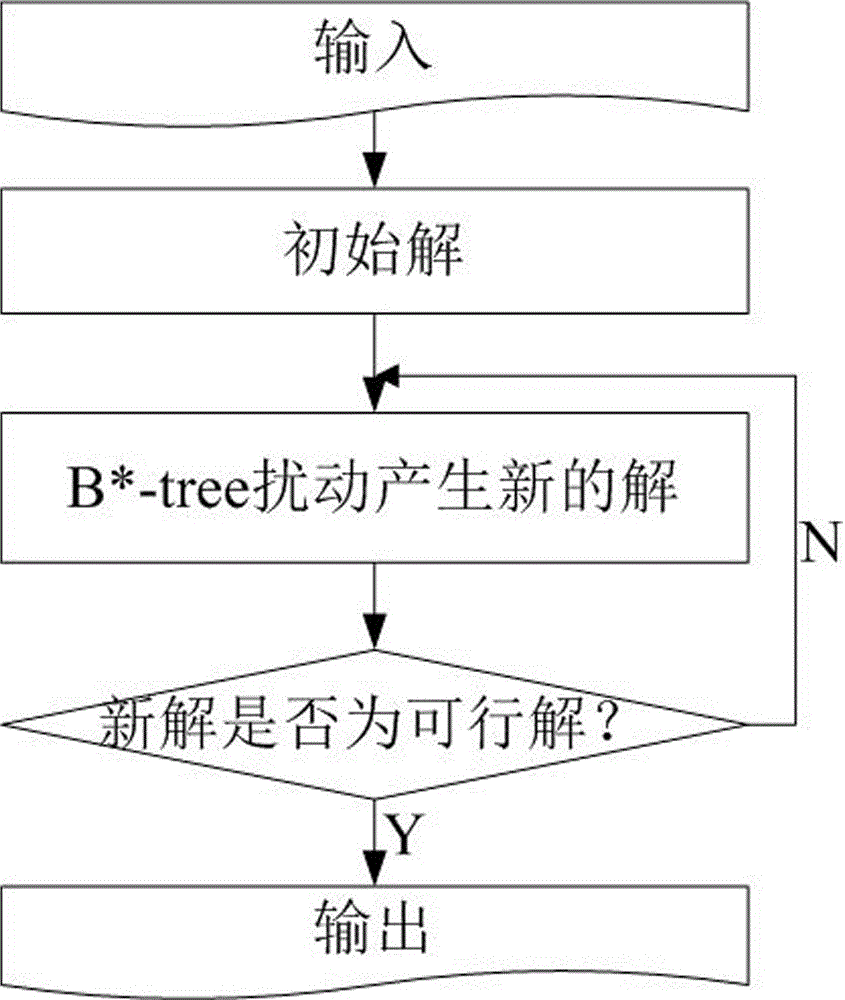

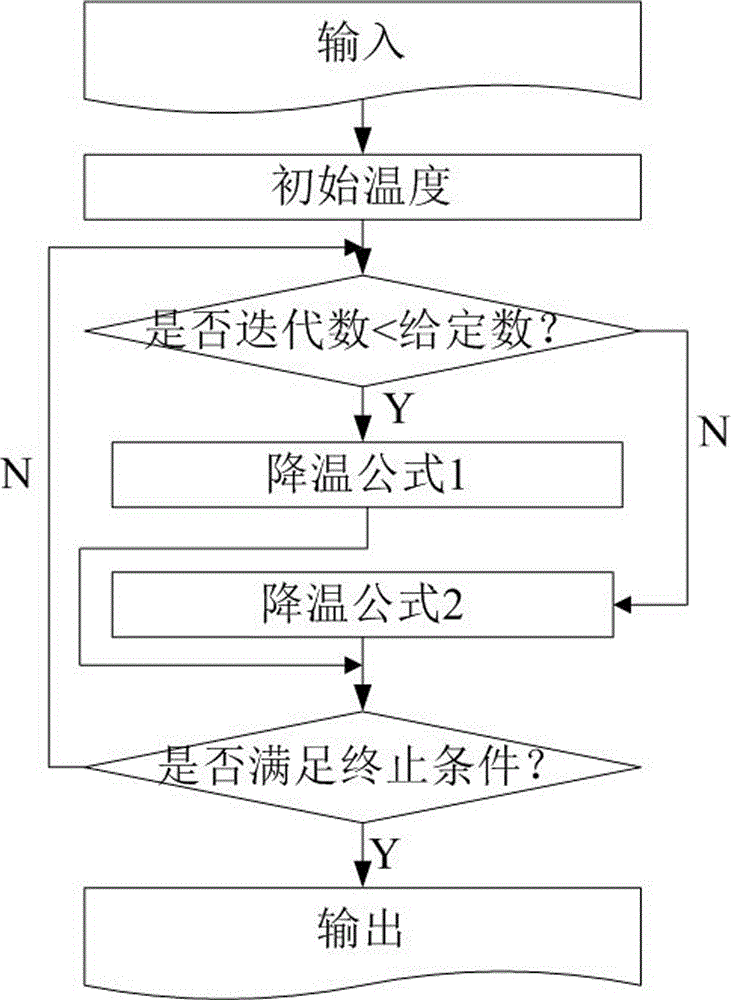

[0063] The invention provides a VLSI layout design method for solving a given border constraint, and aims to use a hybrid simulated annealing algorithm to deal with the layout planning problem of a given border constraint that cannot be divided into two in VLSI. The algorithm uses a penalty function based on the combination of the area violation function and the length violation function, and then uses the feasible solution strategy to make the new solutions that satisfy the bounding box constraints feasible solutions. Finally, the hybrid simulated annealing algorithm is used to search the solution space of the problem. Therefore, a layout planning result with a given border constraint based on an iterative method with superior performance is obtained.

[0064] Furthermore, the present invention proposes a hybrid simulated annealing-based...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More