A preparation method and structure of a three-dimensional memory

A memory, three-dimensional technology, applied in the direction of semiconductor devices, electric solid state devices, electrical components, etc., can solve the problems of contact failure, uncontrollable wafer stress, contact hole 17 growth, etc., to reduce wafer bending and improve macroscopic stress. The effect of distribution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0030] refer to Figure 5-10 As shown, Embodiment 1 of the present invention proposes a method for preparing a three-dimensional memory, which is characterized in that it includes the following steps:

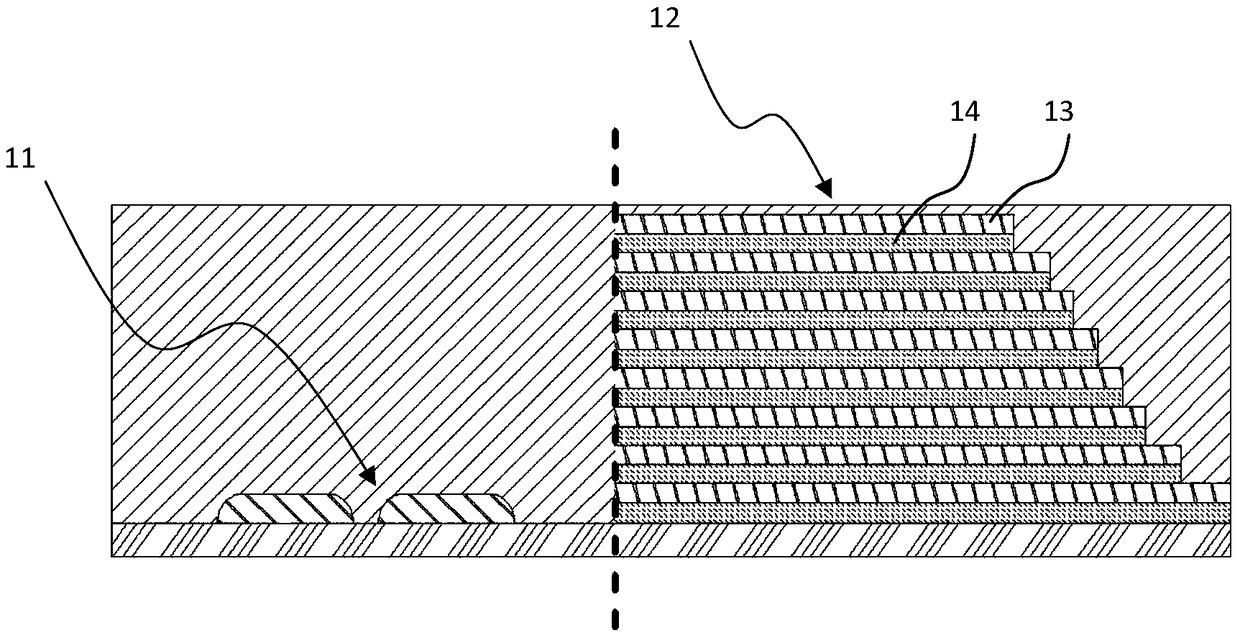

[0031] Such as Figure 5 As shown, a substrate 20 is provided, on which a peripheral circuit area 21 and an array storage area 22 of a three-dimensional memory are formed; preferably, forming the array storage area 22 includes alternately forming silicon nitride on the substrate 20 A multilayer stack structure of layer 23 and silicon oxide layer 24; using a photolithography process to form a step region 25 on at least one side of the multilayer stack structure so that a part of the upper surface of each silicon nitride layer 23 is exposed to the step region 25.

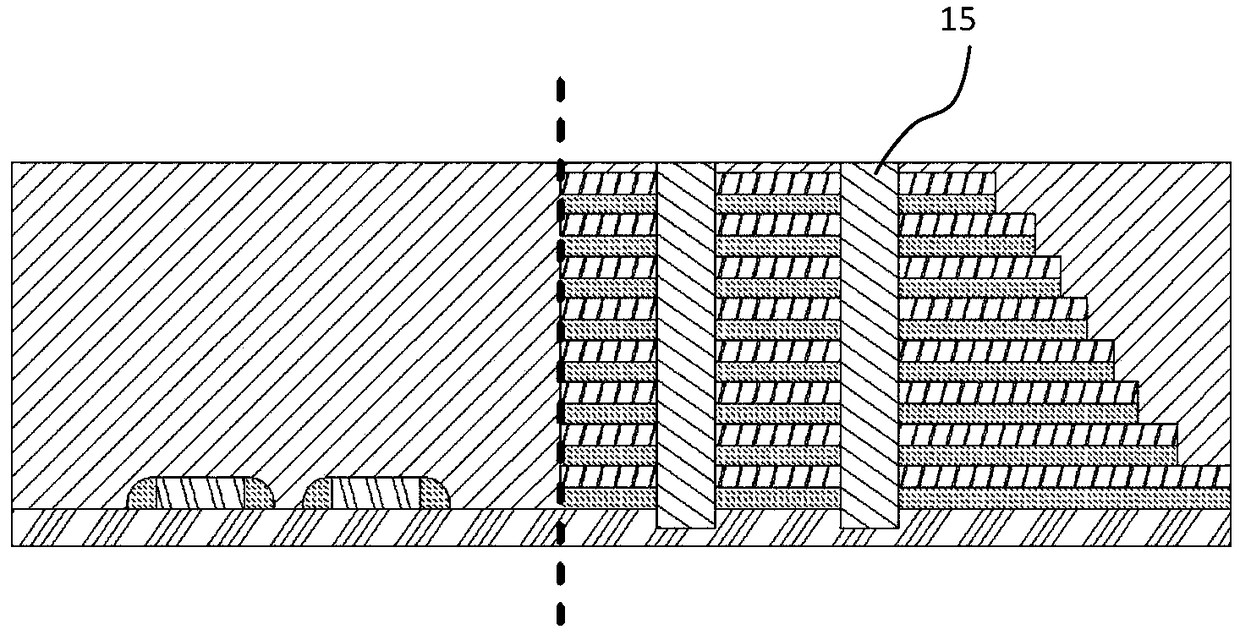

[0032] Forming an insulating layer 26 with a flat surface on the substrate 20 to cover the peripheral circuit area 21 and the array storage area 22;

[0033] Such as Image 6 As shown, the insulating layer 26 on th...

Embodiment 2

[0038] Embodiment 2 of the present invention proposes a method for preparing a three-dimensional memory, which is characterized in that it includes the following steps:

[0039] Such as Image 6As shown, preferably, after the insulating layer 26 on the peripheral circuit region 21 is patterned, etched and filled with metal to form a plurality of first contact holes 27 electrically connected to the peripheral circuit region 21, It also includes the step of performing a chemical mechanical mask on the surface of the substrate 20 .

[0040] Such as Figure 7 As shown, preferably, after the step of performing a chemical mechanical mask on the surface of the substrate 20, a step of depositing a silicon dioxide cap layer 31 on the substrate 20 is also included to protect the first contact hole 27 The metal fill in is not damaged by subsequent processes.

[0041] Preferably, the thickness of the silicon dioxide cap layer is greater than 3000 angstroms.

Embodiment 3

[0043] Embodiment 3 of the present invention proposes a method for manufacturing a three-dimensional memory. In this embodiment, parts different from those in the above embodiments will be described, and the same parts will not be described again.

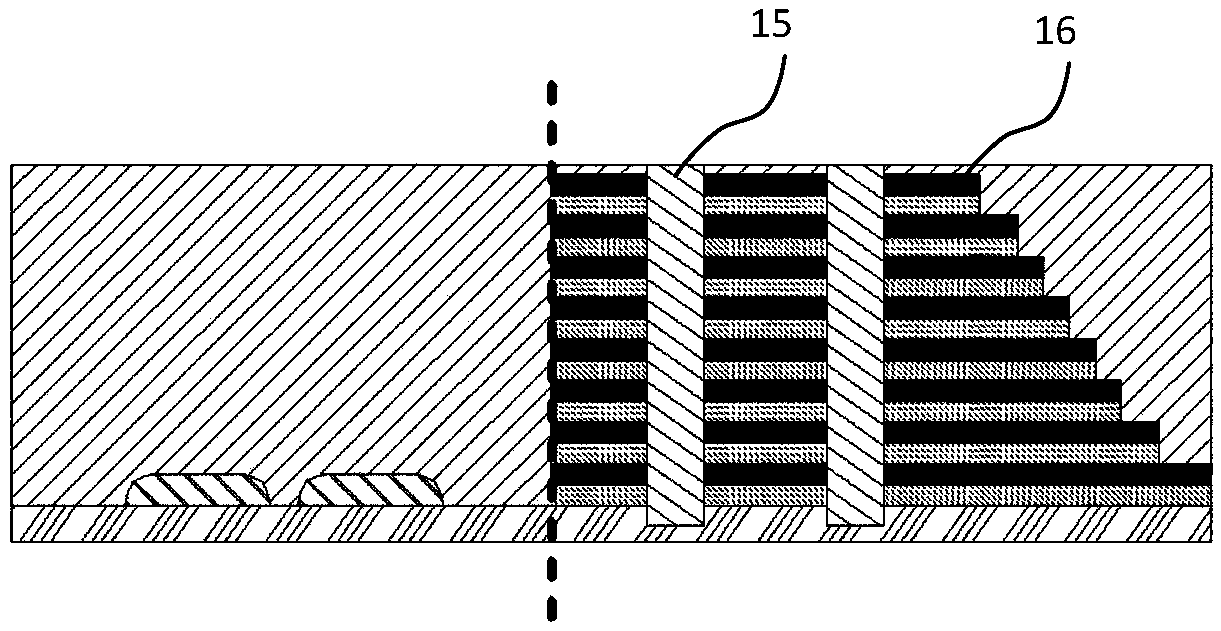

[0044] Such as Figure 9 As shown, preferably, after forming the metal gate 29 of the memory cell in the array storage area 22 , a step of depositing a silicon dioxide filling layer 32 on the silicon dioxide cap layer 31 is also included.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More