A FPGA-based Dynamically Reconfigurable Video Scaler

A technology of video scaling and reconfiguration, which is applied in the fields of digital video signal modification, image communication, electrical components, etc., which can solve the problems such as the inability to meet the new index requirements and affecting the video delay of the superimposed acquisition of the head-up display.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] Embodiments of the present invention are described in detail below, and the embodiments are exemplary and intended to explain the present invention, but should not be construed as limiting the present invention.

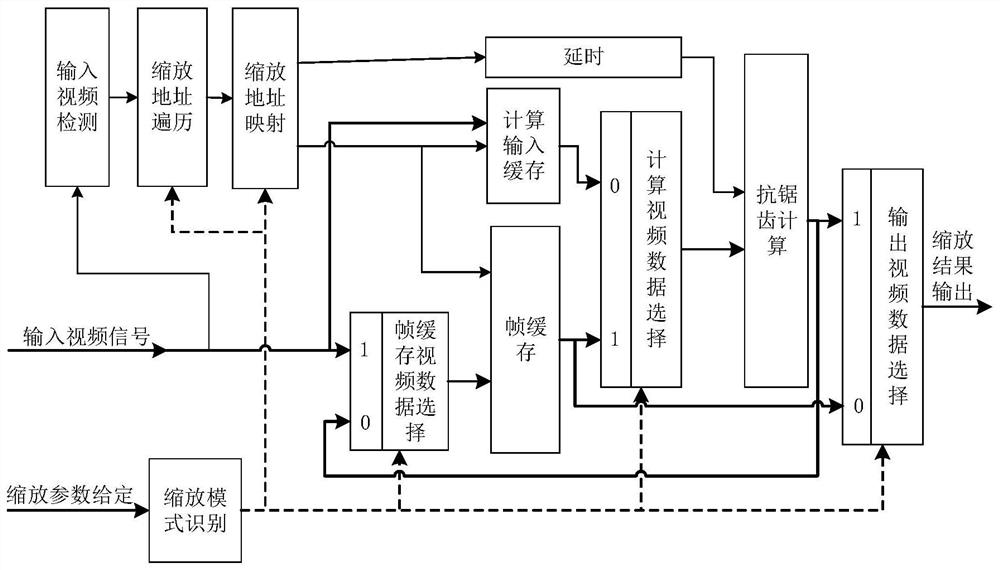

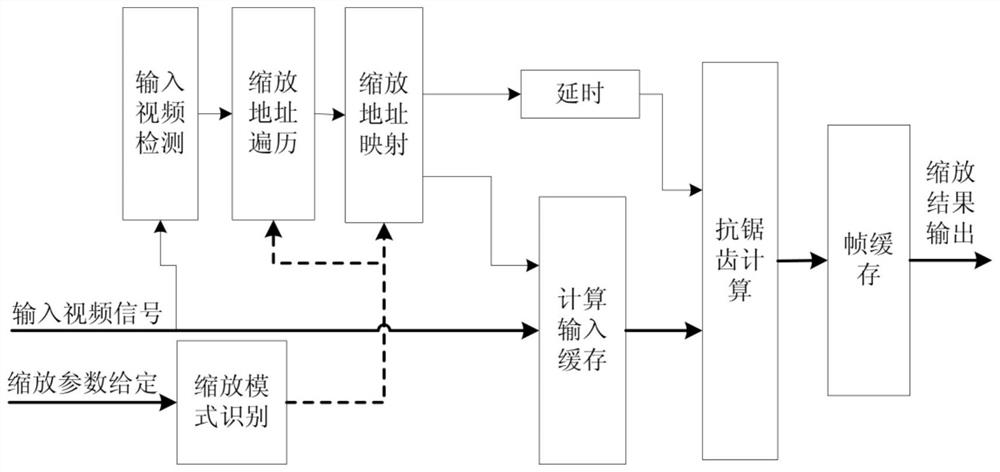

[0029] The FPGA-based dynamic reconfigurable video scaler, the logic architecture is implemented based on FPGA or CPLD, and consists of input video detection, scaling address traversal, scaling address mapping, frame buffer video data selection, calculation input buffer, frame buffer, and calculation video data selection , time delay, anti-aliasing calculation, output video data selection and scaling mode recognition unit.

[0030] The output end of the scaling mode identification unit is connected to the control input ends of the scaling address traversal unit, scaling address mapping unit, frame buffer video data selection unit, calculation video data selection unit and output video data selection unit through instruction signal lines. The scaling mode recog...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More