Universal JTAG debugging card and test method thereof

A test method and technology for debugging cards, which are applied in the directions of error detection/correction, detection of faulty computer hardware and instruments, etc., can solve problems such as reducing the time limit of board debugging, improving the difficulty of board debugging, fault location and abnormal processing, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

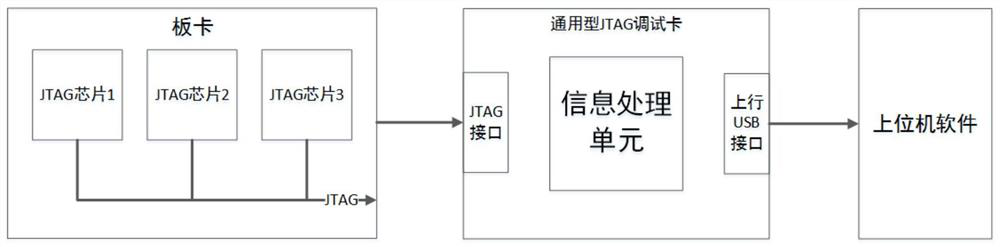

[0027] combined with figure 1 , the present embodiment proposes a general-purpose JTAG debug card, which has a JTAG interface, an information processing unit, and an uplink USB interface;

[0028] The general-purpose JTAG debug card communicates with the JTAG chip on the board through the JTAG interface;

[0029] The information processing unit obtains the register status information of the JTAG chip on the board through a broadcast;

[0030] The general-purpose JTAG debug card transmits the register information obtained from the JTAG chip to the external host computer software through the upstream USB interface. The host computer software integrates the register function definition information of the JTAG chip, which is used to parse the received information into function configuration information and display it to the user. before.

[0031] One, two, or even multiple JTAG chips can be arranged on the board. In this embodiment, three JTAG chips are referred to as JTAG chip ...

Embodiment 2

[0033] combined with figure 1 , the present embodiment proposes a test method based on a general-purpose JTAG debug card, and the realization of the test method is based on three parts of a board, a general-purpose JTAG debug card, and host computer software, wherein:

[0034] A JTAG chip is arranged on the board;

[0035] The general-purpose JTAG debug card has a JTAG interface, an information processing unit, and an uplink USB interface. The general-purpose JTAG debug card communicates with the JTAG chip on the board through the JTAG interface. Register status information, the general-purpose JTAG debug card transfers the register information of the JTAG chip to the external host computer software through the uplink USB interface;

[0036] The upper computer software integrates the register function definition information of the JTAG chip, which is used to parse the received information into function configuration information and display it in front of the user, so that the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More