System and method of determining memory ownership on cache line basis for detecting self-modifying code including modification of a cache line with an executing instruction

a cache line and memory ownership technology, applied in the field of memory ownership, can solve problems such as improper or unintended operation, dcache which is a slow and tedious process, and subsequent modification by sm

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

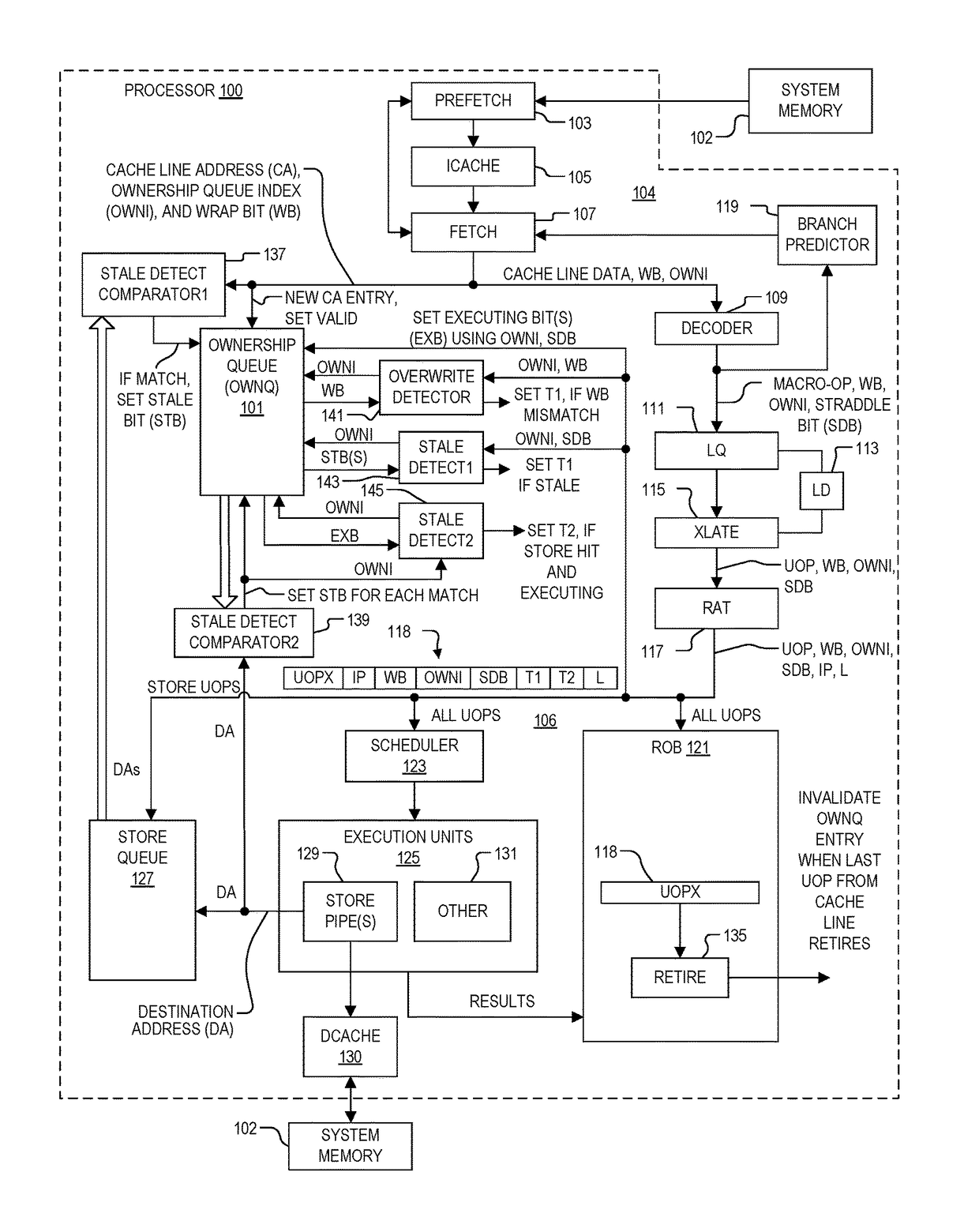

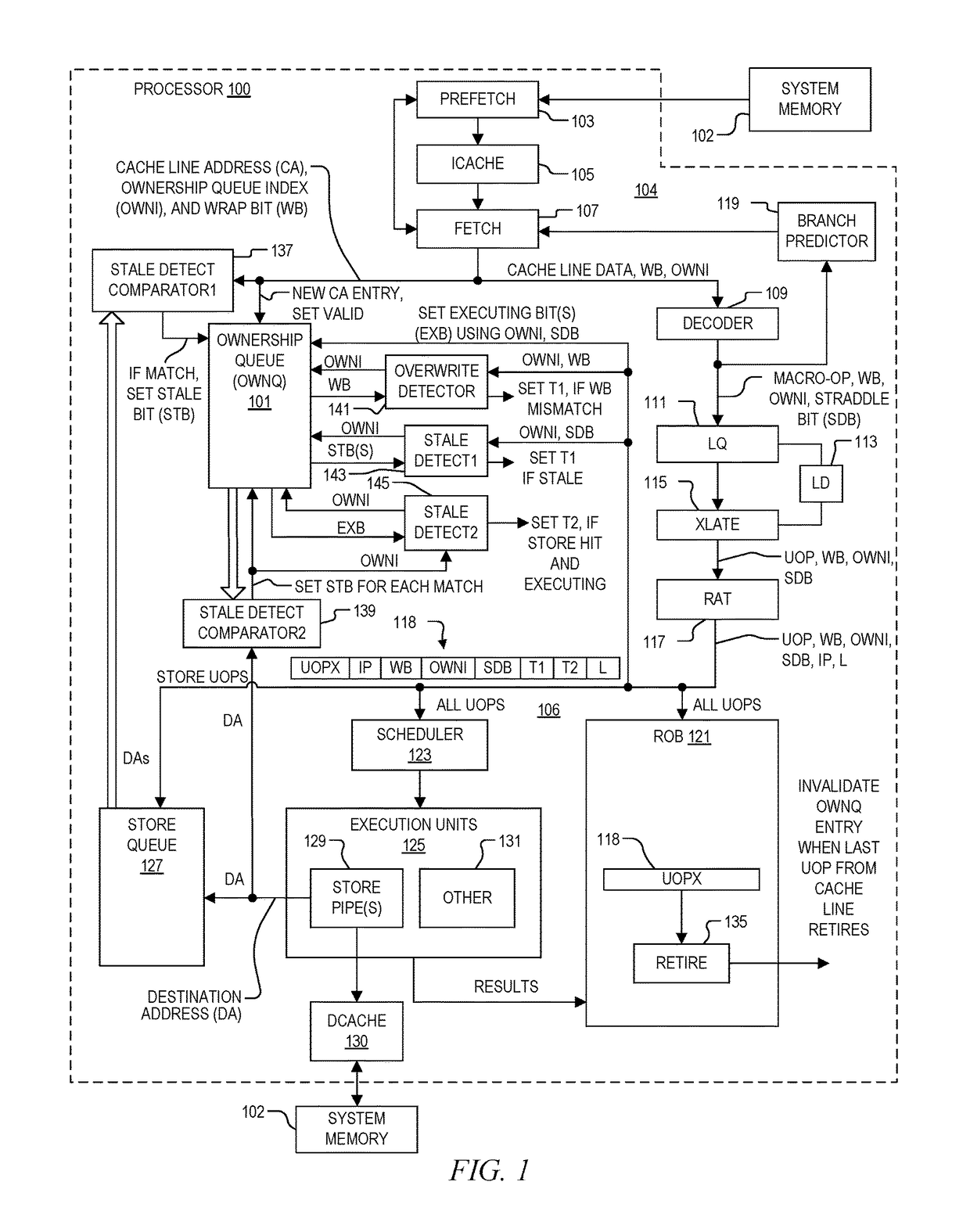

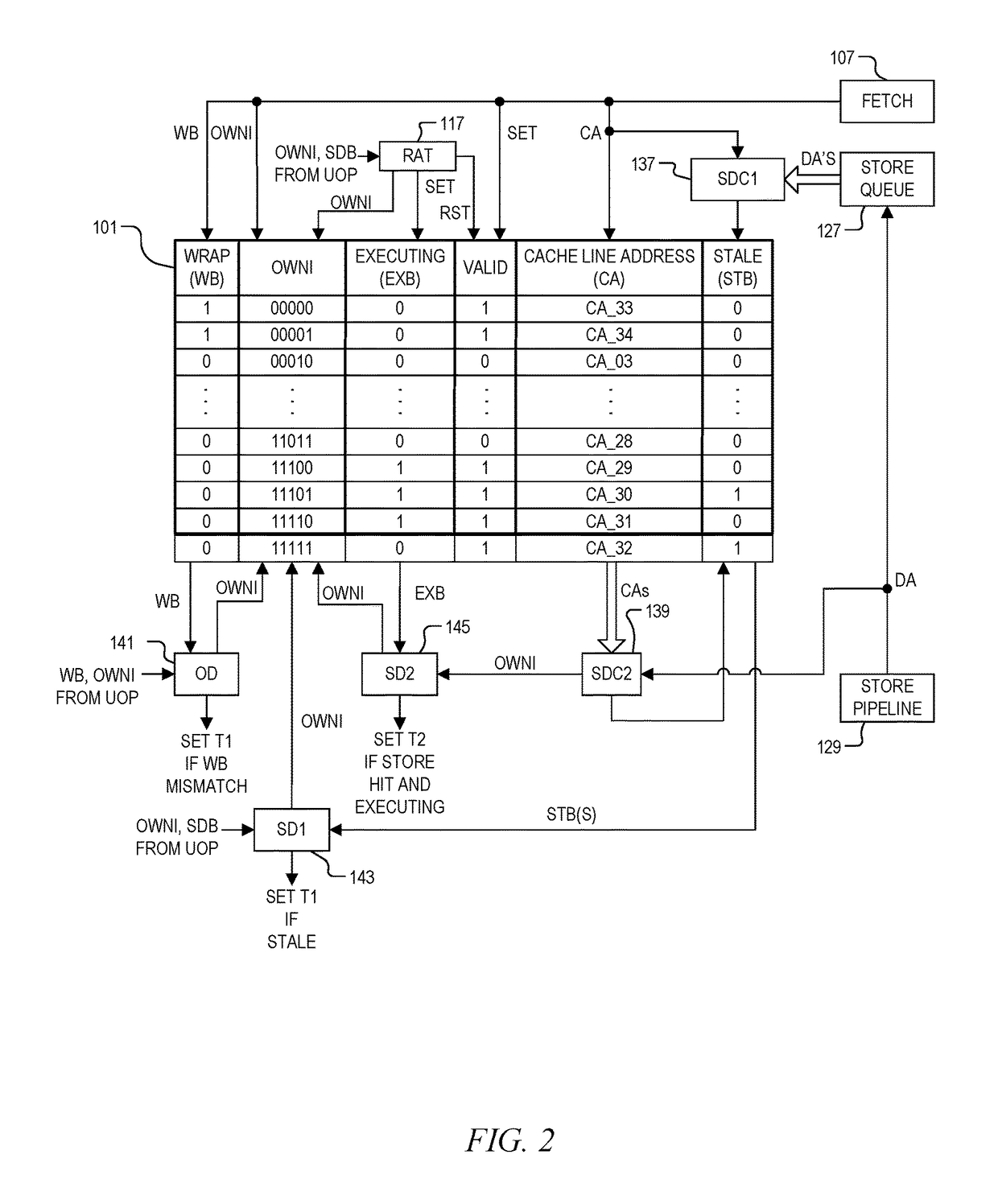

[0025]The inventors have recognized the problems of memory ownership in view of self-modifying code (SMC). They have therefore developed a system and method of establishing memory ownership on a cache line basis using an ownership queue which may be used for detecting SMC including modification of cache lines with executing instructions. An ownership index is determined for each cache line entered into the ownership queue. Each cache line is translated into instructions, and a corresponding ownership index is included with each instruction. As each instruction is issued for execution, an executing bit of the corresponding entry in the ownership queue is set. A destination address is determined for each store instruction that has been issued. A new destination address comparator compares each newly determined destination address, when determined, with each cache line address of valid entries stored in the ownership queue to determine any matching entries. An executing stale detector ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More