High-effective VLSI implement structure of JEPG2000 medium-small wave transformation algorithm

A wavelet transform and address technology, which is applied in the field of VLSI implementation structure of discrete wavelet transform units, can solve the problems of system storage unit distribution and scheduling not being elaborated in detail, structural flexibility and processing speed are not very ideal, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

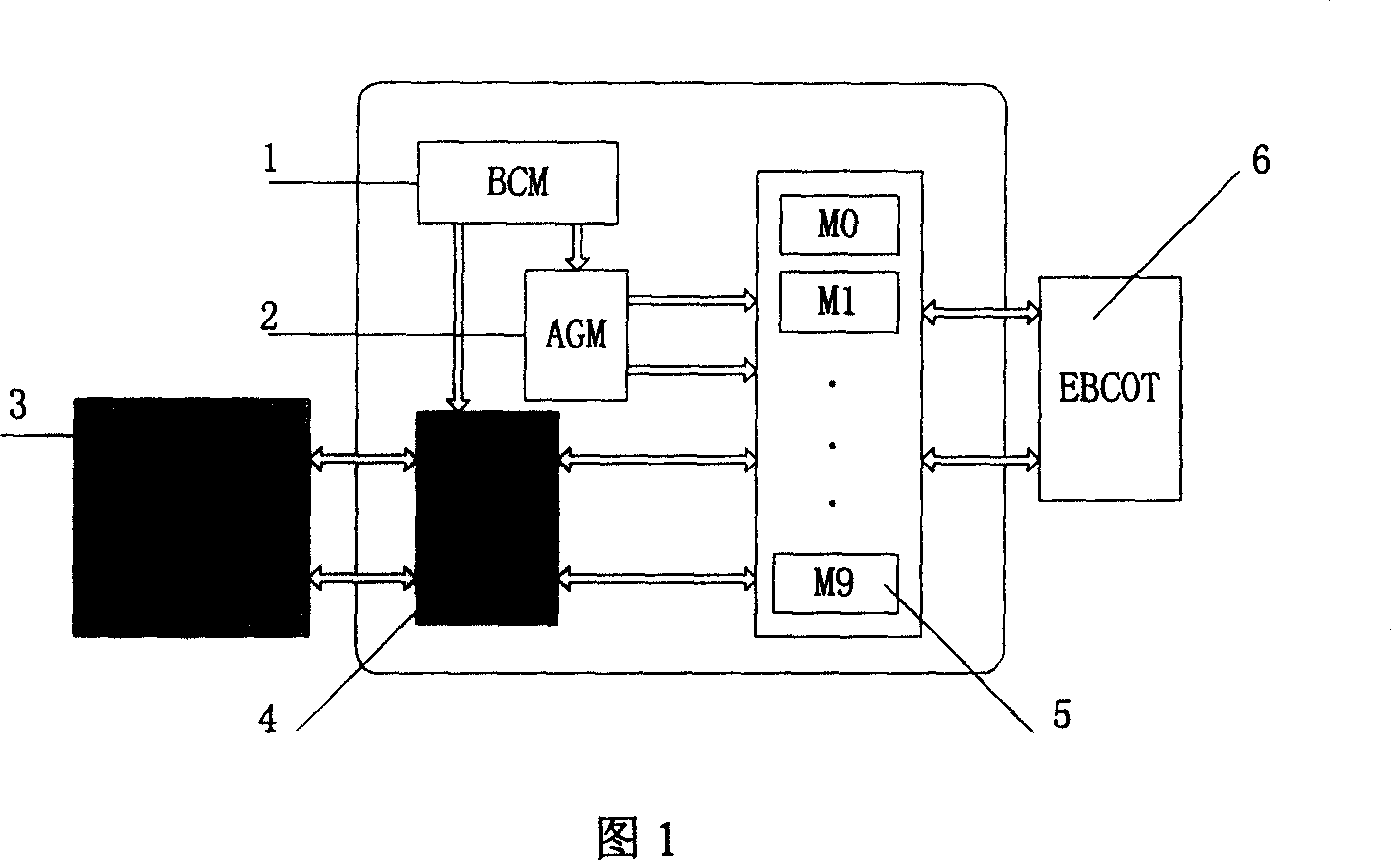

[0034] Basic Control Unit

[0035] The basic control unit is responsible for the control and data scheduling of each module in the control system, including: when controlling the forward / reverse wavelet transform, the address generation unit (AGU) generates address signals for reading / writing external storage units; when controlling the forward / reverse wavelet transform The address generation unit (AGU) generates the address signal for reading / writing the internal storage unit; controls the data scheduling of the pipeline processing of the wavelet processing unit during the forward / reverse wavelet transformation; controls the data extension mode selection of the wavelet processing unit, etc. The unit is mainly based on a two-way countable counter, and the counting range of the counter is: (0-M-1); M is given by formula (1):

[0036] M = N × N 2 + ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More