Decoder device of multi-code LDPC code and decoding method

A technology of LDPC codes and decoders, which is applied to the application of multi-bit parity error detection coding, error correction/detection using block codes, data representation error detection/correction, etc., which can solve the problem of high hardware resource consumption. , decoding rate reduction and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

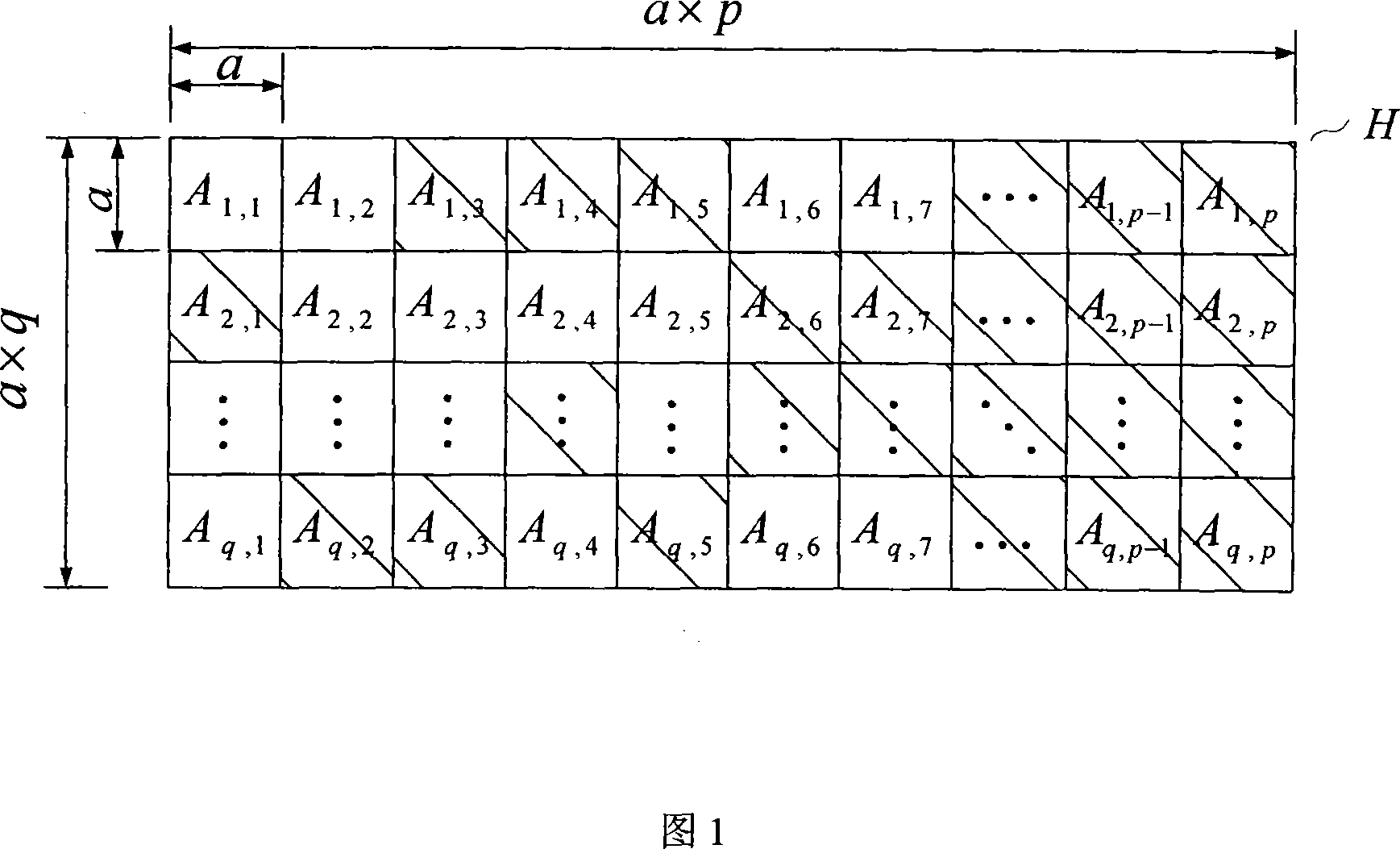

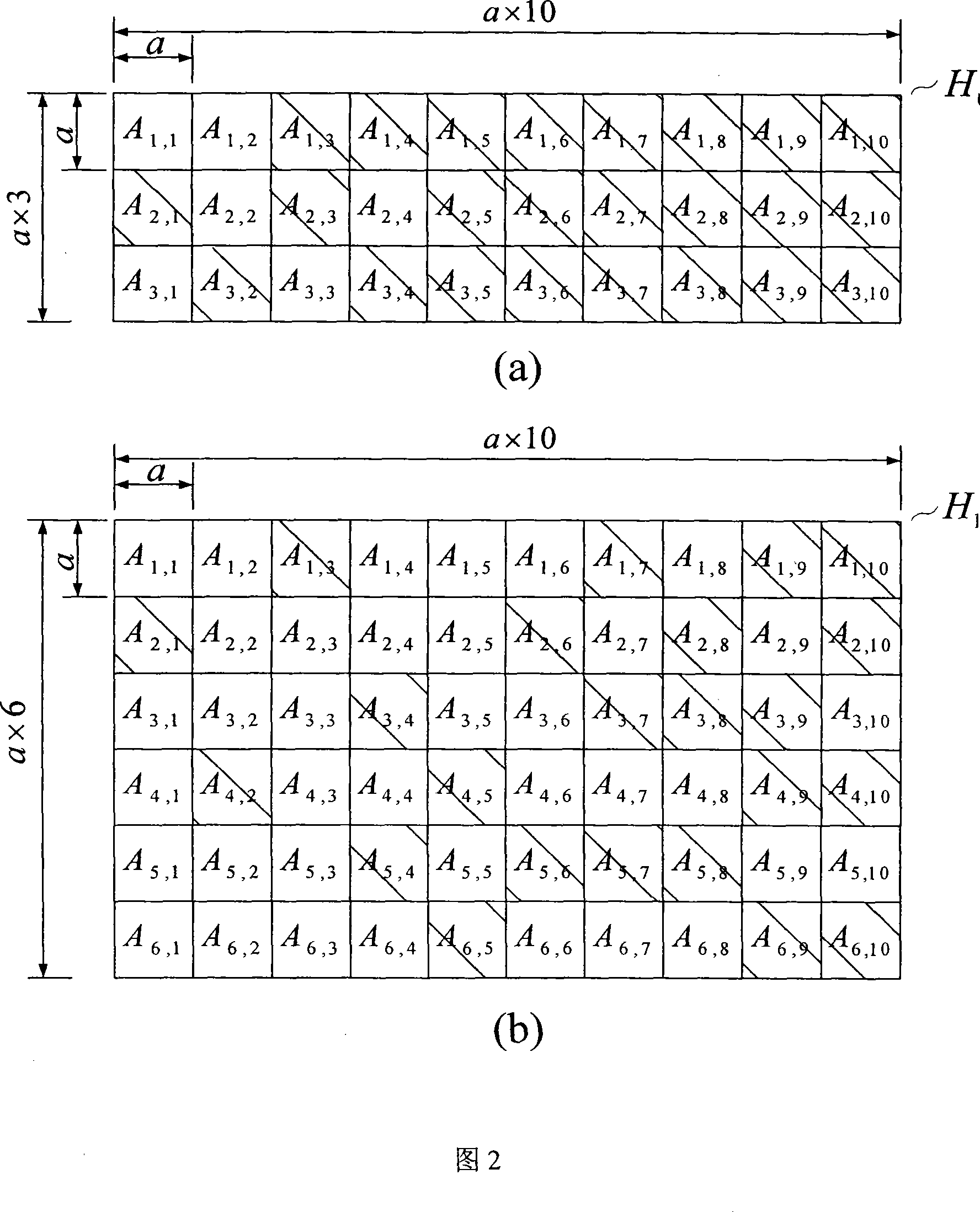

[0036] This embodiment is used for the H shown in Figure 2 0 and H 1 Corresponding high and low dual rate LDPC code decoding. Among them, H 0 Corresponding to the high code rate LDPC code, H 1 Corresponding to the low code rate LDPC code.

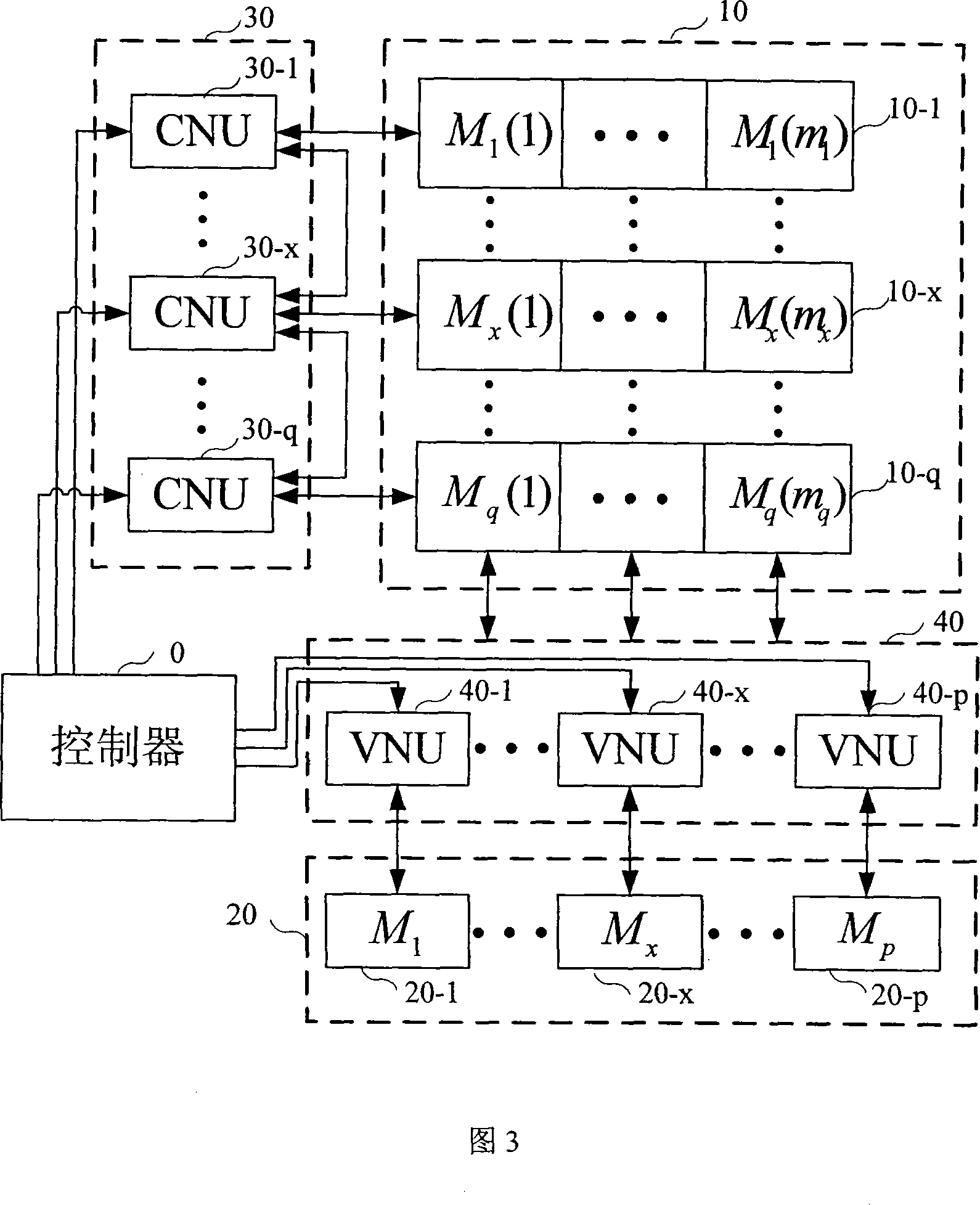

[0037] As shown in FIG. 3 , the decoder in this embodiment includes the following parts: check node operation unit CNU set 30, including q check node operation units, respectively 30-1, ..., 30-x, ... , 30-q. In this example, H 0 The number of row blocks q 0 for 3, H 1 The number of row blocks q 1 is 6, q 0 and q 1 The least common multiple of is 6, so q is 6. for H 0 In terms of, the first q / q in these q CNUs 0 , that is, the first and second CNUs jointly complete the check node update operation of the first row block, and the next q / q 0 CNUs, that is, the third and fourth CNUs jointly complete the check node update operation of the second row block, and the final q / q 0 CNUs, that is, the fifth and sixth CNUs jointly complet...

Embodiment 2

[0078] This embodiment is used for the H shown in Figure 8 2 and H 3 Corresponding high and low dual rate LDPC code decoding. Among them, H 2 Corresponding to the high code rate LDPC code, H 3 Corresponding to the low code rate LDPC code. Compared with Embodiment 1, only the determination method and grouping of the number of CNUs q are different in this embodiment, which are described as follows:

[0079] In this example, H 2 The number of row blocks q 2 for 3, H 3 The number of row blocks q 3 is 5, and as previously stated, the q 3 Add a small integer to q 3 ',q 3 ' is 5, 6, 7, 8, . . . Therefore, q 2 with these several q 3 The least common multiples of ' are respectively 15, 6, 21, 24, ..., so, take q as the minimum value 6 among these least common multiples. for H 2 In terms of, the first q / q in these q CNUs 2 , that is, the first and second CNUs jointly complete the check node update operation of the first row block, and the next q / q 2 CNUs, that is, the t...

Embodiment 3

[0082] This embodiment is used for the H shown in Figure 9 4 , H 5 and H 6 Corresponding decoding of LDPC codes with high, medium and low code rates. Among them, H 4 Corresponding to the high code rate LDPC code, H 5 Corresponding to the LDPC code of the medium code rate, H 6 Corresponding to the low code rate LDPC code. Compared with Embodiment 1, this embodiment also needs to consider the parity check matrix H of the medium code rate when determining the number of CNUs q 5 related information. All the other parts are similar to Example 1. Now describe as follows: In this embodiment, H 4 The number of row blocks q 4 for 2, H 5 The number of row blocks q 5 for 4, H 6 The number of row blocks q 6 is 6, q 4 ,q 5 and q 6 The least common multiple of is 12, so q is taken as 12. for H 4 In terms of q / q 4 It is equal to 6. Therefore, these 12 CNUs are divided into 2 groups, each group has 6 CNUs, and these 2 groups of CNUs complete the check node update operation ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More