Apparatus and method for activating and providing multi-core configuration on bus

A bus, enabling technology, applied in the field of microelectronics, which can solve problems such as timing offset and high frequency noise

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] In order to make the features and advantages of the present invention more comprehensible, preferred embodiments are specifically cited below, together with the attached drawings Figure 1 to Figure 8 , to explain in detail. The description of the present invention provides different examples to illustrate the technical features of different implementations of the present invention. Wherein, the configuration of each element in the embodiment is for illustration, not for limiting the present invention. Moreover, part of the symbols in the figures in the embodiments is repeated, for the sake of simplicity of description, it does not imply the relationship between different embodiments.

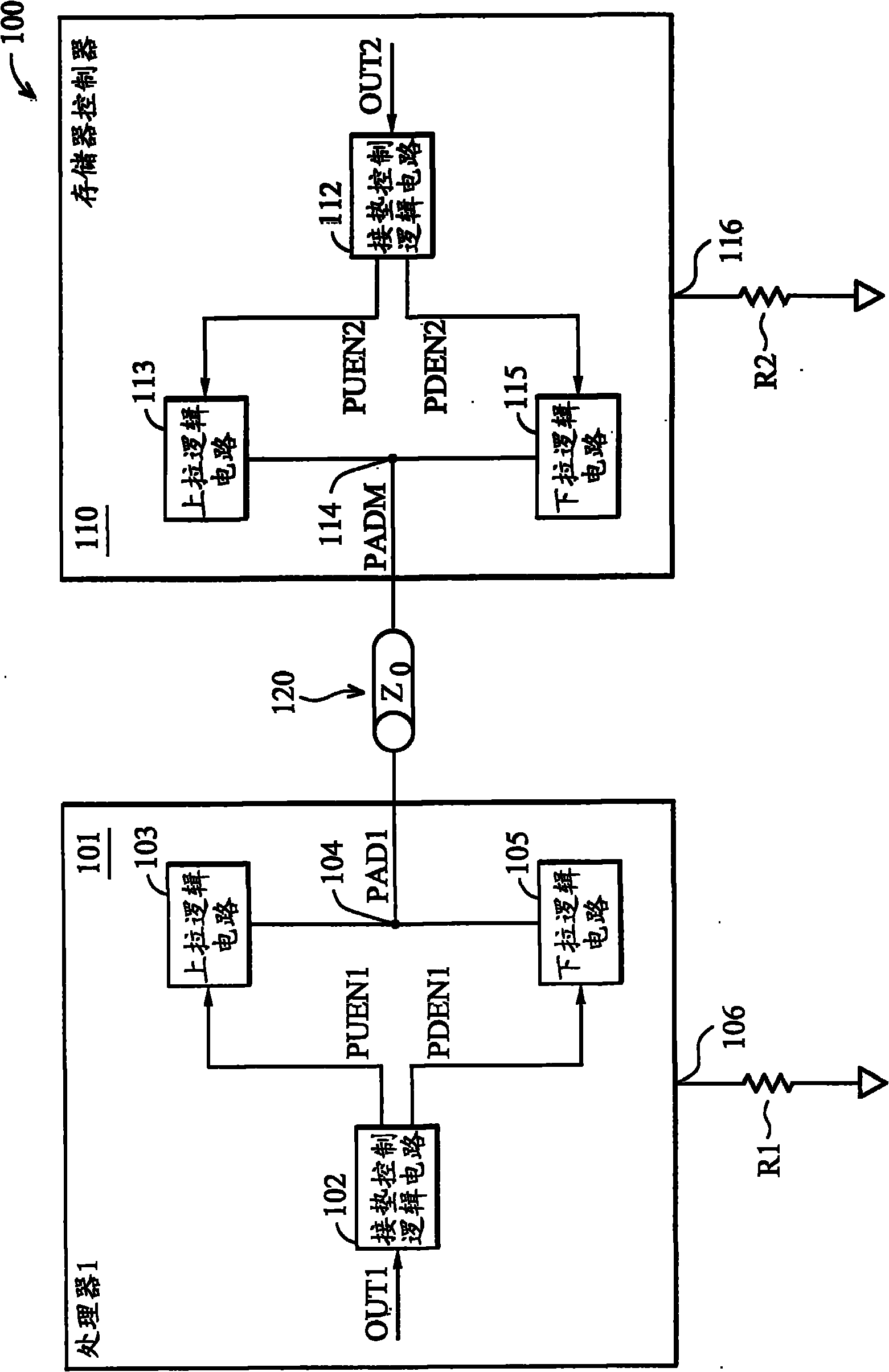

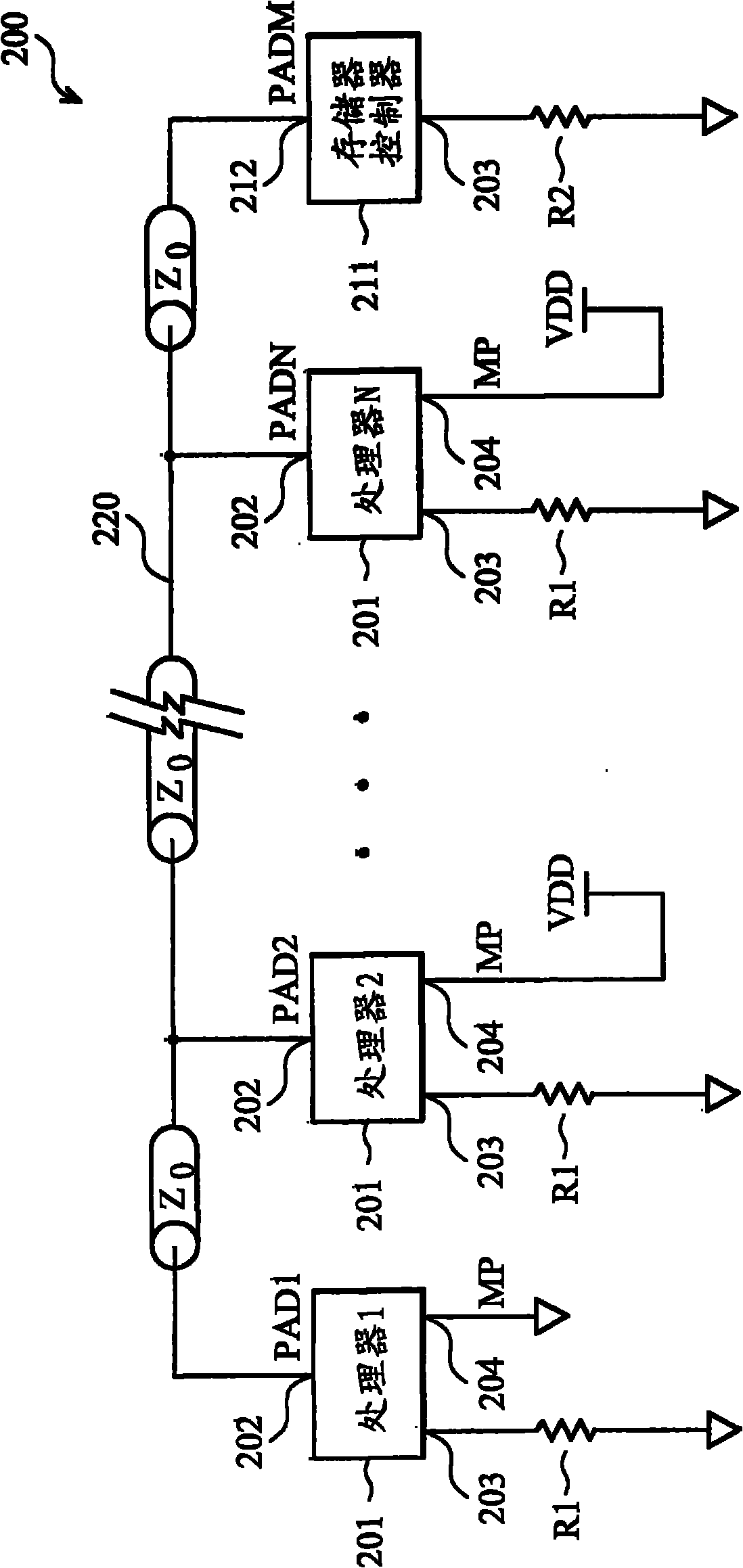

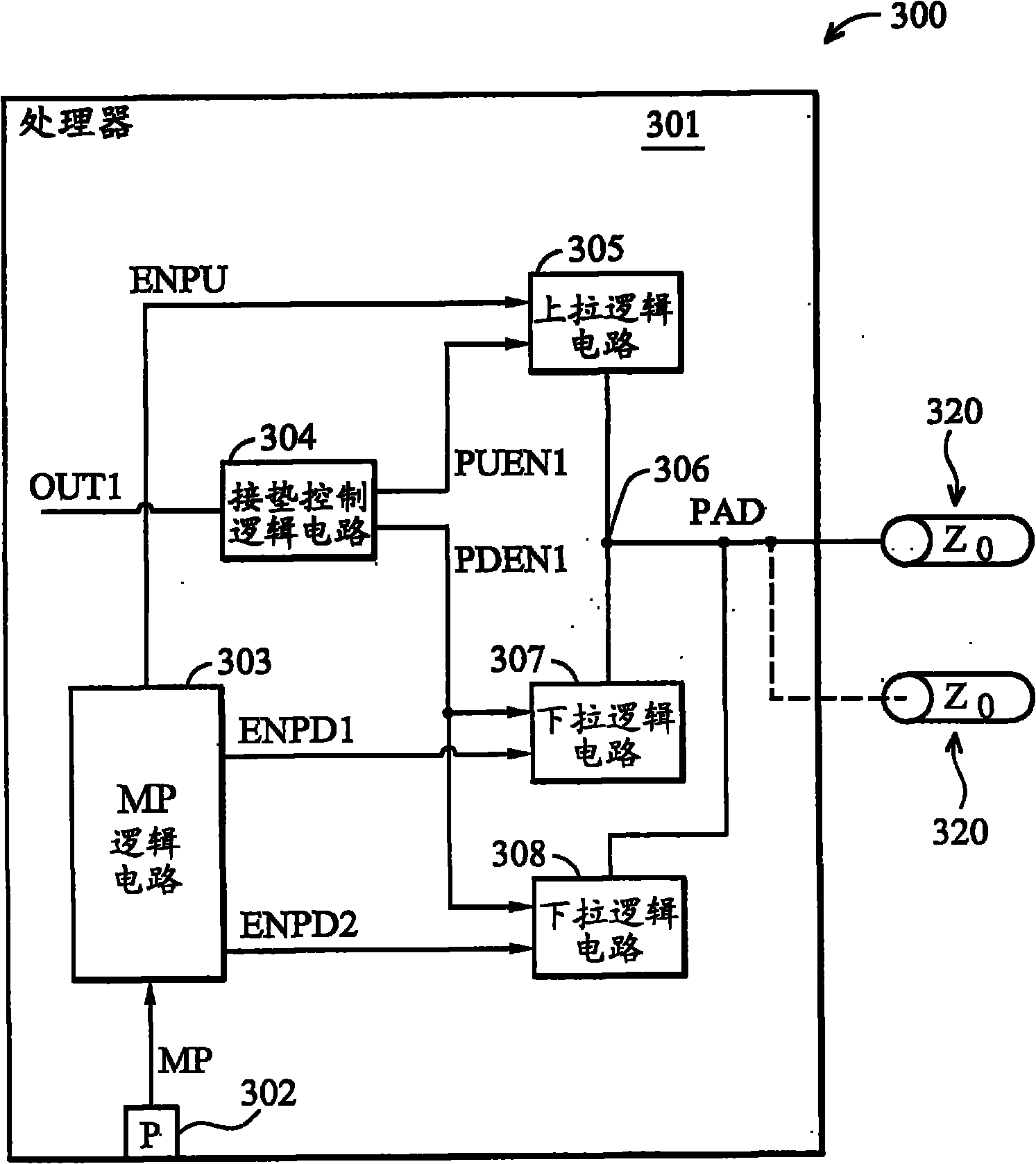

[0023] In view of the bus interface discussed in the prior art and related technologies used to transfer data between devices in integrated circuits, in the following, Figure 1 to Figure 3 will illustrate the problems created by multiple actively terminated buses, while Figure 5 to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com