Instruction allocation device of high performance universal signal processor

A signal processor and instruction distribution technology, applied in the direction of machine execution devices, etc., can solve the problems of high data throughput, computational complexity and the inability of parallel DSP chips to achieve the effect of reasonable task distribution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

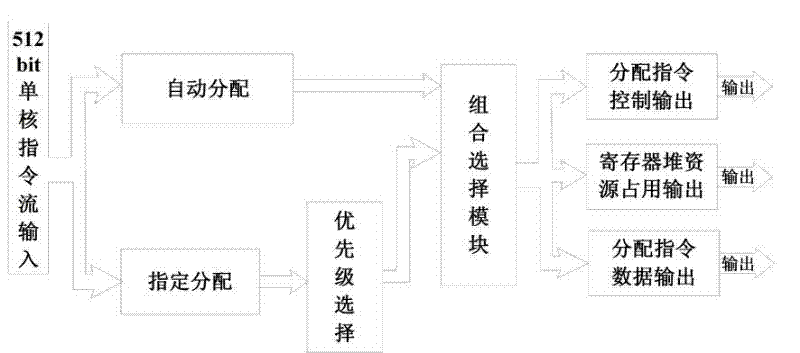

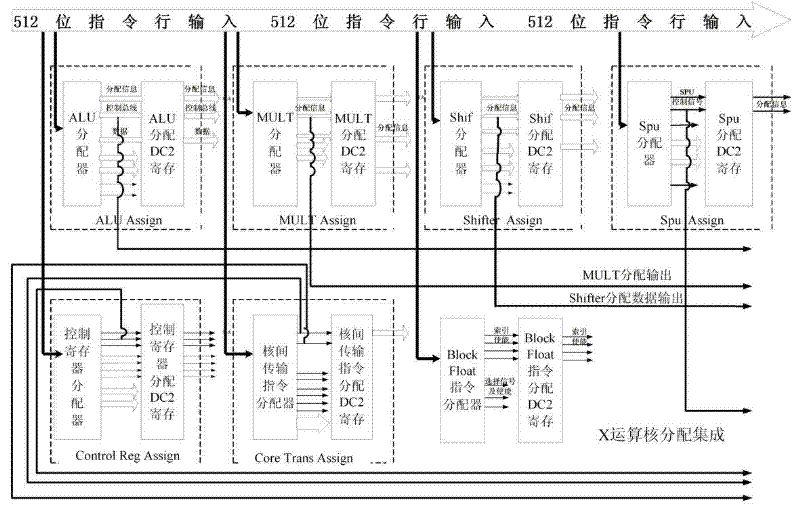

[0028] Such as Figure 4 As shown, a high-performance general-purpose signal processor instruction distribution device includes:

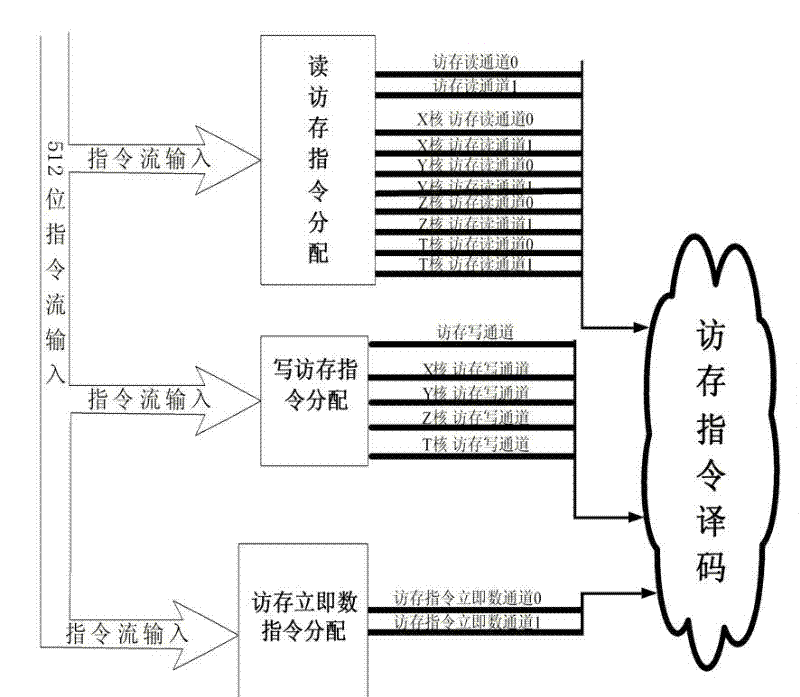

[0029] 1. Instruction sub-core module: Each clock cycle receives 512-bit instruction lines, including 32-bit single-word instructions and 64-bit double-word instructions. One instruction line can contain 1 to 16 instructions. Each instruction can occupy any combination of 1 to 4 operation execution cores among x, y, z, t. The function of the instruction splitting module is to divide the received instruction into four 512-bit instruction lines for different operation execution cores.

[0030] 2. Instruction classification module: The input of the instruction classification module is the output of the instruction classification module. Its function is to classify the instruction lines in parallel according to the classification of the instruction set and output the category flag. In the BWDSP100 chip, the instruction classification module includes ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com