A verification method of SOC hardware and software co-simulation based on network communication protocol

A network communication protocol, software and hardware collaboration technology, applied to electrical components, transmission systems, etc., can solve the problems of low simulation speed, long compilation time, single programming language, etc., and achieve the effect of speeding up simulation and saving compilation time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments.

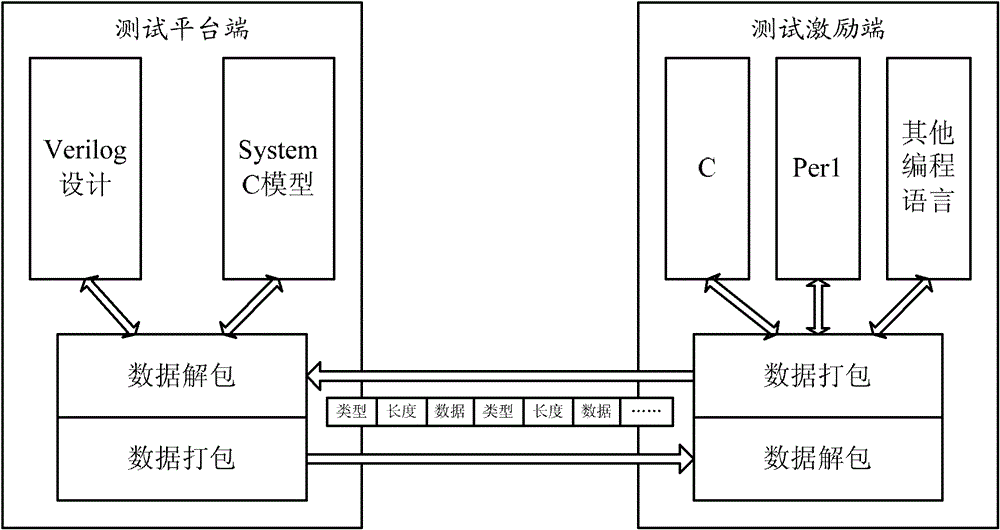

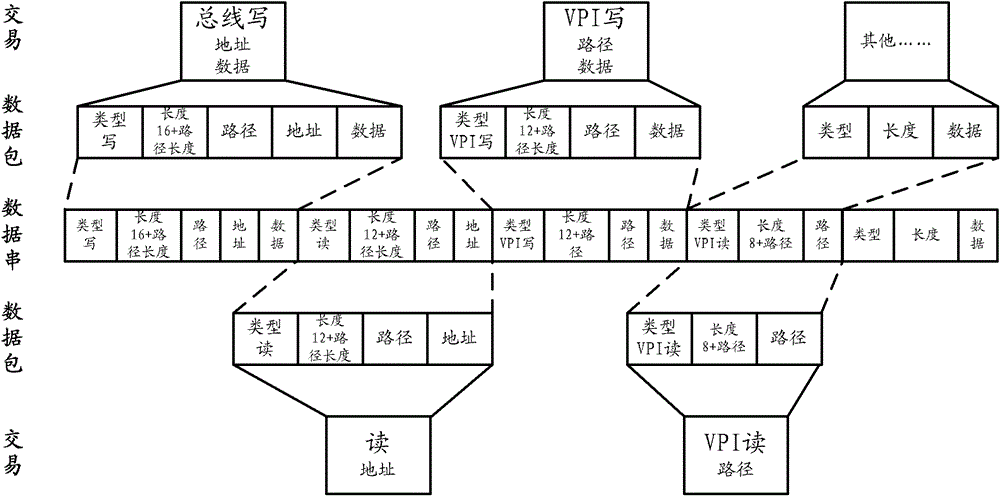

[0018] see figure 1 and figure 2 , a kind of SOC software-hardware co-simulation verification method based on network communication protocol, this verification method comprises the following steps successively:

[0019] Step 1: Build the test platform and test stimulus first. The test platform is the network server, and the test stimulus is the network client. The test platform includes verilog design, SystemC model and The server packaging / unpacking module written by C++, the test stimulation end includes the test software and the client packaging / unpacking module, and then the test platform end and the test stimulation end are separated by a network protocol so as to operate independently; the server Packing / unpacking module and client packing / unpacking module exchange data through self-explanatory packet format on the network; ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More