Method and electric device for interacting cache descriptors

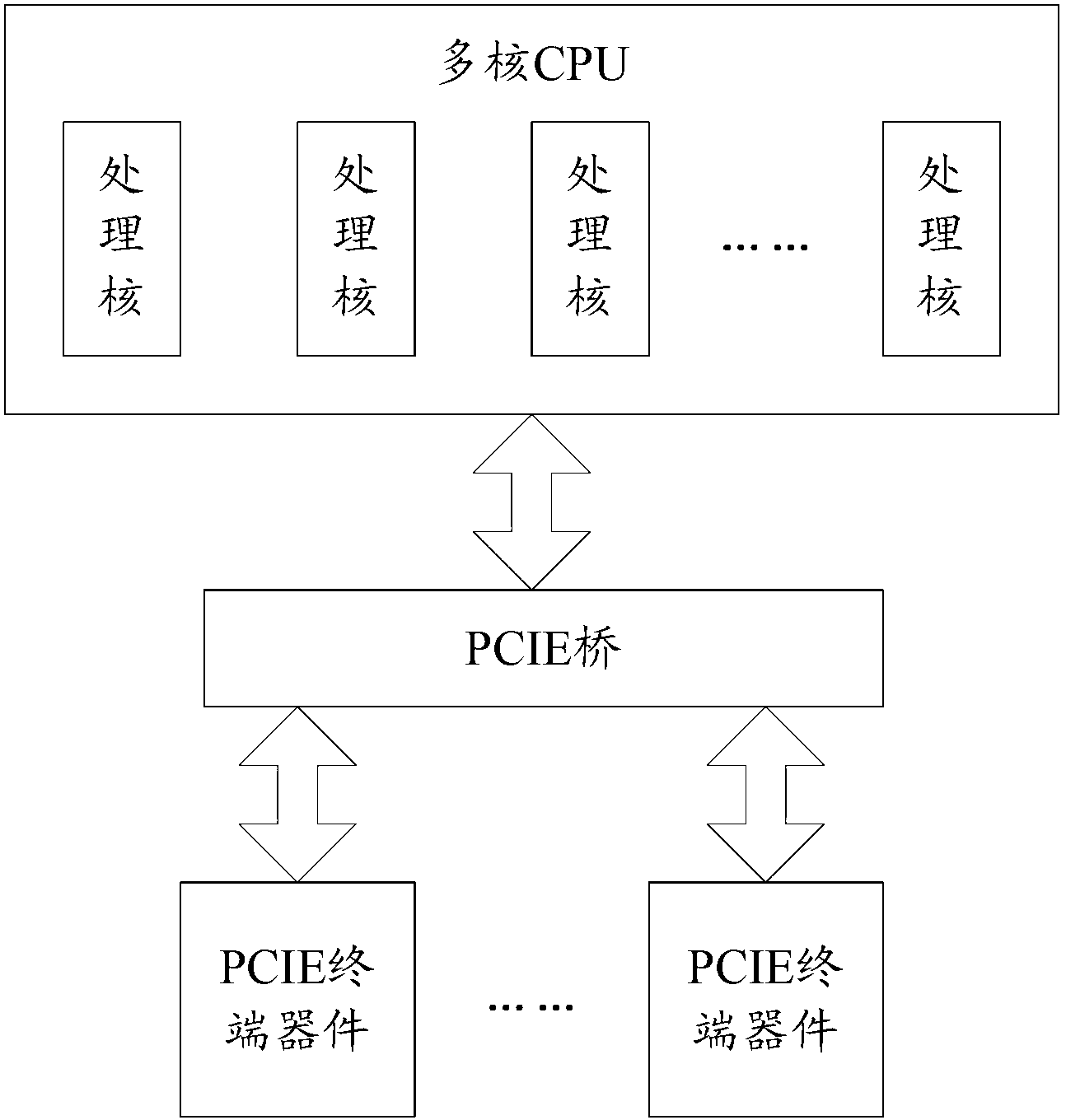

A technique for caching descriptors and electronic devices, which is applied in memory systems, electrical digital data processing, memory address/allocation/relocation, etc., and can solve problems affecting the overall efficiency of multi-core CPUs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0048] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and examples.

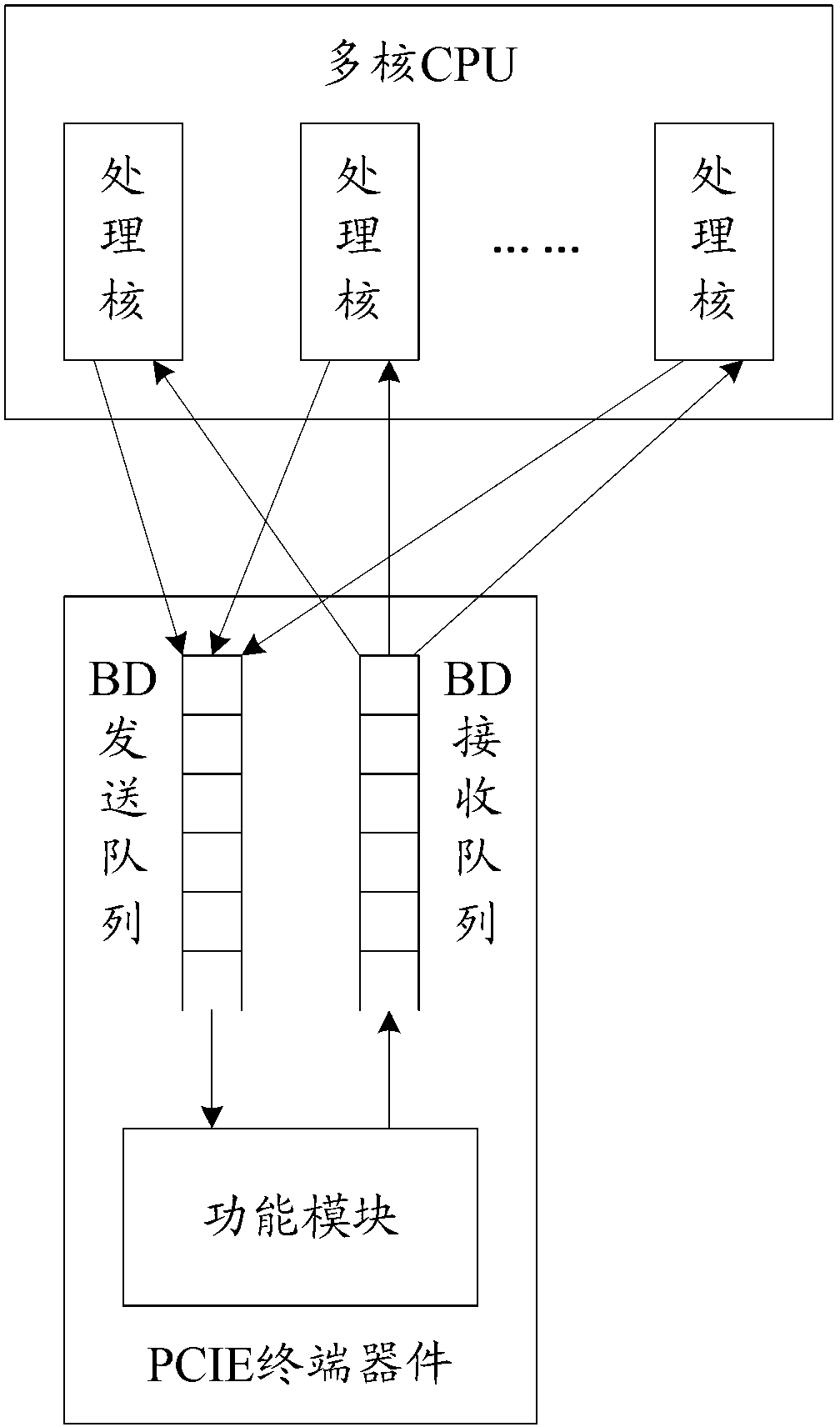

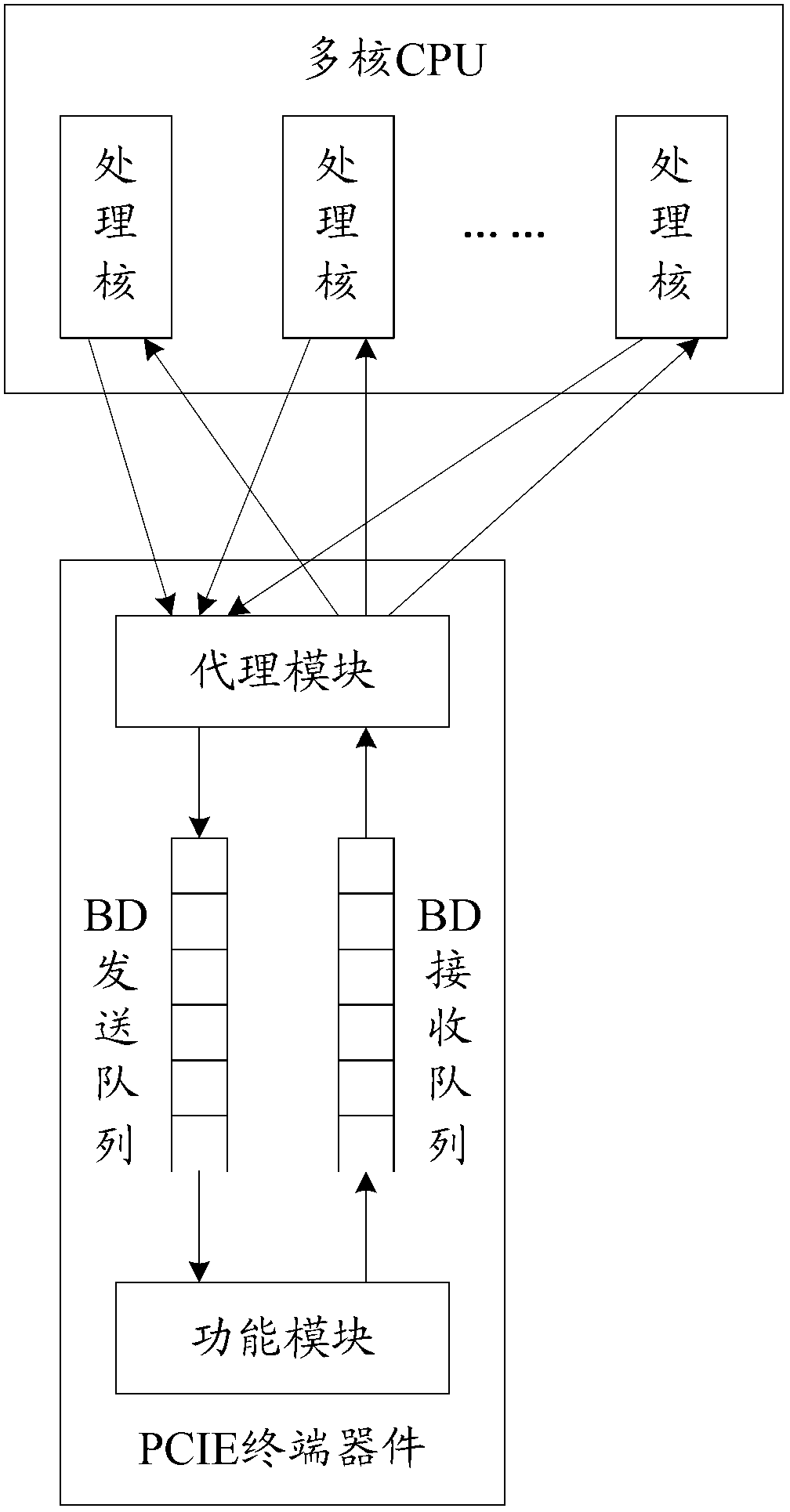

[0049] The write operation to the BD send queue and the read operation to the BD receive queue can actually be divided into two parts, one part is the addressing of the BD send queue and the BD receive queue and the BD send and receive operation, or become an entry (Entry) operation, The other part is the pointer operation on the BD sending queue and the BD receiving queue. Among them, the Entry operation does not have mutual exclusion; while the pointer operation has a higher mutual exclusion requirement.

[0050] Therefore, this embodiment adds a proxy module in the PCIE terminal device, and makes the BD sending queue and the BD receiving queue invisible to each processing core. In this way, the proxy module executes pointer operations that require h...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com