Data automatic comparison test circuit of non-volatile memory

A test circuit, non-volatile technology, applied in the field of data automatic comparison test circuit, can solve the problems of address address dissatisfaction, not all 1, large circuit area, etc., to achieve the effect of flexible comparison, reduced use, and reduced implementation area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

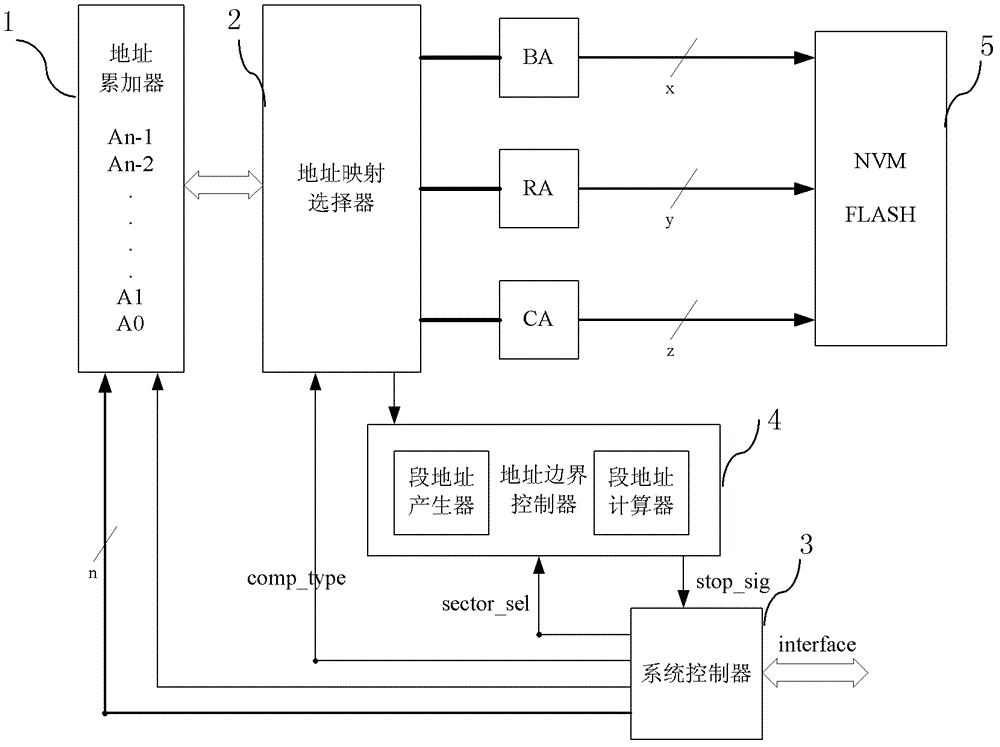

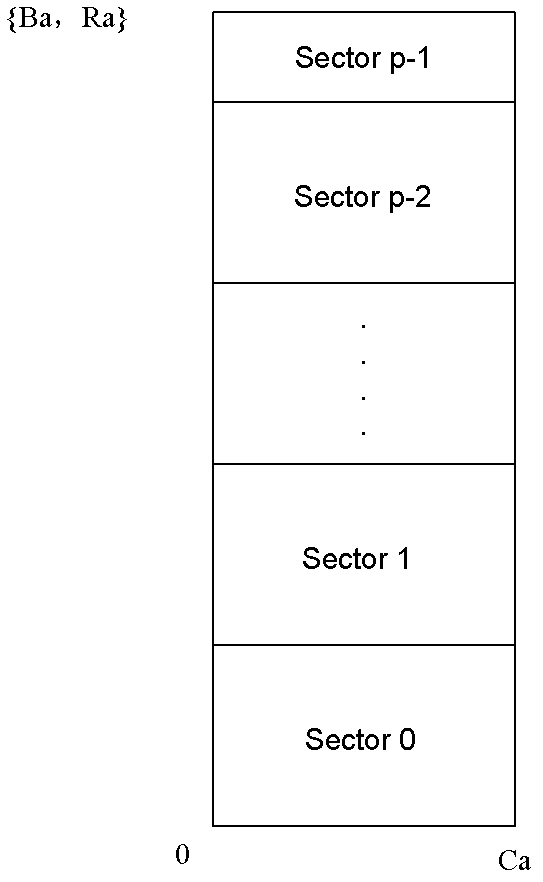

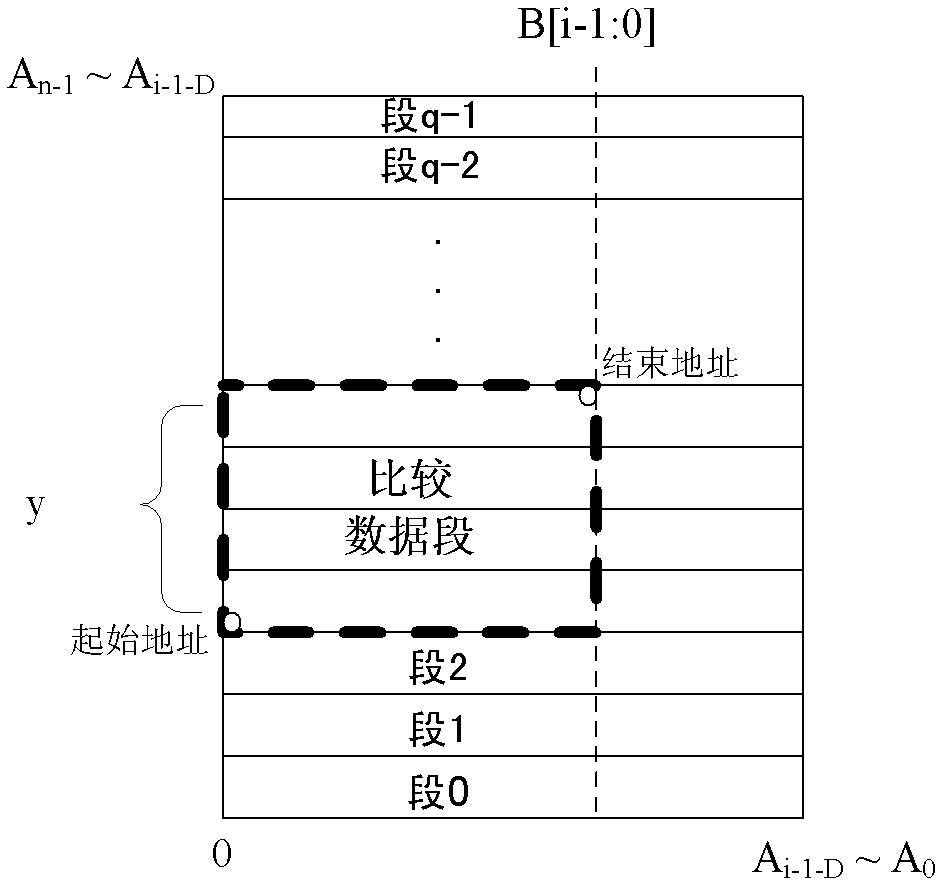

[0024] Such as figure 1 Shown is a circuit structure diagram of an embodiment of the present invention. The data automatic comparison test circuit of the non-volatile memory in the embodiment of the present invention includes: address accumulator 1, address mapping selector 2, system controller 3, address boundary controller 4 , Used for automatic data comparison test of non-volatile memory (NVM FLASH) 5. The non-volatile memory 5 includes a z-bit row address (Ca), a y-bit column address (Ra), and an x-bit block address (Ba).

[0025] The system controller 3 provides control signals for the address accumulator 1, the address mapping selector 2 and the address boundary controller 4. The system controller 3 is connected to an external testing machine through an interface.

[0026] The address accumulator 1 is composed of n-bit address registers, and is used to add and subtract the test circuit addresses of the automatic data comparison test circuit. The n-bit test circuit addresses...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More