Round transformation multiplexing circuit and AES (Advanced Encryption Standard) decryption circuit

A technology of multiplexing circuits and round transformation, which is used in electrical components, encryption devices with shift registers/memory, digital transmission systems, etc., to reduce the implementation area, improve the efficiency of circuit optimization, and reduce the implementation area.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

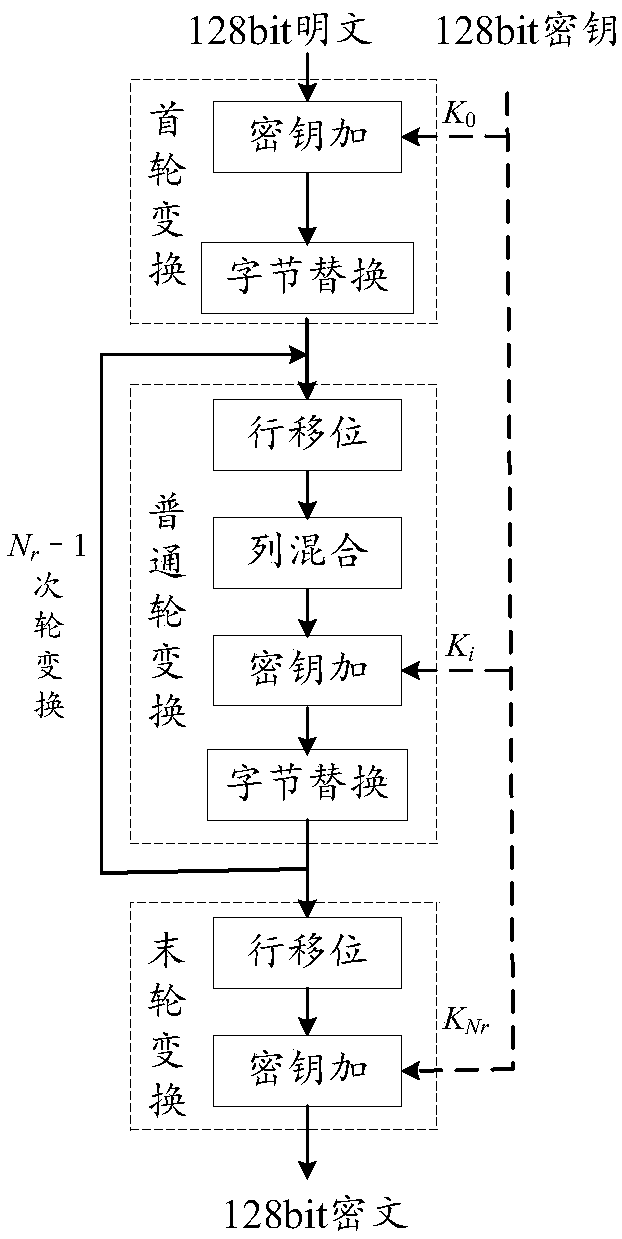

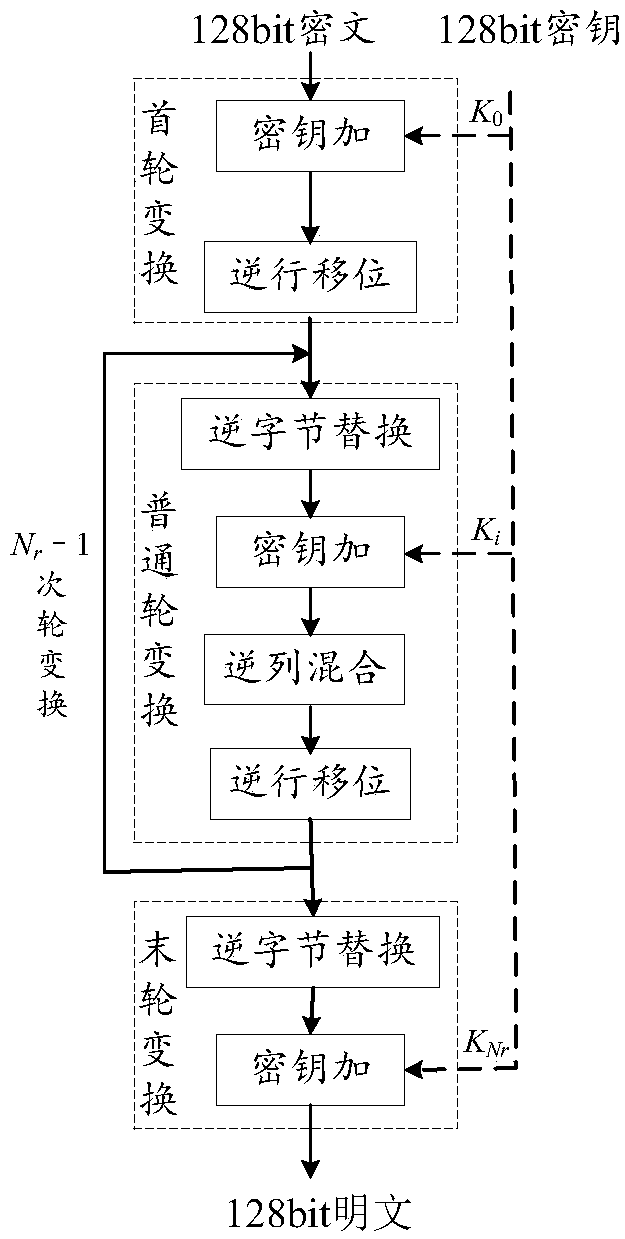

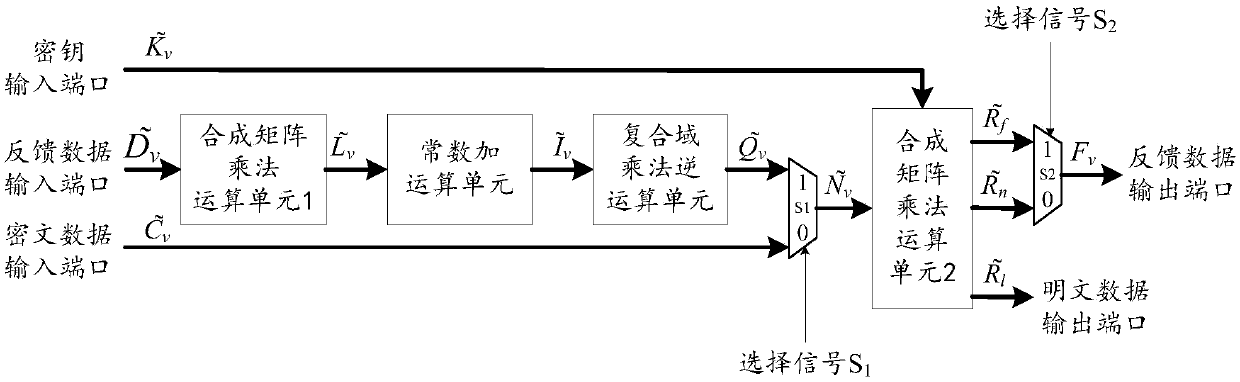

[0130] The decryption method of the AES decryption circuit provided by Embodiment 1 includes the following steps:

[0131] S1. The first 4 calculations constitute the first round of transformation. The first round of transformation refers to inputting the four groups of four-byte ciphertext data from the ciphertext data input port into the round transformation multiplexing circuit, and the selector S2 performs the round transformation multiplexing circuit operation. a vector of the first through fourth rows of the result Output to register 1, when register 1 stores 16 bytes of data, transfer the stored data to register 2;

[0132] S2, the 5th to 4N of the multiplexing wheel conversion circuit r The operation constitutes (N r -1) general wheel transformation, register 2 outputs 4 bytes of data each time to the feedback data input end of the wheel transformation multiplexing circuit, and through the operation of the wheel transformation multiplexing circuit, the selector S2 t...

Embodiment 2

[0137] The decryption method of the AES decryption circuit provided by the second embodiment comprises the following steps:

[0138] S1. The first two operations constitute the first round of transformation. The first round of transformation means that the four-byte ciphertext data is input into two round transformation multiplexing circuits from the ciphertext data input port respectively, and the selector S2 converts the operation result of the round transformation multiplexing circuit. A vector consisting of the first to fourth rows of Output to register 1, when register 1 stores 16 bytes of data, transfer the stored data to register 2;

[0139] S2, the 3rd to 2nd N of the multiplexing round conversion circuit r The composition of the operations (N r -1) Common round-to-round conversion, register 2 outputs two sets of 4-byte data each time, and transmits them to the feedback data input terminals of the two round-conversion multiplexing circuits respectively. After the op...

Embodiment 3

[0144] The decryption method of the AES decryption circuit provided by the third embodiment comprises the following steps:

[0145] S1. The first operation constitutes the first round of transformation. The first round of transformation means that four groups of four-byte ciphertext data are respectively input into four rounded transformation multiplexing circuits from the ciphertext data input port, and the selector S2 converts the round transformation multiplexing circuit. A vector consisting of the first row to the fourth row of the operation result output to the register;

[0146] S2, the second to N of the multiplexing round conversion circuit r The composition of the operations (N r -1) Ordinary round-to-round conversion, the register outputs four groups of 4-byte data each time, which are respectively transmitted to the feedback data input terminals of the four round-conversion multiplexing circuits. A vector composed of vectors from the fifth row to the eighth row ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More