Distributed building blocks for r-c clamp circuits in the core region of a semiconductor die

A core area, clamping circuit technology, applied in semiconductor devices, circuits, transistors, etc., can solve problems such as occupying chips and restricting wiring options

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] One disadvantage of conventional timer-based clamp circuit designs is that the timer-based clamp occupies a large area and it uses a large portion of the conductive (eg, metal) layer to handle the ESD current. This introduces a problem at the block or chip level, since a considerable area is allocated to place the timer-based (e.g., RC) clamp, resulting in congestion due to conductive layer congestion within the timer-based clamp. Increases the difficulty of routing signals in the core area.

[0014] According to aspects of the present invention, these problems with conventional timer-based clamper implementations can be mitigated by distributing the building blocks of the timer-based clamper. Distributed timer-based clamps can be applied in a flip-chip configuration or any other chip configuration.

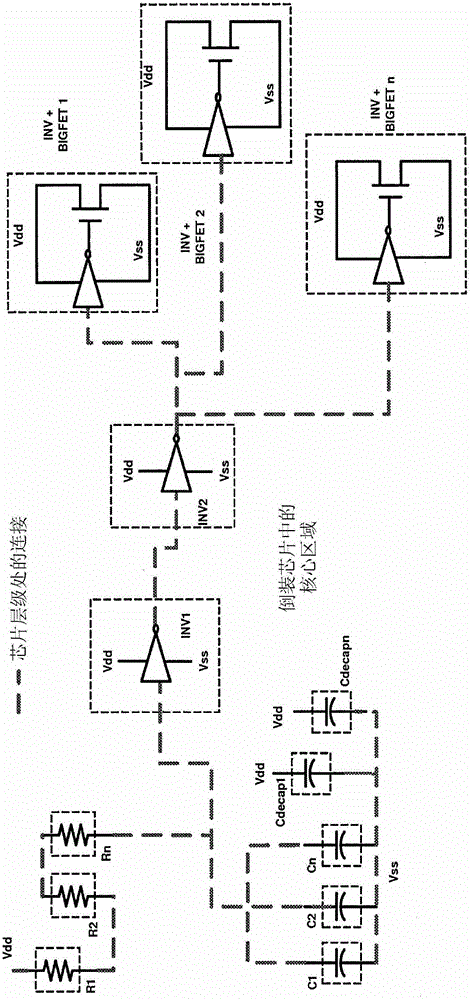

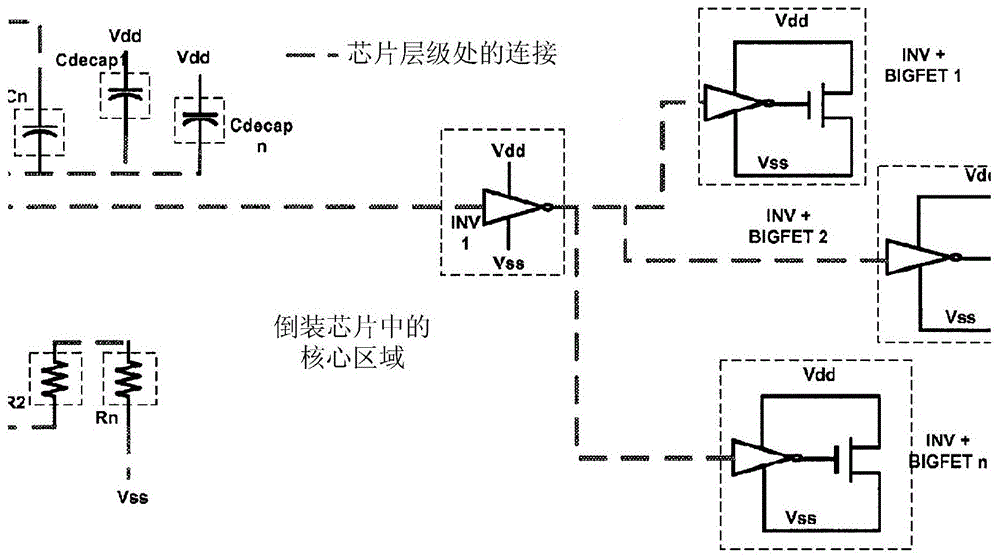

[0015] Figure 1A is a block diagram of an exemplary timer-based clamp circuit in which components of the timer-based circuit (eg, resistors and capacitors) are distribut...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More