Data queue dequeue control method and device

A data queuing and queuing technology, used in multi-programming devices, electrical digital data processing, instruments, etc., can solve the SRAM resource occupancy, can not meet the processing rate requirements of the queue, and can not meet the rate requirements of entering and leaving the queue. And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0064] It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

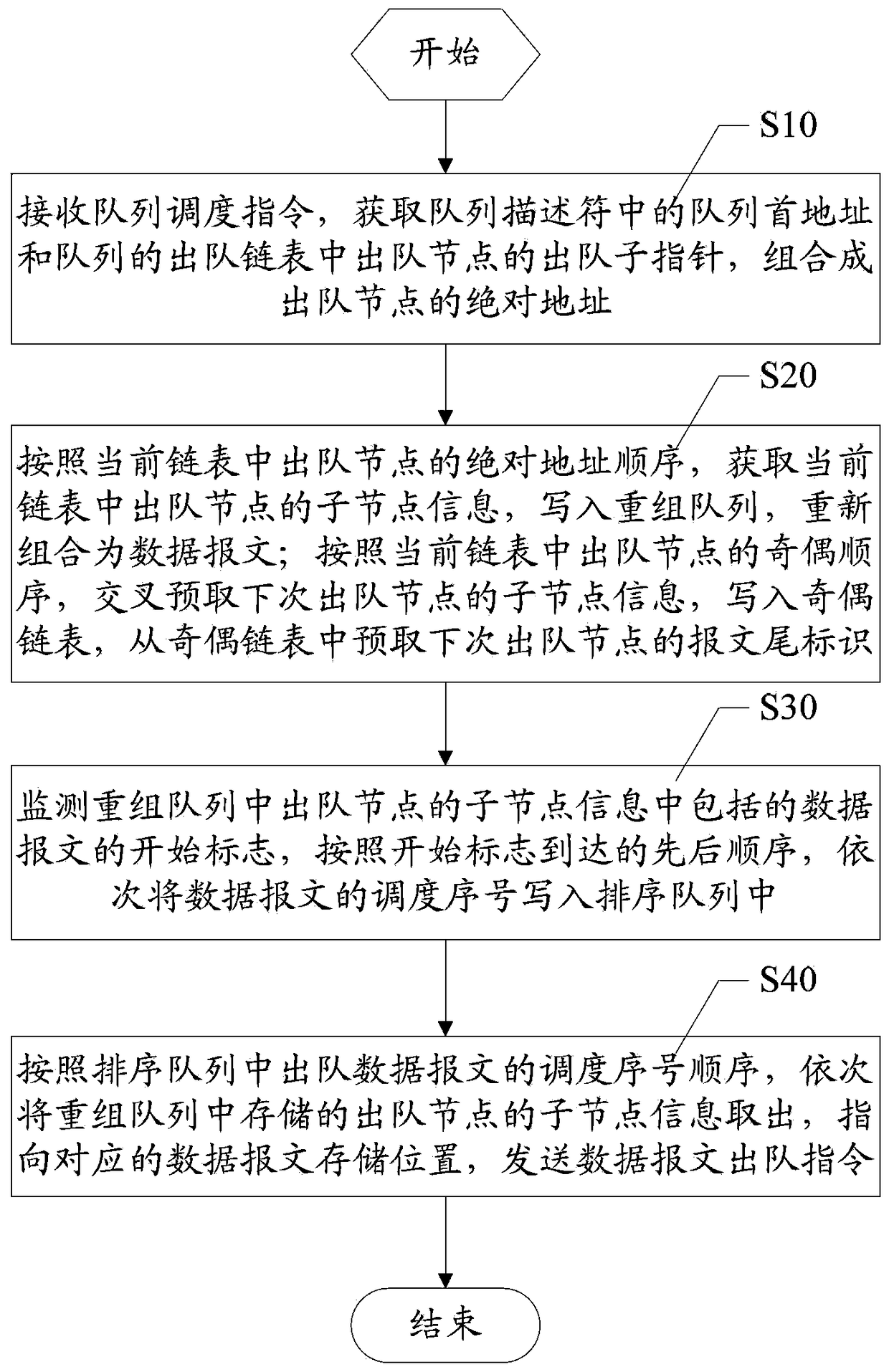

[0065] Such as figure 1 as shown, figure 1 It is a flow chart of the first embodiment of the data queue dequeue management and control method of the present invention. The data queue dequeuing management and control method mentioned in this embodiment includes:

[0066] Step S10, receiving the queue scheduling instruction, obtaining the head address of the queue in the queue descriptor and the dequeue sub-pointer of the dequeue node in the dequeue linked list of the queue, and combining them into an absolute address of the dequeue node;

[0067] The off-chip QDR memory of this embodiment includes a queue descriptor off-chip QDR memory, a linked list off-chip QDR memory, and a child node information off-chip QDR memory, respectively storing descriptors, queue head pointers and queue tail pointers, and sink nodes ( T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More