A large-scale chip-on-chip interconnection method and routing algorithm for realizing interconnection structure

A chip-on-chip, large-scale technology, applied in digital transmission systems, electrical components, transmission systems, etc., can solve problems such as inability to adapt to localized computing of nodes and localized data storage, and achieve the effect of speeding up communication efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

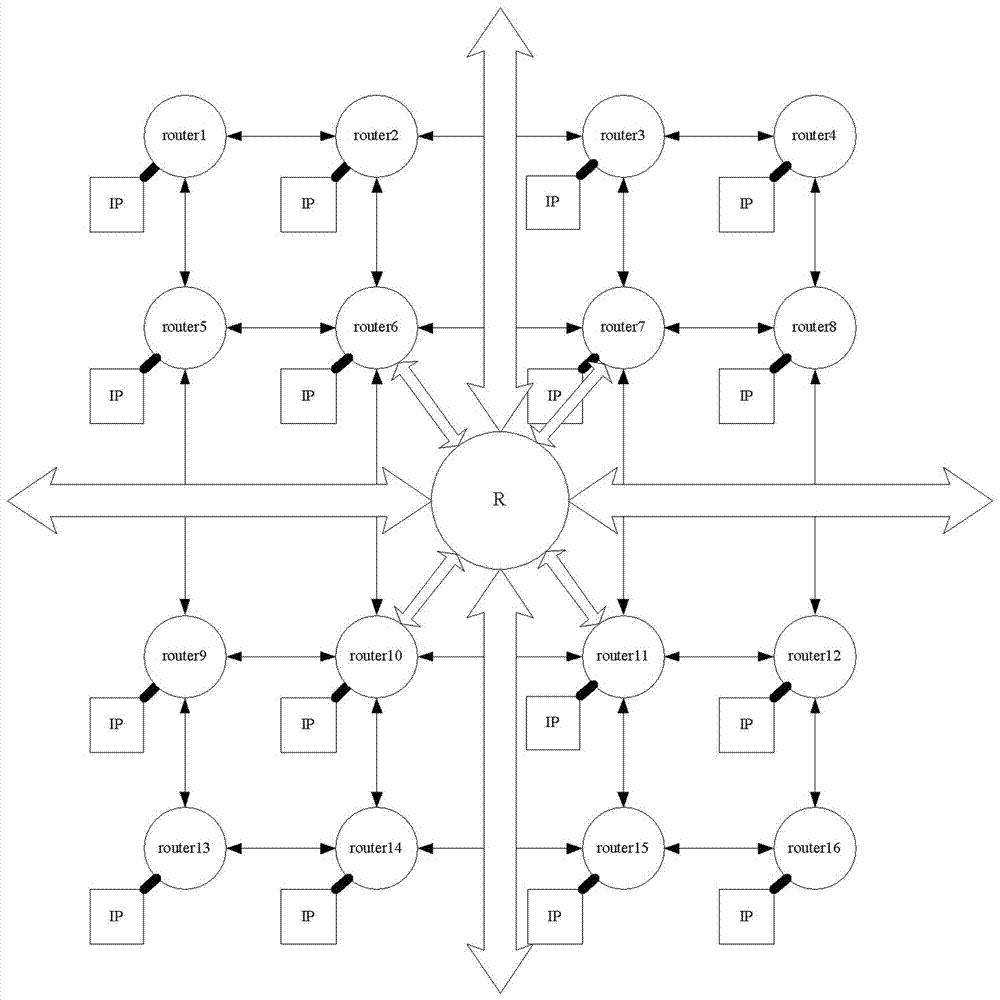

[0021] Example 1: see figure 2 , The cross-domain direct connection large-scale chip-on-chip interconnection method of the present invention, in the chip-on-chip network structure design with a network interconnection structure, is aimed at the peer-to-peer connection of nodes in the current on-chip network structure, which cannot adapt to node localized calculations and data The actual demand for localized storage,

[0022] 1) At the peer node location, instantiate a local subnet and add the local computing node (IP) connected to the local subnet as a local computing domain;

[0023] 2) At the same time, between adjacent local computing domains, they are directly connected through the routing nodes of the local subnet to build the main network of the on-chip network structure to speed up the communication efficiency between different local computing domains.

Embodiment 2

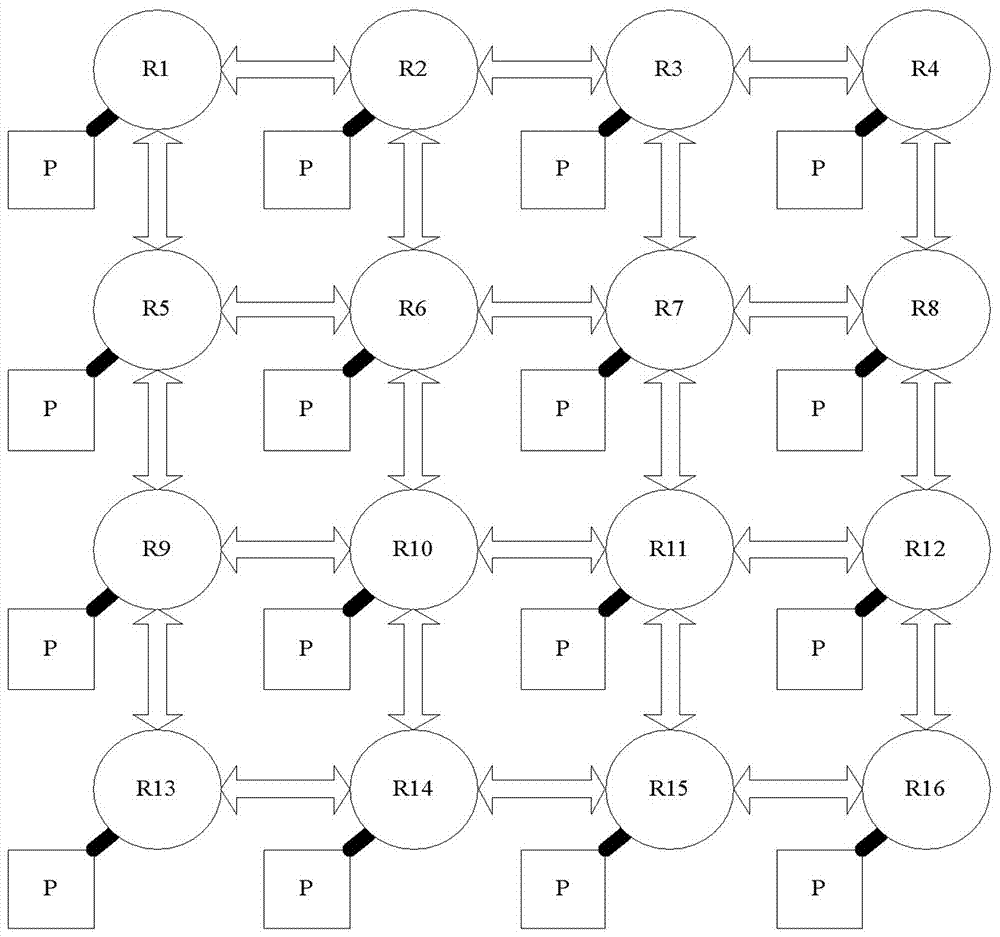

[0024] Example 2: see figure 1 , figure 2 Compared with the embodiment, the cross-domain direct connection large-scale chip-on-chip interconnection method of this embodiment furthermore includes a local computing domain resource (P) and adjacent routers for each local subnet at the peer node location (R), each local computing domain resource is connected to a backbone router through a network interface, where the local computing domain resources are processor cores, memory or user-defined hardware modules, and the backbone router is adjacent to the main network The router (R) is directly connected and connected to the four subnet routers of the local subnet at the same time.

Embodiment 3

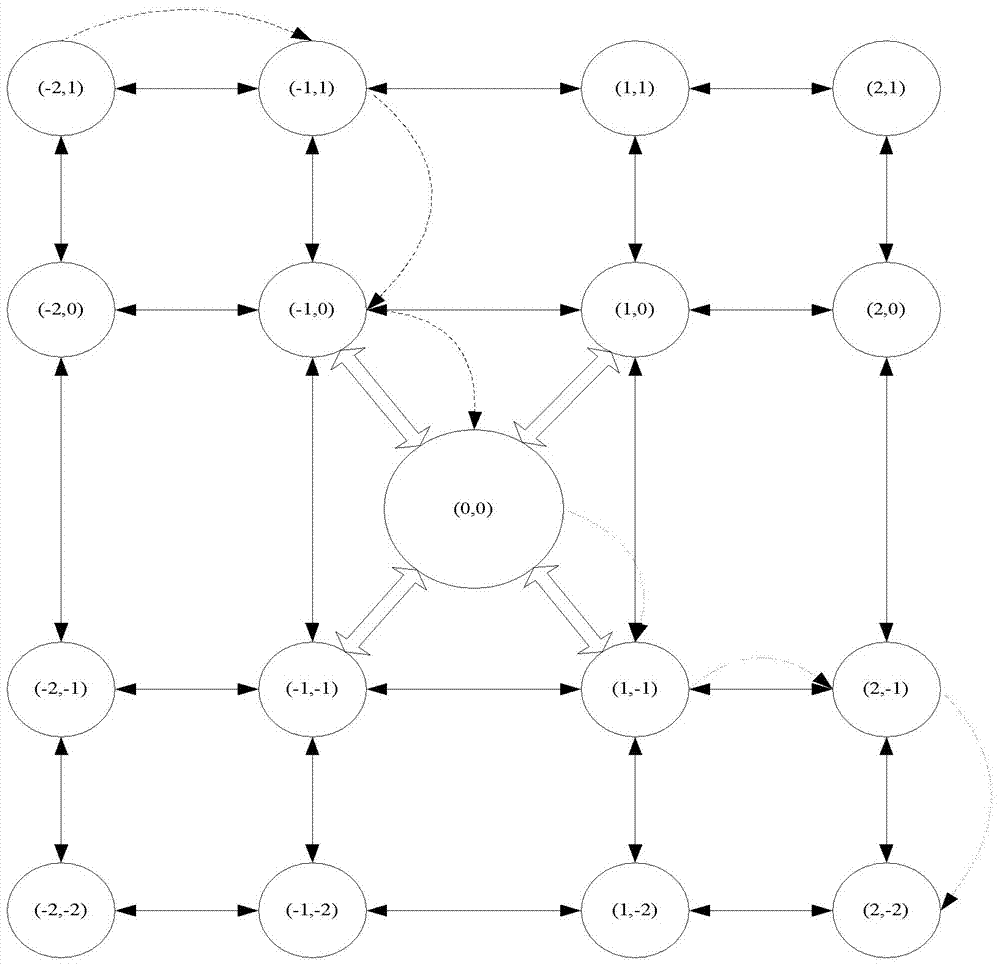

[0025] Embodiment 3: This embodiment takes the simplest network topology 4*4 mesh network as an example to illustrate the design idea of the cross-domain direct connection large-scale chip-on-chip interconnect structure of the present invention. Each node in the network is connected to a resource and its neighboring routers. Here is different from other on-chip network structures in that each resource is not connected to the corresponding router through a network interface (NI). This router is directly embedded in the resource and connected to the internal router in the resource. Here we are for convenience Observe and draw it outside. The so-called resources here are chips with a network interconnection structure. The router and the router are connected by a pair of input and output channels. The channel is composed of two unidirectional point-to-point buses.

[0026] For the internal structure of resources in the main network, we also use the simplest network topology in t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com