Twin-channel server mainboard main-slave CPU switching device and switching control method thereof

A switching device and control method technology, applied in the direction of instruments, response error generation, electrical digital data processing, etc., can solve problems such as master-slave CPU judgment, and achieve good promotion and use value, easy processing, and reasonable design effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

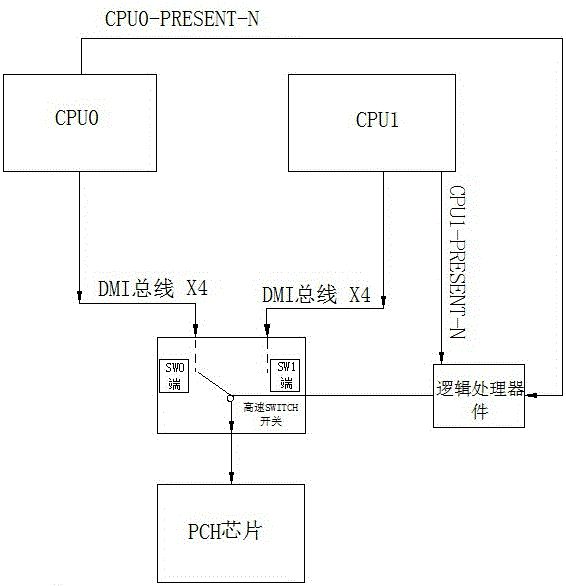

[0034] as attached figure 1 Shown, the master-slave CPU switching device of two-way server motherboard of the present invention, its structure comprises CPU0, CPU1, high-speed SWICH switch, PCH chip and logic processing device, the switching position of described high-speed SWICH switch comprises SW0 end and SW1 end; CPU0 and CPU1 are respectively connected to the SW0 and SW1 ends of the high-speed SWICH switch through the DMI bus, and the high-speed SWICH switch is respectively connected to the PCH chip and the logic processing device; at the same time, both CPU0 and CPU1 are connected to the logic processing device; the logic processing device is used to detect CPU0 and CPU1 loading situation. CPU0 transmits the CPU0-PRESENT-N signal to the logic processing device, and CPU1 transmits the CPU1-PRESENT-N signal to the logic processing device. The DMI bus is connected to the DMI ports of CPU0 and CPU1 respectively. The DMI bus adopts the DMIX4 bus.

Embodiment 2

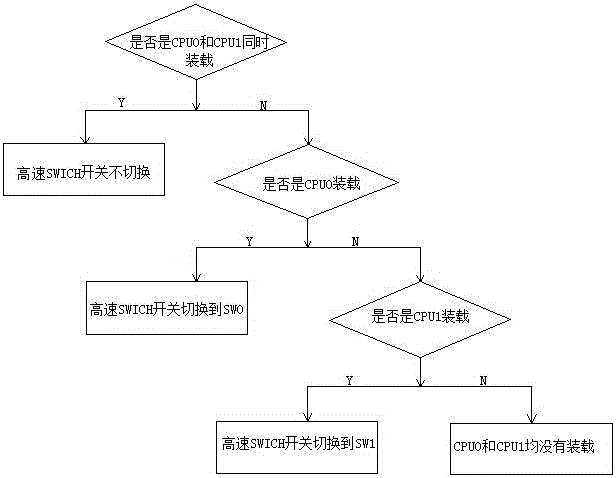

[0036] as attached figure 2 Shown, a kind of two-way server motherboard master-slave CPU switching control method of the present invention comprises the steps:

[0037] (1) The AUX power supply on the motherboard is powered on, and the logic processing device starts to work;

[0038] (2) Judging by the logic processing device, the loading status of CPU0 and CPU1:

[0039] ①The logic processing device judges whether CPU0 and CPU1 are loaded at the same time according to the detected CPU0-PRESENT-N signal and CPU1-PRESENT-N signal validity:

[0040] (a) If both the CPU0-PRESENT-N signal and the CPU1-PRESENT-N signal are valid, it is judged that CPU0 and CPU1 are loaded at the same time, and at this time, the high-speed SWICH switch gives up switching;

[0041] (b) If the CPU0-PRESENT-N signal and the CPU1-PRESENT-N signal are not valid at the same time, it is judged that CPU0 and CPU1 are not loaded at the same time, and at this time, go to step ②;

[0042] ②. The logic proc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More