A Method of Suppressing the Propagation of Normally Connected Defects in Nano CMOS Circuits

A nano-defect technology, applied in the direction of logic circuits, logic circuits with logic functions, electrical components, etc., can solve the problems of uncontrolled signal transmission, affecting the logic function of the circuit, and speeding up the application process of CMOL circuits. Effects of Simplifying Constraints and Solving the Problem of Constantly Connected Defect Propagation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The present invention will be further described in detail below in conjunction with the accompanying drawings.

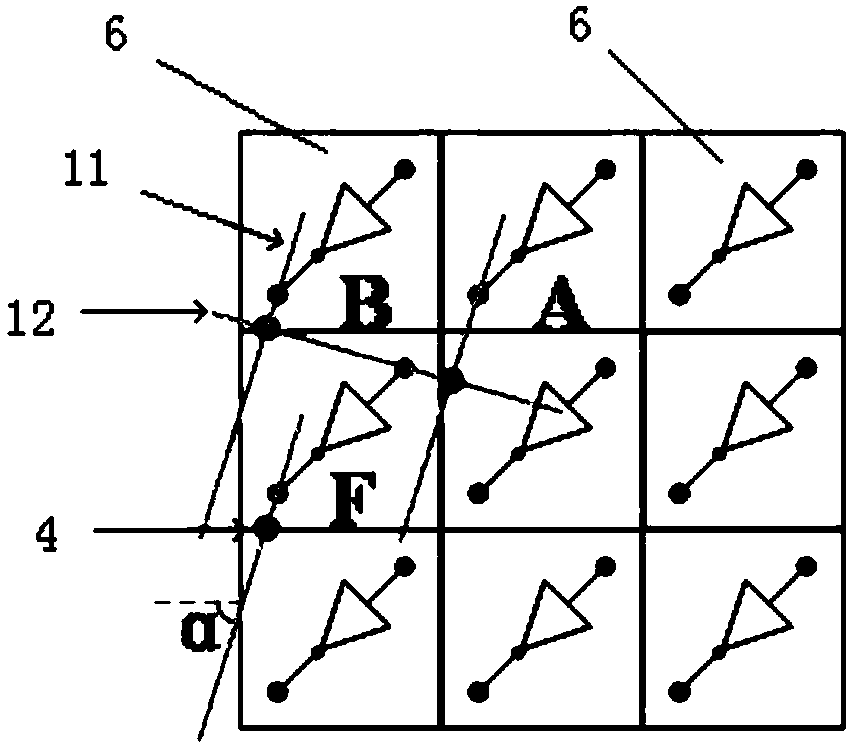

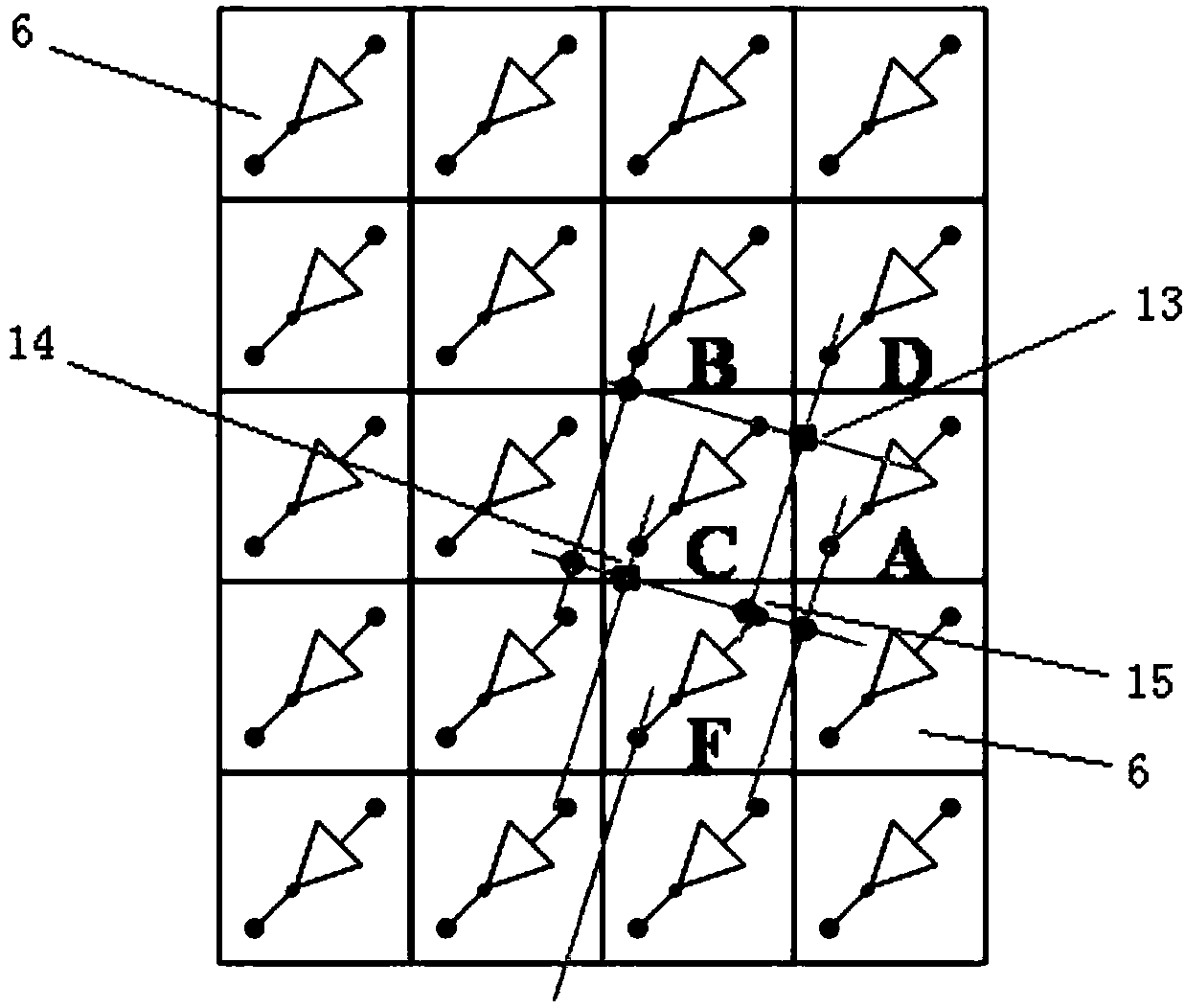

[0025] by image 3 Taking the nano-CMOS circuit structure with a size of 4*5 as shown as an example, the method for suppressing the propagation of the always-connected defect of the nano-CMOS circuit includes the following steps:

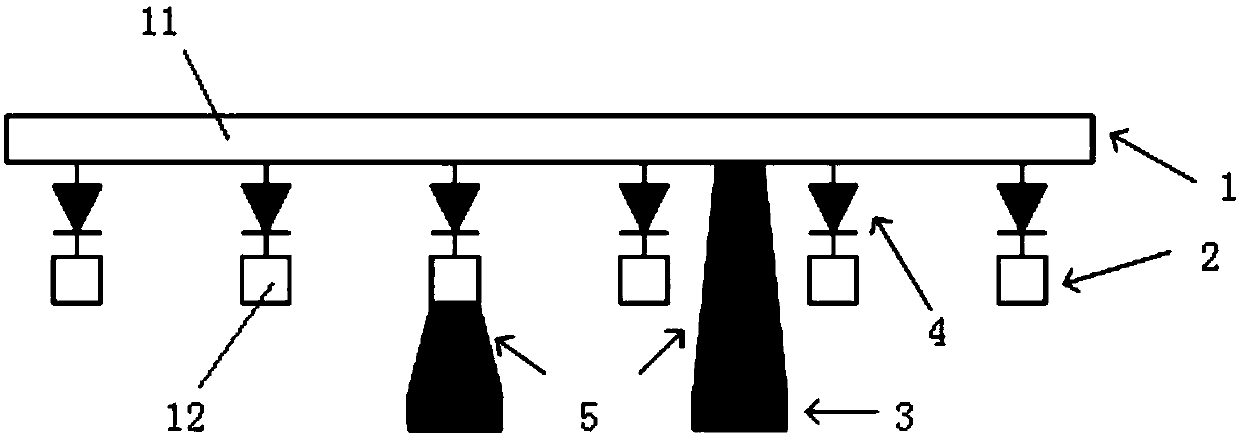

[0026] Define nanoscale CMOS circuit structures (see figure 1 ) includes an output nanowire layer 1, an input nanowire layer 2, several programmable nanodiodes 4 and several nanometer CMOS units 6, the output nanowire layer 1 and the input nanowire layer 2 are arranged at intervals up and down, and the output nanowire layer 1 consists of A plurality of parallel output nanowires 11, the input nanowire layer 2 is composed of a plurality of parallel input nanowires 12, any output nanowire 11 is vertically crossed with any input nanowire 12, and a programmable Nano diode 4; several nano CMOS units 6 are provided with a CMOS stack 3, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More