Semiconductor structure and forming method thereof

A technology of semiconductor and device area, applied in the field of semiconductor structure and its formation, can solve problems such as performance degradation of semiconductor structure, and achieve the effects of improving performance, improving top recess, and improving top flatness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

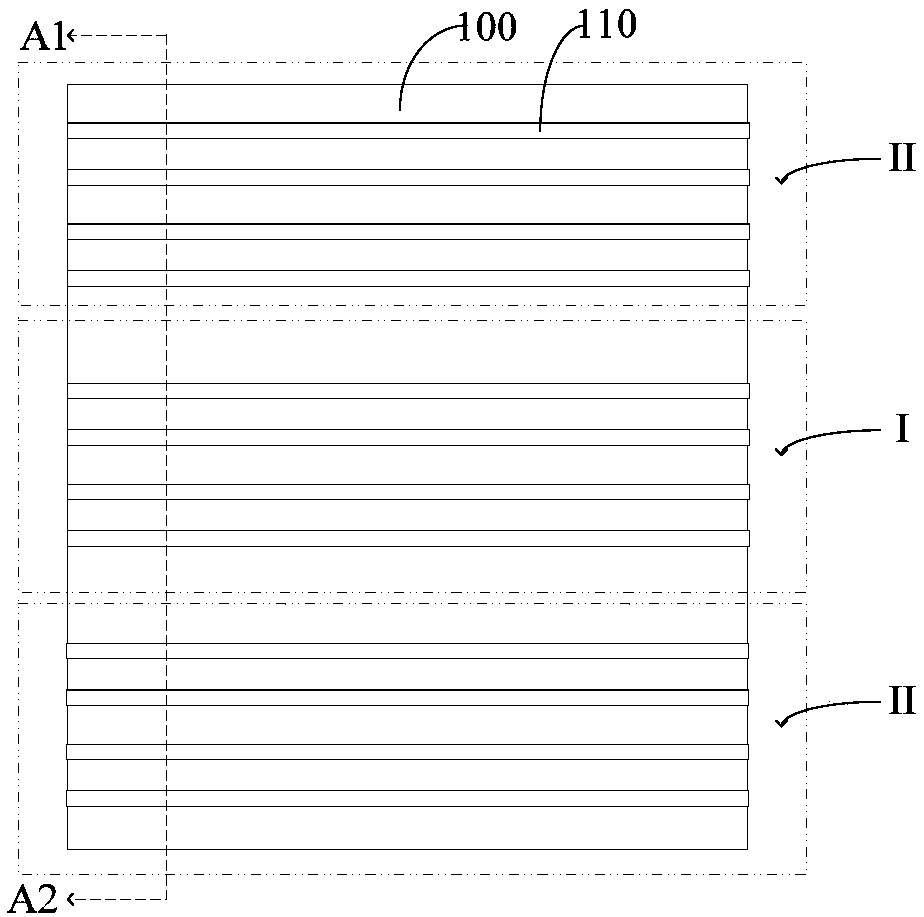

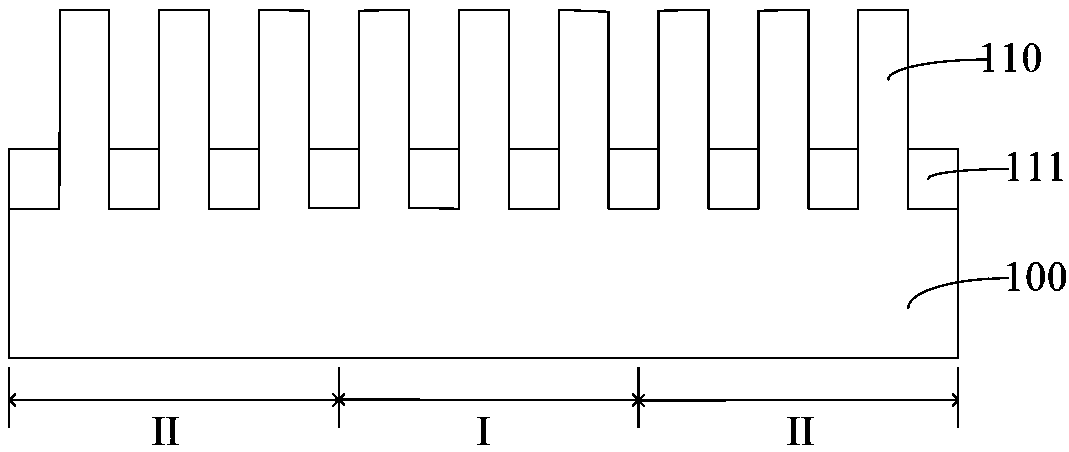

[0023] It can be seen from the background art that the process of forming the metal resistance device easily leads to performance degradation of the semiconductor structure. Analyzing the performance degradation of the semiconductor structure due to:

[0024] Currently, a discrete metal layer is usually formed on the interlayer dielectric layer above the isolation structure as a metal resistor device (Metal Resistor Device). When forming the interlayer dielectric layer, since the region corresponding to the isolation structure is a sparse area (Iso Area), after the planarization process for forming the interlayer dielectric layer, the top of the interlayer dielectric layer is flat The accuracy is poor, and the top of the interlayer dielectric layer is prone to a dishing problem, which leads to a decrease in the performance of the semiconductor structure.

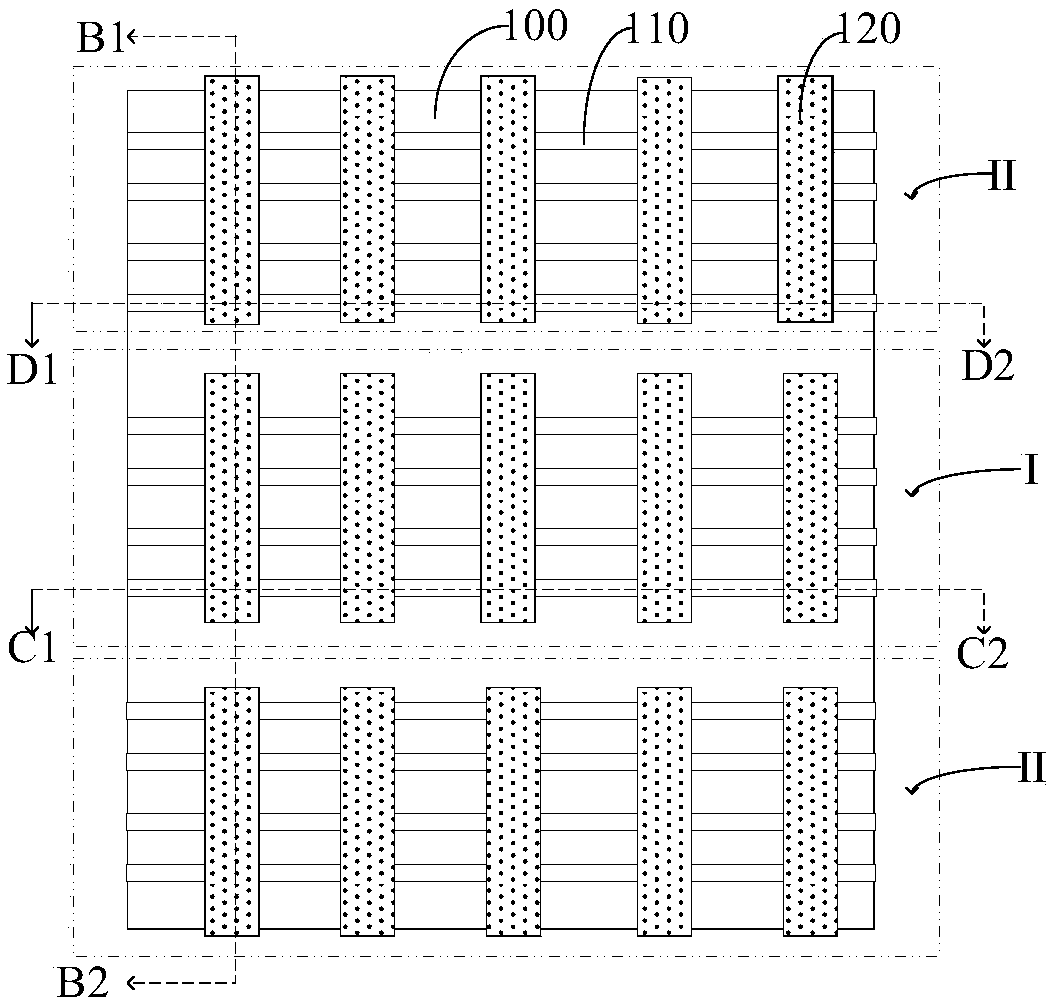

[0025] In order to solve the technical problem, the present invention forms discrete dummy gates on the substrates of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More