Patents

Literature

34results about How to "Improve planarization effect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

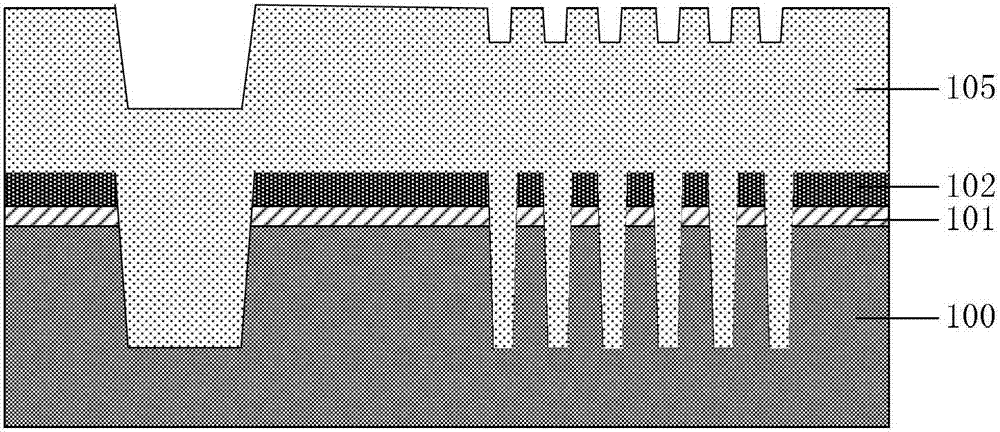

Method for improving photoetching critical dimension in groove process

InactiveCN102087471AImprove impactCut etch processPhotomechanical apparatusPhysical chemistryProcess window

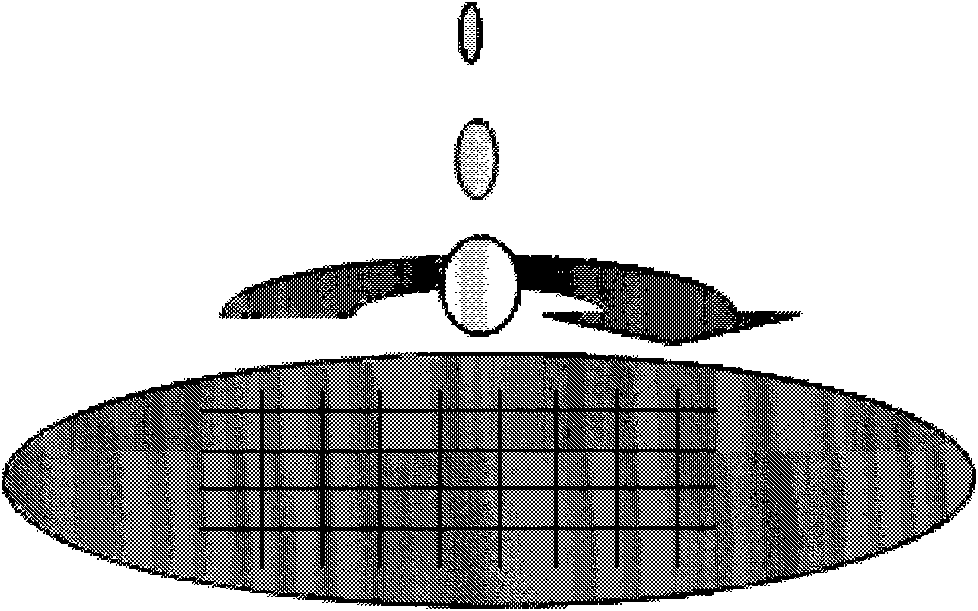

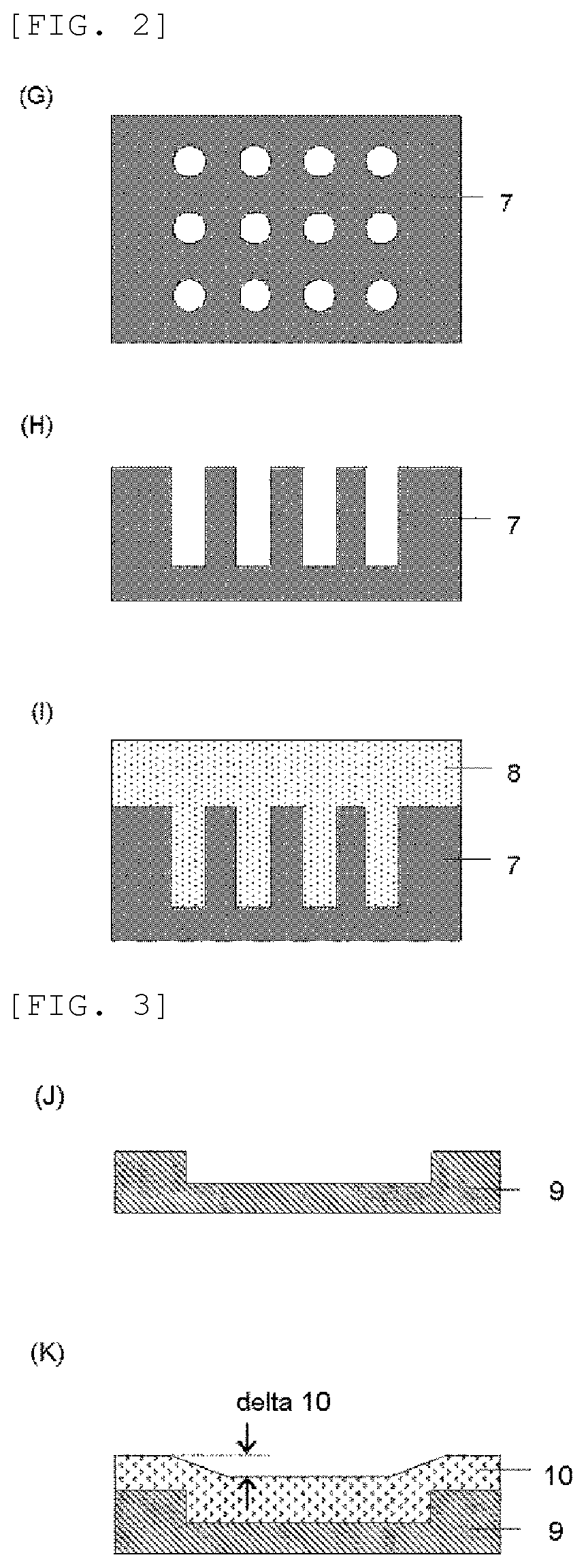

The invention discloses a method for improving a photoetching critical dimension in a groove process. The method comprises the following steps of: 1, spin-coating negative photoresist on the surfaces of a groove and a silicon wafer and then roasting; 2, carrying out exposure and development by using a maskplate with a graph of a groove of a front layer; and 3, spin-coating a bottom antireflection coating (BARC) on a graph formed in the groove and roasting. By the method, the control capacity of the photoetching critical dimension (CD) in the groove process can be improved and a process window can be optimized.

Owner:SHANGHAI HUA HONG NEC ELECTRONICS

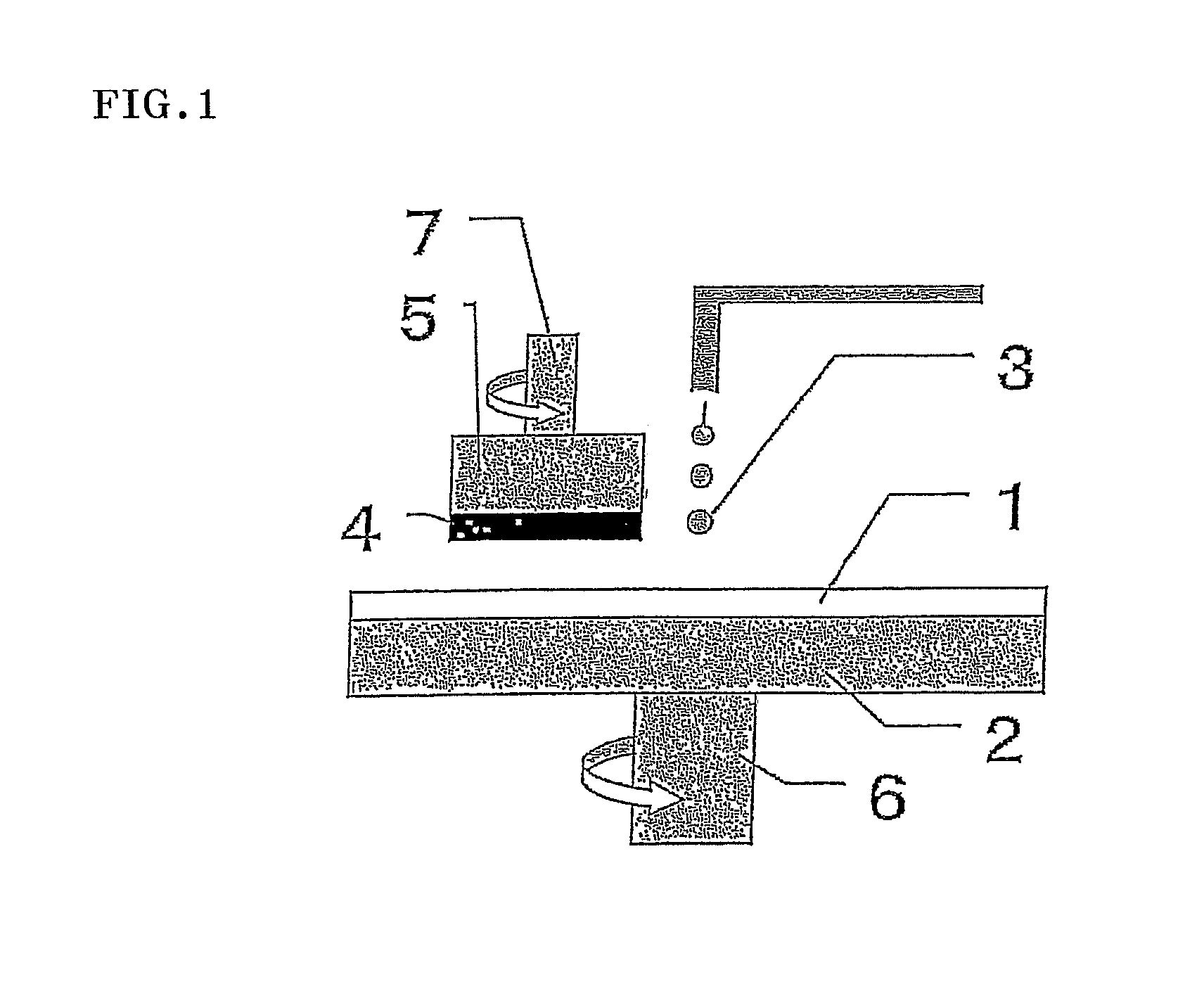

Manufacturing system

InactiveCN1744285AImprove planarization effectSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingNon destructiveMetrology

A fabrication system. A plating tool generates a layer of conductive material on a substrate. A polishing tool uses a mechanical mechanism to remove the conductive material from the substrate. A metrology tool measures an electromagnetic signal induced in the conductive material using a non-destructive testing mechanism. A controller, coupled to the polishing and metrology tools, determines residue thickness and removal rate of the conductive material during the polishing process according to the measured electromagnetic signal, and adjusts process parameters for the plating and polishing tools accordingly.

Owner:TAIWAN SEMICON MFG CO LTD

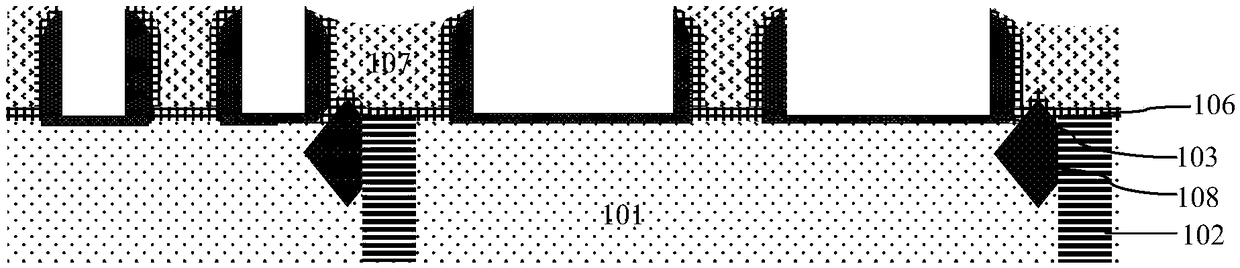

Manufacturing method for shallow trench isolation structure

InactiveCN103199052AReduce use costTo achieve a flattening effectSemiconductor/solid-state device manufacturingEtchingIsolation layer

The invention provides a manufacturing method for a shallow trench isolation structure. The method includes the following steps: covering a semiconductor substrate with an oxide layer and a nitride layer sequentially; carrying out exposure and etching process to form a shallow trench figure; depositing an isolation layer to fill the shallow trench figure; carrying out flattening processing on the isolation layer, and leaving part of the isolation layer; and removing the remaining isolation layer by adopting the method of wet etching, and then removing the nitride layer. According to the manufacturing method for the shallow trench isolation structure, in the process of flattening processing, the nitride layer is not contacted, flattening can be achieved by adopting common lapping fluid, cost of the lapping fluid is reduced, and meanwhile, the phenomena of indentation and corrosion caused by chemical and mechanical lapping are avoided due to the fact that the remaining isolation layer on the nitride layer is removed by using the method of wet etching.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

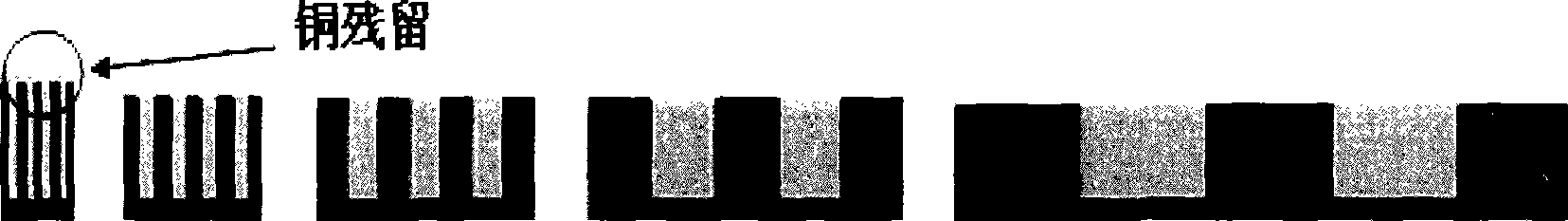

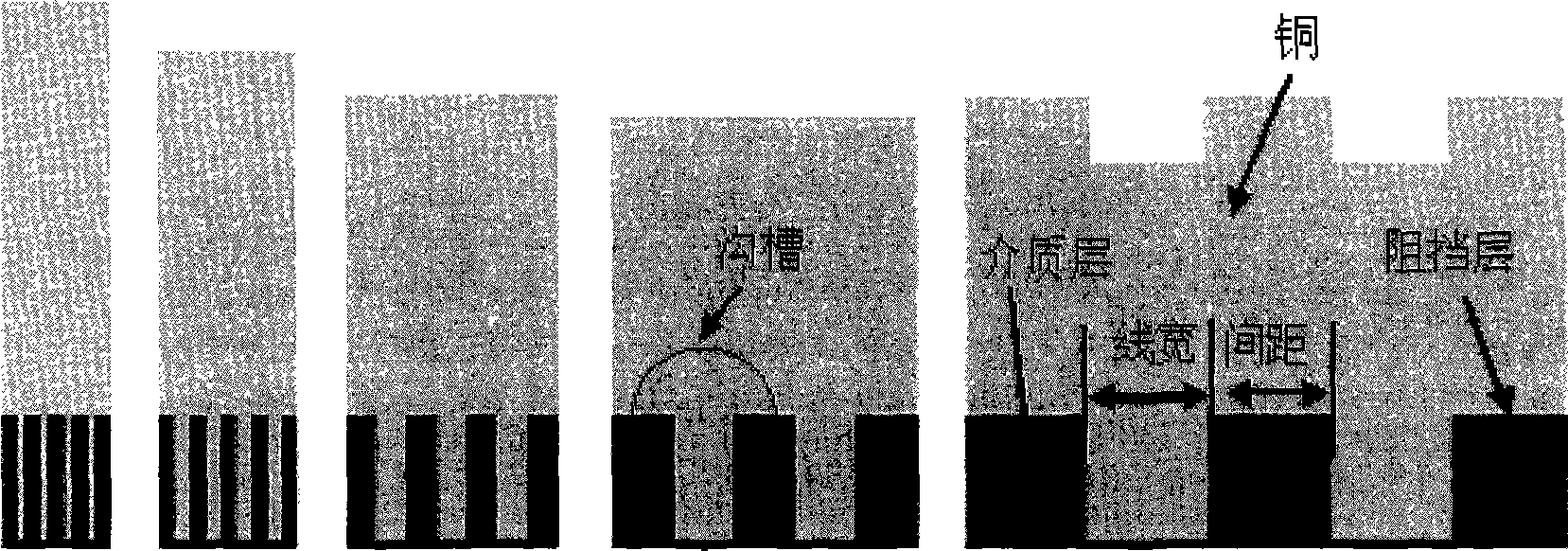

Fabrication method of shallow groove isolation structure and chemical mechanical grinding method and system

ActiveCN110071041AEliminate residueImprove yield rateSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingActual useMetallurgy

The invention provides a fabrication method of a shallow groove isolation structure and a chemical mechanical grinding method and system. The fabrication method comprises the following steps of 1) measuring a previous value thickness of a target material layer, and determining a first target removal thickness according to the previous value of the target material layer and the thickness of the target material layer maintained after first-stage chemical mechanical grinding; 2) determining theoretical grinding rate according to actual application time of a grinding consumption material; 3) dynamically correcting a grinding parameter according to the first target removal thickness and the theoretical grinding rate, and performing first-stage chemical mechanical grinding on the target materiallayer according to the grinding parameter; and 4) performing second-stage chemical mechanical grinding on the target material layer to achieve removal of second target removal thickness. By the fabrication method, the grinding parameter is determined by collecting the target removal thickness of the target material layer and grinding the actual application time of the grinding consumption material, the planarization effect of grinding is improved, the residue of the target material layer after chemical mechanical grinding is eliminated, and the yield is improved.

Owner:CHANGXIN MEMORY TECH INC

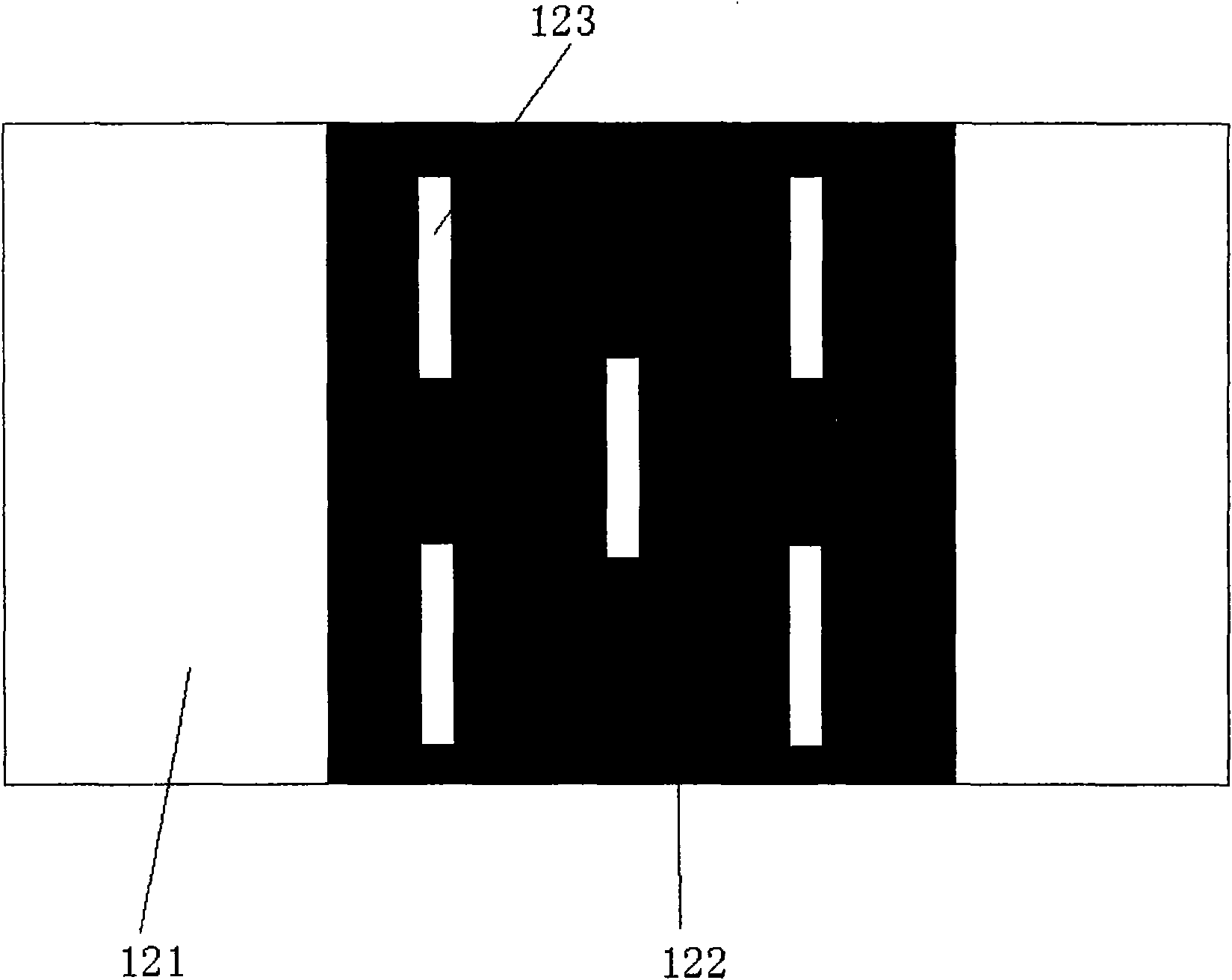

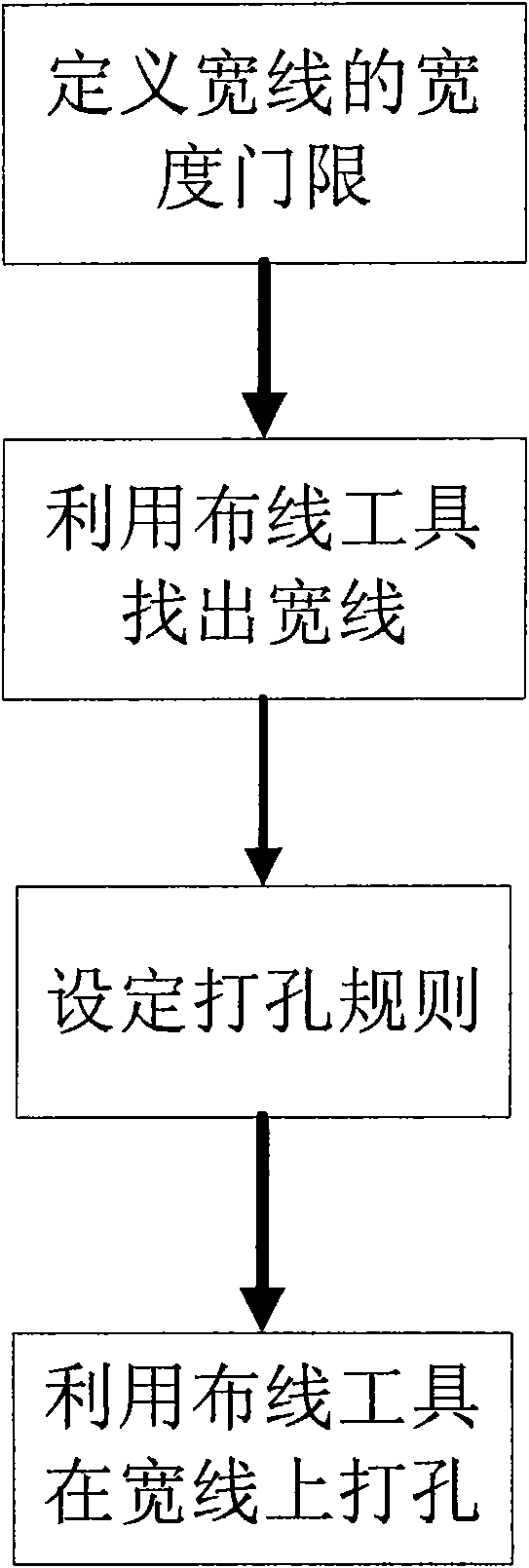

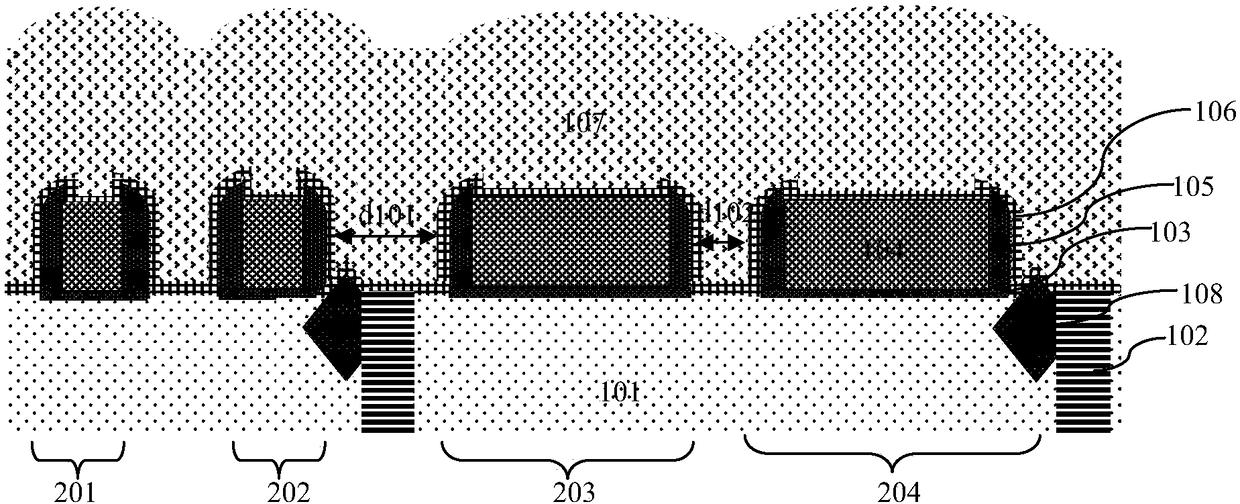

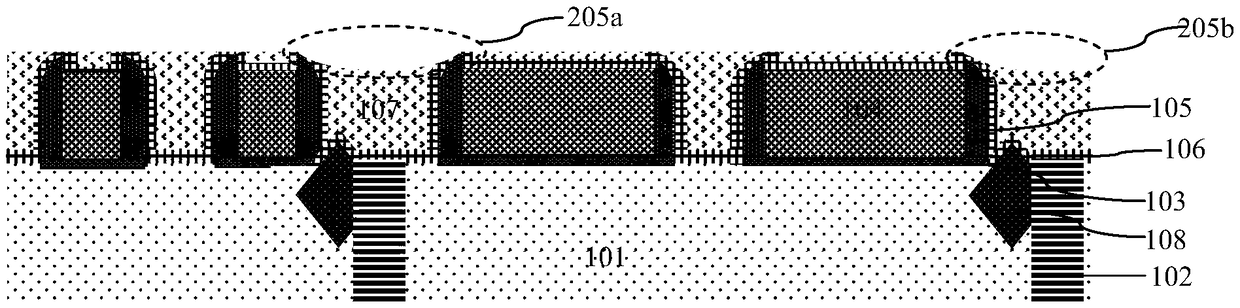

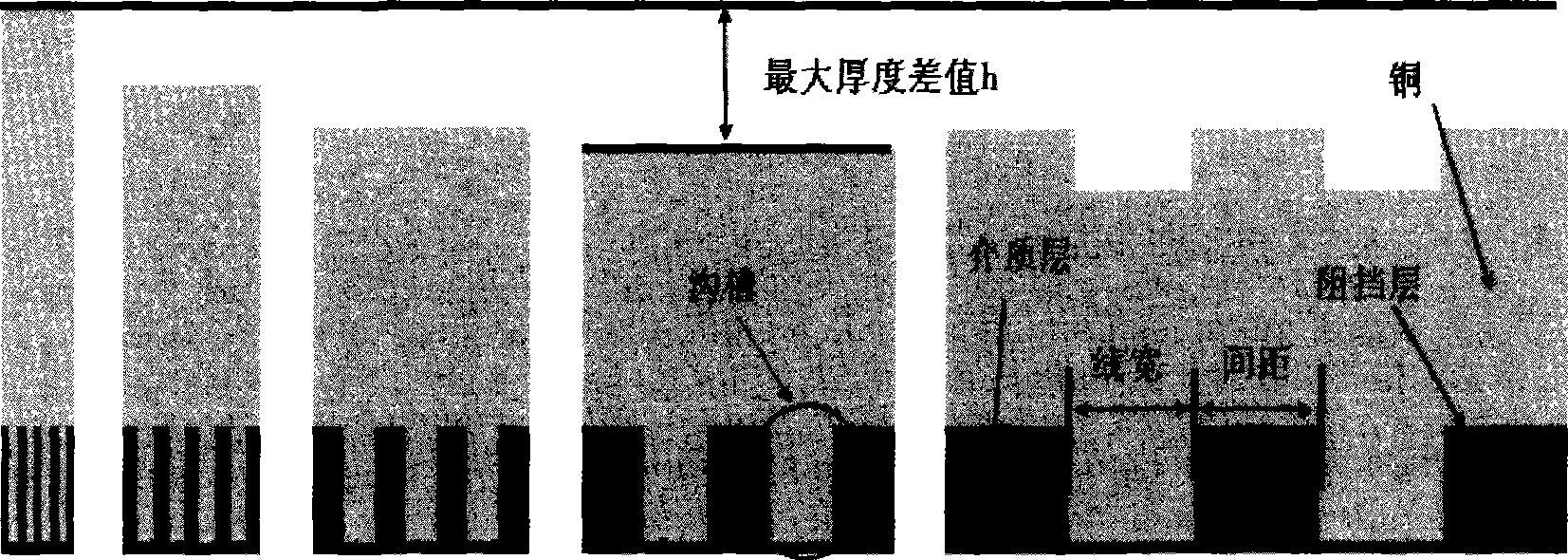

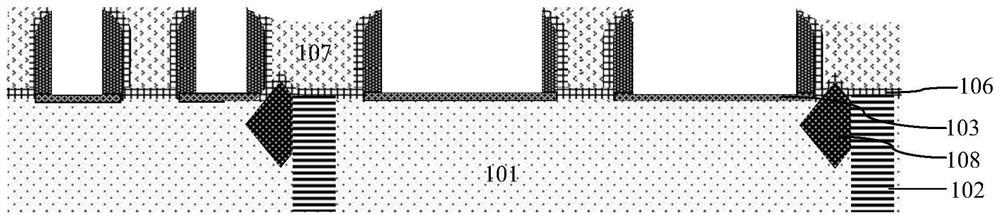

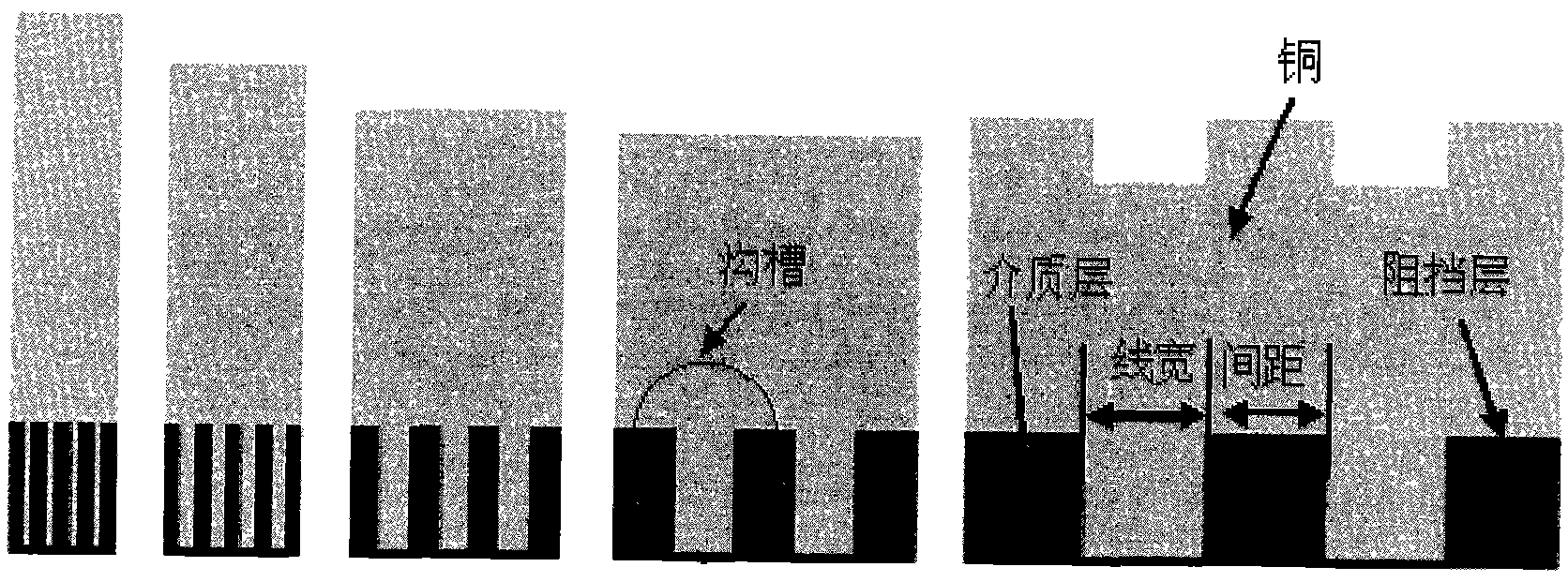

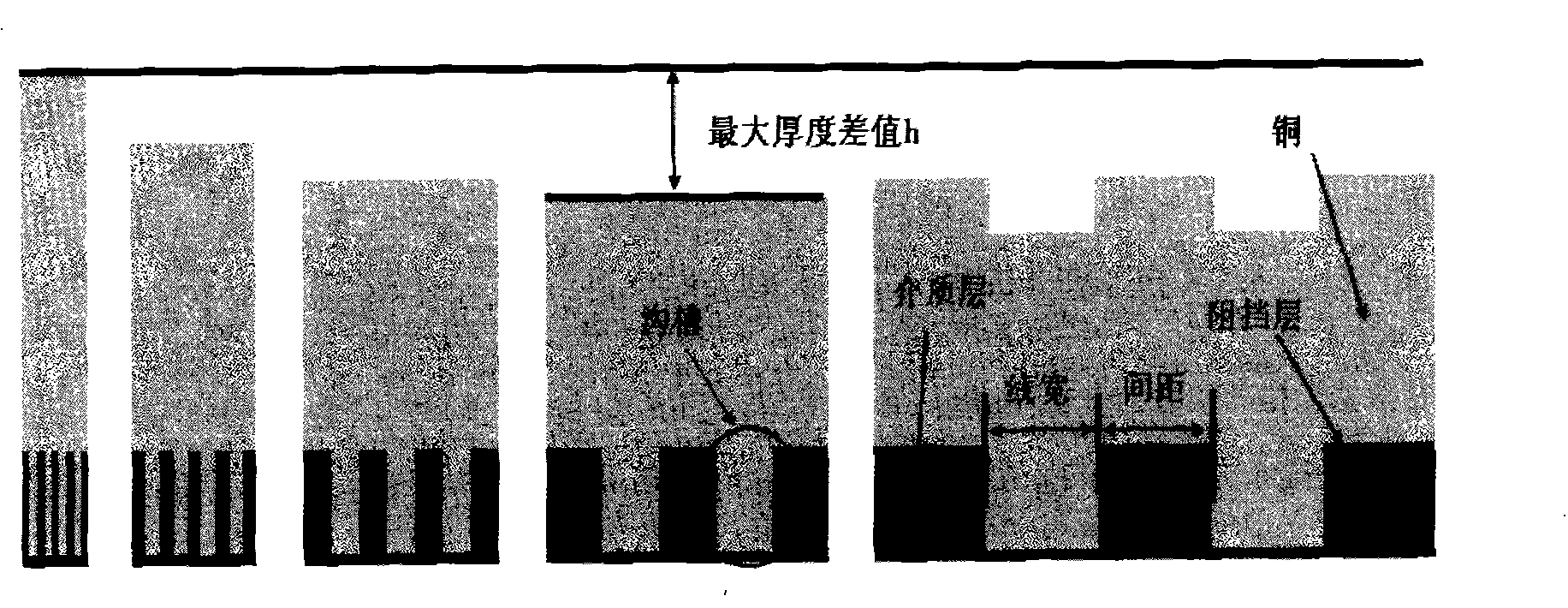

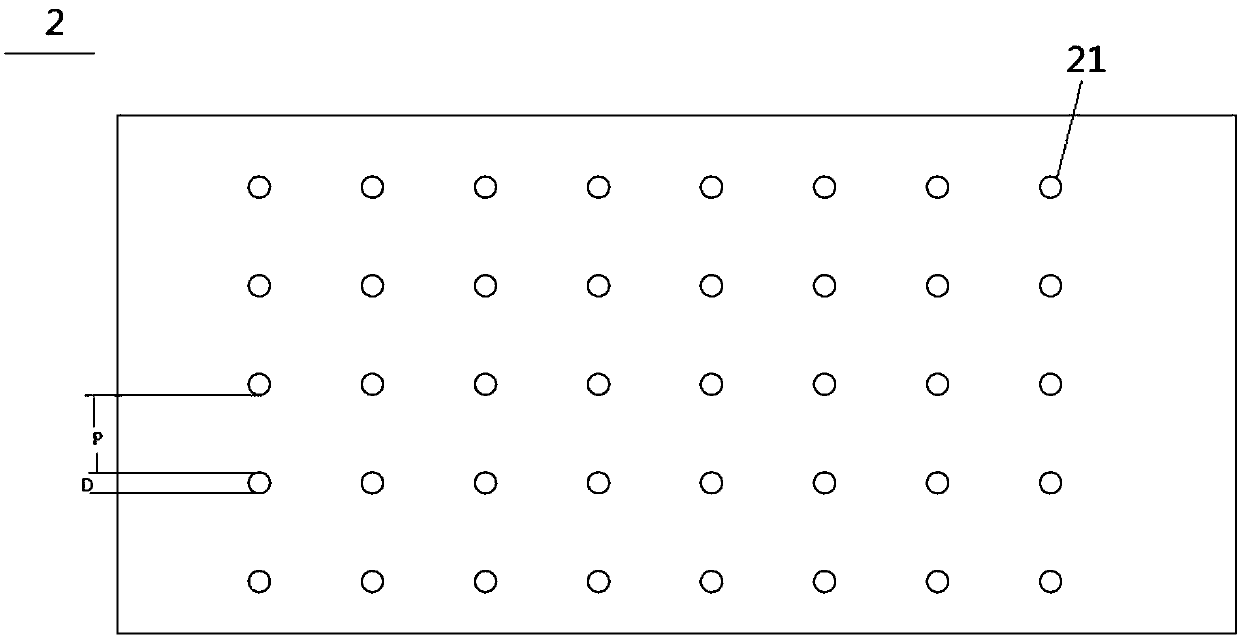

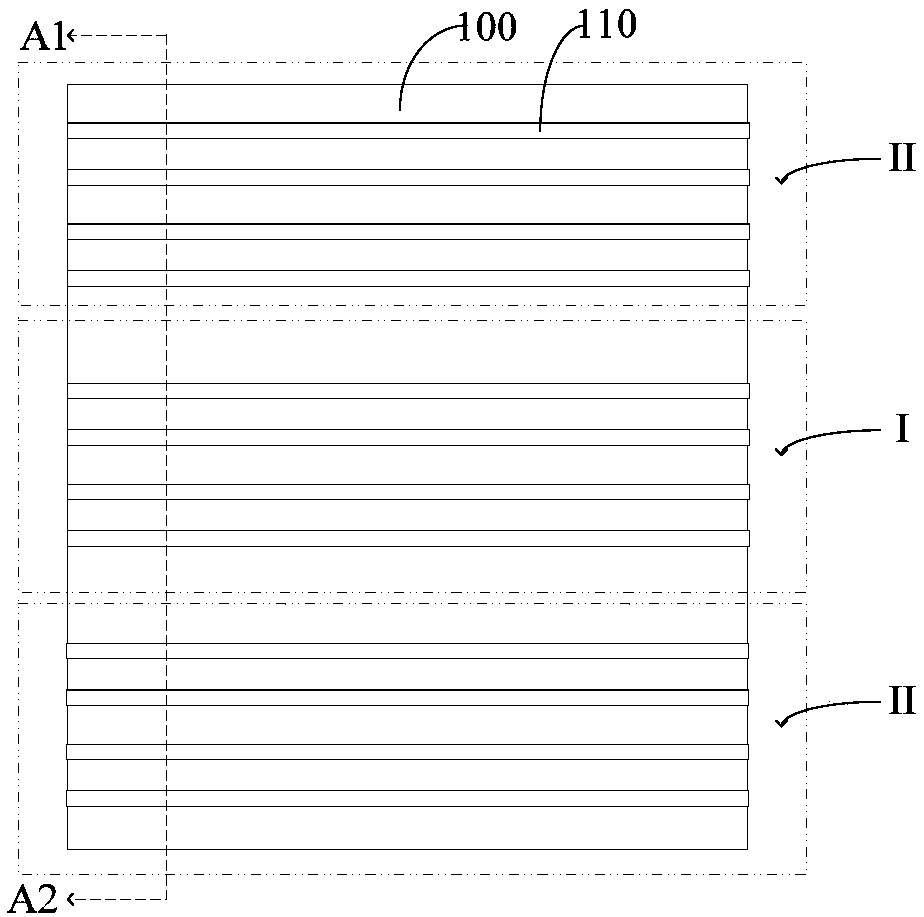

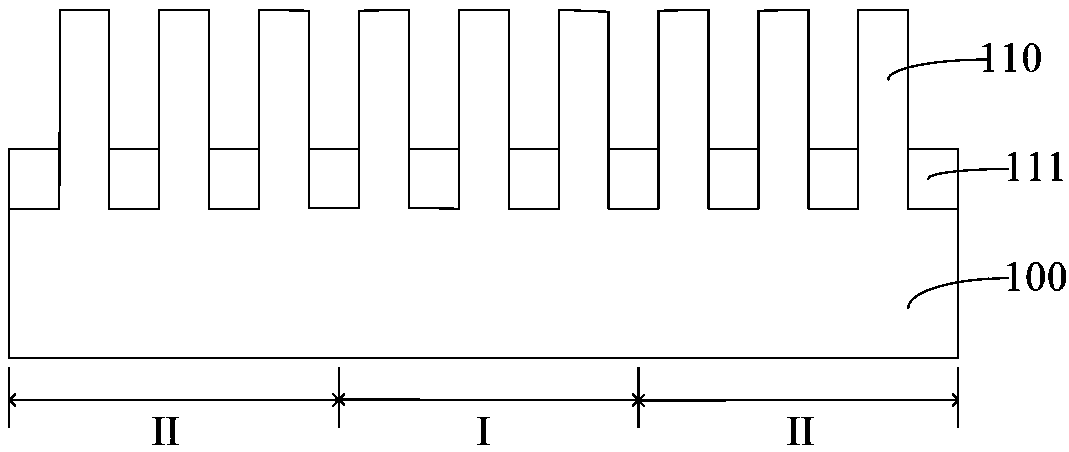

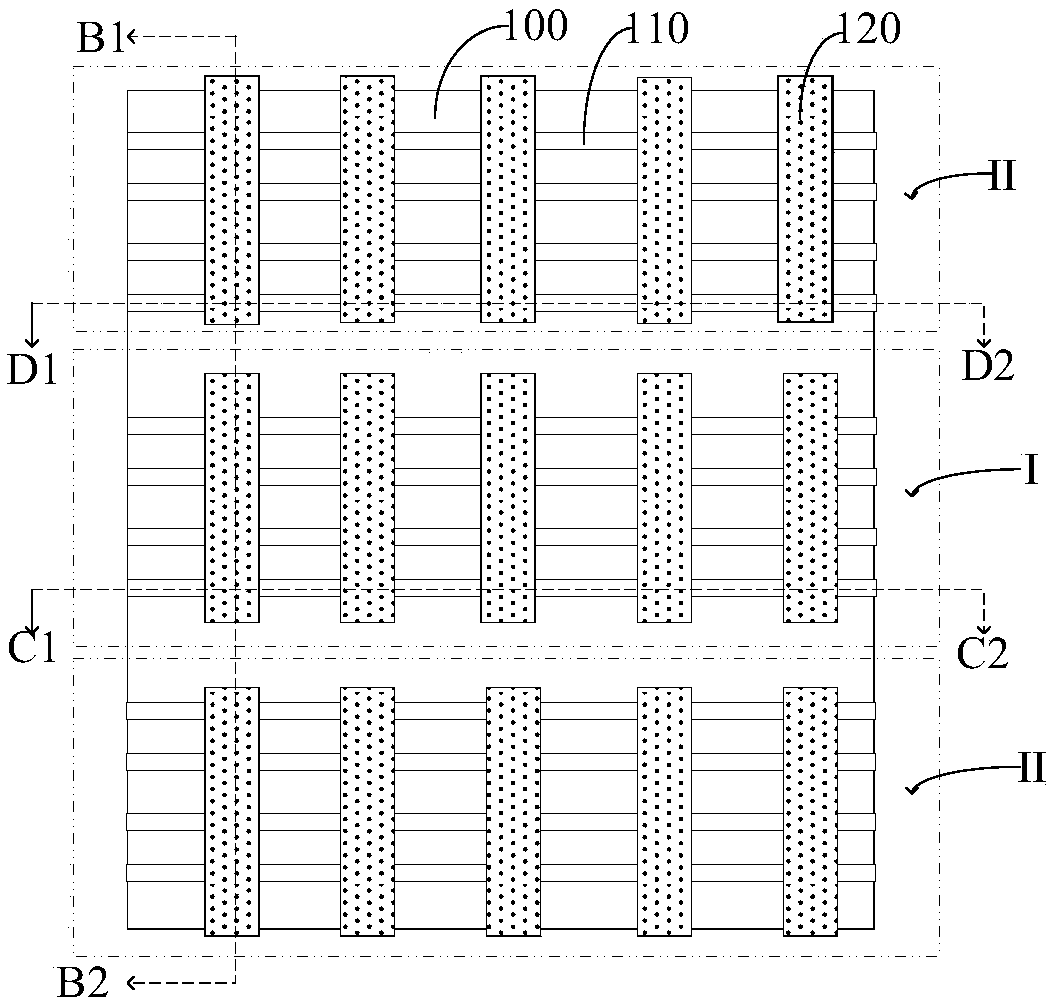

Integrated circuit layout structure and manufacturing method thereof

InactiveCN101887882AUniform growthAvoid hotspotsSemiconductor/solid-state device detailsSolid-state devicesState of artIntegrated circuit manufacturing

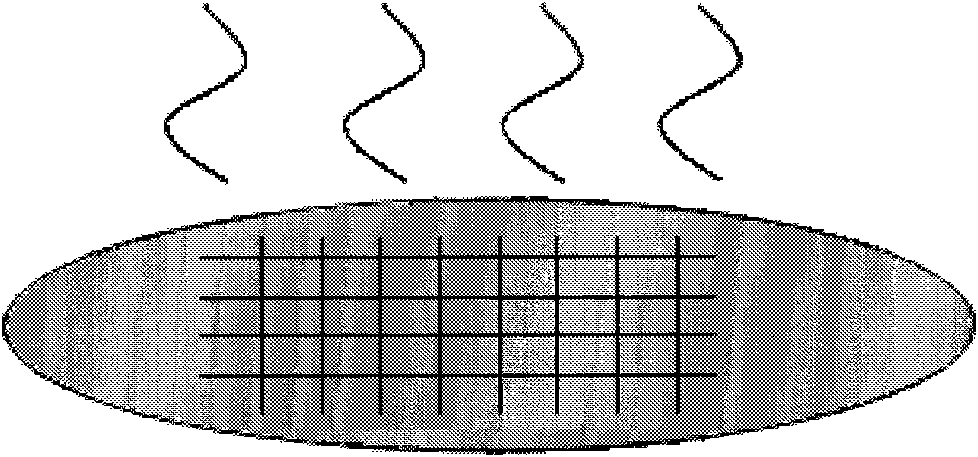

The invention relates to the fields of an integrated circuit manufacturing process and layout design, and discloses an integrated circuit layout structure and a manufacturing method thereof. In order to solve the problem of too low thickness of copper metal in a broad-line region of an integrated circuit layout after chemically mechanical polishing in the prior art, the invention provides an integrated circuit layout structure and a preparation method thereof. By regularly drilling holes for broad lines and through chemically mechanical polishing, the thickness of the copper metal of the broad lines is greatly improved, and the thickness of the copper metal on the broad lines and the thin lines is uniform, so the burden of the chemically mechanical polishing is lightened, the planization capacity is improved, the hotspot problems caused by the broad lines are avoided, and the finished product rate is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

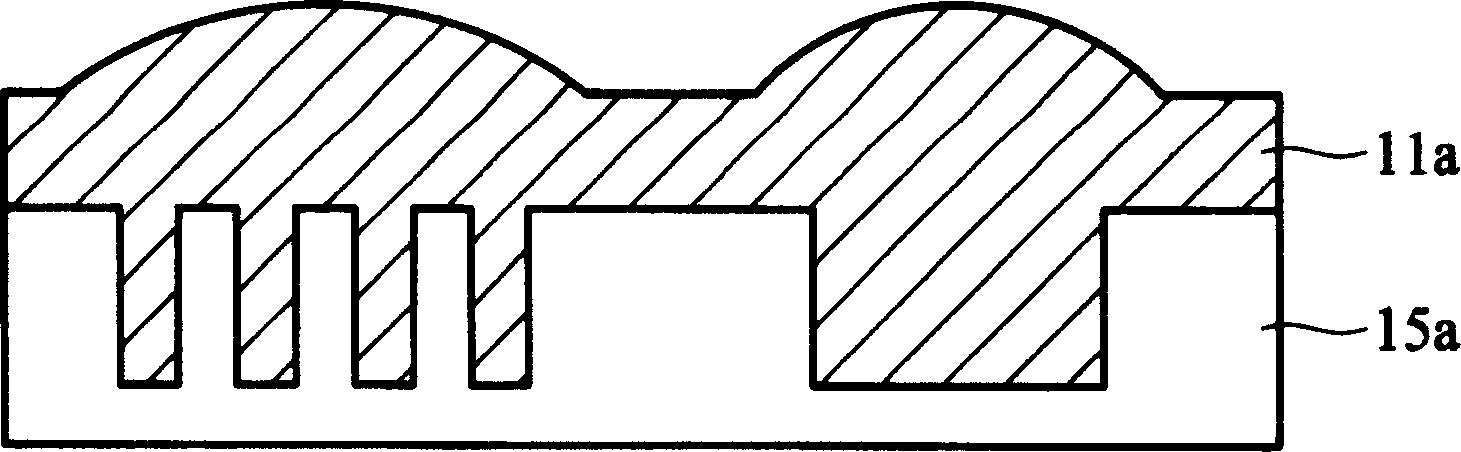

Interlayer film manufacturing method

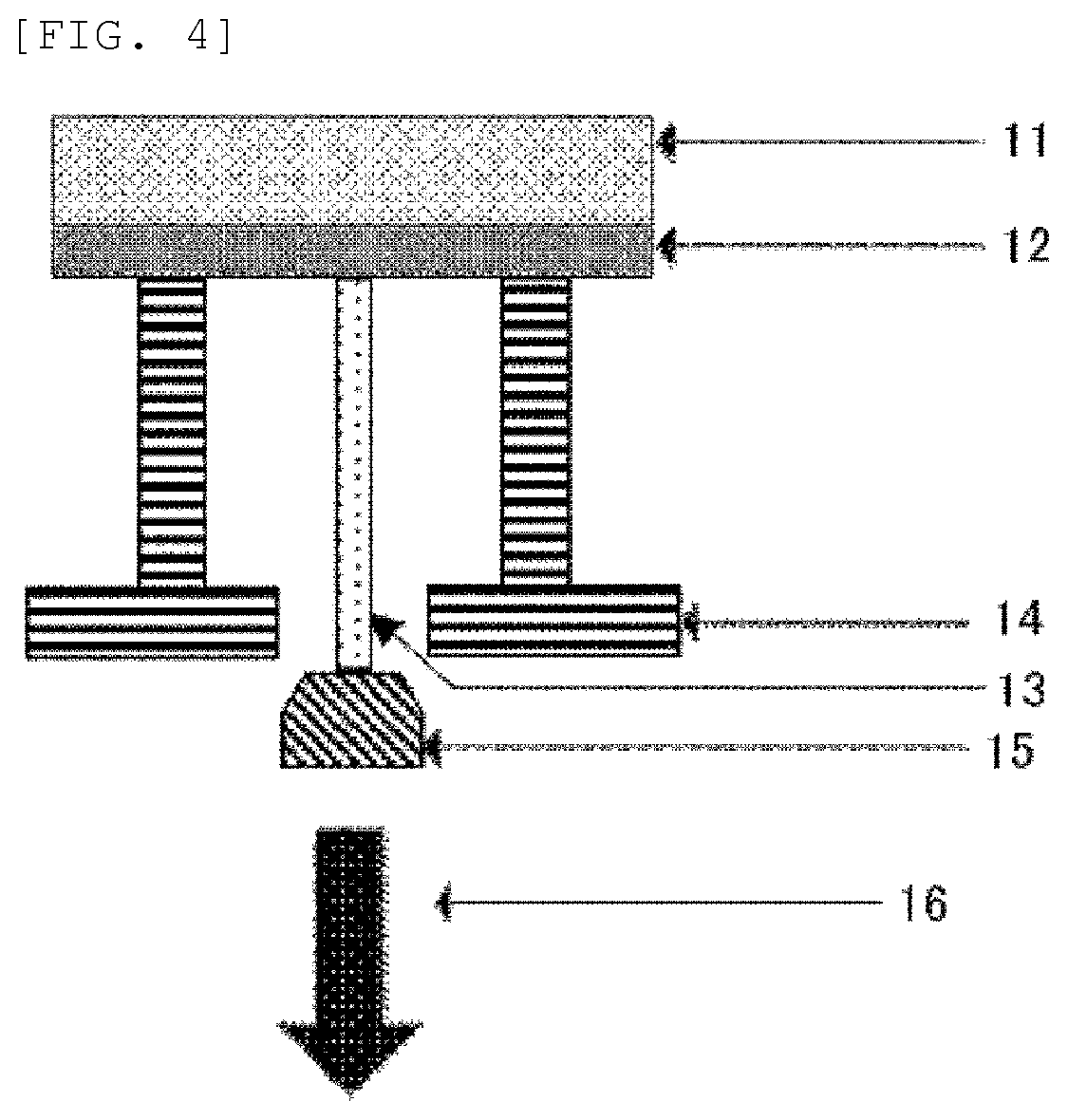

ActiveCN108878288AEffect on electrical performanceImprove surface flatnessSemiconductor/solid-state device manufacturingPower semiconductor deviceDevice material

The invention discloses an interlayer film manufacturing method. The interlayer film manufacturing method comprises the following steps: step one, providing a semiconductor substrate on which a pattern structure of a semiconductor device is formed; step two, forming a first insulating layer on the bottom surface and side surfaces of the pattern spacer and the surface of the pattern structure outside the pattern spacer; step three, forming a second insulating layer to completely fill the pattern spacer and extend outside the pattern spacer; and step four: performing chemical mechanical polishing on the second insulating layer and the first insulating layer with the pattern structure as a stop layer, and forming the interlayer film formed by stacking the first and second insulating layers filled in the pattern spacer. The interlayer film manufacturing method can reduce or eliminate dishing defects on the interlayer film surface at the top of the pattern spacer, can improve the flatness of the entire interlayer film, and can improve the electrical properties of semiconductor devices.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

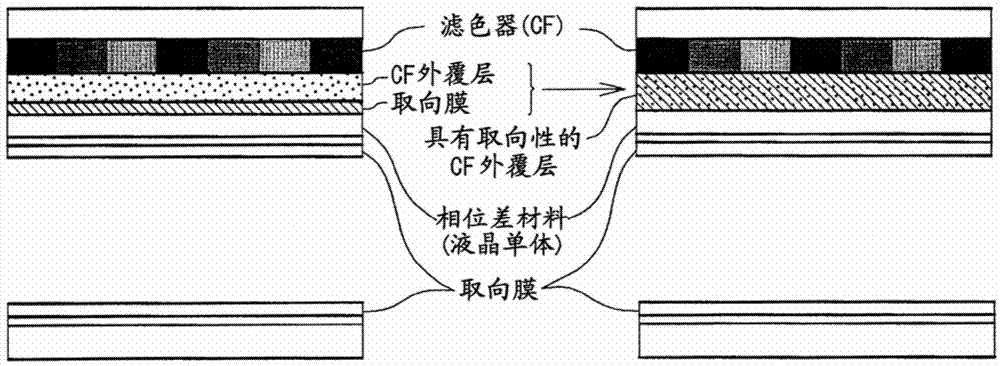

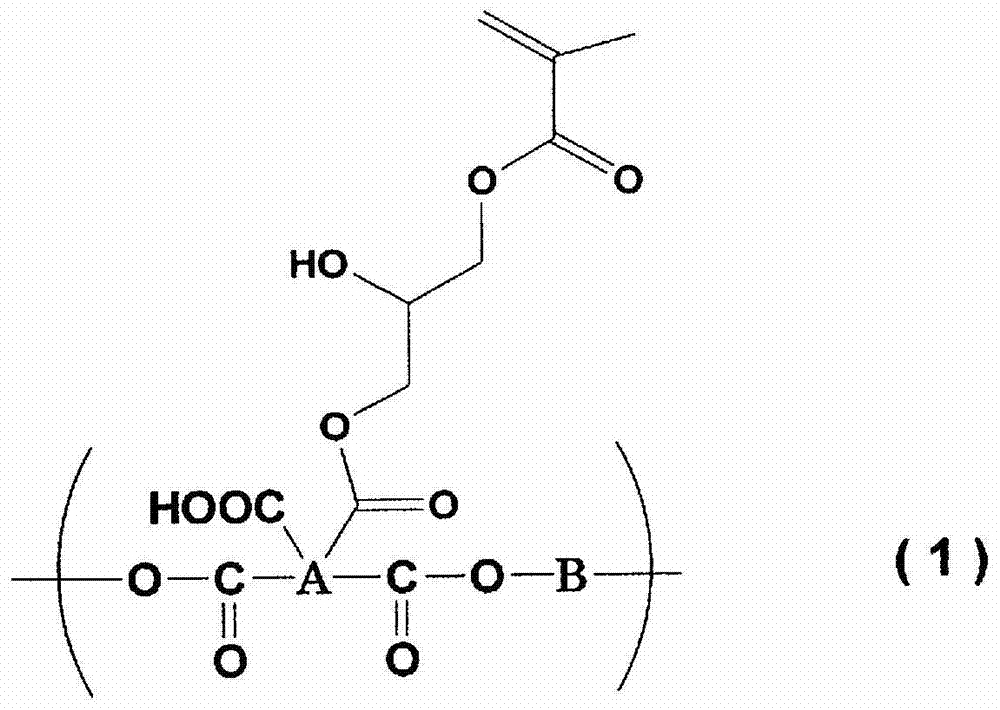

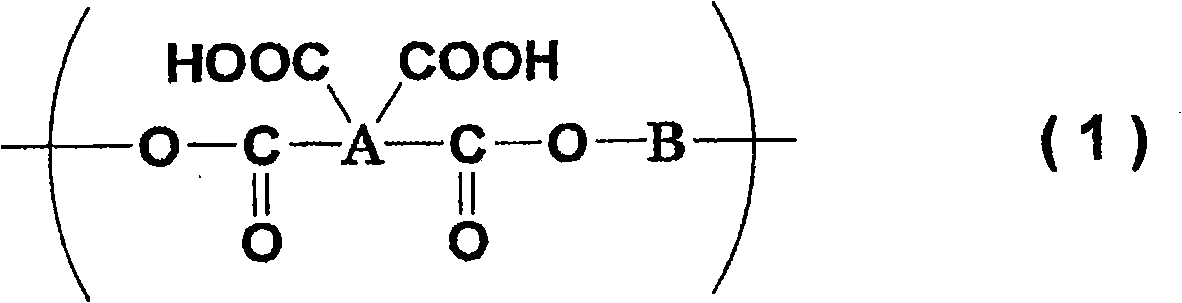

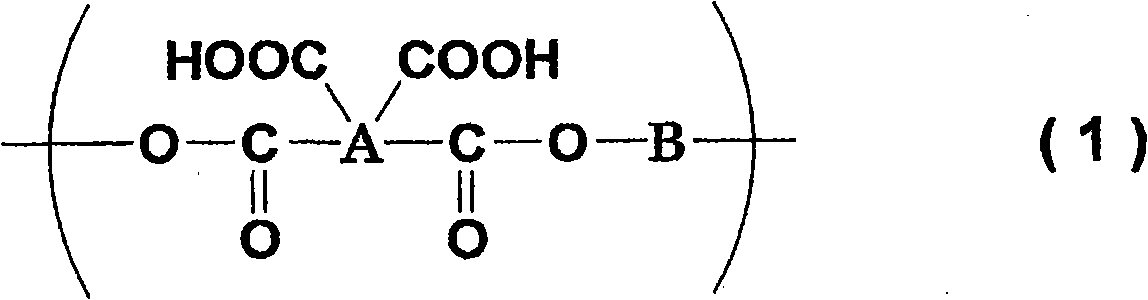

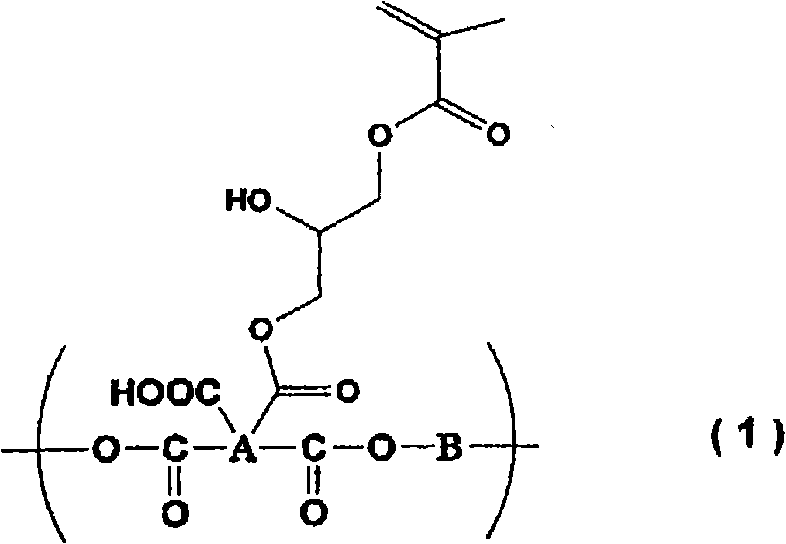

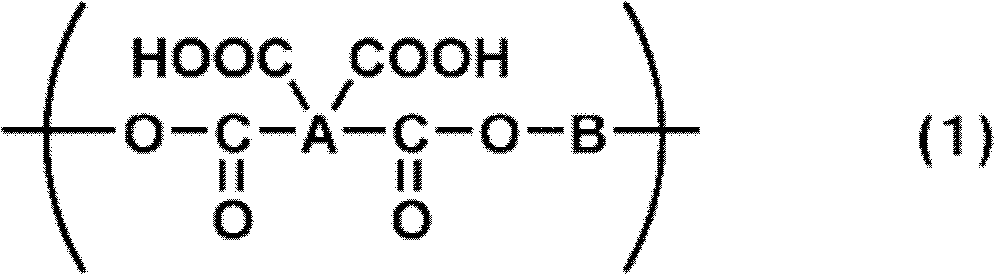

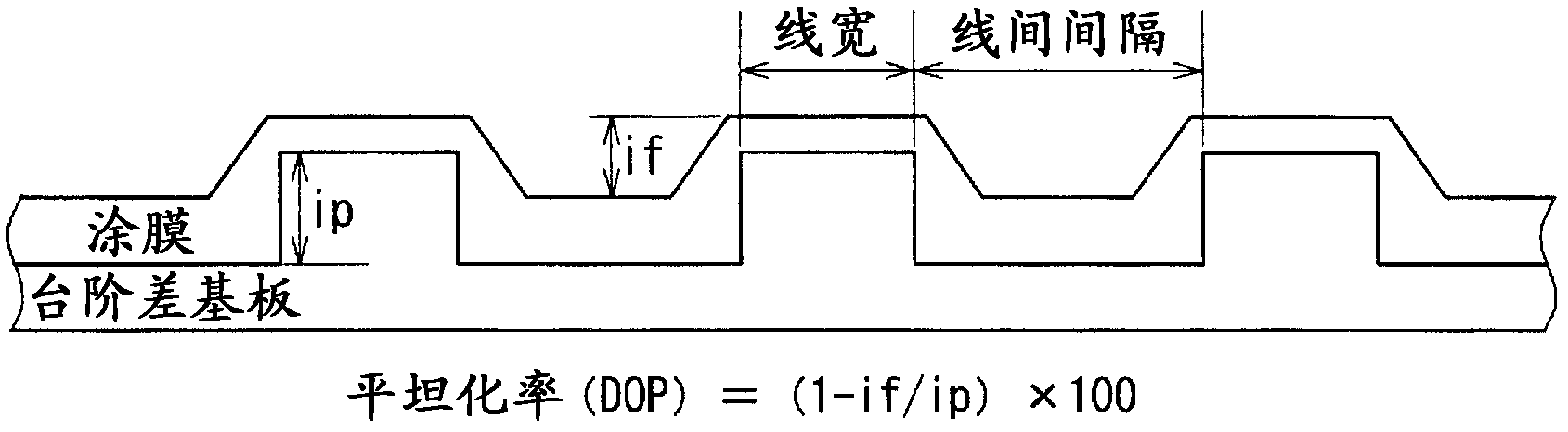

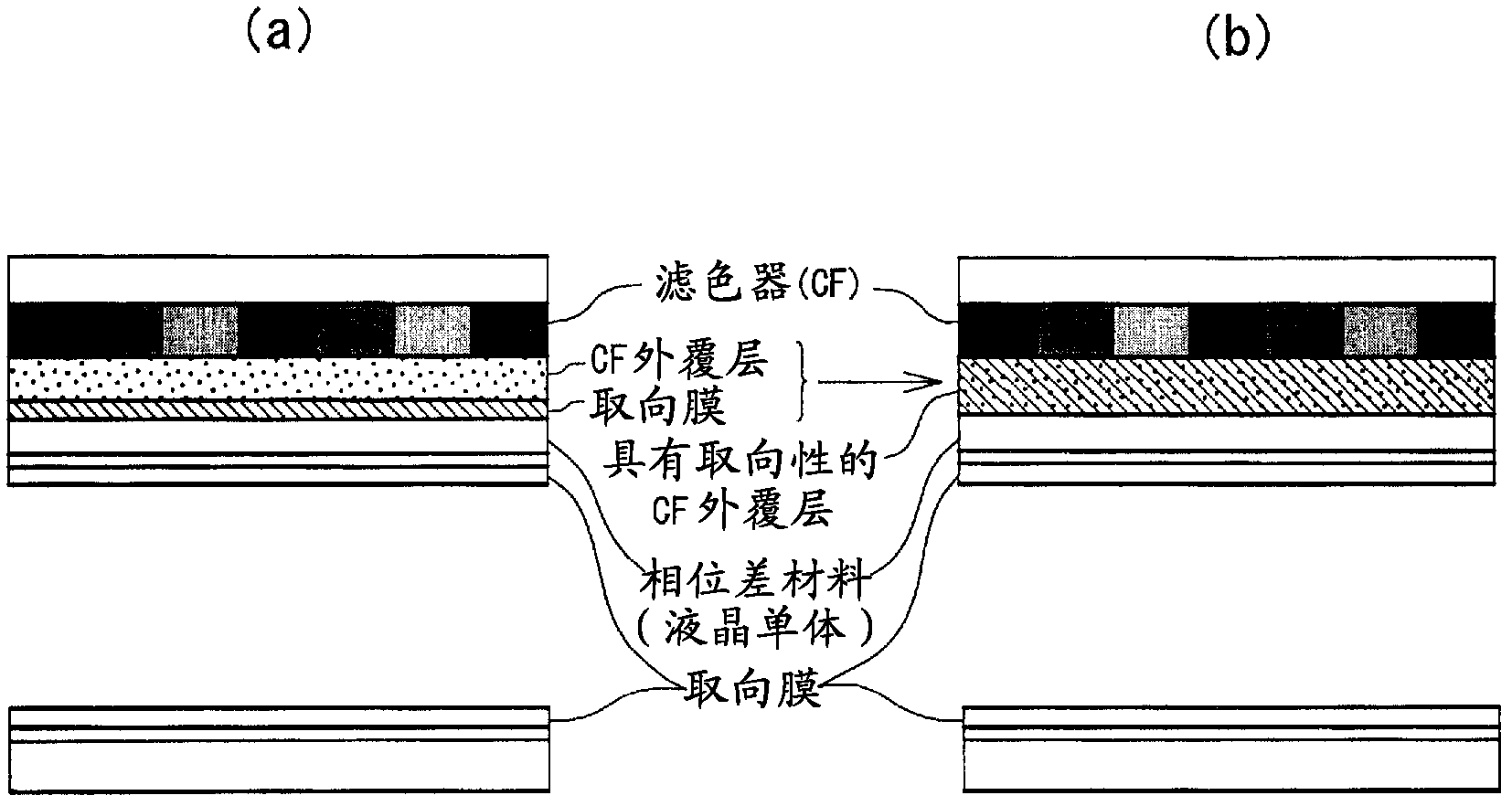

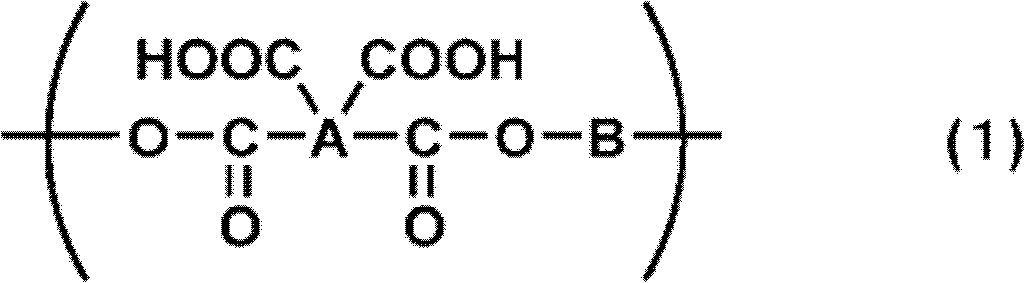

Cured film

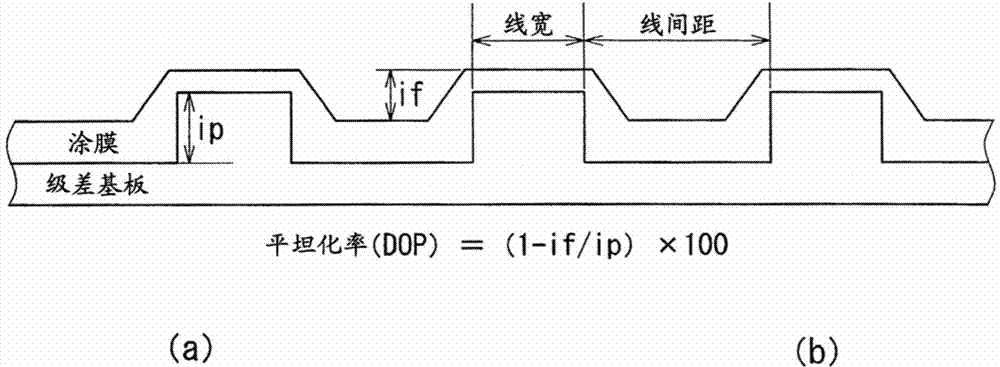

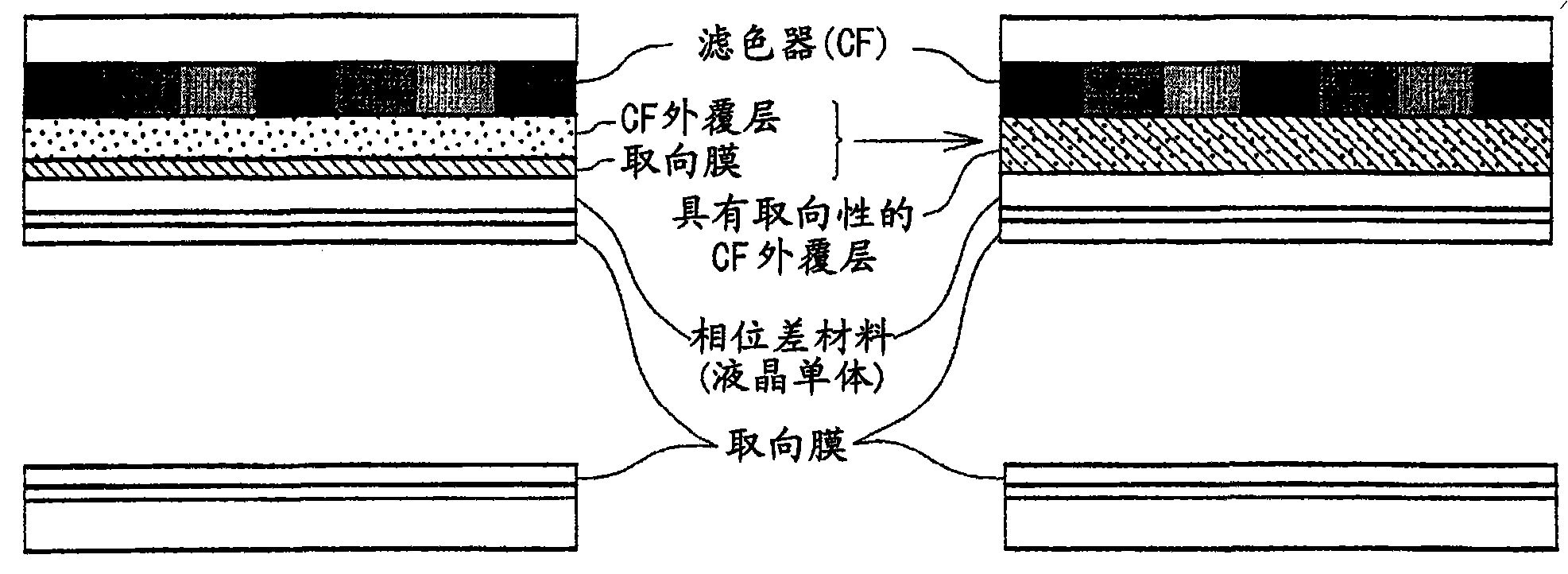

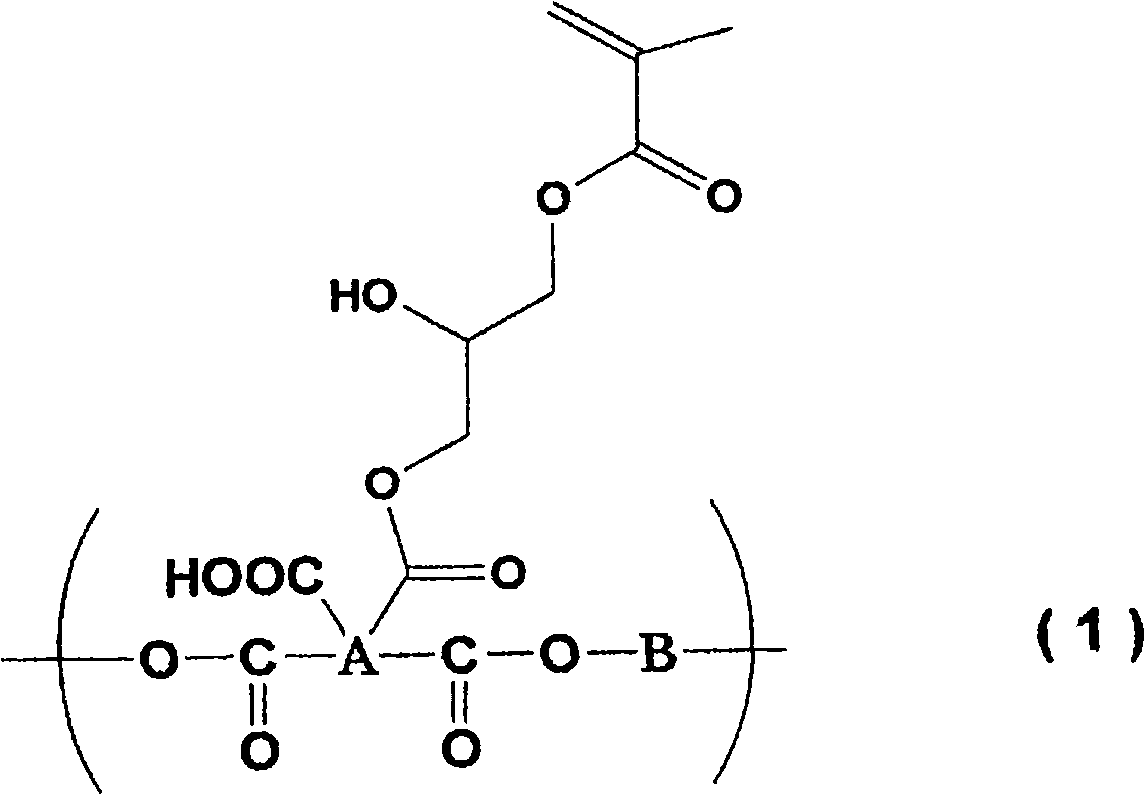

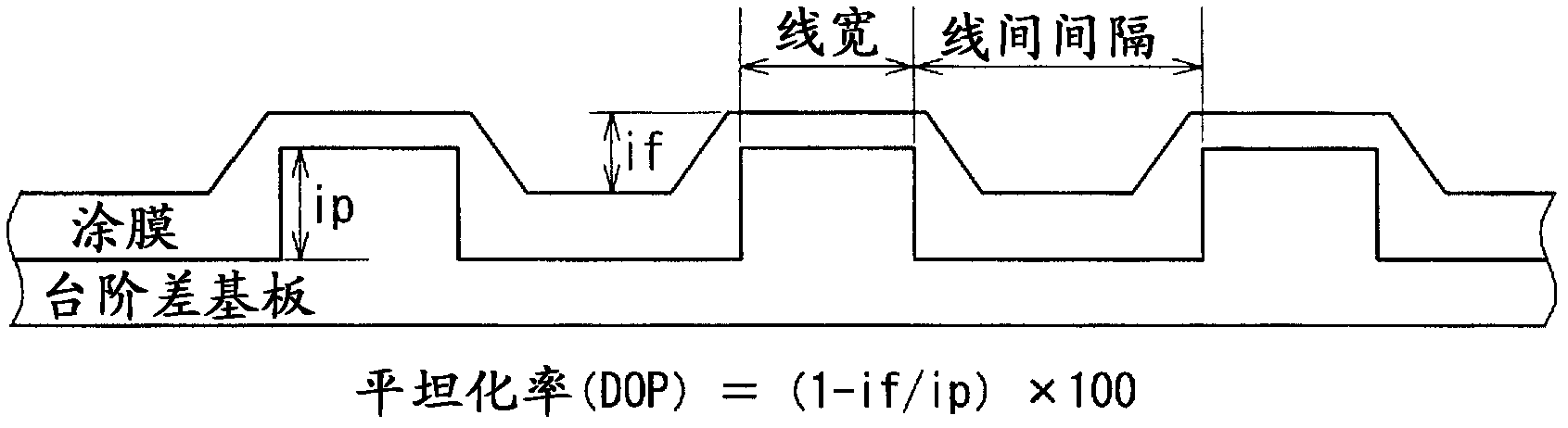

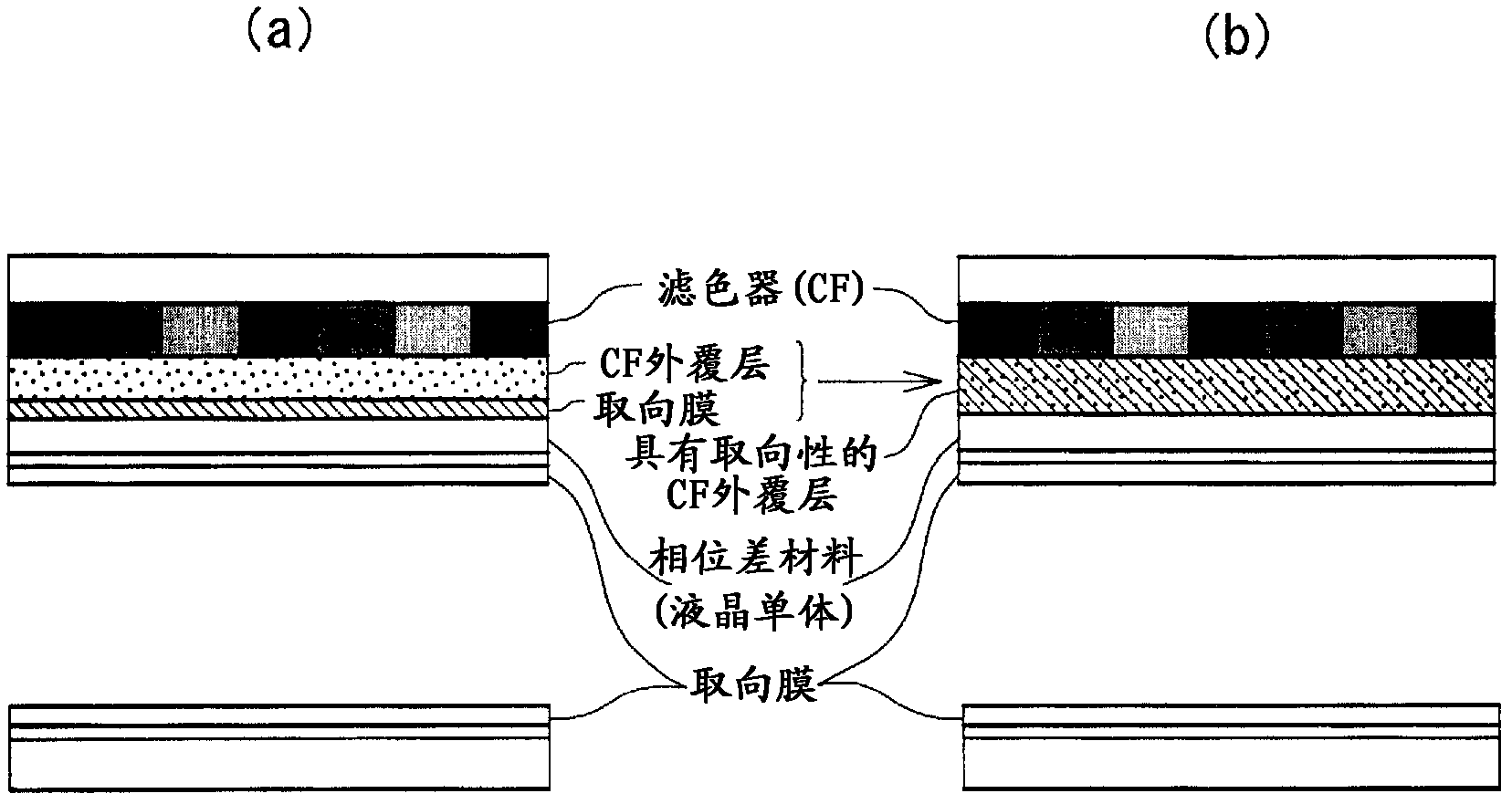

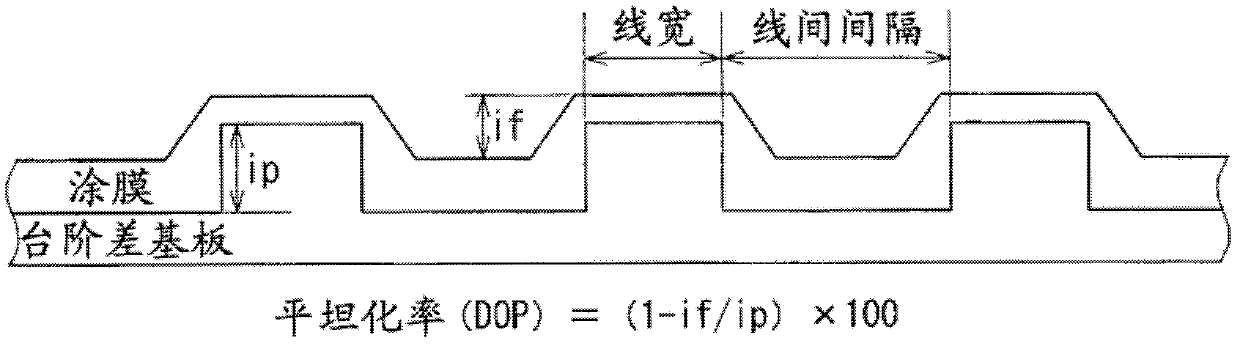

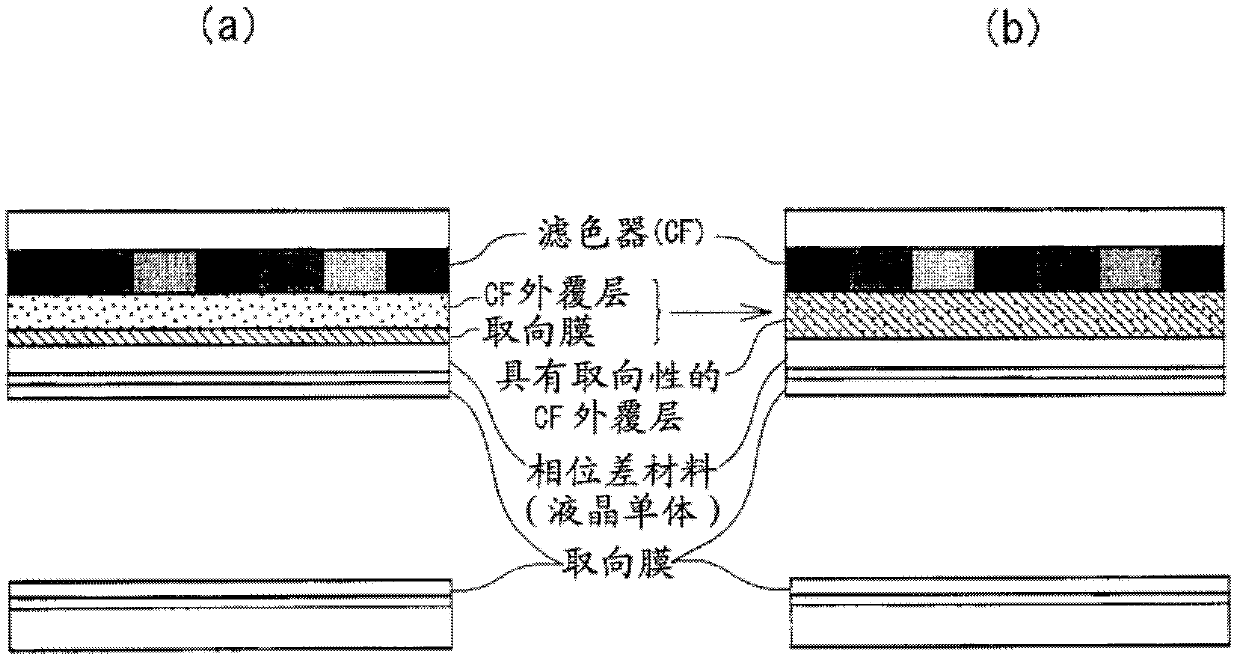

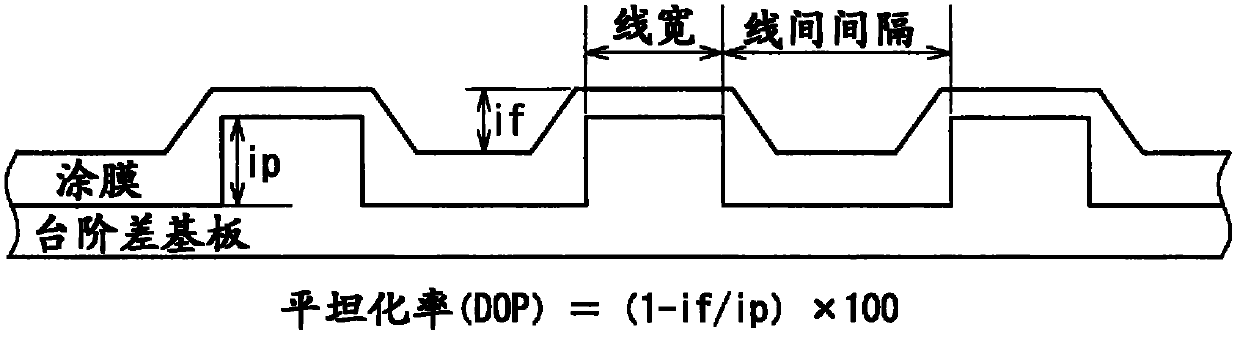

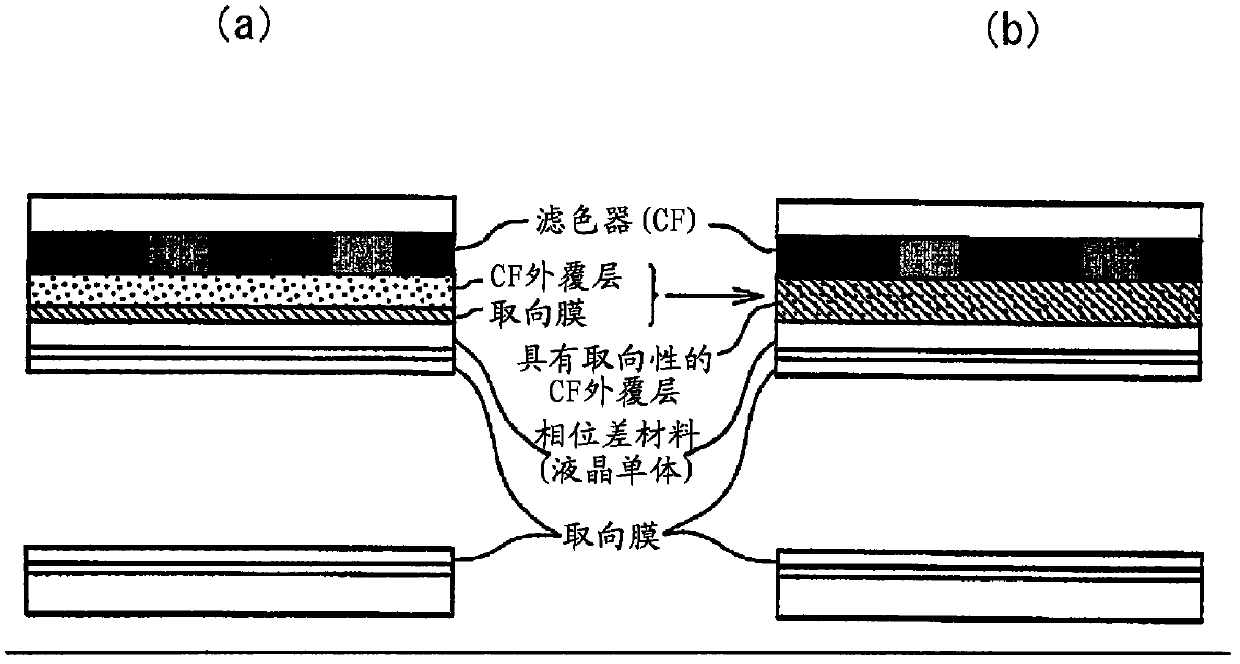

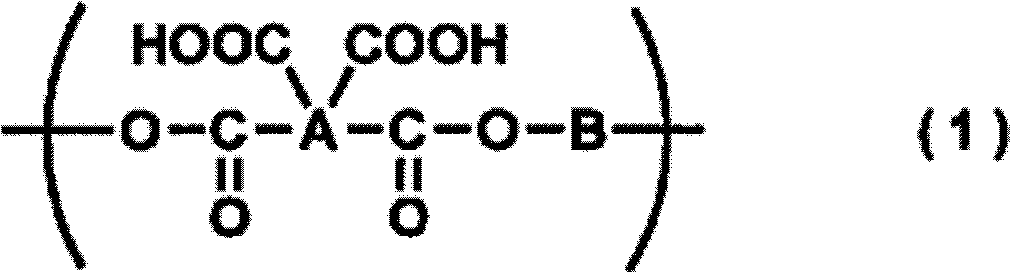

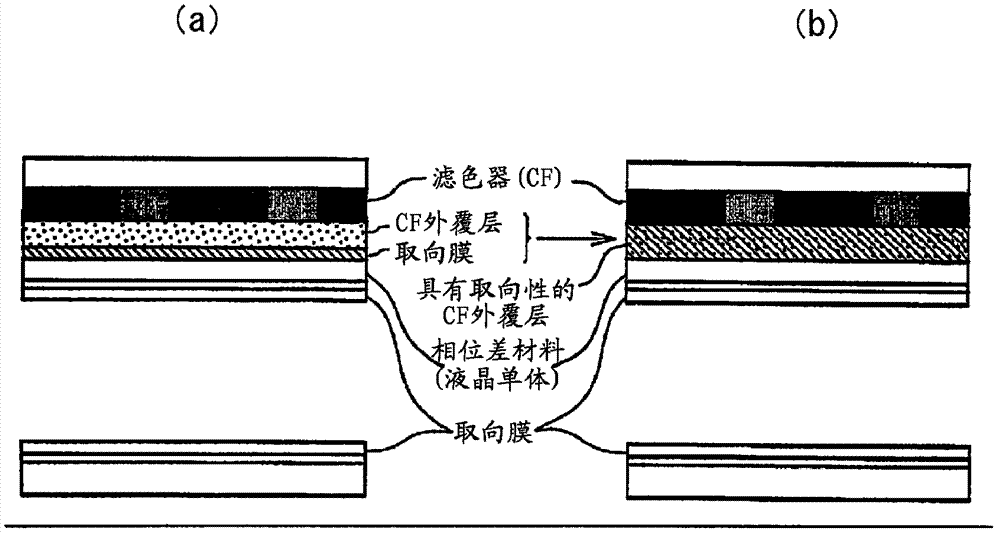

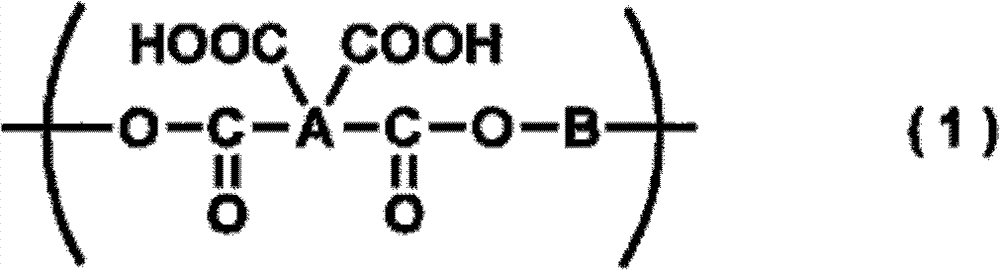

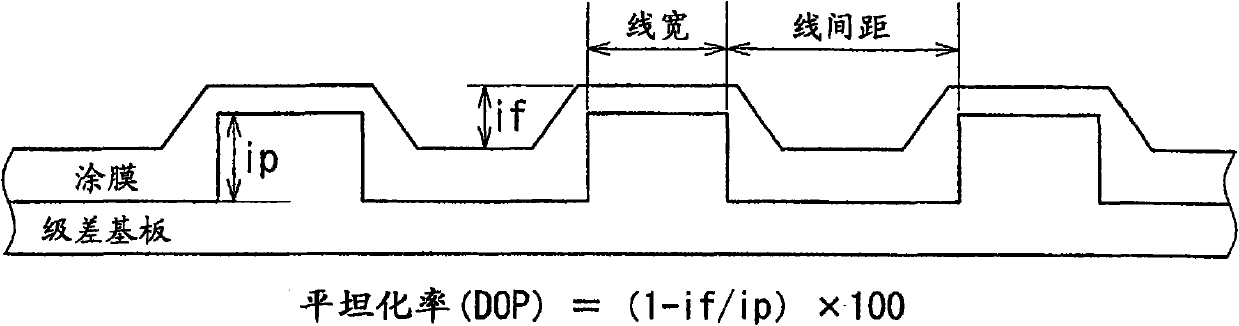

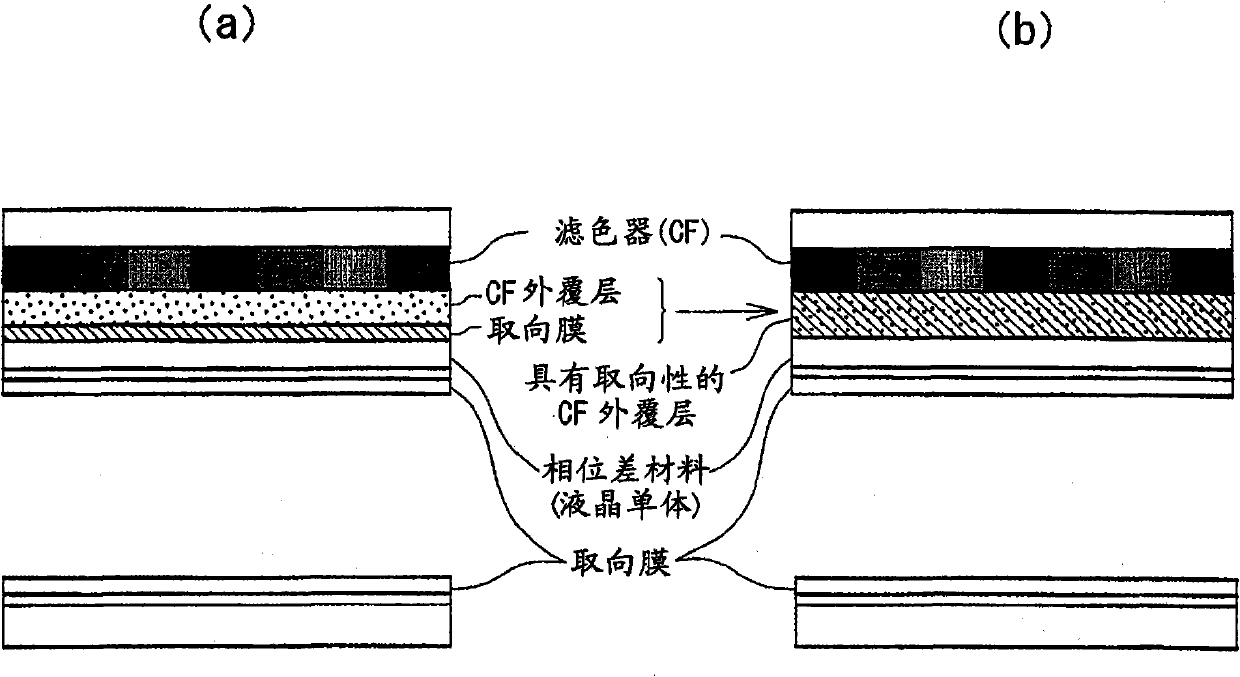

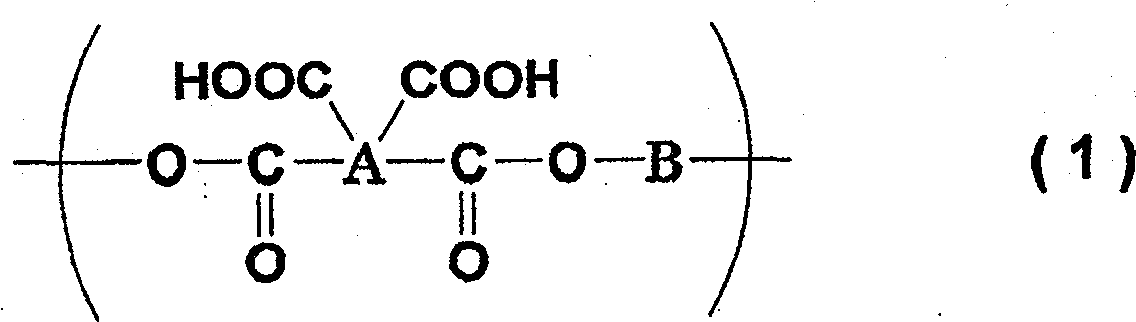

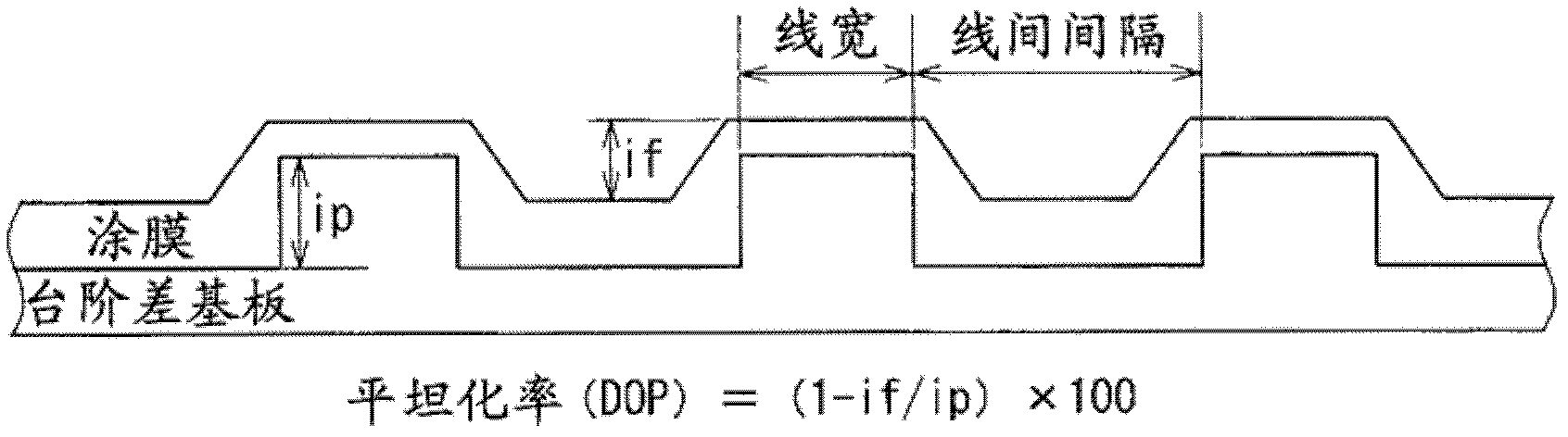

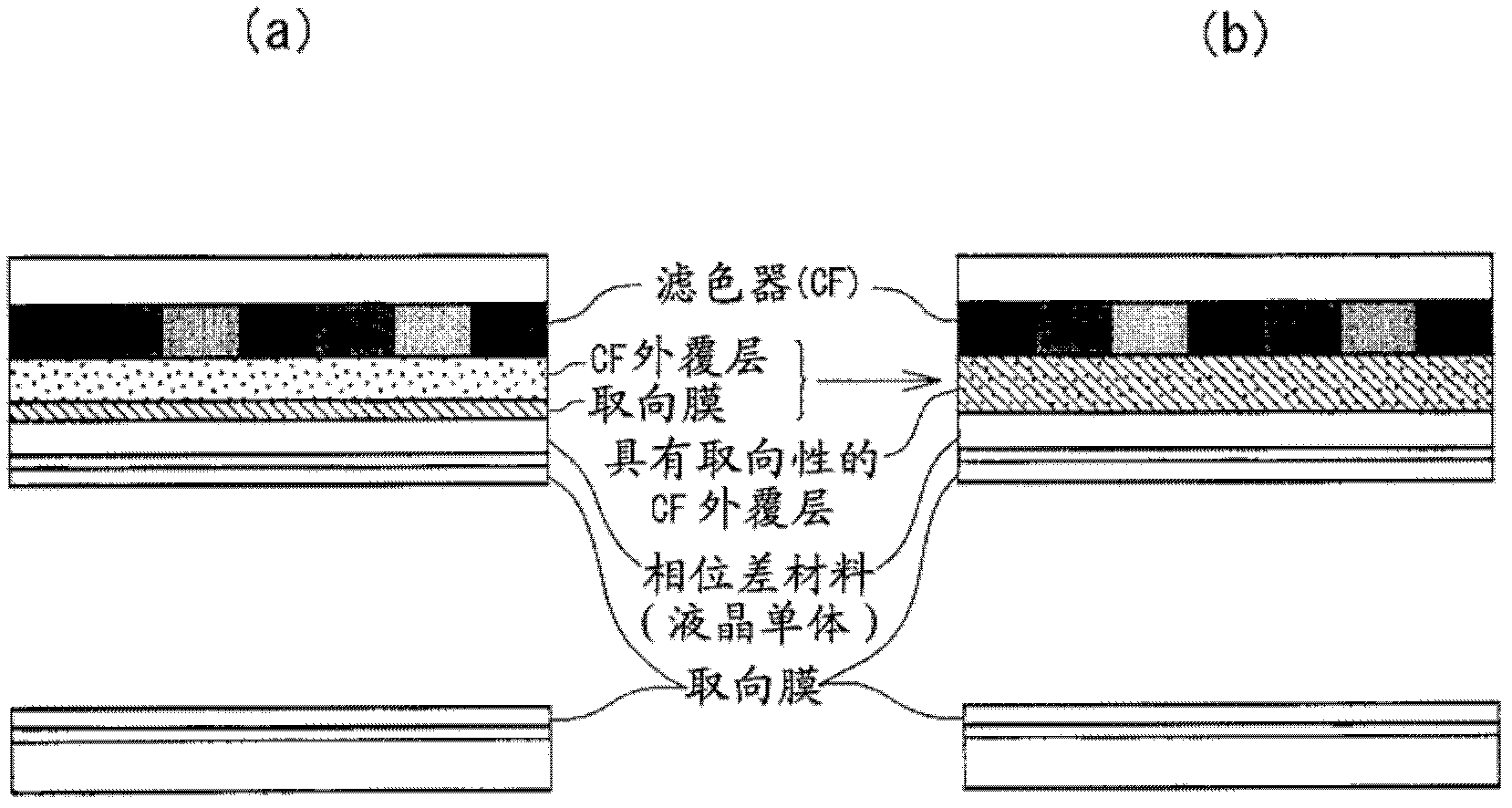

InactiveCN103709911AImprove planarization effectHigh transparencyNon-linear opticsPolyester coatingsProduction linePolystyrene

To provide a material which can be formed into a cured film having high solvent resistance, liquid crystal-aligning properties, high transparency and high planarization, and which can be dissolved in a glycol-type solvent and is therefore applicable in the production line for a planarized film of a color filter when used in the formation of a cured film from the material. Disclosed are: a polyester resin solution for the production of a thermally cured film, which comprises a polyester polymer having a structural unit represented by the formula (1); and a cured film, a liquid crystal alignment layer and a planarized film each of which is produced from the polyester resin solution. (1) wherein A and B independently represent an organic group containing a ring structure.

Owner:NISSAN CHEM IND LTD

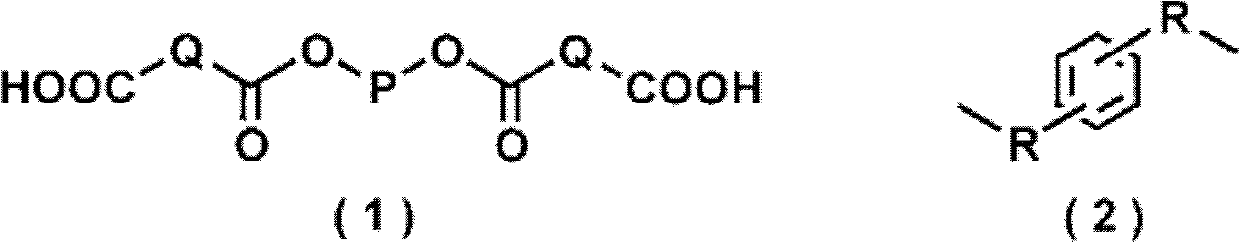

Polyester composition for production of thermally cured film

ActiveCN101809057AImprove planarization effectHigh transparencyEpoxy resin coatingsNon-linear opticsPolyesterProduction line

To provide a material which can be formed into a cured film having high solvent resistance, liquid crystal-aligning properties, heat resistance, high transparency and high planarization, and which can be dissolved in a glycol-type solvent and a lactic acid ester-type solvent (which are solvents applicable in the production line for a planarized film of a color filter) in the formation of a cured film from the material. Disclosed is a polyester composition for the production of a thermally cured film, which comprises the following components (A) and (B): (A) a polyester having a constituent unit represented by the formula (1); and (B) an epoxy compound having two or more epoxy groups. (1) wherein A and B independently represent an organic group containing a ring structure.

Owner:NISSAN CHEM IND LTD

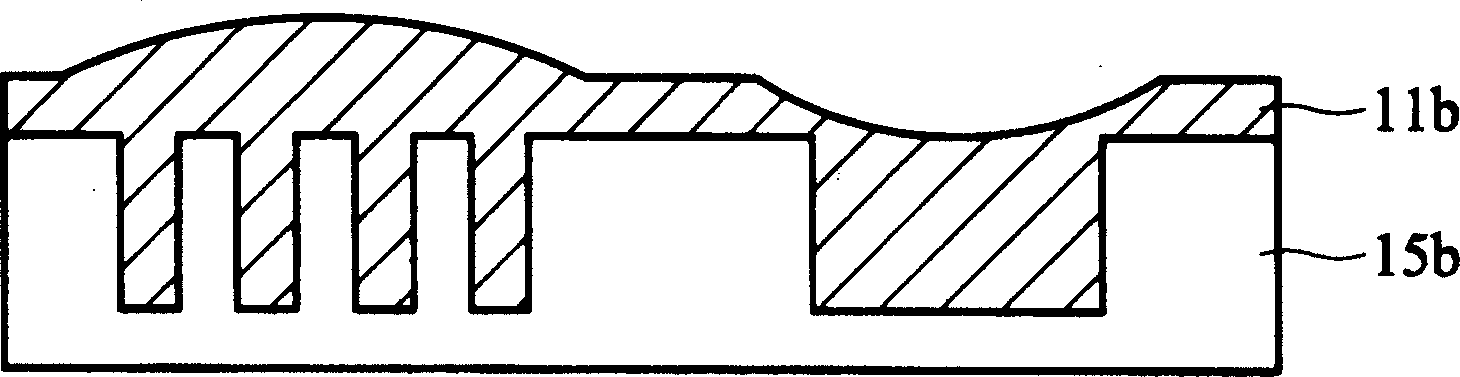

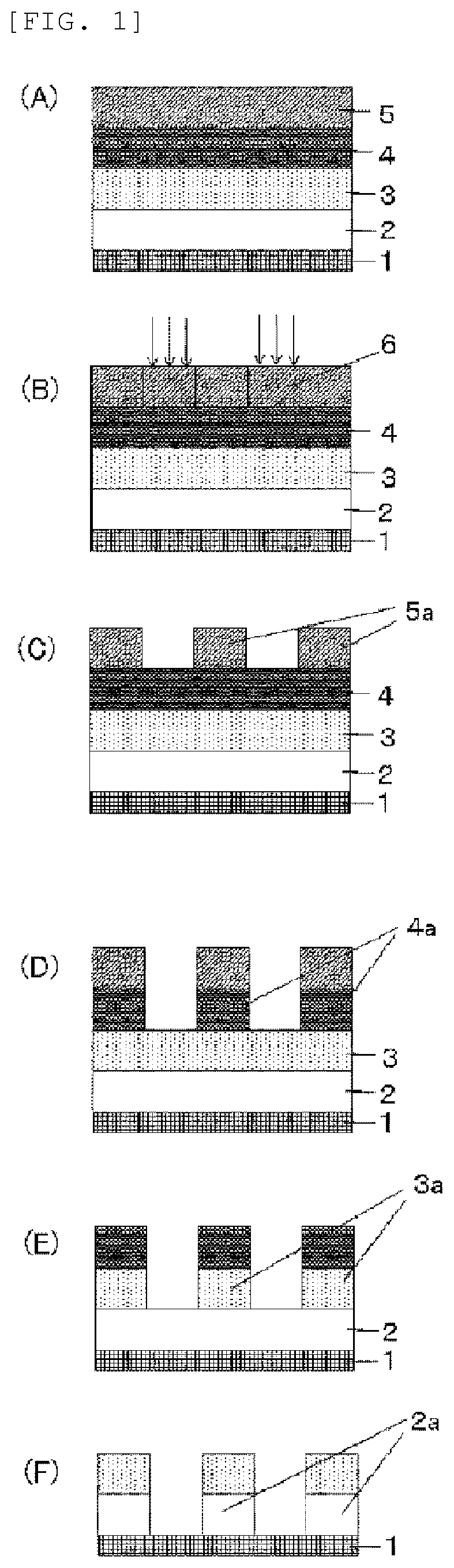

Material for forming organic film, method for forming organic film, patterning process, and compound

PendingUS20210198472A1High fill propertyHigh planarizing propertyOrganic chemistrySemiconductor/solid-state device manufacturingPolymer chemistryOrganic film

The present invention provides a material for forming an organic film, containing a compound shown by the following general formula (1), and an organic solvent. In the formula (1), X represents an organic group having a valency of n1 and 2 to 50 carbon atoms, n1 represents an integer of 2 to 10, R1 represents at least one or more of the following formulae (2) to (4), where l1 represents 0 or 1, and l2 represents 0 or 1. Thus, provided is an organic film material for forming an organic film that has all of high filling property, high planarizing property, and excellent adhesive force to a substrate.

Owner:SHIN ETSU CHEM CO LTD

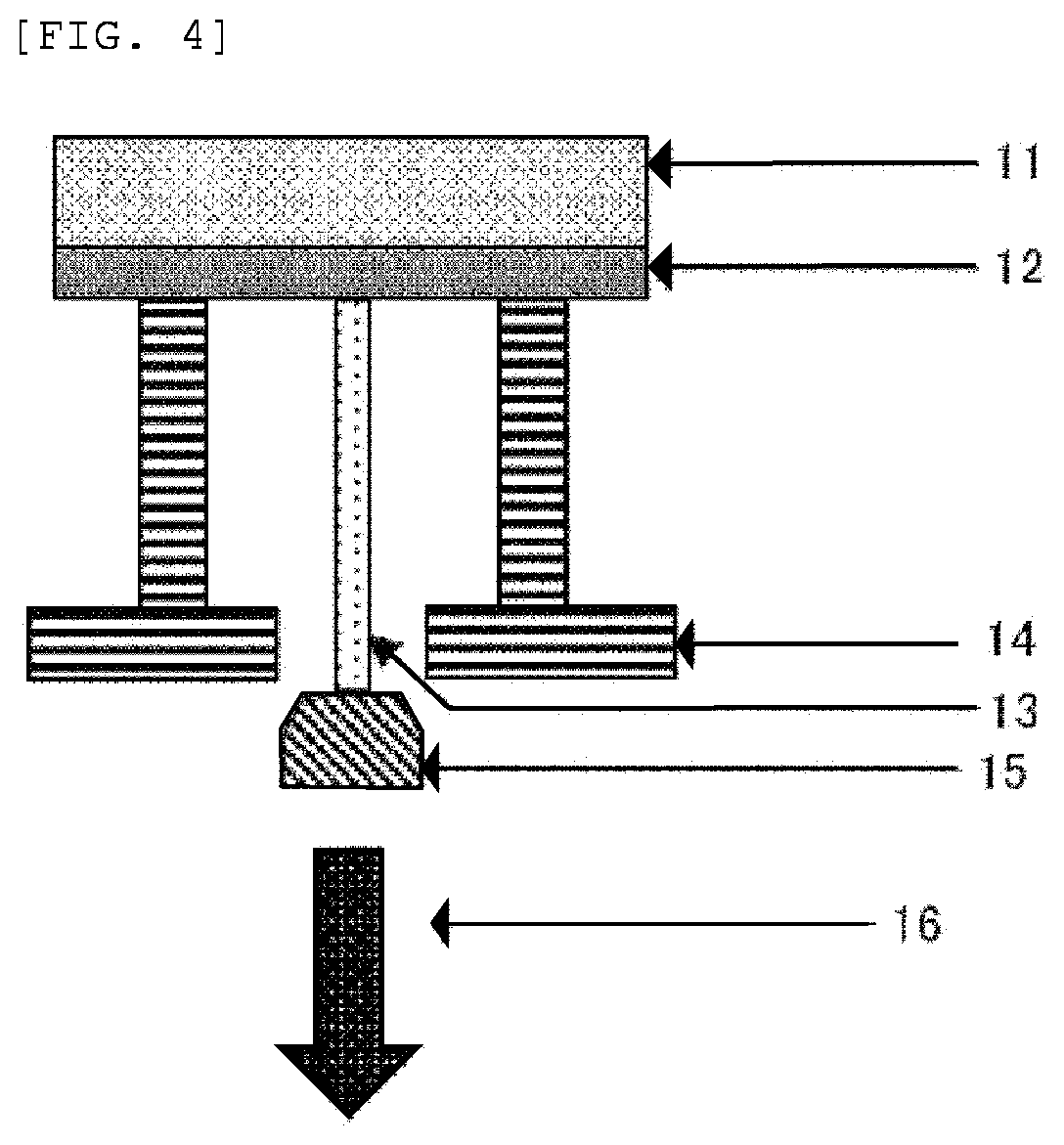

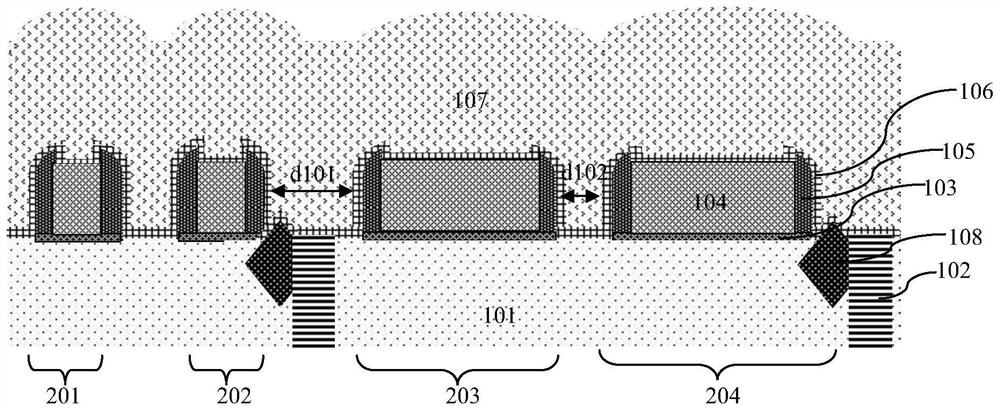

Method of manufacturing embedded magnetoresistive random access memory

ActiveUS10535817B1Improve planarization effectImprove flattening effectMagnetic-field-controlled resistorsSolid-state devicesMemory cellDielectric layer

A method of manufacturing an embedded magnetoresistive random access memory including the following steps is provided. A memory cell stack structure is formed on a substrate structure. The memory cell stack structure includes a first electrode, a second electrode, and a magnetic tunnel junction structure. A first dielectric layer covering the memory cell stack structure is formed. A metal nitride layer is formed on the first dielectric layer. A second dielectric layer is formed on the metal nitride layer. A first CMP process is performed on the second dielectric layer to expose the metal nitride layer by using the metal nitride layer as a stop layer. An etch back process is performed to completely remove the metal nitride layer and expose the first dielectric layer. A second CMP process is performed to expose the second electrode. The manufacturing method can have a better planarization effect.

Owner:UNITED MICROELECTRONICS CORP

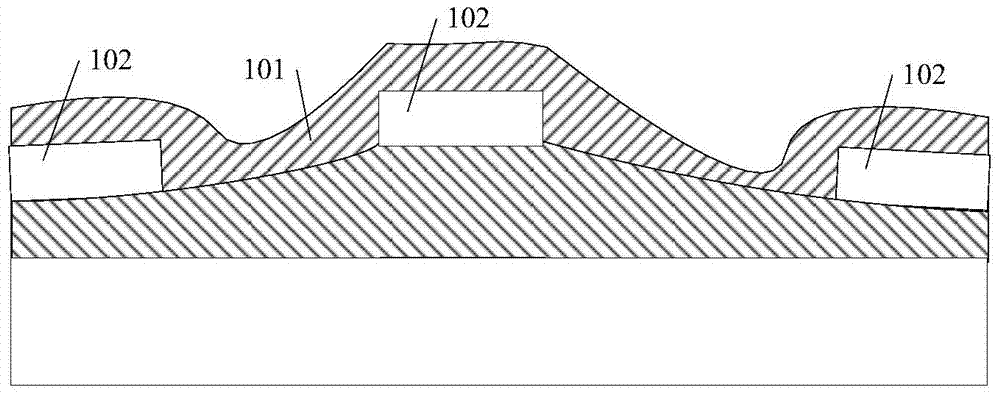

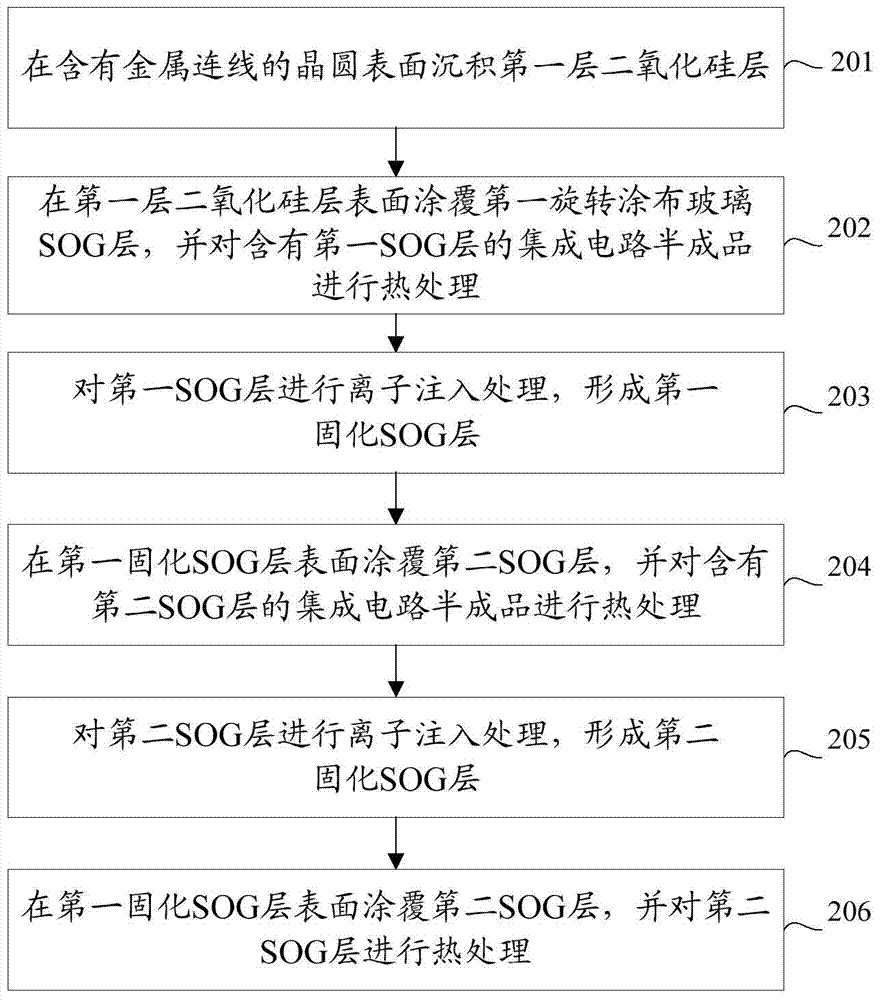

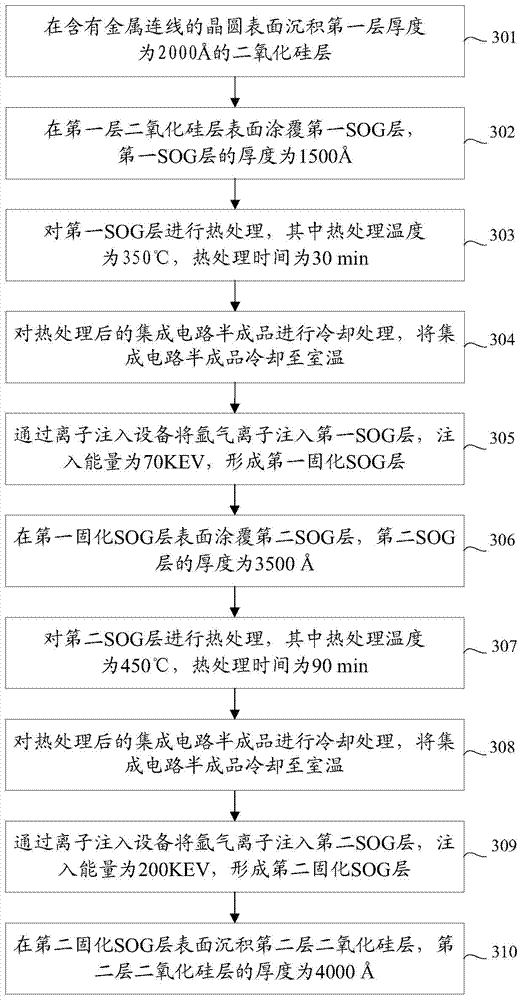

Integrated circuit and metal interlayer dielectric layer planarization method

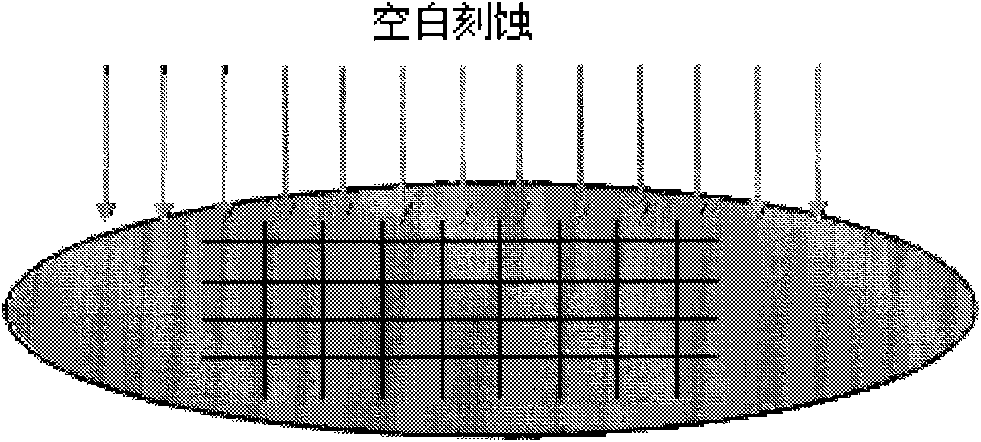

ActiveCN104779196AIncreasing the thicknessImprove planarization effectSemiconductor/solid-state device manufacturingCircuit reliabilitySpins

The embodiment of the invention relates to the field of semiconductor manufacturing, and particularly relates to an integrated circuit and a metal interlayer dielectric layer planarization method for the integrated circuit, so as to solve the problems that surface planarization effects of the metal interlayer dielectric layer are poor and reliability of the integrated circuit is influenced as etch-back is carried out on a spin coating glass layer in the prior art. According to the integrated circuit and the metal interlayer dielectric layer planarization method provided by the embodiment of the invention, as ion curing treatment is carried out on two SOG layers respectively, incomplete thickness curing of the two SOG layers can be avoided, and the integrated circuit can be prevented from having a broken layer; as etch-back treatment does not need to be carried out on the second SOG layer, the problem that the surface planarization degree of the metal interlayer dielectric layer is deteriorated as a result of different etch speeds, surface planarization effects of the metal interlayer dielectric layer are improved, and reliability of the integrated circuit is enhanced.

Owner:FOUNDER MICROELECTRONICS INT

Polyester resin solution for production of thermally cured film

InactiveCN101809060AImprove planarization effectHigh transparencyNon-linear opticsPolyester coatingsProduction lineOrganic group

To provide a material which can be formed into a cured film having high solvent resistance, liquid crystal-aligning properties, high transparency and high planarization, and which can be dissolved in a glycol-type solvent and is therefore applicable in the production line for a planarized film of a color filter when used in the formation of a cured film from the material. Disclosed are: a polyester resin solution for the production of a thermally cured film, which comprises a polyester polymer having a structural unit represented by the formula (1); and a cured film, a liquid crystal alignment layer and a planarized film each of which is produced from the polyester resin solution. (1) wherein A and B independently represent an organic group containing a ring structure.

Owner:NISSAN CHEM IND LTD

Polyester composite for forming thermoset films

ActiveCN102369230AImprove planarization effectHigh transparencyNon-linear opticsHigh resistanceProduction line

Provided is a polyester composite for forming thermoset films, said composite having, after forming a thermoset film, high resistance to solvents and heat, good liquid crystal orientation, high transparency, and high planarizability. Said composite can also, when forming a thermoset film, be dissolved in glycol solvents and lactate ester solvents that can be applied to production lines for planarized color filter films. The composite contains: a component (A) which is a polyester obtained by reacting a tetracarboxylic dianhydride with a diol compound; a component (B) which is an epoxy compound having at least two epoxy groups; and a component (C) which is an amino-group-containing carboxylic compound obtained by reacting a diamine compound with a dicarboxylic anhydride.

Owner:NISSAN CHEM IND LTD

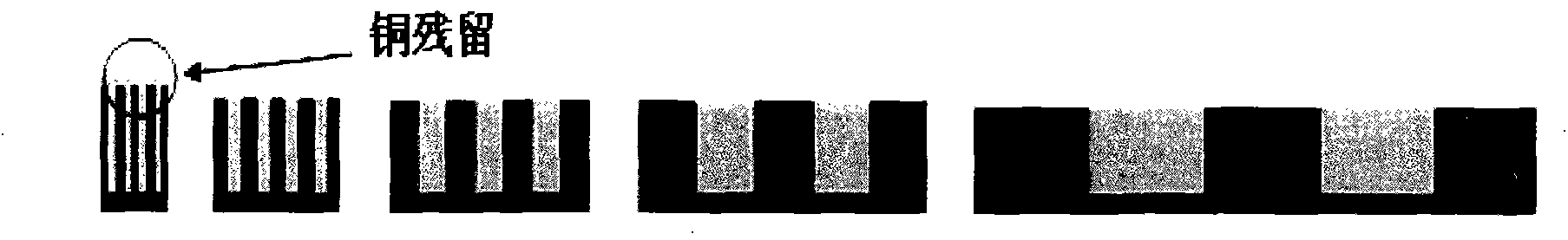

Integrated circuit layout structure and manufacturing method thereof

InactiveCN101447473AUniform growthReduce the burden onSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuit layoutEngineering

The invention relates to an integrated circuit layout structure and a manufacturing method thereof belonging to the technical field of the manufacturing process of an integrated circuit and the layout design. In order to solve the problem in the prior art that after chemical mechanical polishing, copper metal in a thin line area of the integrated circuit layout is left, the invention provides the integrated circuit layout structure and the manufacturing method thereof. By increasing the line space in the thin line area, the growth thickness of the copper in the thin line area is lowered, and copper with different structures grows evenly, thus reducing the load of chemical mechanical polishing, improving planarization capacity, avoiding heat spots in the thin line area and improving yield of products.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

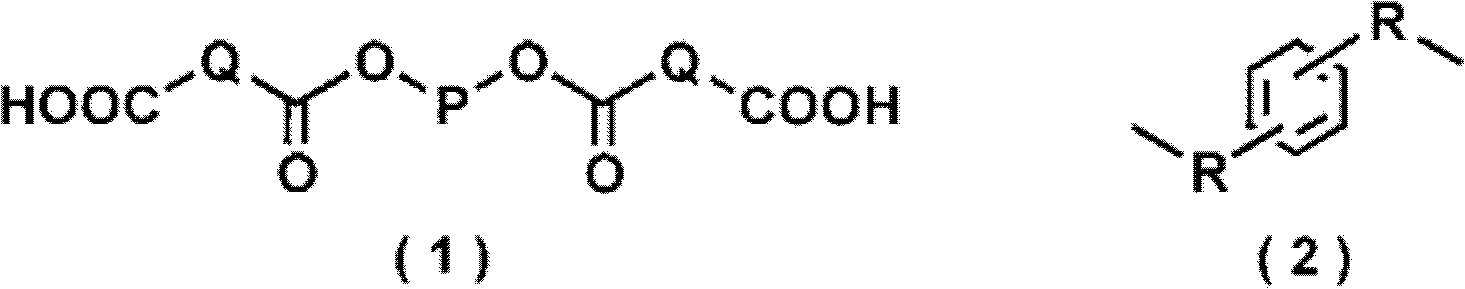

Polyester composition for forming heat-cured film

ActiveCN102361932AImprove planarization effectHigh transparencyNon-linear opticsPolyesterProduction line

A material which forms a cured film that has high solvent resistance, the property of aligning liquid crystals, heat resistance, high transparency, and high planarization characteristics and which, when used in forming a cured film, can be dissolved in various solvents usable in a line for producing, for example, a planarization film for color filters. The material is a polyester composition for forming heat-cured films which comprises a polyester as component (A), a crosslinking agent as component (B), and at least one diester compound represented by formula (1) as component (C). (In formula(1), P represents an alicyclic group, a group composed of an alicyclic group and an aliphatic group, or a structure represented by formula (2), and Q represents an alicyclic group or a group composedof an alicyclic group and an aliphatic group. In formula (2), R represents an alkylene group.)

Owner:NISSAN CHEM IND LTD

Material for forming organic film, method for forming organic film, patterning process, and compound

ActiveUS20210181637A1Good filling effectImprove adhesionOrganic chemistrySemiconductor/solid-state device manufacturingOrganic filmPolymer science

The present invention provides a material for forming an organic film, containing a compound shown by the following general formula (1), and an organic solvent, where X represents an organic group having a valency of n1 and 2 to 50 carbon atoms, n1 represents an integer of 1 to 10, and R1 represents at least one or more of the following general formulae (2) to (4). This aims to provide an organic film material for forming an organic film that has all of high filling property, high planarizing property, and excellent adhesive force to a substrate.

Owner:SHIN ETSU CHEM IND CO LTD

Manufacturing method of interlayer film

ActiveCN108878288BIncrease grinding rateGuaranteed thicknessSemiconductor/solid-state device manufacturingDevice materialMembrane surface

The invention discloses an interlayer film manufacturing method. The interlayer film manufacturing method comprises the following steps: step one, providing a semiconductor substrate on which a pattern structure of a semiconductor device is formed; step two, forming a first insulating layer on the bottom surface and side surfaces of the pattern spacer and the surface of the pattern structure outside the pattern spacer; step three, forming a second insulating layer to completely fill the pattern spacer and extend outside the pattern spacer; and step four: performing chemical mechanical polishing on the second insulating layer and the first insulating layer with the pattern structure as a stop layer, and forming the interlayer film formed by stacking the first and second insulating layers filled in the pattern spacer. The interlayer film manufacturing method can reduce or eliminate dishing defects on the interlayer film surface at the top of the pattern spacer, can improve the flatness of the entire interlayer film, and can improve the electrical properties of semiconductor devices.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

Integrated circuit layout structure and manufacturing method thereof

InactiveCN101447473BUniform growthReduce the burden onSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuit layoutThin line

The invention relates to an integrated circuit layout structure and a manufacturing method thereof belonging to the technical field of the manufacturing process of an integrated circuit and the layout design. In order to solve the problem in the prior art that after chemical mechanical polishing, copper metal in a thin line area of the integrated circuit layout is left, the invention provides theintegrated circuit layout structure and the manufacturing method thereof. By increasing the line space in the thin line area, the growth thickness of the copper in the thin line area is lowered, and copper with different structures grows evenly, thus reducing the load of chemical mechanical polishing, improving planarization capacity, avoiding heat spots in the thin line area and improving yield of products.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Photosensitive polyester composition for use in forming thermally cured film

Disclosed is a material which enables pattern formation in an alkaline developer, and shows high solvent resistance, liquid crystal orientation, heat resistance, high transparency, and high planarity after being formed into a cured film, and can be dissolved in a glycol solvent which can be applied to the production line of a planarized film of a color filter while being formed into a cured film. Specifically disclosed is a photosensitive polyester composition for use in forming thermally cured film, containing component (A), component (B), component (C), and component (D): component (A): a modified polyester obtained by reacting a compound having a functional group selected from a glycidyl group and an isocyanate group with a polyester containing a structural unit represented by formula (1); component (B): an epoxy compound having two or more epoxy groups; component (C): an amino group-containing carboxylic acid compound obtained by reacting a diamine compound with dicarboxylic acid dianhydride; and component (D): 1,2-quinone diazide compound. In formula (1), A and B each independently represent an organic group containing a cyclic structure.

Owner:NISSAN CHEM IND LTD

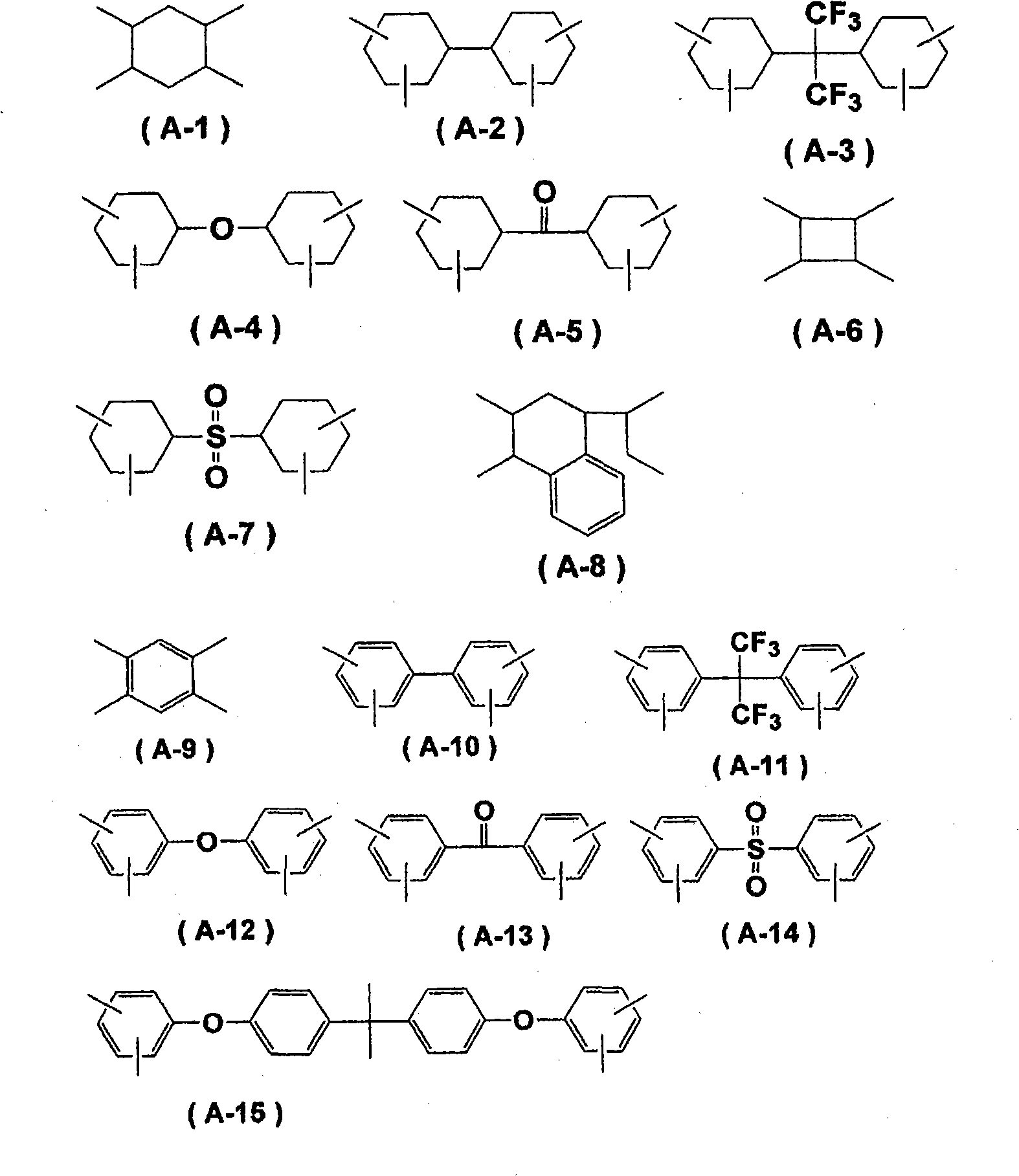

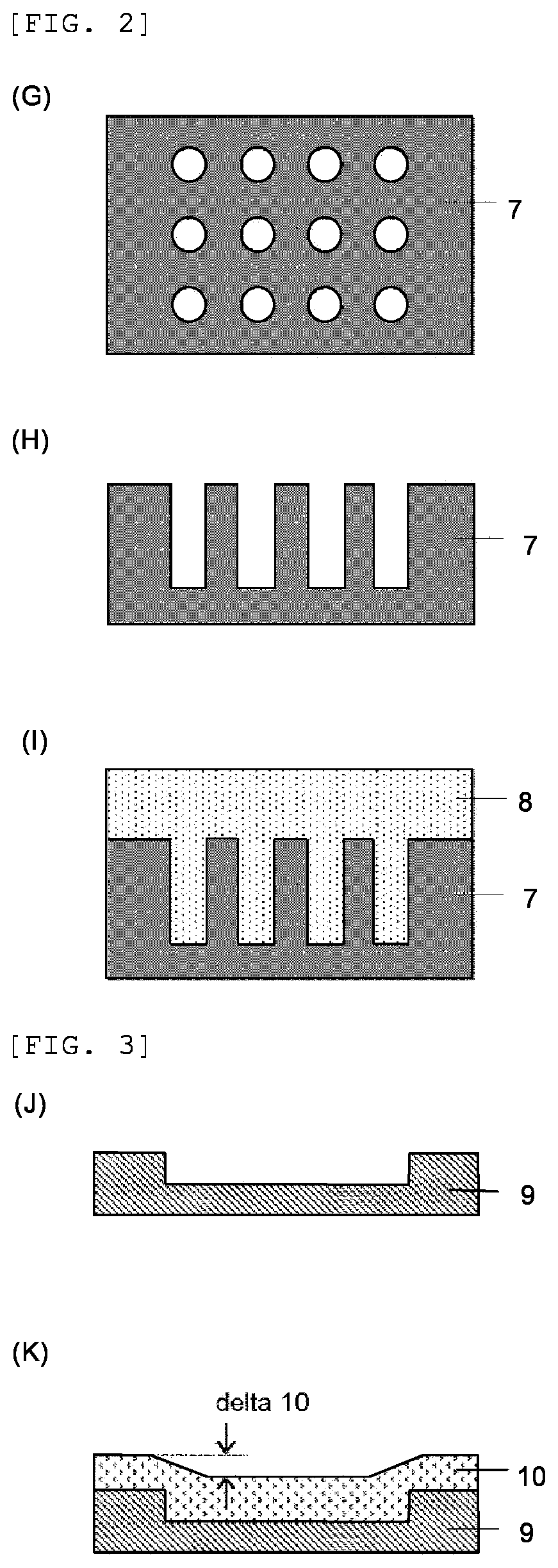

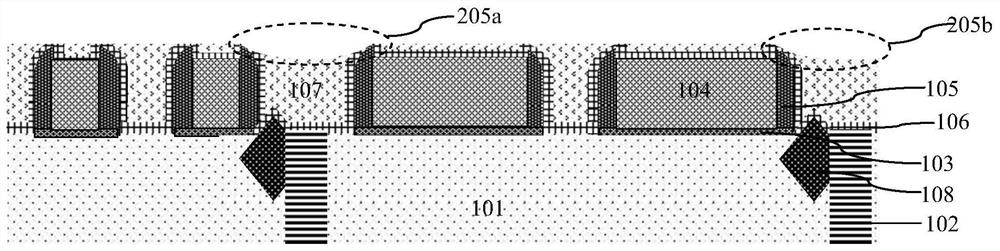

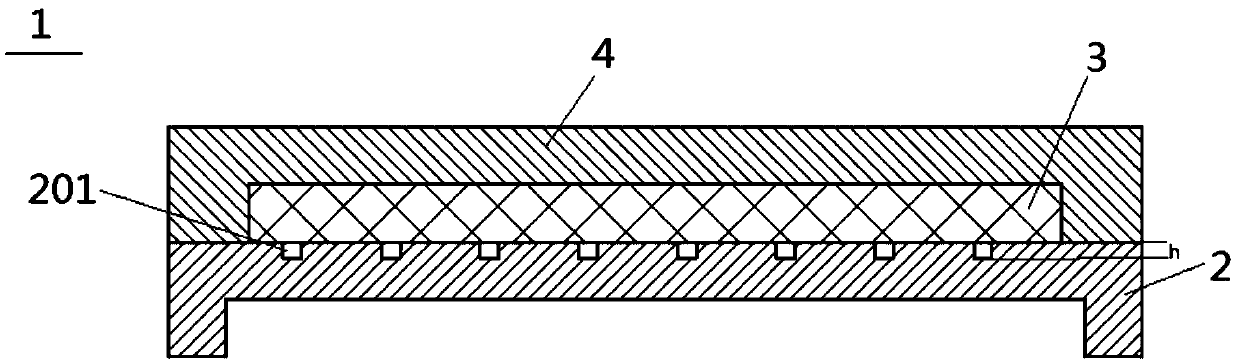

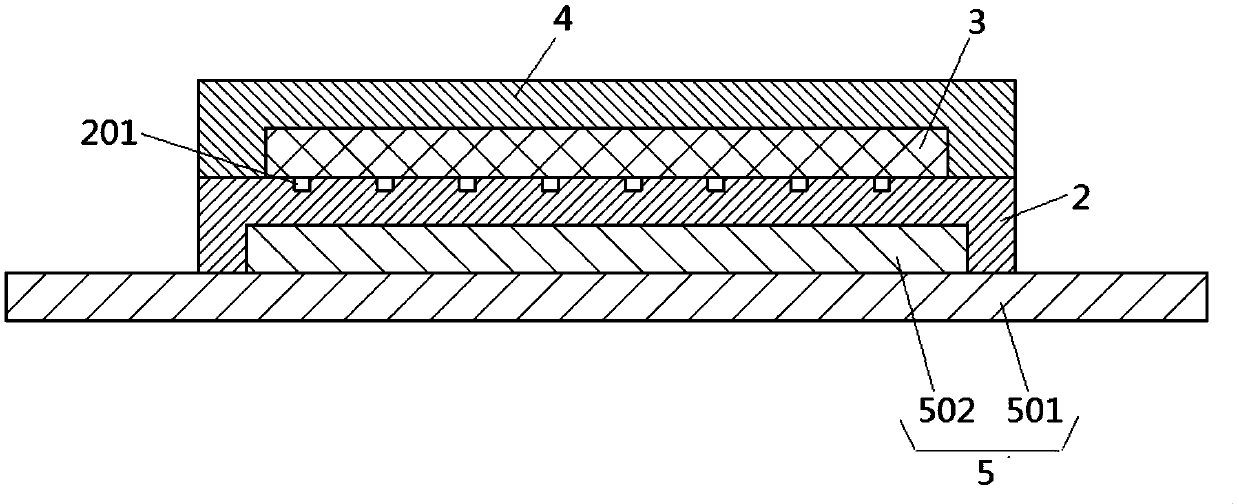

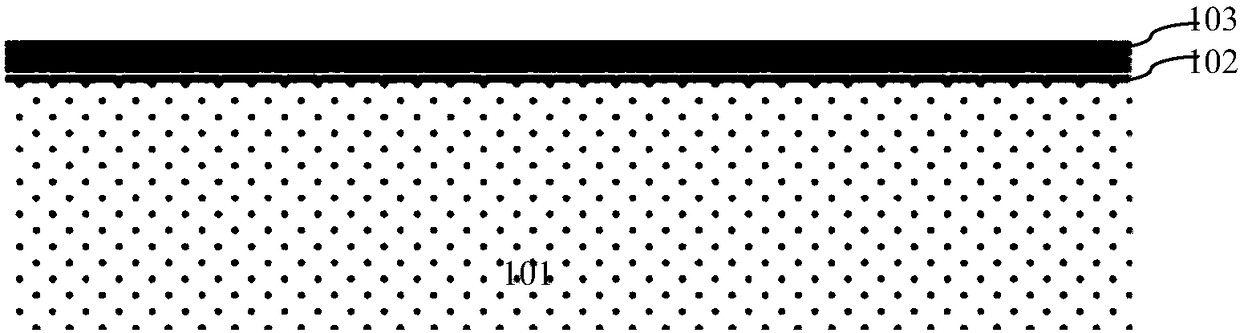

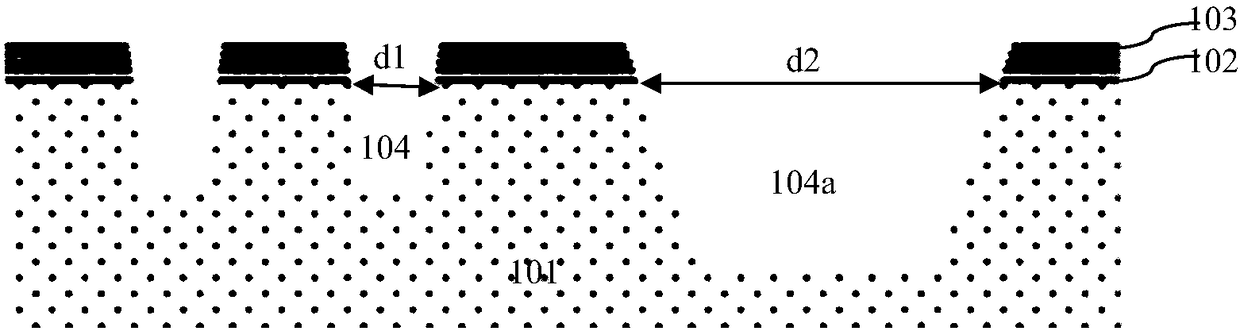

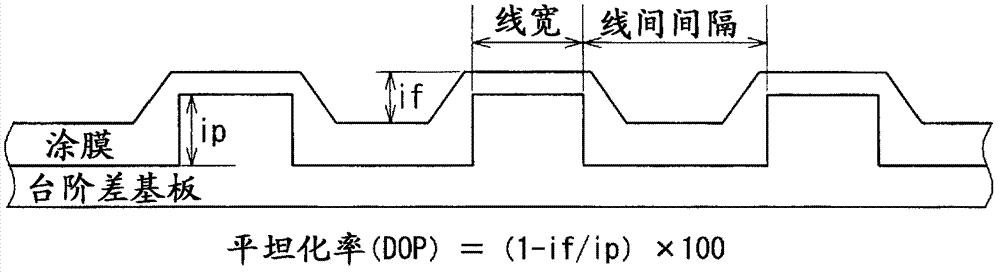

Thin film packaging structure, thin film packaging method and concave hole design method

InactiveCN111211238ALower contact angleImprove wettabilitySolid-state devicesSemiconductor/solid-state device manufacturingThin membraneComposite material

The invention relates to a thin film packaging structure, a thin film packaging method and a concave hole design method. The thin film packaging structure comprises a first inorganic packaging layer,an organic packaging layer, and a second inorganic packaging layer; the first inorganic packaging layer is disposed at the lower end of the thin film packaging structure; the upper surface of the first inorganic packaging layer is provided with a plurality of concave holes; the organic packaging layer is arranged on the first inorganic packaging layer; the organic packaging layer is made of organic ink; and the organic packaging layer is formed by coating the organic ink on the first inorganic packaging layer, making the organic ink stand still and flattening the organic ink; and the second inorganic encapsulation layer is disposed on the organic encapsulation layer. According to the thin film packaging structure of the invention, the first inorganic packaging layer is formed, the plurality of concave holes are formed in the first inorganic packaging layer; the plurality of concave holes are designed; the contact angle between the organic ink and the first inorganic packaging layer isreduced by changing the hole diameter of each concave hole and the hole distance between two adjacent concave holes, and therefore, the wettability of the organic ink is improved, and the planarization effect of the organic ink is improved.

Owner:INCOFLEX SEMICON TECH CO LTD

Polyester composite for forming thermoset films

ActiveCN102369231BImprove planarization effectHigh transparencyNon-linear opticsOperating systemPolyester composite

A multi-core processor system includes a given configured to queue an interrupt process of a software interrupt request to the given core, and execute queued processes in the order of queuing at the given core; execute preferentially an interrupt process of a hardware interrupt request to the given core over a process under execution at the given core; determine whether the software interrupt request is a specific software interrupt request; and perform control to preferentially execute the interrupt process without queuing, upon determining that the software interrupt request is the specific software interrupt request.

Owner:NISSAN CHEM IND LTD

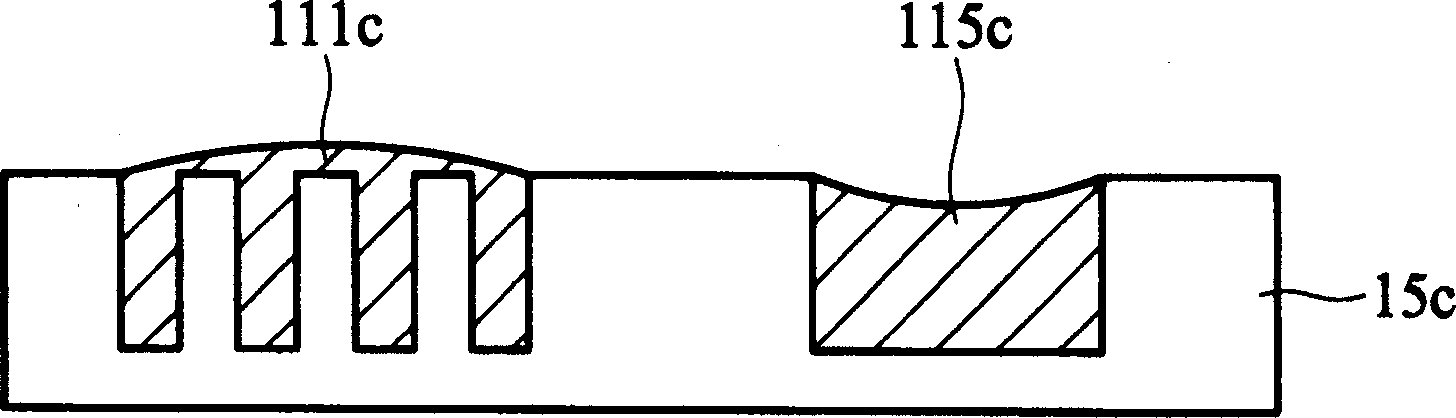

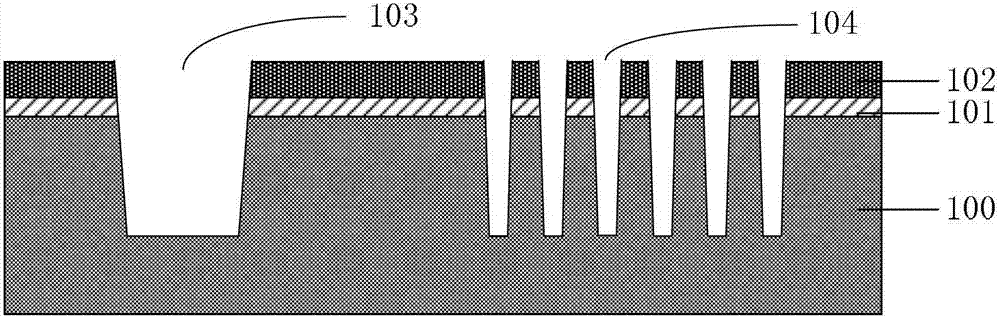

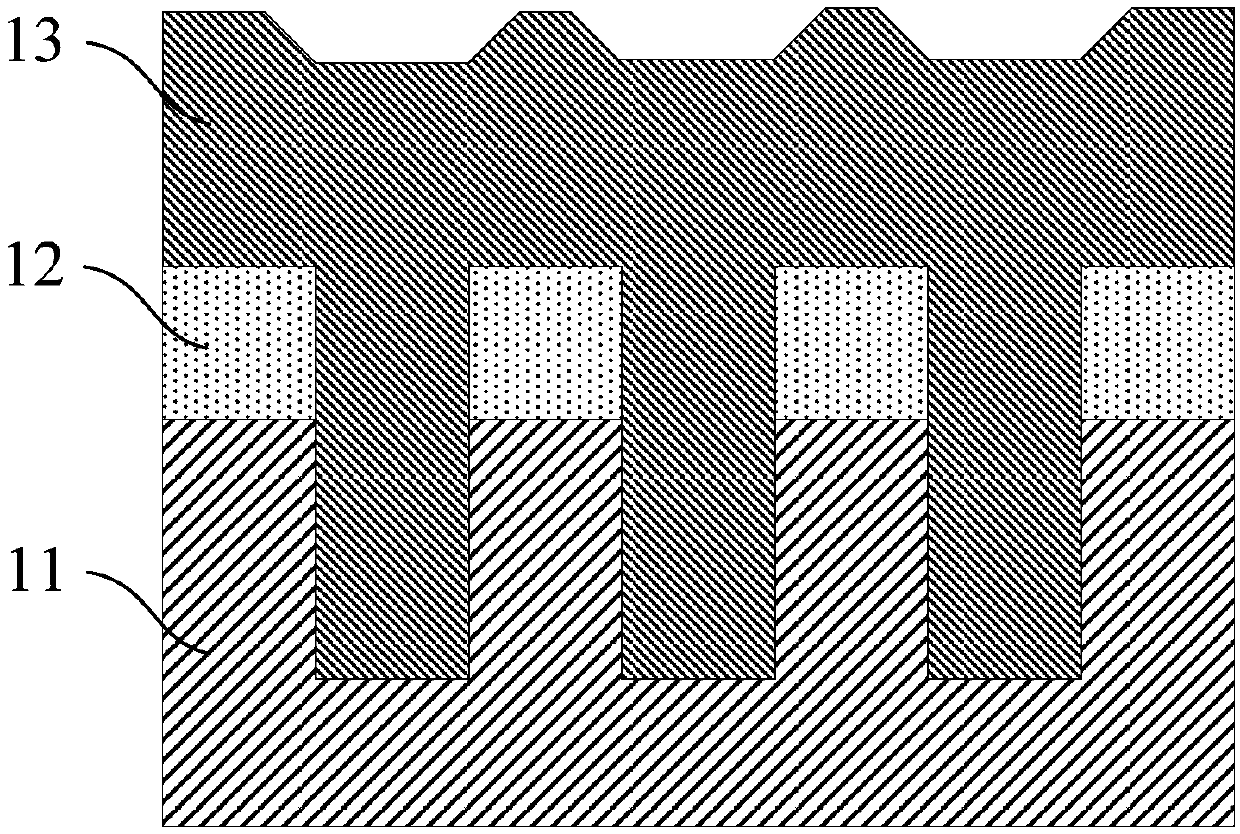

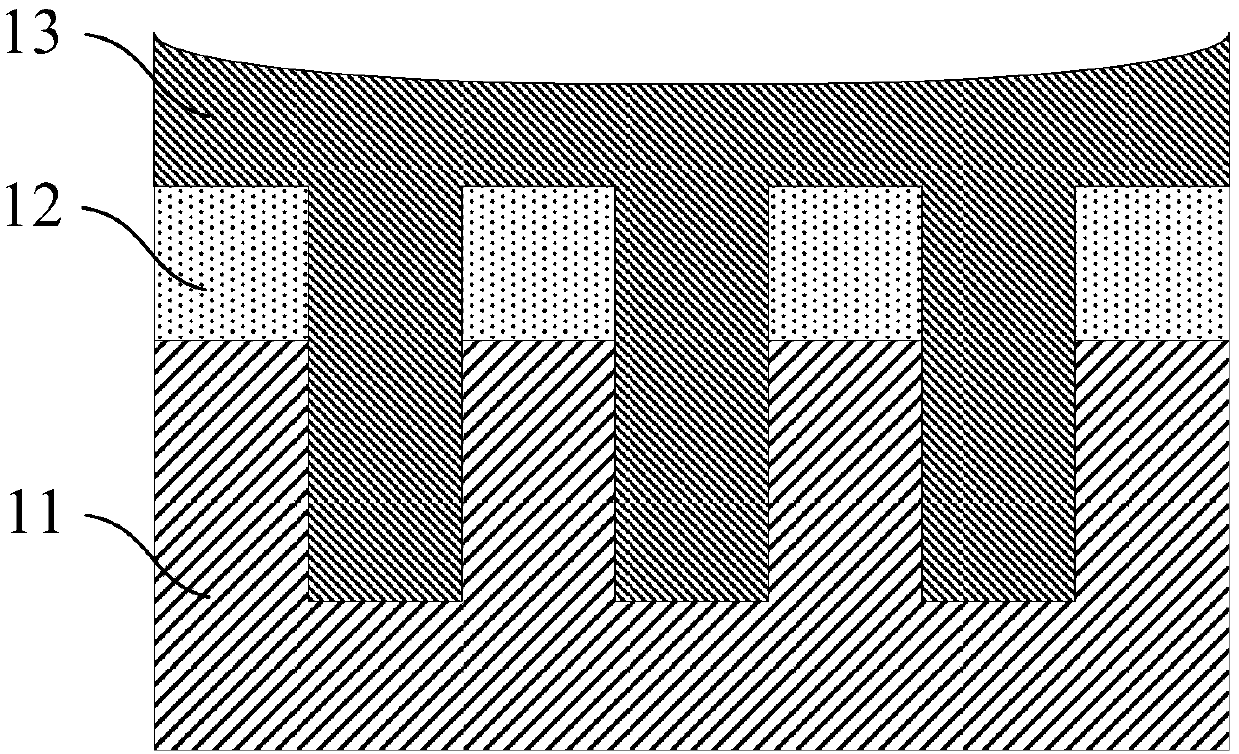

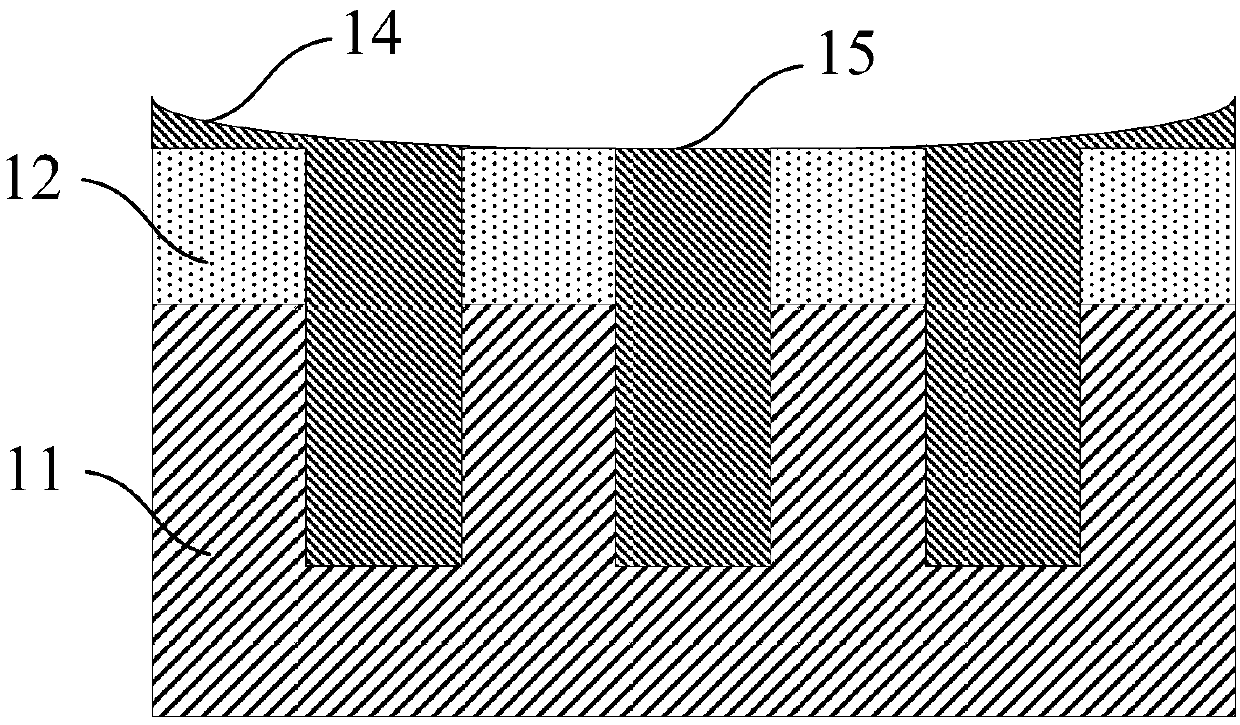

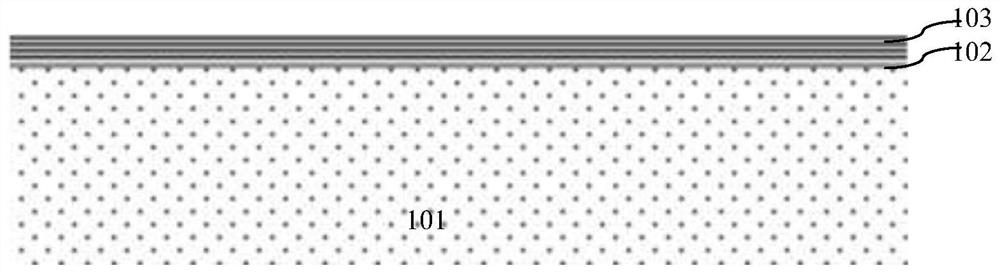

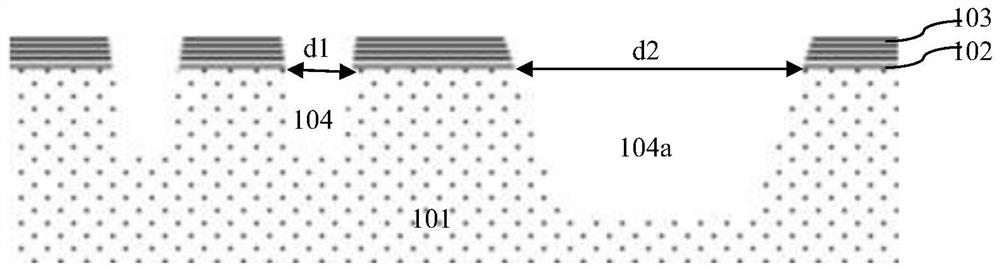

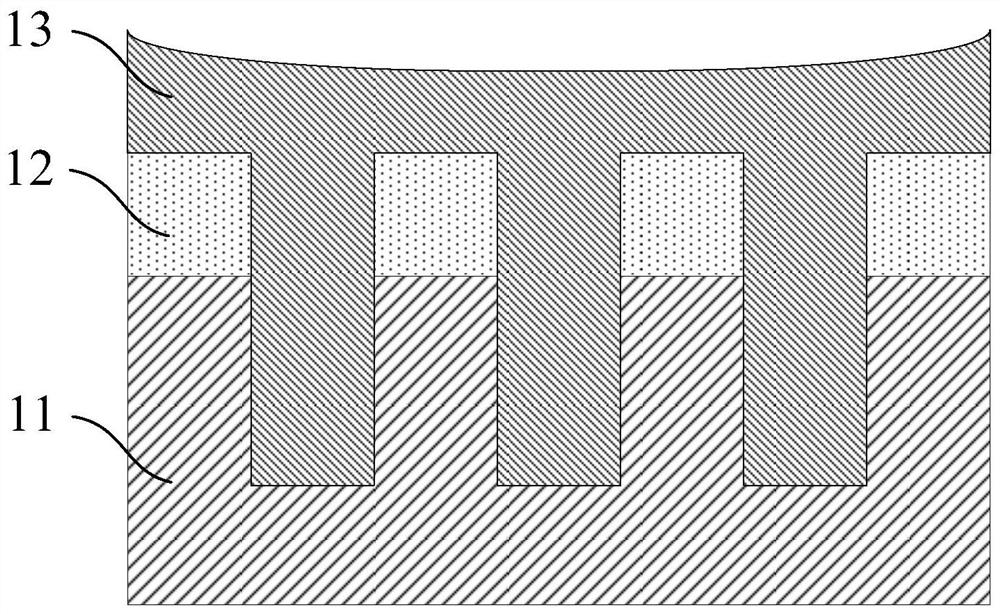

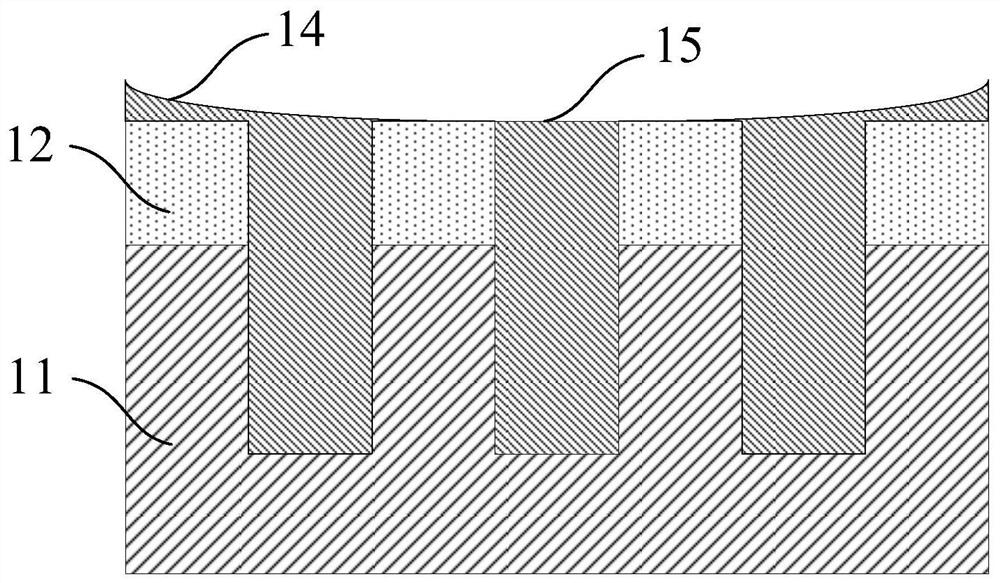

Manufacturing method of shallow trench insulation structure

ActiveCN108520863AFast CMP rateCMP rate increaseSemiconductor/solid-state device manufacturingCompound (substance)Engineering

The invention discloses a manufacturing method of a shallow trench insulation structure. The manufacturing method comprises the following steps: step 1, forming a hard mask layer on a semiconductor substrate and forming a shallow trench; step 2, forming a first insulating layer on the bottom surface and the side surface of a shallow trench and the surface of the hard mask layer outside the shallowtrench; step 3, forming a second insulating layer to completely fill the shallow trench and extend out of the shallow trench; step 4, performing chemical mechanical grinding on the second insulatinglayer and the first insulating layer by using the hard mask layer as a stop layer, and forming a shallow trench insulation structure formed by superposing the first insulating layer and the second insulating layer which are filled in the shallow trench. According to the invention, the flattening effect of the whole substrate surface can be improved, the disc-shaped defects at the top of the shallow trench insulation structure can be reduced or eliminated, and the CMP efficiency can be improved.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

Manufacturing method of shallow trench isolation structure

ActiveCN108520863BFast CMP rateCMP rate increaseSemiconductor/solid-state device manufacturingEngineeringSemiconductor

The invention discloses a manufacturing method of a shallow trench insulation structure. The manufacturing method comprises the following steps: step 1, forming a hard mask layer on a semiconductor substrate and forming a shallow trench; step 2, forming a first insulating layer on the bottom surface and the side surface of a shallow trench and the surface of the hard mask layer outside the shallowtrench; step 3, forming a second insulating layer to completely fill the shallow trench and extend out of the shallow trench; step 4, performing chemical mechanical grinding on the second insulatinglayer and the first insulating layer by using the hard mask layer as a stop layer, and forming a shallow trench insulation structure formed by superposing the first insulating layer and the second insulating layer which are filled in the shallow trench. According to the invention, the flattening effect of the whole substrate surface can be improved, the disc-shaped defects at the top of the shallow trench insulation structure can be reduced or eliminated, and the CMP efficiency can be improved.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

Photosensitive polyester composition for use in forming thermally cured film

Disclosed is a material which enables pattern formation in an alkaline developer, and shows high solvent resistance, liquid crystal orientation, heat resistance, high transparency, and high planarity after being formed into a cured film, and can be dissolved in a glycol solvent which can be applied to the production line of a planarized film of a color filter while being formed into a cured film. Specifically disclosed is a photosensitive polyester composition for use in forming thermally cured film, containing component (A), component (B), component (C), and component (D): component (A): a modified polyester obtained by reacting a compound having a functional group selected from a glycidyl group and an isocyanate group with a polyester containing a structural unit represented by formula (1); component (B): an epoxy compound having two or more epoxy groups; component (C): an amino group-containing carboxylic acid compound obtained by reacting a diamine compound with dicarboxylic acid dianhydride; and component (D): 1,2-quinone diazide compound. In formula (1), A and B each independently represent an organic group containing a cyclic structure.

Owner:NISSAN CHEM IND LTD

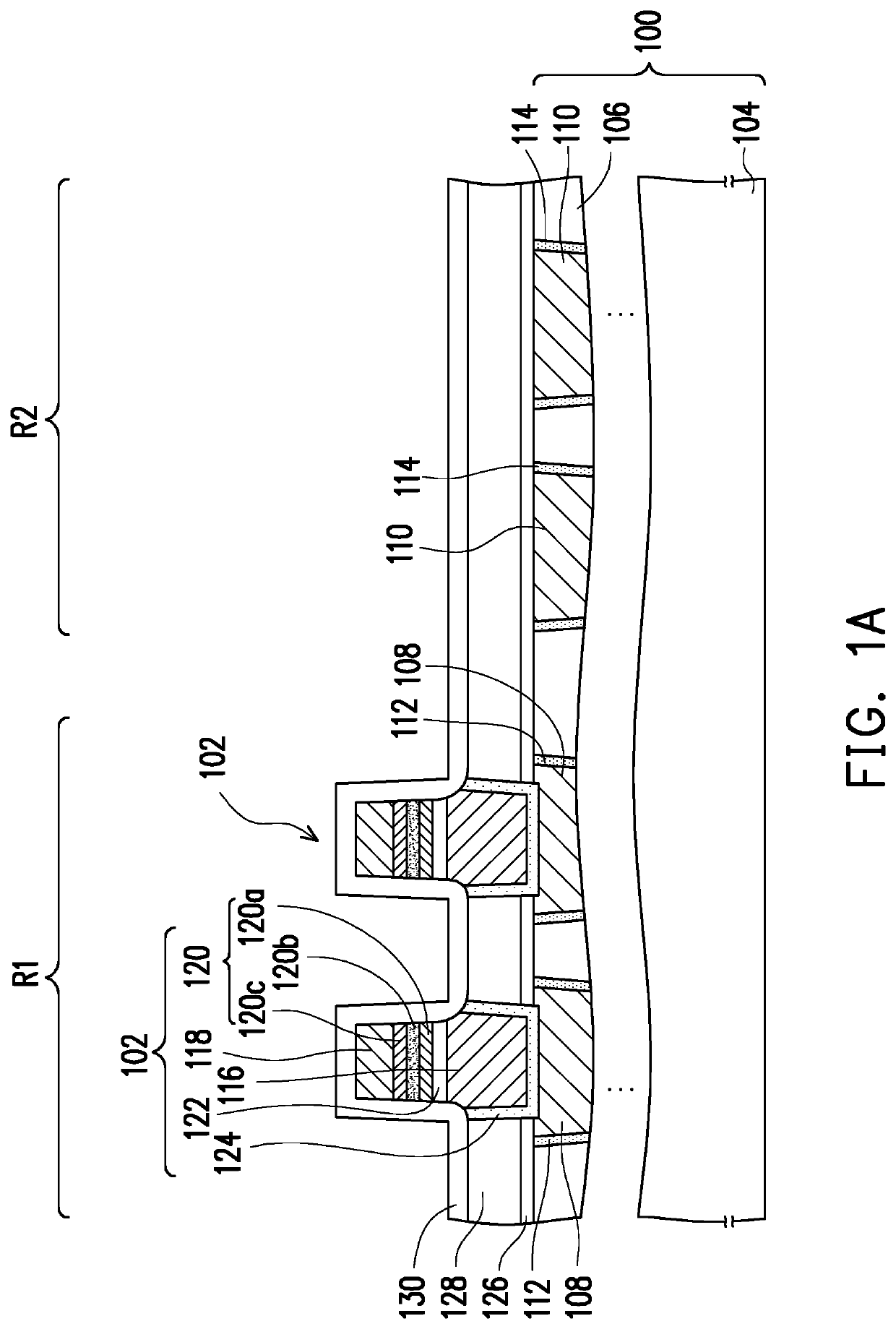

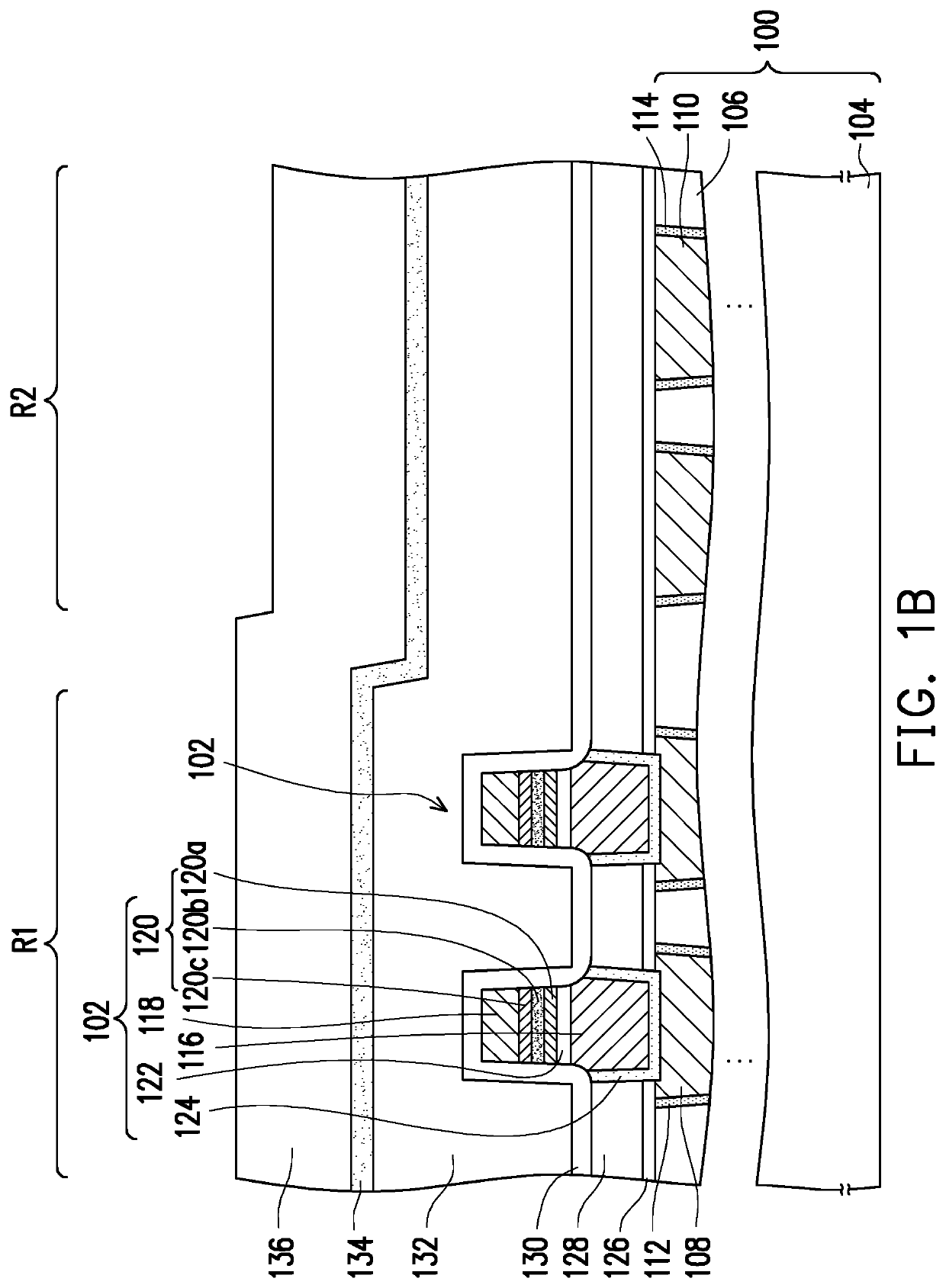

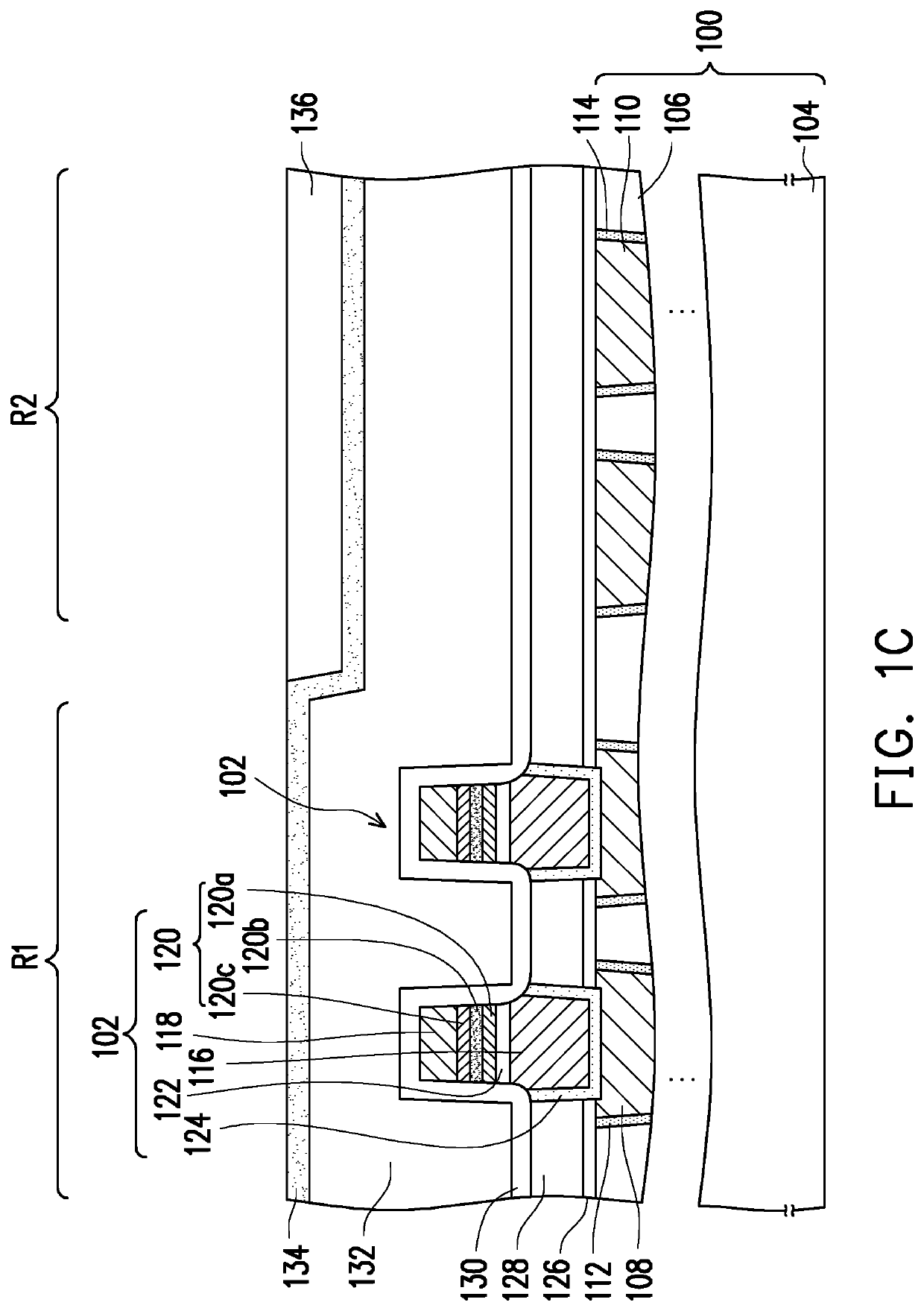

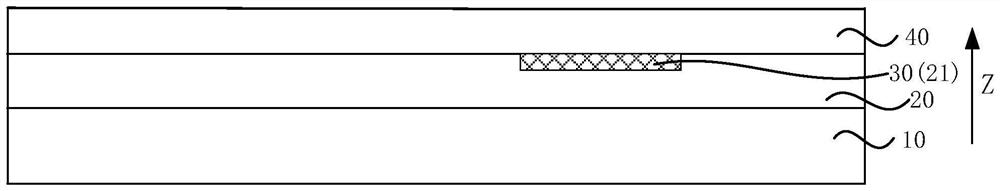

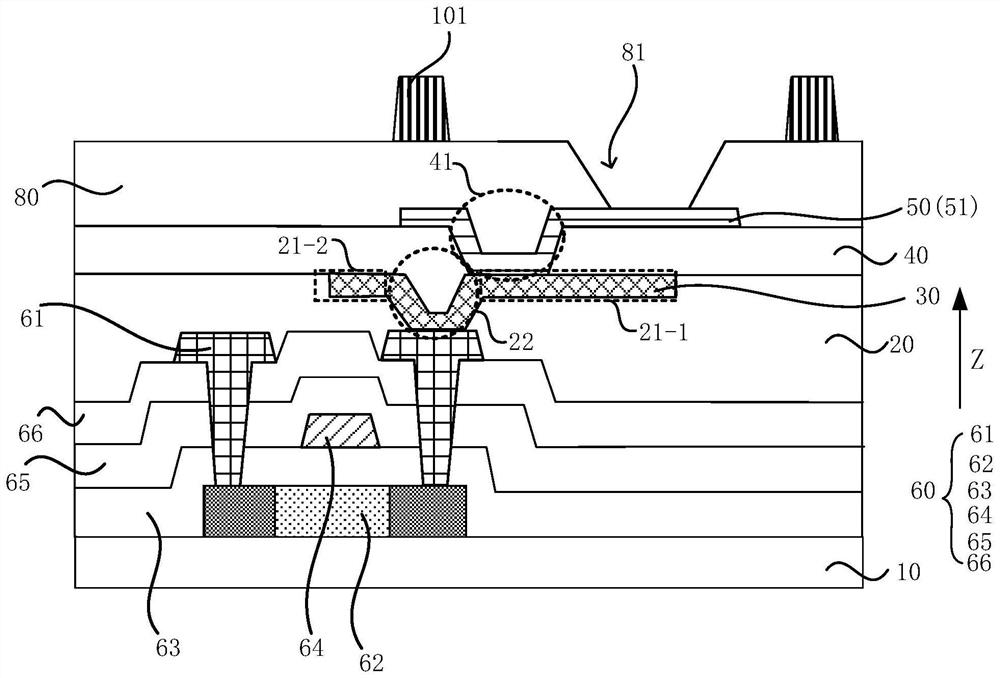

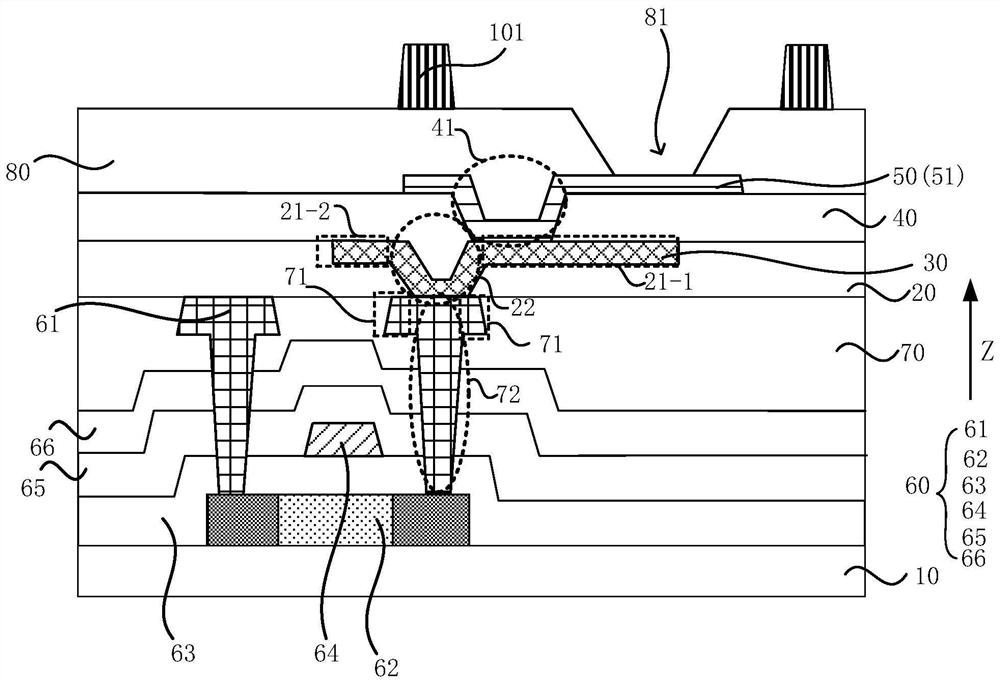

Array substrate, manufacturing method thereof and display panel

PendingCN113871399AReduce thicknessImprove planarization effectSolid-state devicesSemiconductor/solid-state device manufacturingMaterials scienceAtomic physics

Owner:HEFEI VISIONOX TECH CO LTD

Semiconductor structure and forming method thereof

ActiveCN108878419AImprove top flatnessImprove the problem of dishing at the topTransistorSolid-state devicesHigh resistanceSemiconductor structure

Disclosed are a semiconductor structure and a forming method thereof. The forming method comprises the following steps that a substrate is provided, wherein the substrate comprises a high-resistance device area, and the high-resistance device area is composed of a device area and an edge area; separated virtual pseudo gates are formed on the substrate of the device area and the edge area; and an interlayer dielectric film is formed on the substrate exposed out of the virtual pseudo gates, wherein the interlayer dielectric film covers the tops of the virtual pseudo gates; the interlayer dielectric film is subjected to planarization treatment, so that the residual interlayer dielectric film exposes the tops of the virtual pseudo gates, and the residual interlayer dielectric film serves as aninterlayer dielectric layer. Compared with the scheme that the virtual pseudo gate is not formed, the method has the advantage that in the planarization process in the subsequent formation of the interlayer dielectric layer, the top flatness of the interlayer dielectric layer can be improved, and the problem of top dishing of the interlayer dielectric layer can be improved, so that the performance of the semiconductor structure can be improved.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

Polyester composition for production of thermally cured film

ActiveCN101809057BCapable of aligning liquid crystalsImprove planarization effectEpoxy resin coatingsNon-linear opticsProduction linePolyester

To provide a material which can be formed into a cured film having high solvent resistance, liquid crystal-aligning properties, heat resistance, high transparency and high planarization, and which can be dissolved in a glycol-type solvent and a lactic acid ester-type solvent (which are solvents applicable in the production line for a planarized film of a color filter) in the formation of a cured film from the material. Disclosed is a polyester composition for the production of a thermally cured film, which comprises the following components (A) and (B): (A) a polyester having a constituent unit represented by the formula (1); and (B) an epoxy compound having two or more epoxy groups. (1) wherein A and B independently represent an organic group containing a ring structure.

Owner:NISSAN CHEM CORP

Polyester composition for forming heat-cured film

ActiveCN102361932BImprove planarization effectHigh transparencyNon-linear opticsPolyesterPolymer science

A material which forms a cured film that has high solvent resistance, the property of aligning liquid crystals, heat resistance, high transparency, and high planarization characteristics and which, when used in forming a cured film, can be dissolved in various solvents usable in a line for producing, for example, a planarization film for color filters. The material is a polyester composition for forming heat-cured films which comprises a polyester as component (A), a crosslinking agent as component (B), and at least one diester compound represented by formula (1) as component (C). (In formula (1), P represents an alicyclic group, a group composed of an alicyclic group and an aliphatic group, or a structure represented by formula (2), and Q represents an alicyclic group or a group composed of an alicyclic group and an aliphatic group. In formula (2), R represents an alkylene group.)

Owner:NISSAN CHEM IND LTD

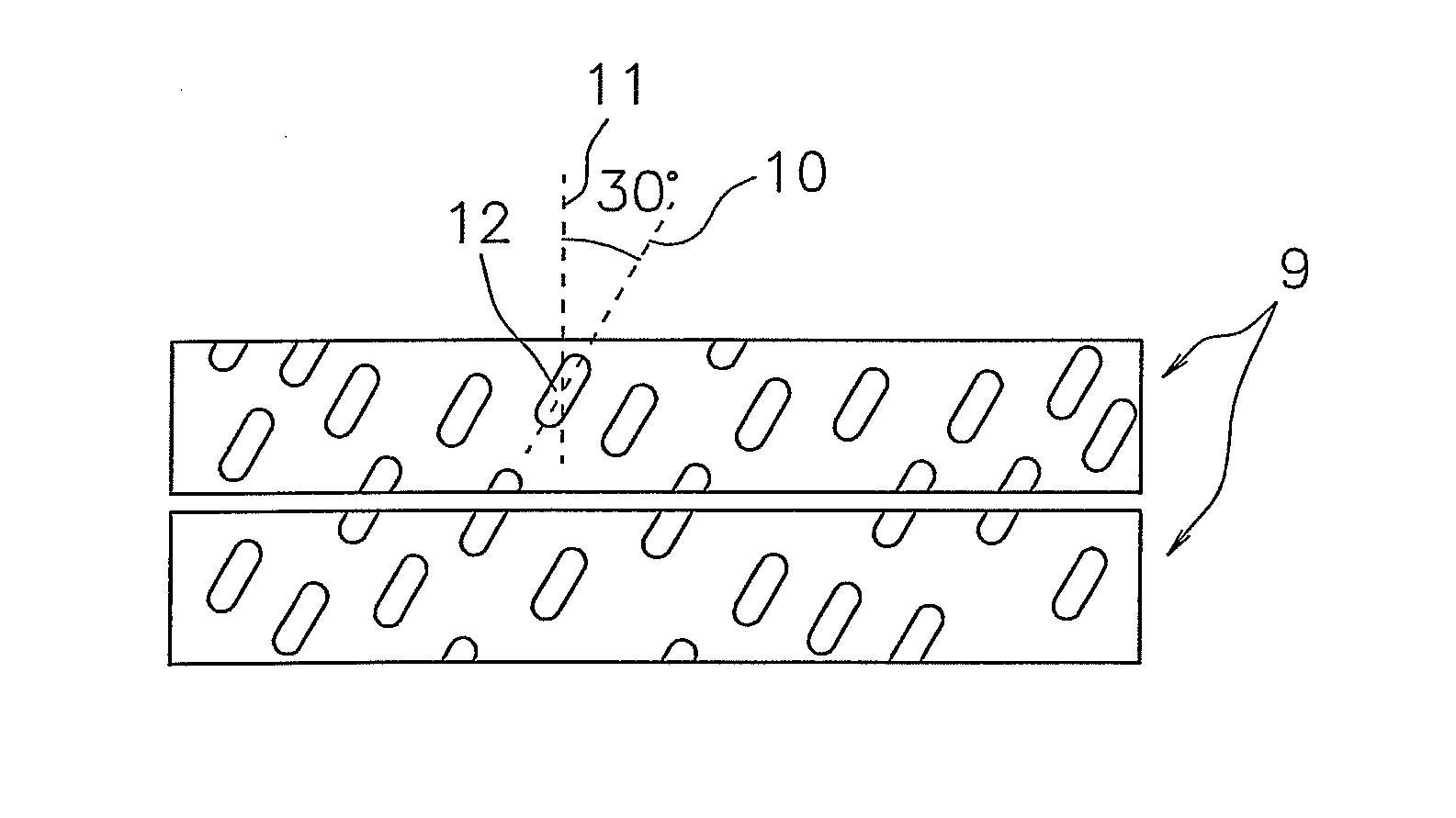

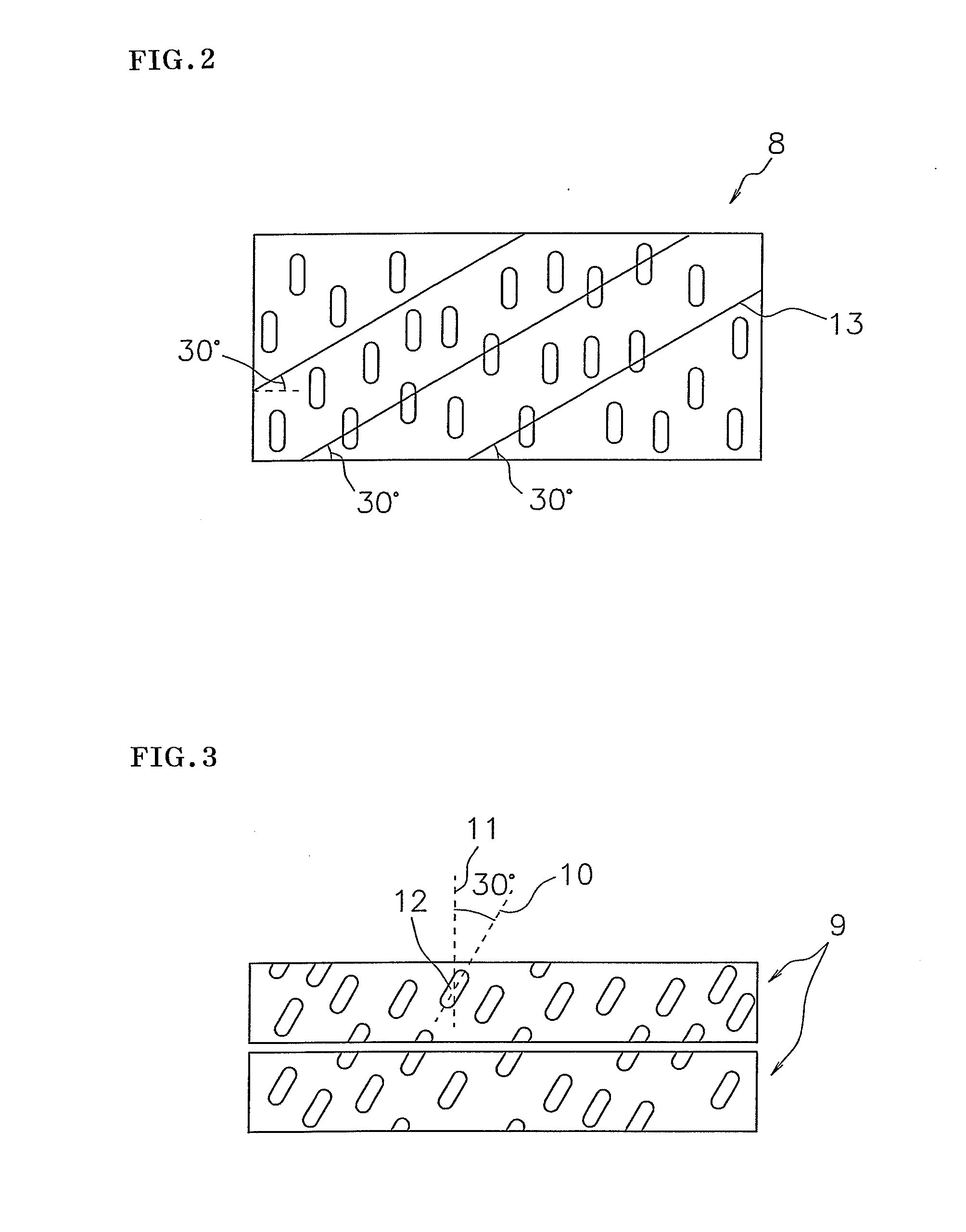

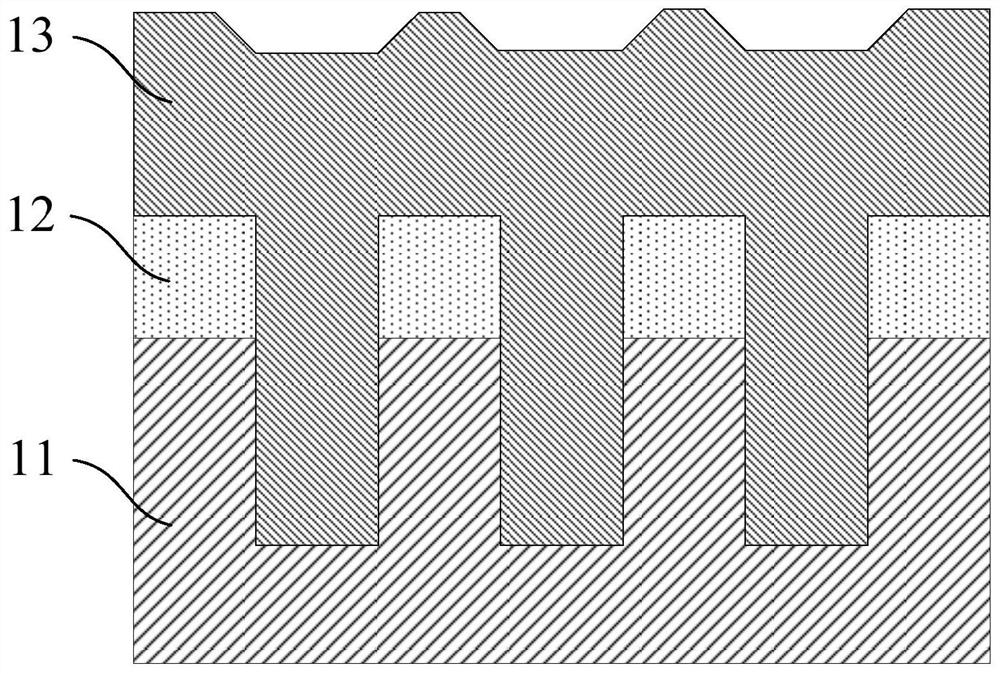

Polishing pad

ActiveUS9314898B2InhibitionImprove planarization effectAbrasion apparatusSemiconductor/solid-state device manufacturingLong axisEngineering

An object of the present invention is to provide a polishing pad having high planarization property and capable of making it possible to suppress the occurrence of scratches. A polishing pad of the present invention has a polishing layer having oval cells each with a long axis inclined by 5° to 45° with respect to the direction of the thickness of the polishing layer.

Owner:ROHM & HAAS ELECTRONICS MATERIALS CMP HLDG INC

Preparation method of shallow trench isolation structure, chemical mechanical polishing method and system

ActiveCN110071041BEliminate residueImprove yield rateSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingMechanical millingPolishing

The present invention provides a method for preparing a shallow trench isolation structure, a chemical mechanical polishing method and a system, including the following steps: 1) measuring the previous thickness of the target material layer, according to the previous thickness of the target material layer and the first stage The thickness of the target material layer retained after chemical mechanical polishing determines the first target removal thickness; 2) The theoretical grinding rate is determined according to the actual use time of the grinding consumables; 3) The grinding parameters are dynamically corrected according to the first target removal thickness and the theoretical grinding rate. The grinding parameters perform the first-stage chemical mechanical grinding on the target material layer; 4) perform the second-stage chemical mechanical grinding on the target material layer to achieve the removal of the second target removal thickness. The invention determines the grinding parameters by collecting the target removal thickness of the target material layer and combining the actual use time of the grinding consumables, thereby improving the flattening effect of grinding, eliminating the residue of the target material layer after chemical mechanical grinding, and improving the yield.

Owner:CHANGXIN MEMORY TECH INC