Integrated circuit and metal interlayer dielectric layer planarization method

A technology of integrated circuits and metal layers, applied in the manufacture of circuits, electrical components, semiconductor/solid-state devices, etc., can solve the problems of poor surface planarization effect and affect the reliability of integrated circuits, and achieve the effect of improving the effect of planarization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

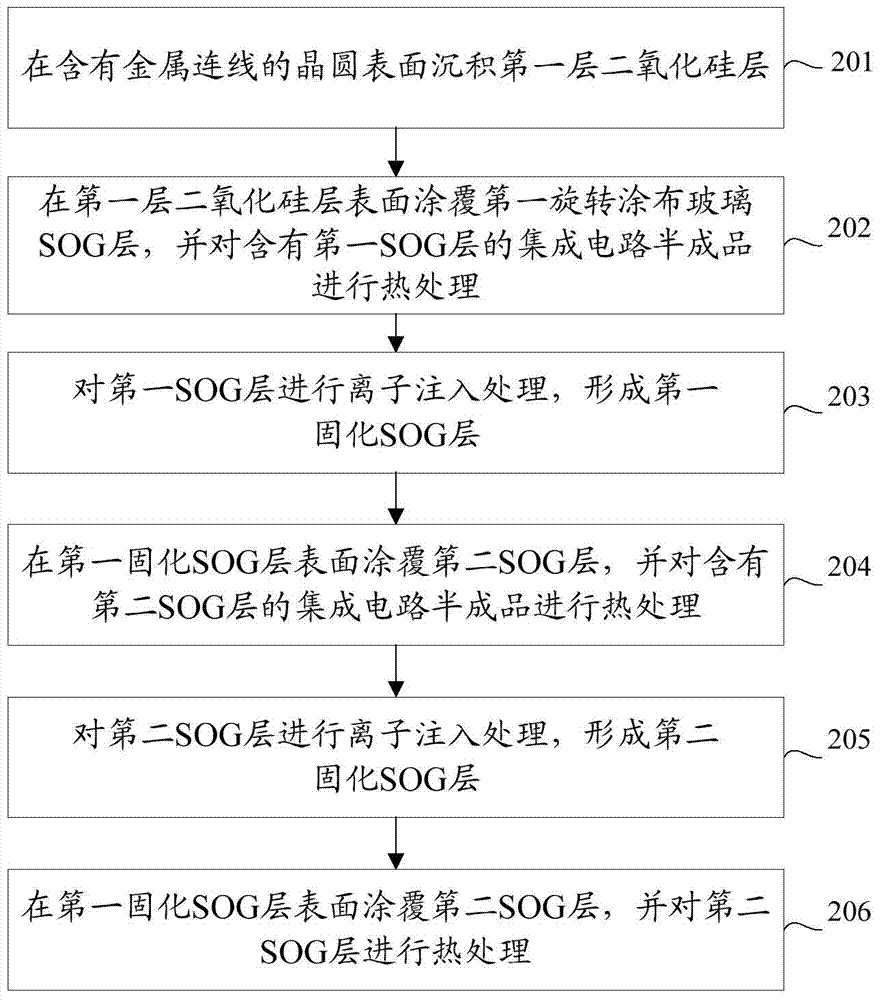

[0056] Such as image 3 As shown, it is Embodiment 1 of the method for planarizing the inter-metal dielectric layer of the integrated circuit in the embodiment of the present invention, and the method includes:

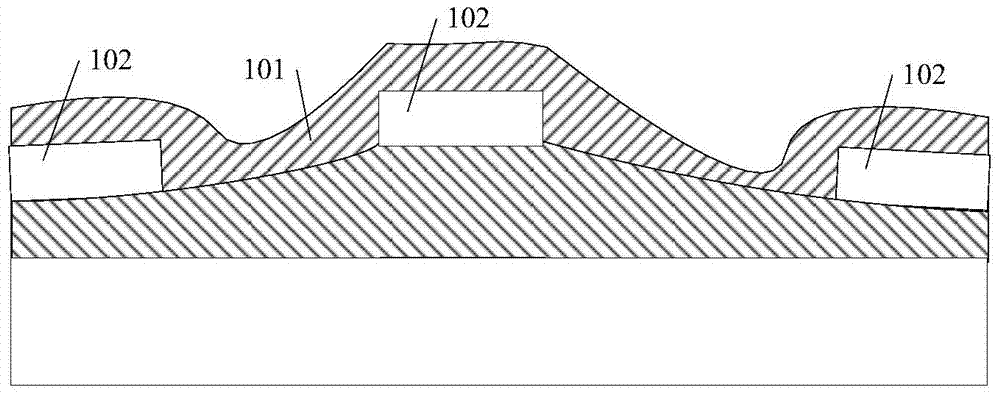

[0057] Step 301: Depositing a first layer with a thickness of The silicon dioxide layer; such as Figure 4 The schematic diagram of the structure after the first layer of silicon dioxide layer is deposited on the surface of the wafer in the embodiment of the present invention is shown, wherein 401 is the first layer of silicon dioxide layer, and 402 is a metal connection;

[0058] Step 302: Coating a first SOG layer on the surface of the first silicon dioxide layer, the thickness of the first SOG layer is

[0059] Step 303: performing heat treatment on the first SOG layer, wherein the heat treatment temperature is 350° C., and the heat treatment time is 30 minutes;

[0060] Step 304: cooling the semi-finished integrated circuit after heat treatment, and cooling ...

Embodiment 2

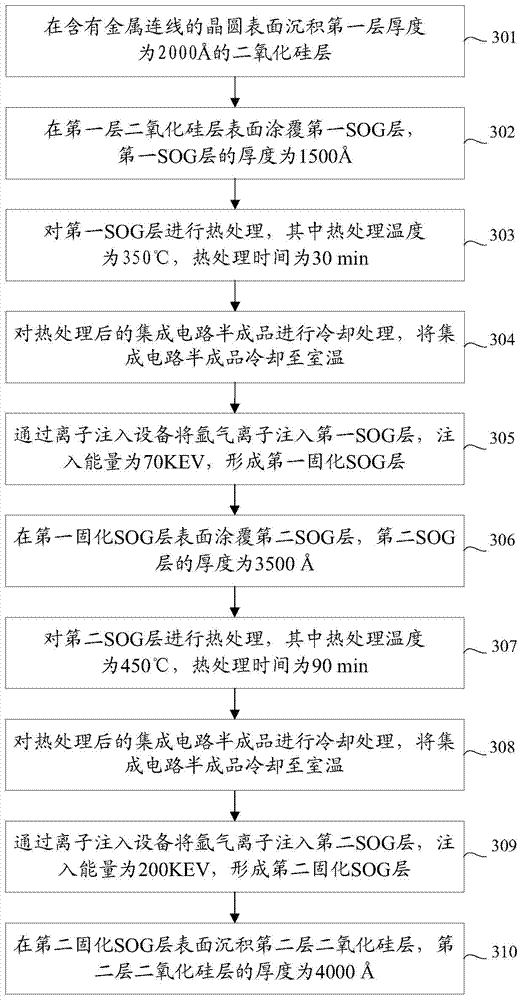

[0067] Such as Figure 8 As shown, it is the second embodiment of the method for planarizing the inter-metal dielectric layer of the integrated circuit in the embodiment of the present invention. The method includes:

[0068] Step 801: Depositing a first layer with a thickness of the silicon dioxide layer;

[0069] Step 802: Coating a first SOG layer on the surface of the first silicon dioxide layer, the thickness of the first SOG layer is

[0070] Step 803: performing heat treatment on the first SOG layer, wherein the heat treatment temperature is 375° C., and the heat treatment time is 45 minutes;

[0071] Step 804: cooling the semi-finished integrated circuit after heat treatment, cooling the semi-finished integrated circuit to room temperature;

[0072] Step 805: Implanting argon ions into the first SOG layer through ion implantation equipment with an implantation energy of 120KEV to form a first cured SOG layer;

[0073] Step 806: Coating a second SOG layer on the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More