Integrated circuit layout structure and manufacturing method thereof

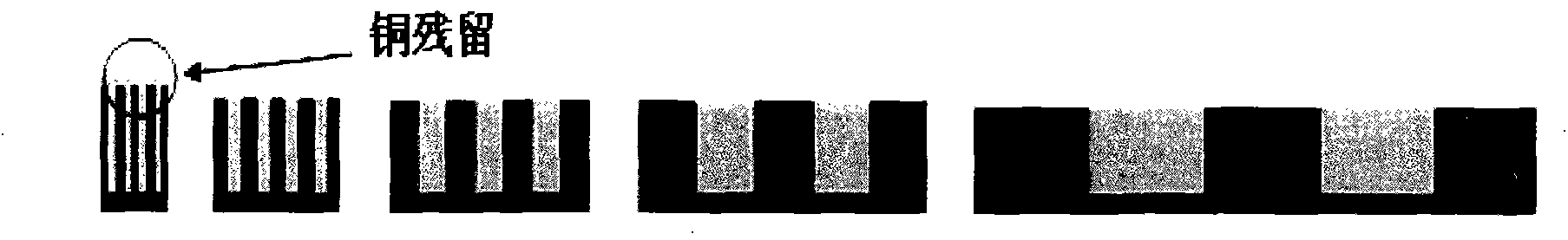

A technology of integrated circuits and layout structures, applied in circuits, electrical components, electrical solid devices, etc., can solve problems such as copper metal residues, and achieve the effects of improving yield, reducing burden, and uniform copper growth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The technical solutions of the present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

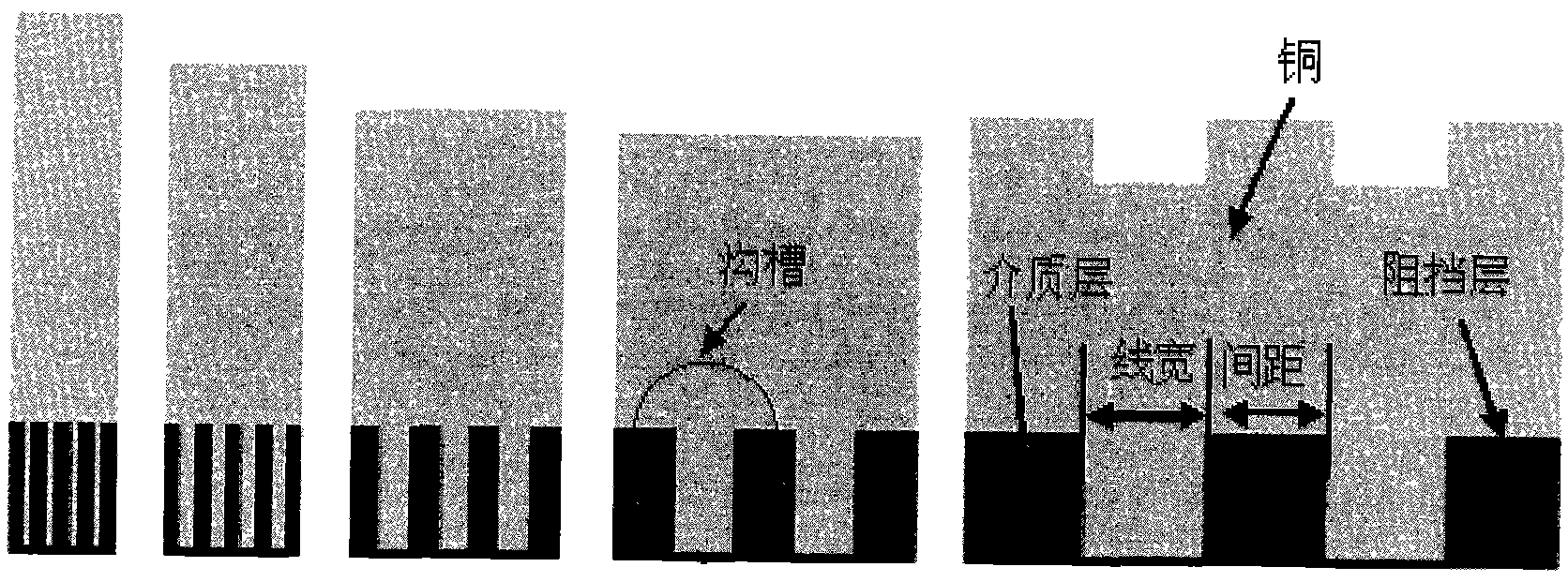

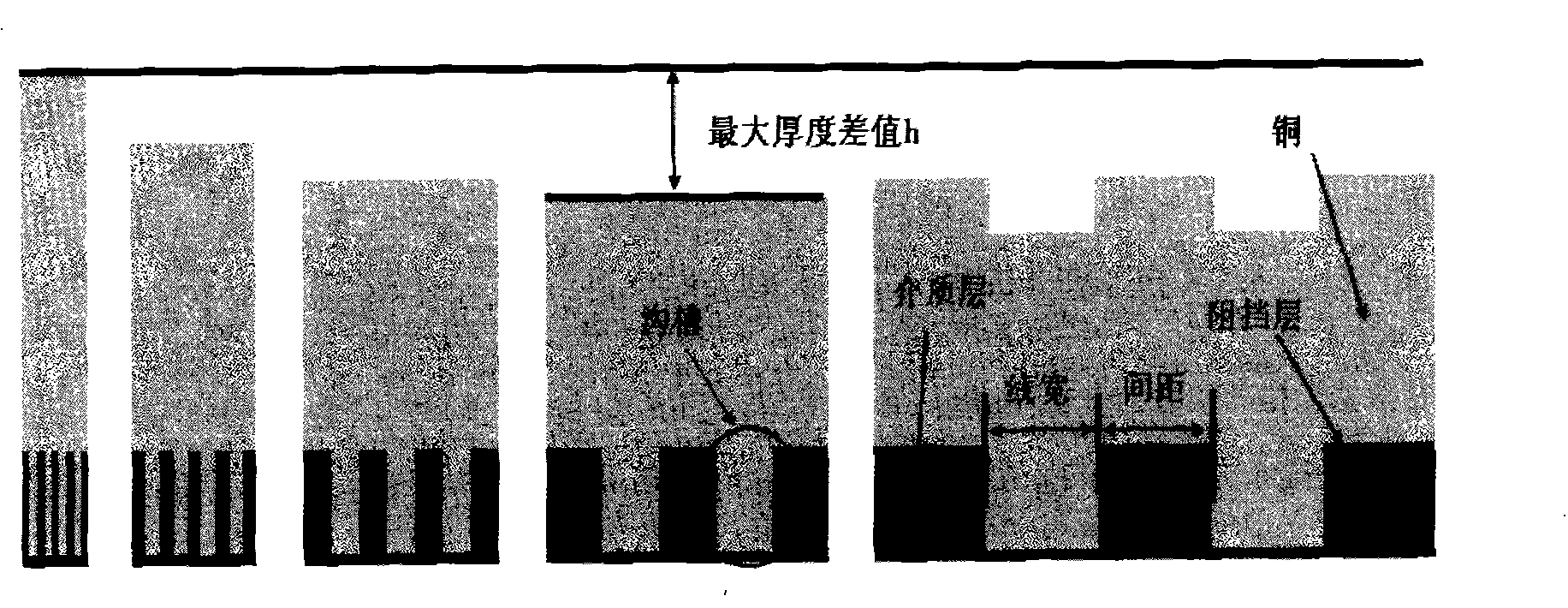

[0017] Referring to Fig. 3, the present invention is a structure of an integrated circuit layout, the width of the copper wire in the thin line area is less than 0.2 microns, the line spacing in the thin line area is twice the width of the copper wire, and the area of the copper wire is 1 / 2 of the total area of the layout. 30%, this structure reduces the copper growth thickness in the thin line area, and the copper growth of different structures is relatively uniform, which reduces the surface fluctuation before the CMP process, reduces the burden of the CMP process, improves the chemical mechanical grinding ability, and will obtain the optimal flatness effect.

[0018] A manufacturing method of an integrated circuit layout, under the condition that the total area of the layout is allowed, during the layout an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More