Patents

Literature

57results about How to "Effect on electrical performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

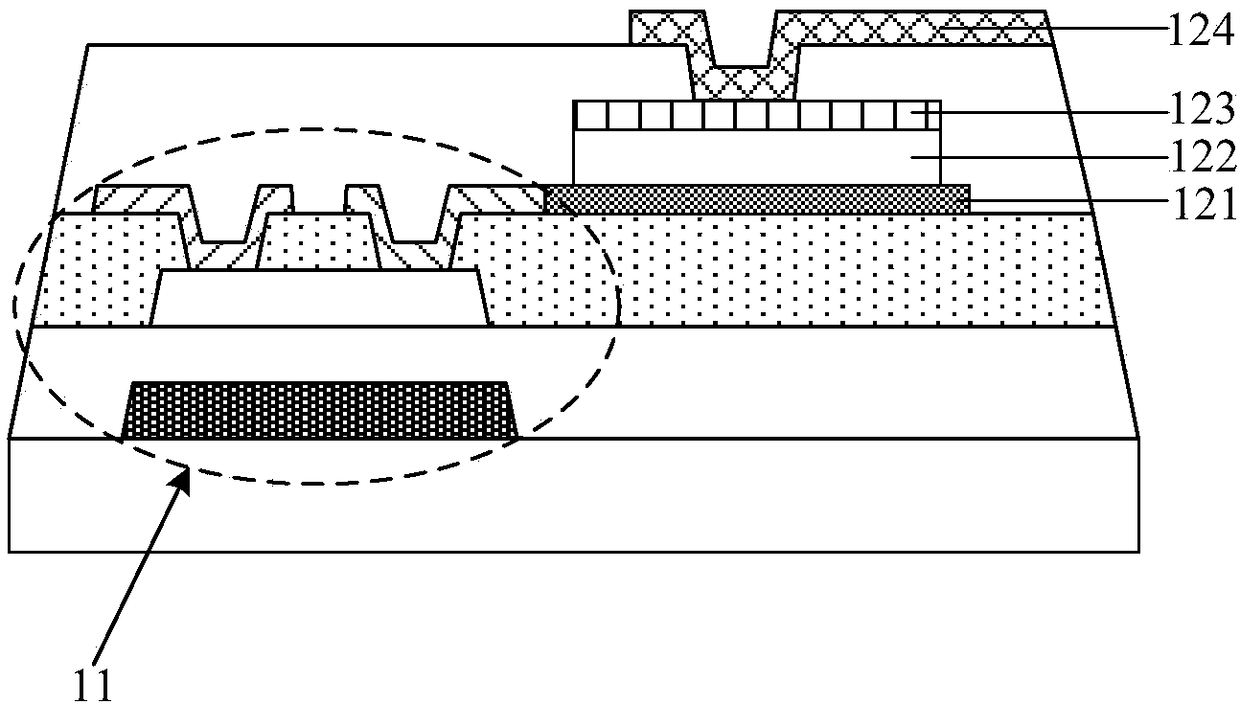

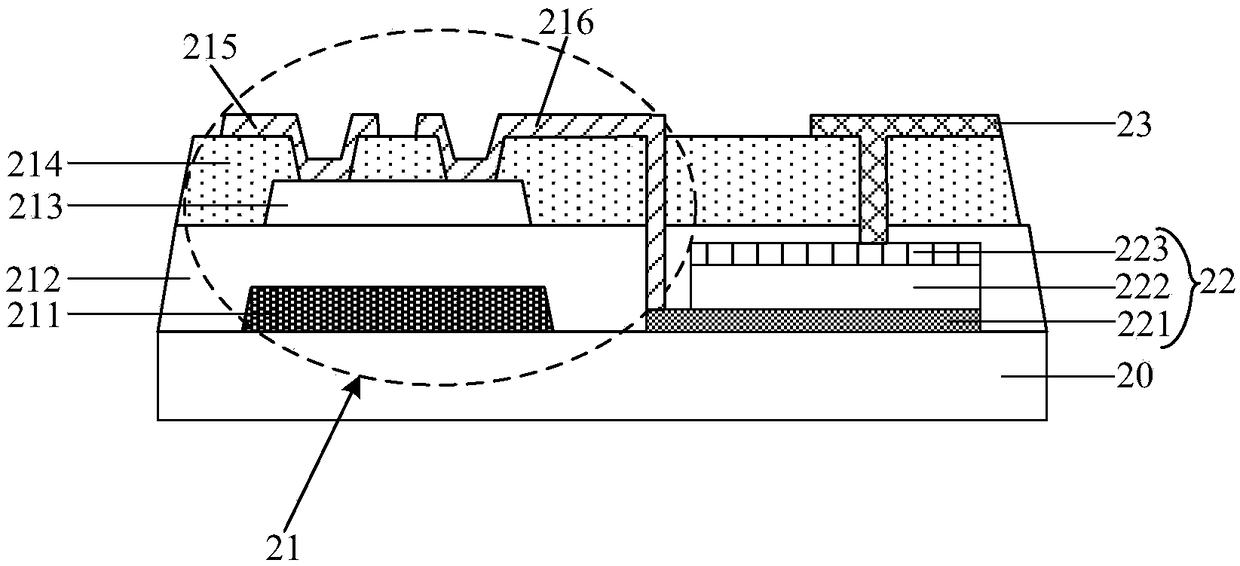

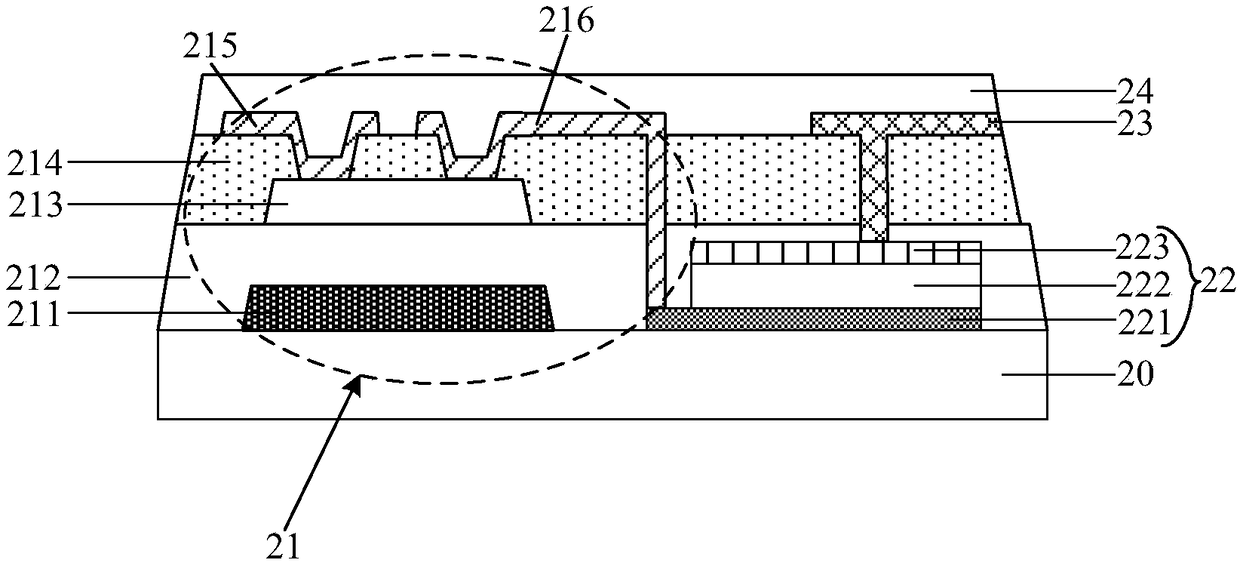

Photosensitive assembly and preparation method, array substrate and display device thereof

PendingCN108376688AEffect on electrical performanceTransistorSolid-state devicesInsulation layerHydrogen

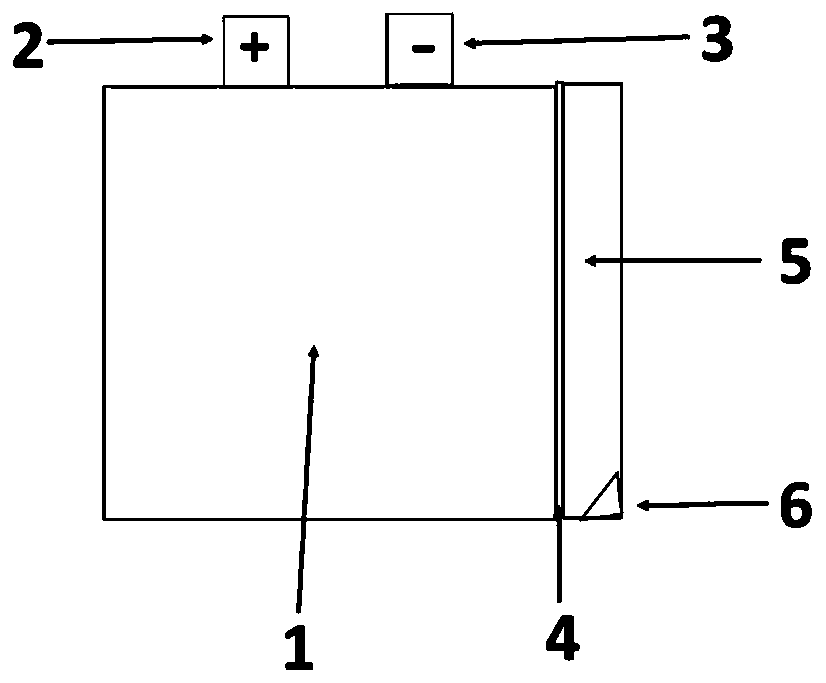

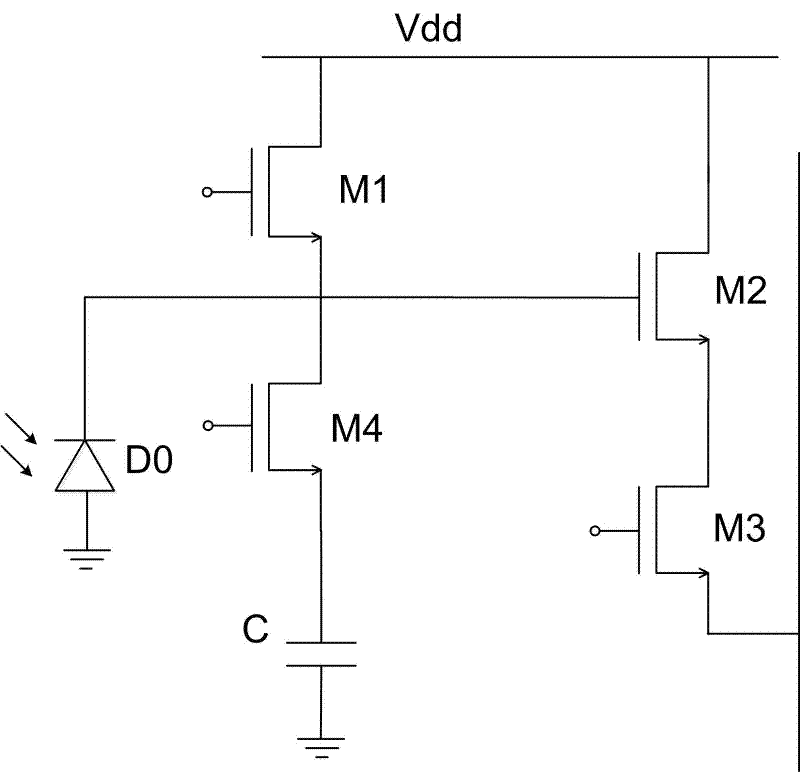

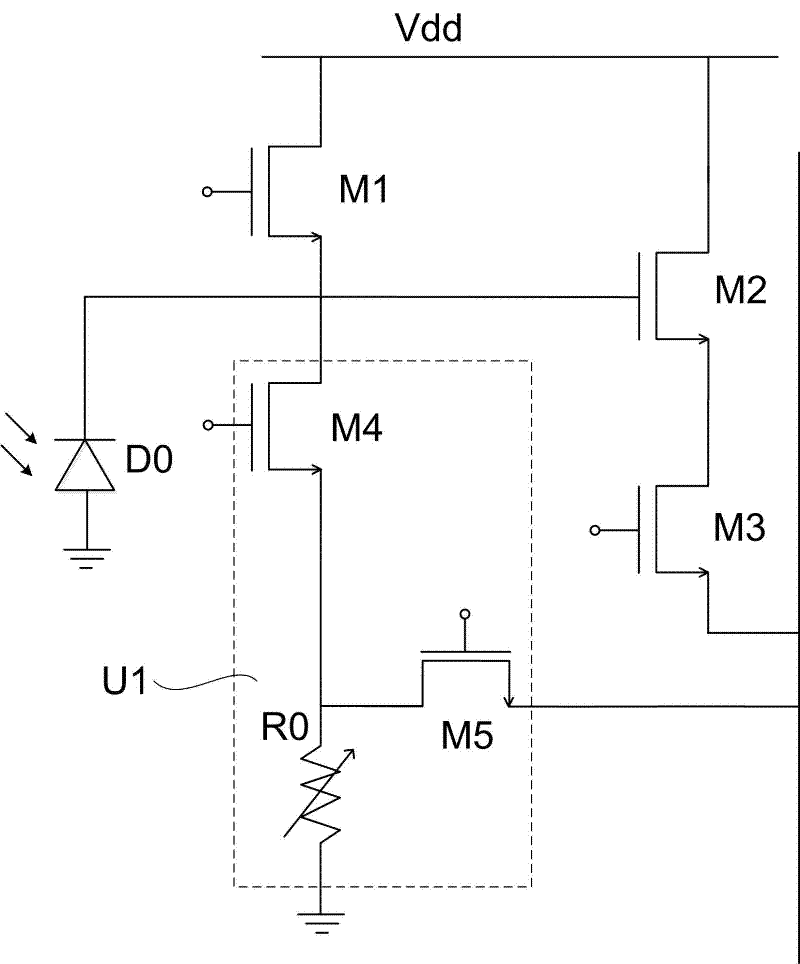

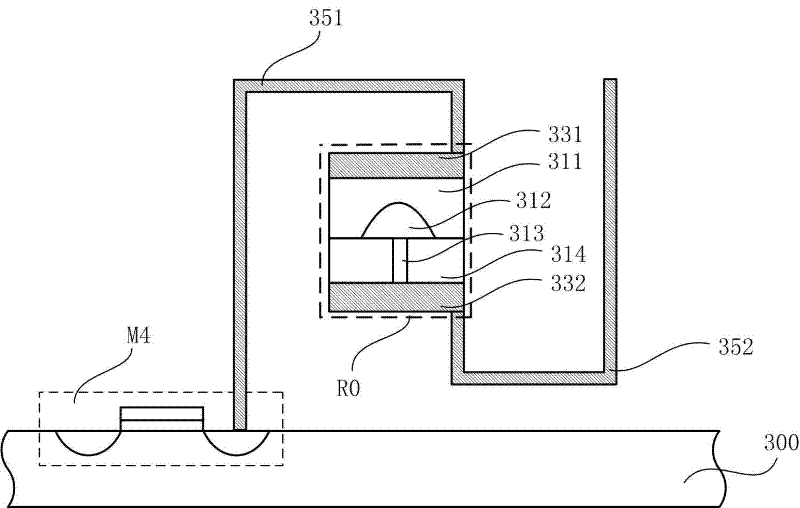

The embodiment of the invention provides a photosensitive assembly and a preparation method, an array substrate and a display device thereof, and relates to the technical field of display. The photosensitive assembly can avoid the adverse effect to the electrochemical property of a thin film transistor by H (hydrogen) element in a photosensitive sensing unit. The photosensitive assembly comprisesa substrate, the thin film transistor, a photosensitive unit and an insulation layer, wherein the thin film transistor and the photosensitive unit are staggered along the direction vertical to the thickness direction of the substrate; the insulation layer is arranged between an active layer of the thin film transistor and the photosensitive unit; the photosensitive unit sequentially comprises a first electrode, the photosensitive sensing unit and a second electrode which are sequentially arranged on the substrate; a drain of the thin film transistor is electrically connected with the first electrode; the active layer of the thin film transistor is positioned at one side, away from the substrate, of the insulation layer; the photosensitive unit is positioned at one side, near the substrate,of the insulation layer.

Owner:BOE TECH GRP CO LTD

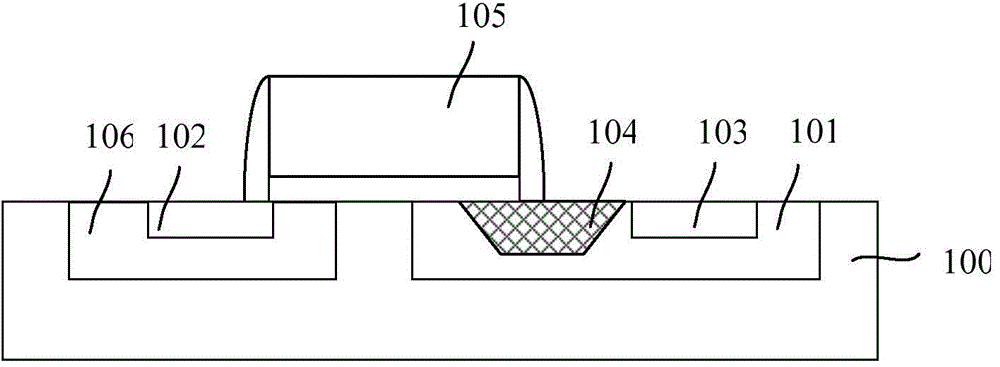

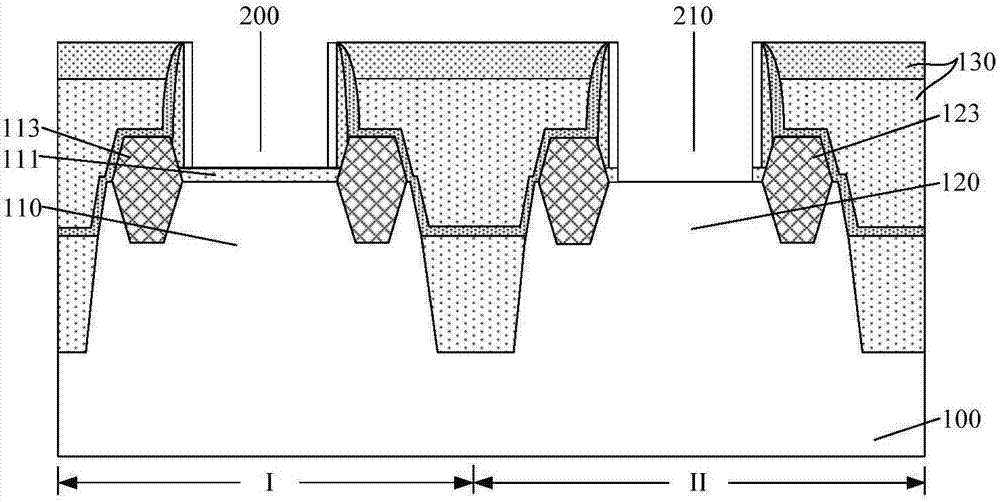

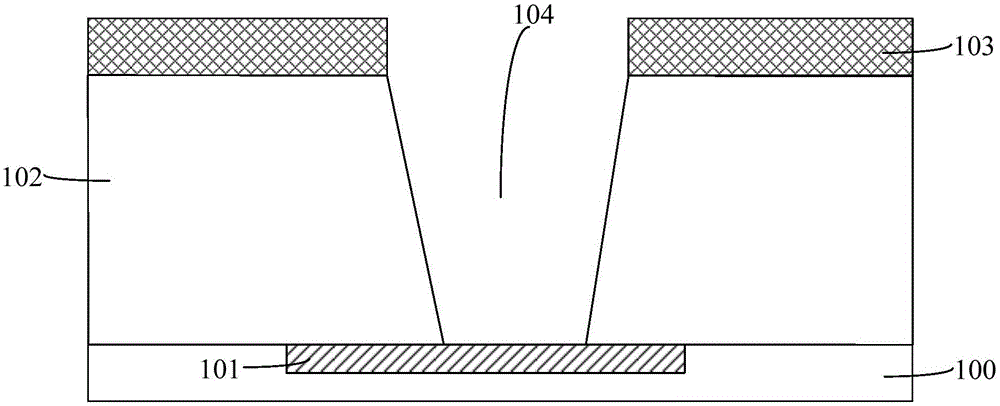

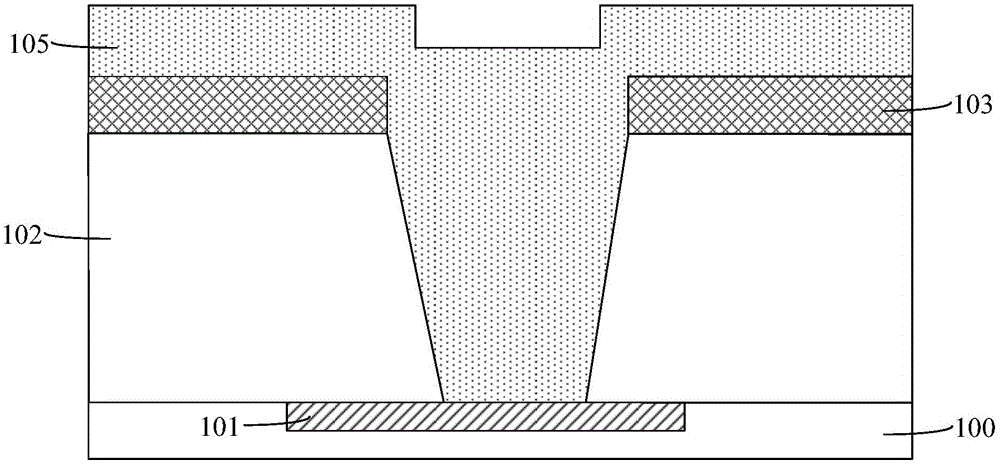

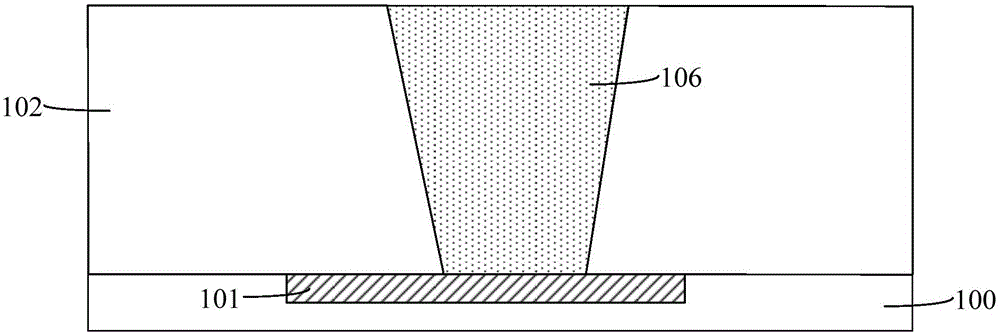

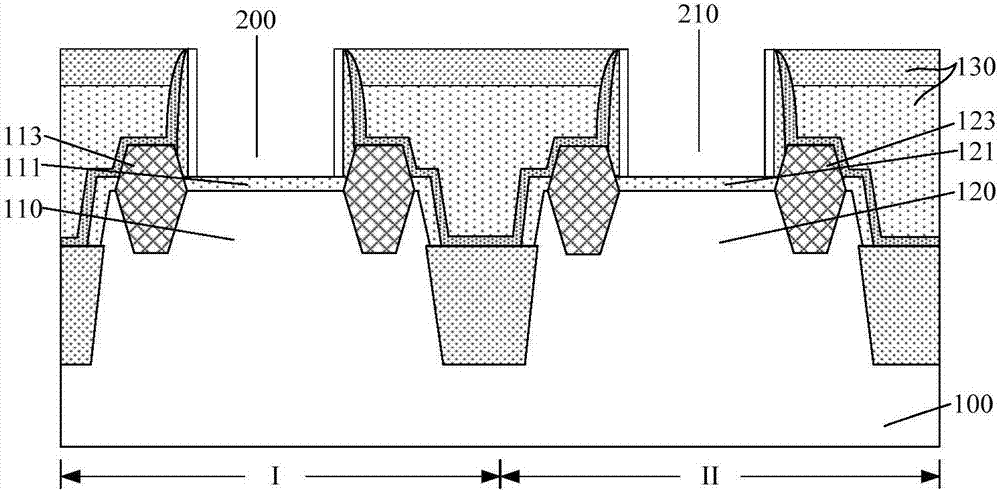

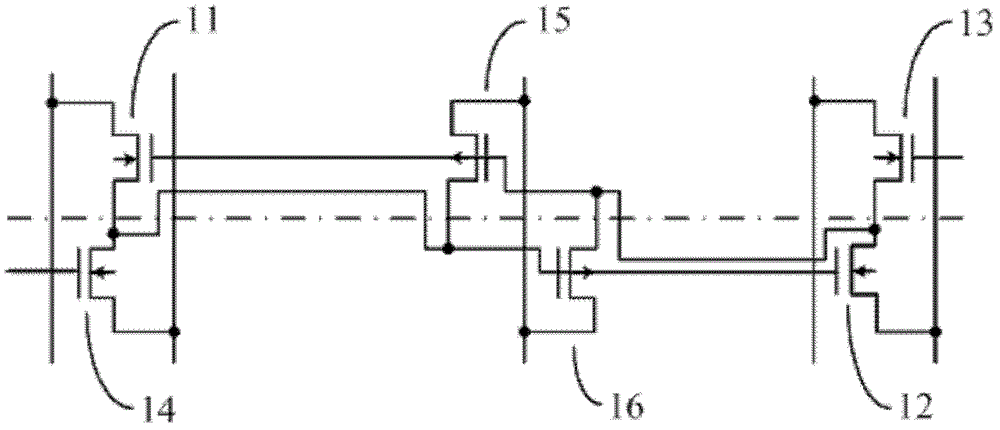

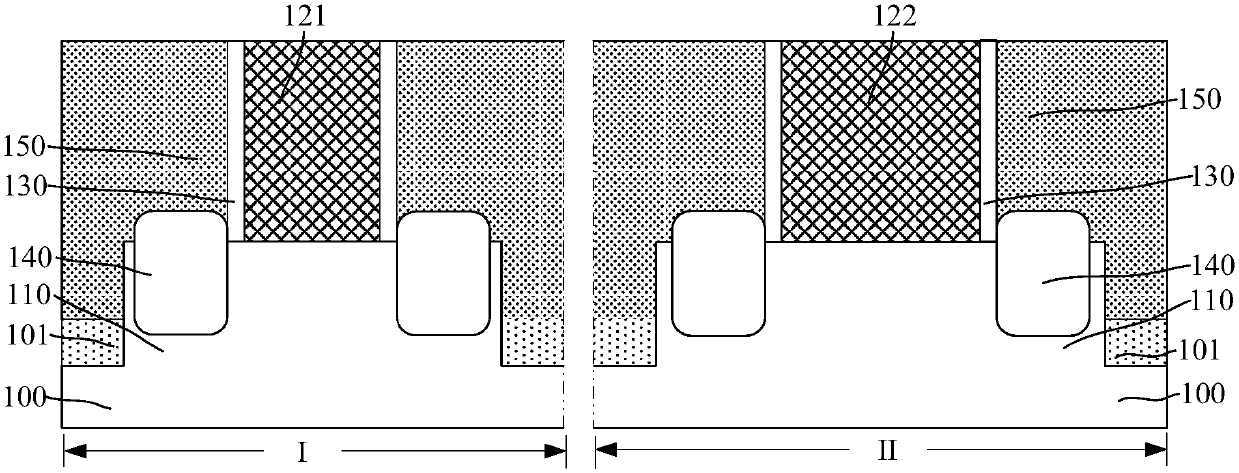

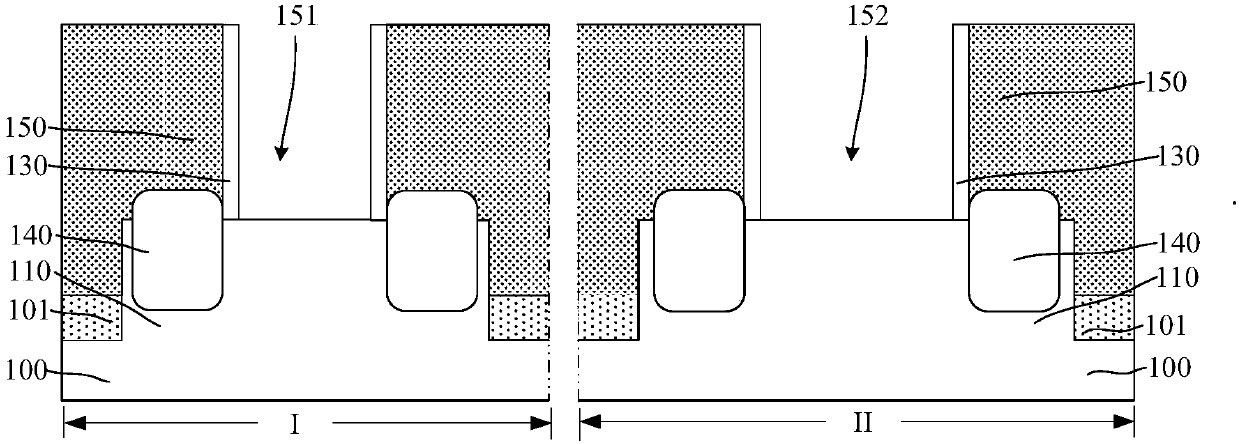

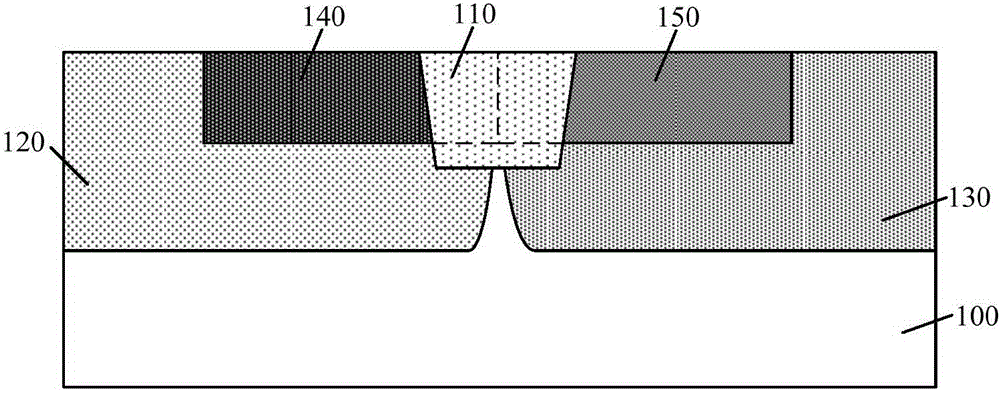

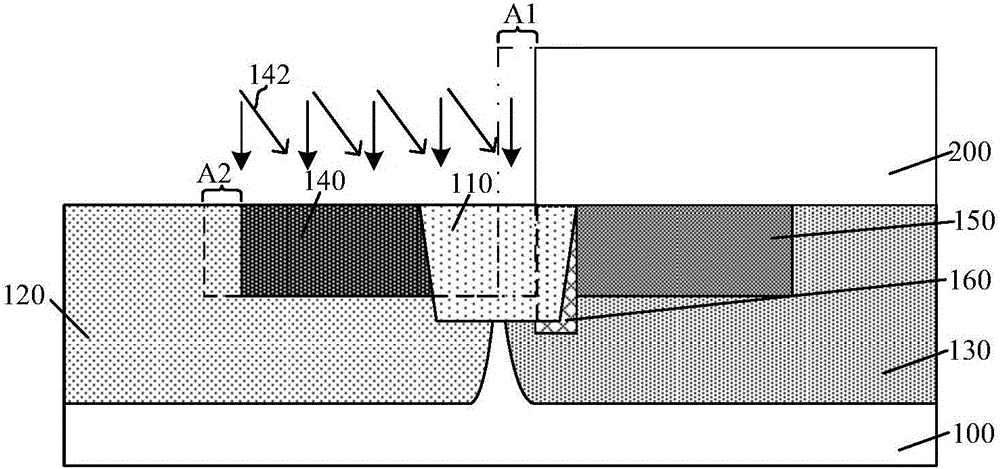

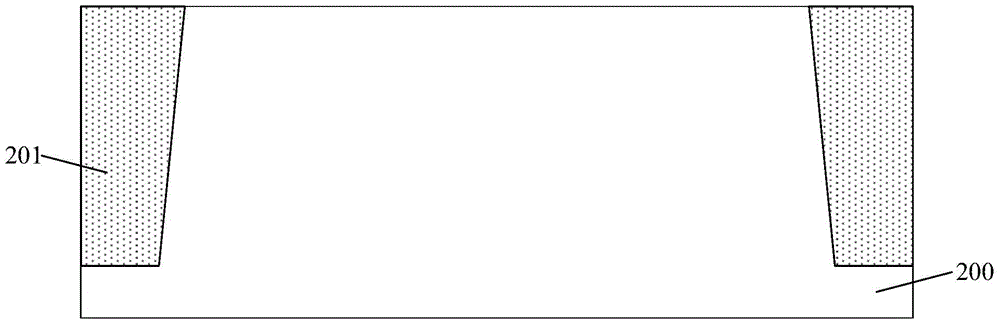

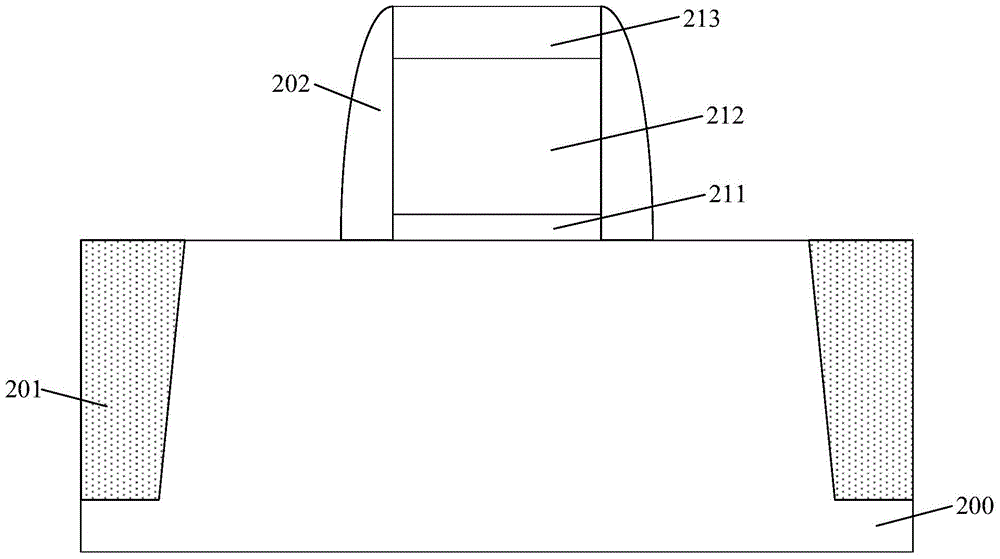

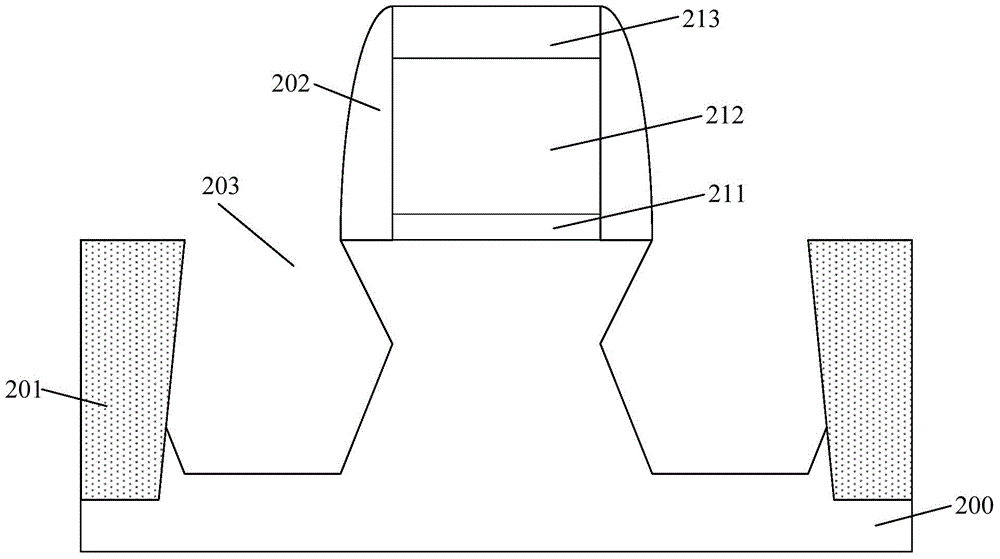

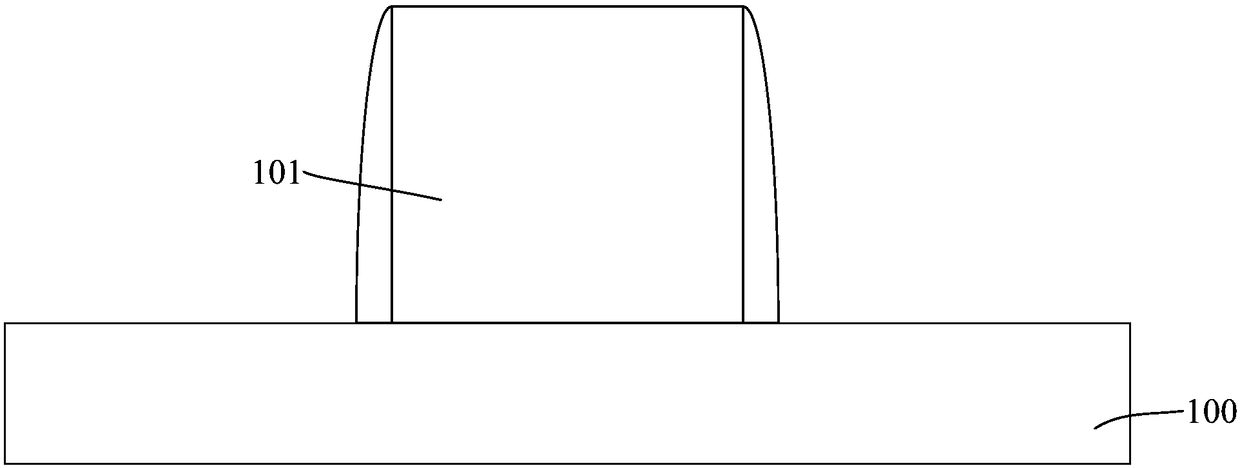

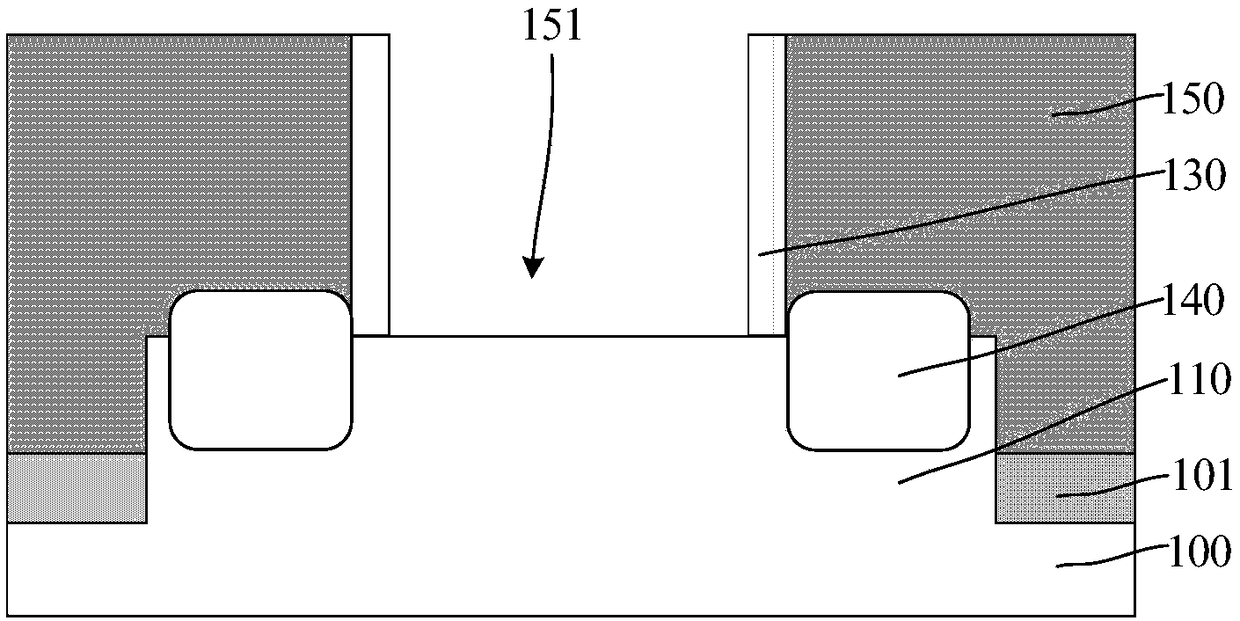

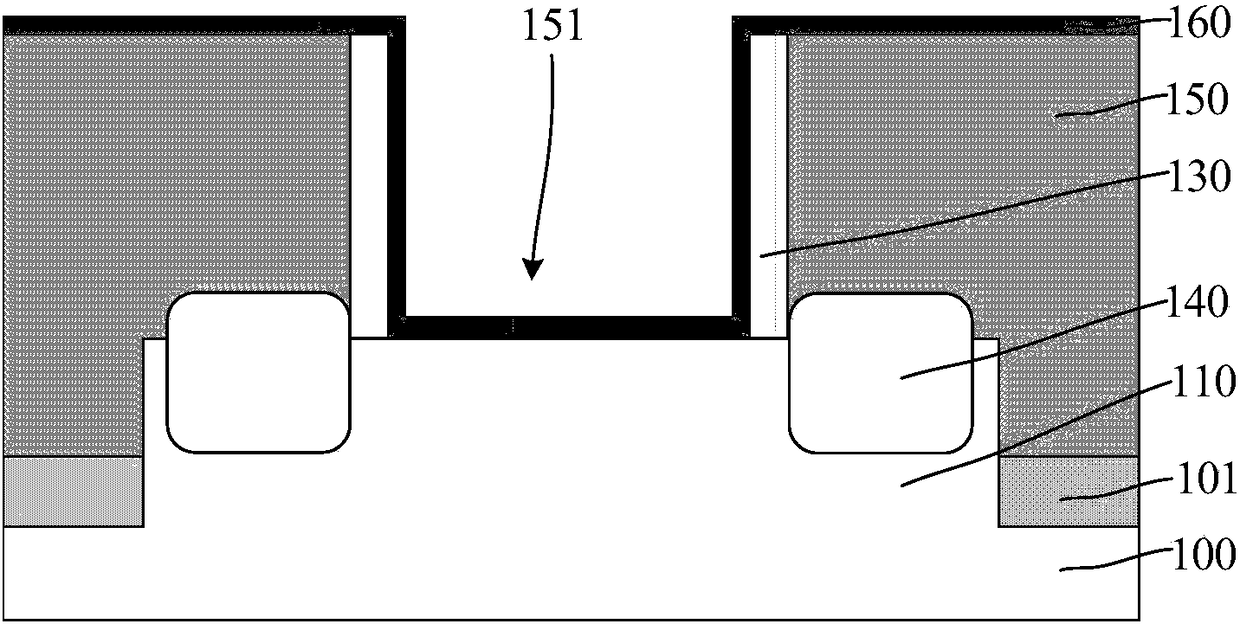

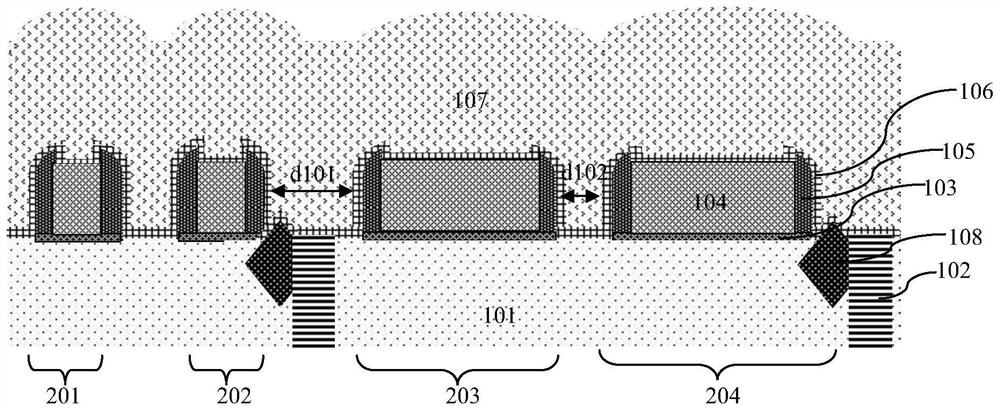

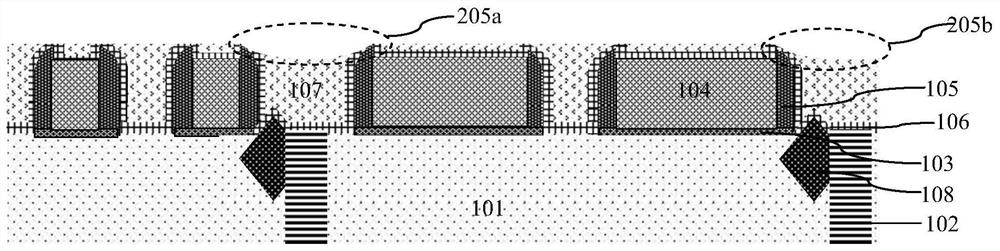

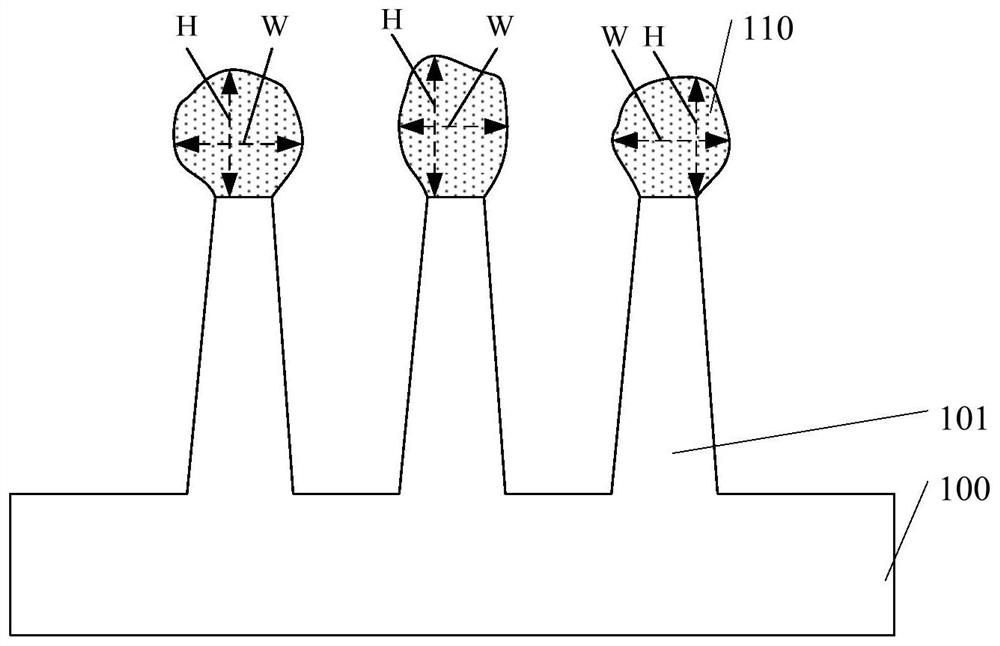

Semiconductor device and forming method thereof

ActiveCN105448725AIncrease distanceMeet the requirements of different processesSemiconductor/solid-state device manufacturingSemiconductor devicesParasitic capacitanceBody region

A semiconductor device and a forming method thereof are provided. The semiconductor device comprises a semiconductor substrate, a first shallow trench isolation structure which is disposed in the semiconductor substrate and of which the top surface is higher than the surface of the semiconductor substrate, a drift region which is disposed in the semiconductor substrate and surrounds the first shallow trench isolation structure and of which the depth is greater than the depth of the first shallow trench isolation structure, a first body region which is disposed in the semiconductor substrate on one side of the drift region and is of a doping type opposite to the doping type of the drift region, a first gate structure which is disposed on the semiconductor substrate and stretches across and covers part of the surfaces of the body region, the semiconductor substrate, the drift region and the first shallow trench isolation structure, a first drain region which is disposed in the drift region on one side of the first gate structure, and a first source region which is disposed in the first body region on the other side of the first gate structure. The gate-drain parasitic capacitance of the semiconductor device is reduced.

Owner:SEMICON MFG INT (SHANGHAI) CORP

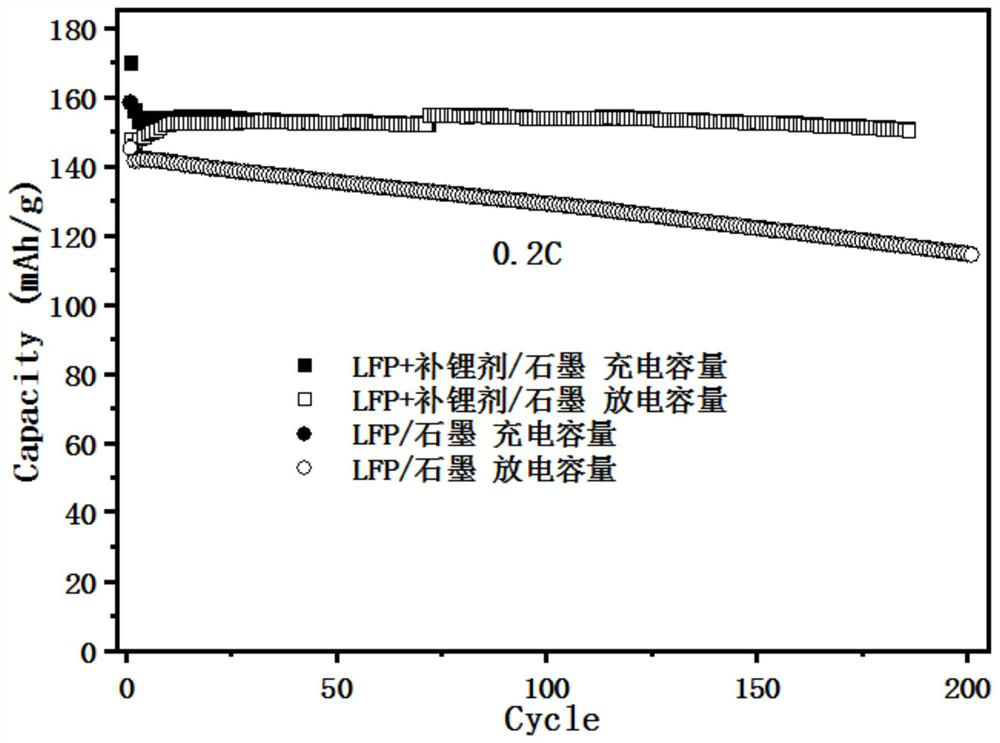

Electrolyte and lithium ion battery

ActiveCN112397786ALow costLower internal resistanceSecondary cellsOrganic electrolytesElectrolytic agentOrganic solvent

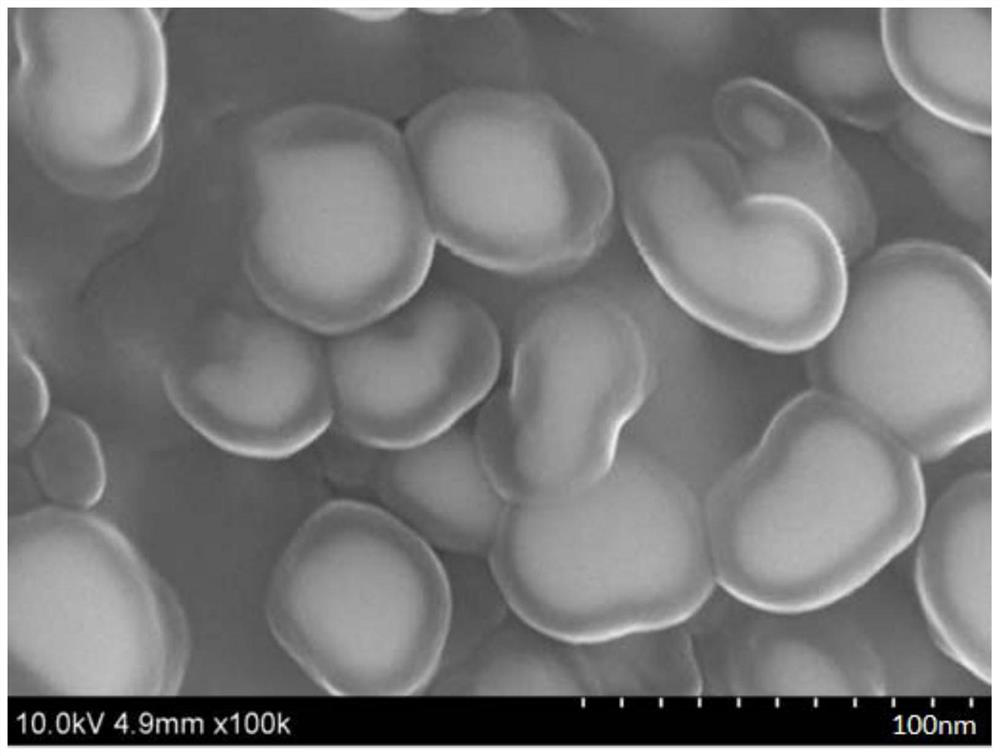

The invention provides an electrolyte and a lithium ion battery, and belongs to the technical field of batteries. The electrolyte comprises an organic solvent and a lithium salt dissolved in the organic solvent, and also comprises an auxiliary agent. The auxiliary agent is selected from one or more of S elementary substance, B elementary substance, P elementary substance and a reducing compound capable of releasing specific negative ions in the electrolyte, and the specific negative ions are selected from one or more of S negative ions, B negative ions and P negative ions. The lithium ion battery comprises the electrolyte. The specific type of auxiliary agent can effectively reduce the potential when a lithium-containing compound is decomposed; and by adding the auxiliary agent into the electrolyte, the battery is ensured to have better cycling stability, and meanwhile, the applicability in a battery production process is good.

Owner:SONGSHAN LAKE MATERIALS LAB +1

High energy graphene battery

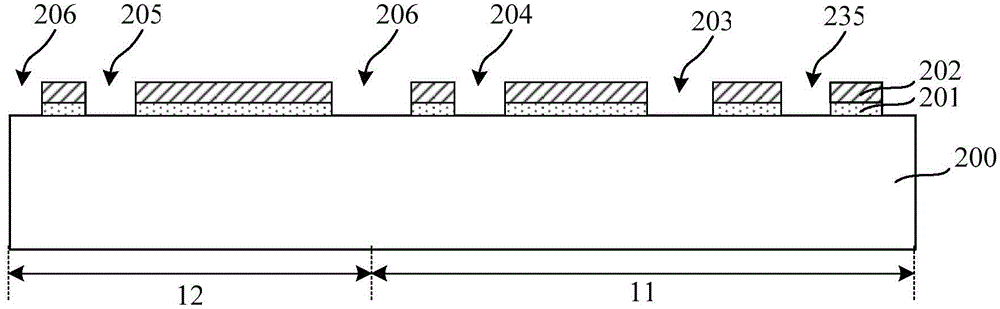

ActiveCN107369828AImprove internal conductivityImprove conductivityCell electrodesLi-accumulatorsSolid state electrolyteHigh energy

The invention discloses a high energy graphene battery which comprises a battery anode prepared from graphene wrapped Li0.89Ti0.11FePO4, a solid electrolyte membrane prepared from a Li11Si2PS12 material and a battery cathode prepared from a graphene wrapped silica-based material; the solid electrolyte membrane is arranged between the battery anode and the battery cathode, and the Li11Si2PS12 solid electrolyte membrane is prepared by taking Li2S particles, SiS2 particles and P2S5 particles at a mole mass ratio of 11:4:1 as raw materials, performing grinding and mixing by a high energy ball milling method, preparing sheets by taking molten polyphenyl ether, and performing roll squeezing, hot press molding and chloroform soaking. The prepared graphene battery has the advantages of safety, stability, and high weight energy density, the high pressure is not required in a preparation process, and the preparation cost is low.

Owner:深圳市荣利伟业科技有限公司

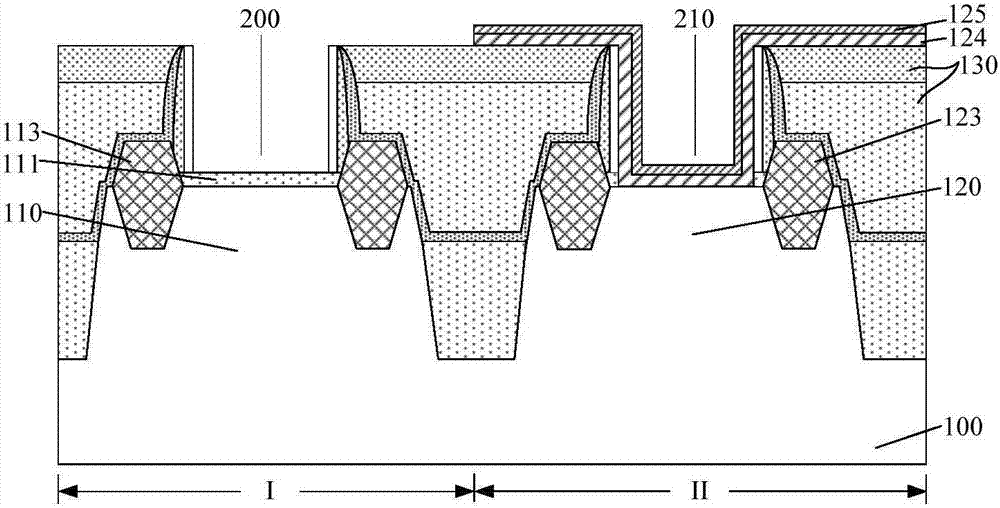

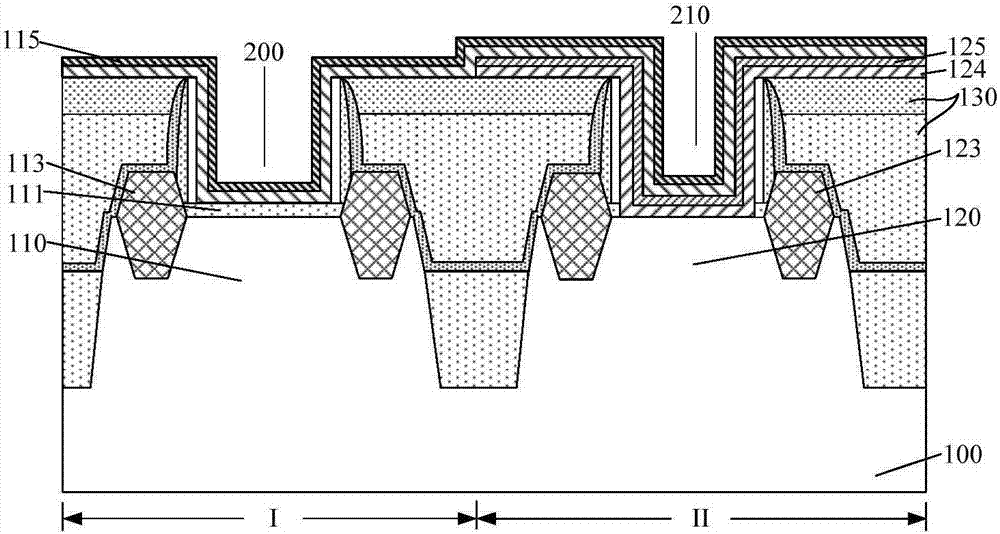

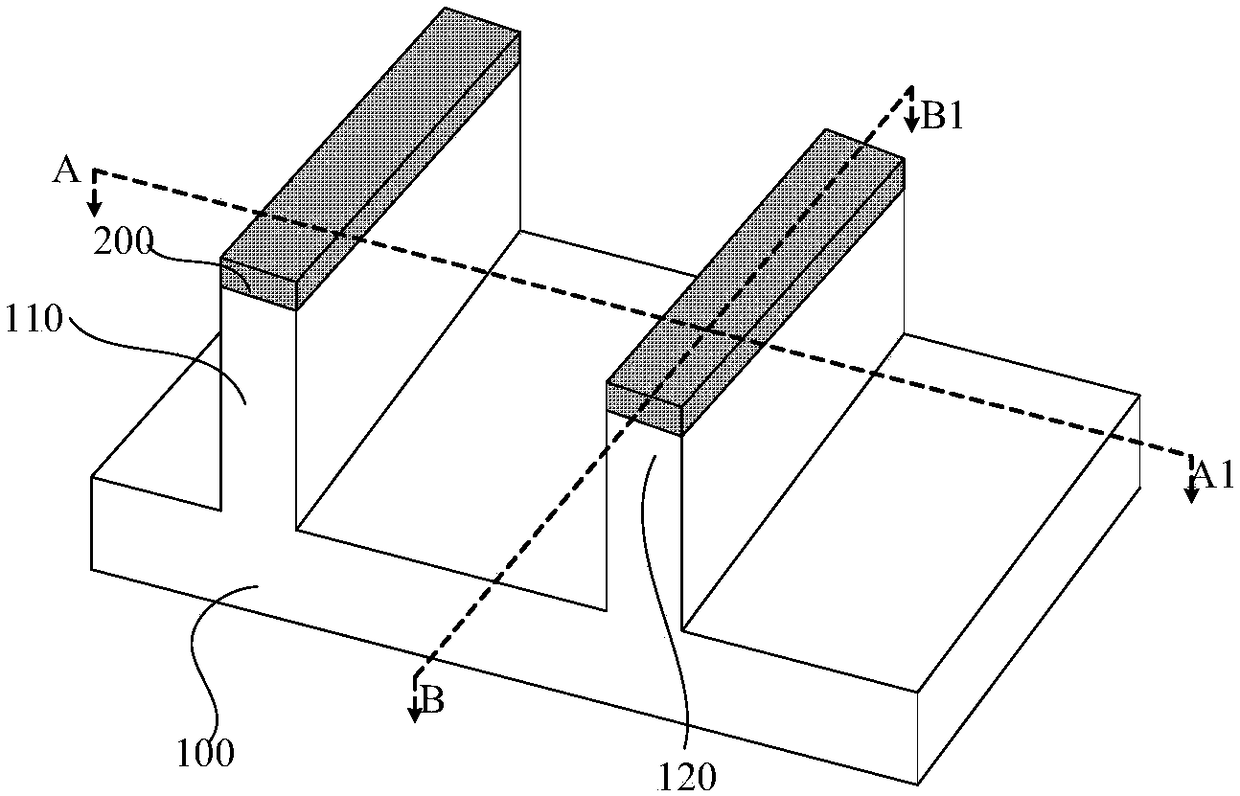

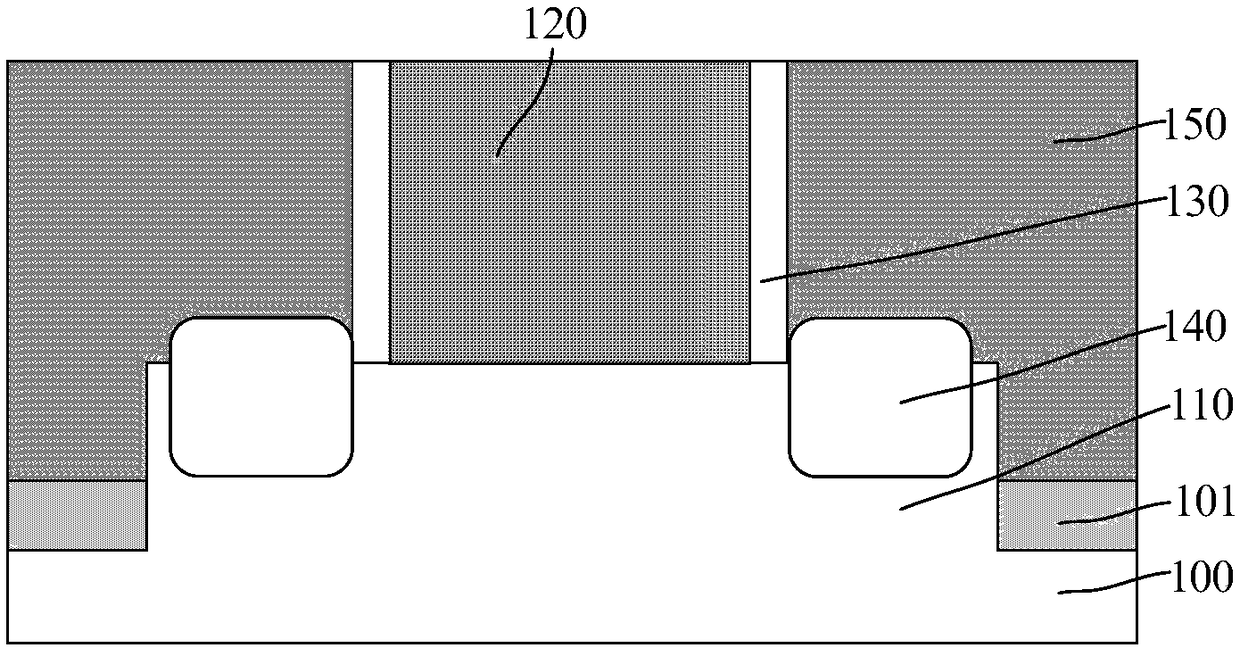

Semiconductor structure and manufacturing method thereof

ActiveCN107346783AReduce process difficultyAvoid voidsSemiconductor/solid-state device manufacturingSemiconductor devicesWork functionSemiconductor structure

The invention provides a semiconductor structure and a manufacturing method thereof. The manufacturing method comprises the steps of: providing a substrate comprising a first region and a second region; forming an interlayer dielectric layer on the substrate; forming a first opening through which the substrate is exposed in the interlayer dielectric layer in the first region, and forming a second opening through which the substrate is exposed in the interlayer dielectric layer in the second region; forming gate dielectric layers on the bottom part and the side wall of the first opening as well as that of the second opening; forming a second work function layer on the gate dielectric layer in the second region; converting a partial thickness of the second work function layer into a barrier layer; forming a first work function layer on the gate dielectric layer in the first region and the barrier layer in the second region; and forming a metal layer which fills up the first opening and the second opening. According to the semiconductor structure and the manufacturing method thereof, the partial thickness of the second work function layer is converted into the barrier layer, the barrier layer can prevent metal ions in the first work function layer from diffusing into the second work function layer, and an additional film layer is not introduced, thereby avoiding adverse influence on the performance of the second work function layer.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

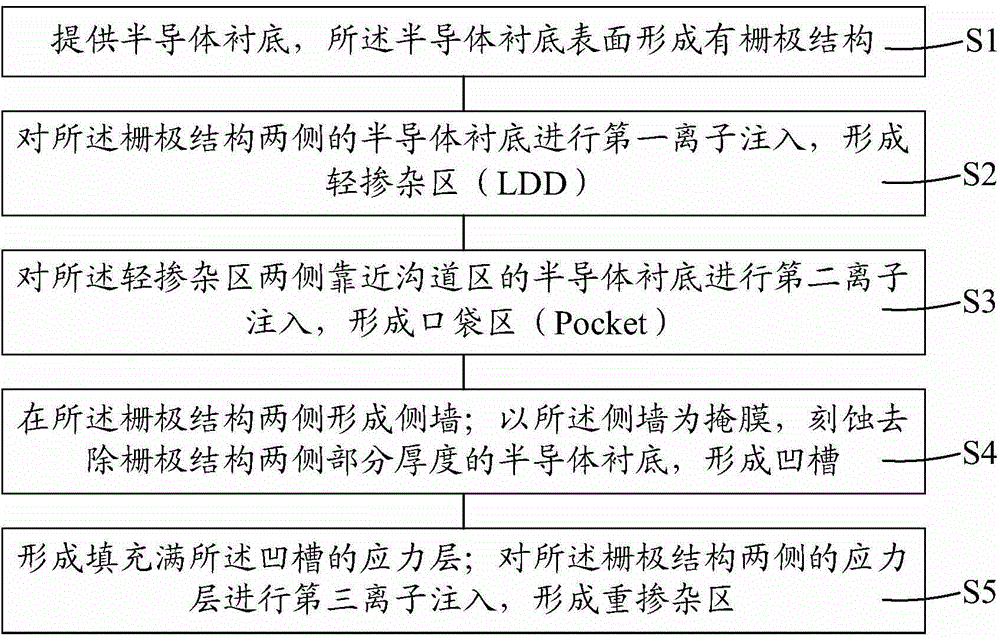

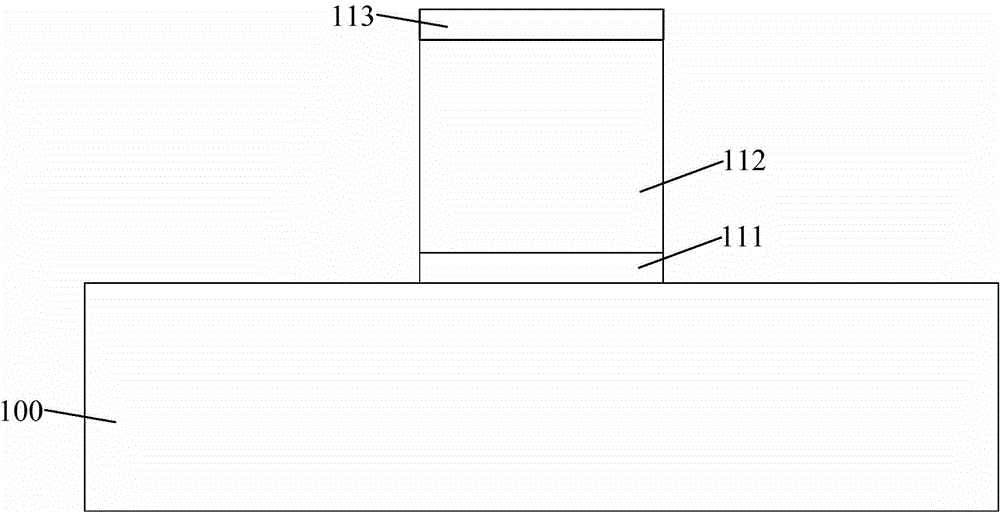

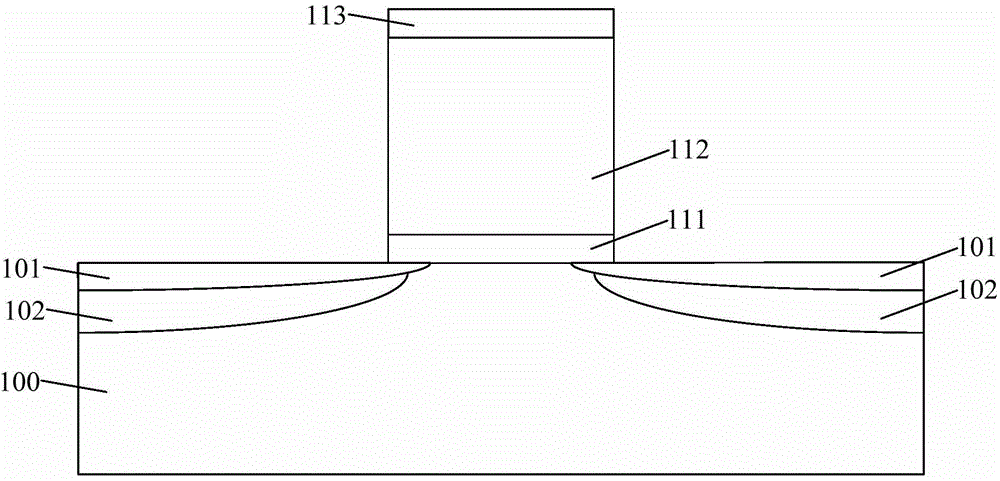

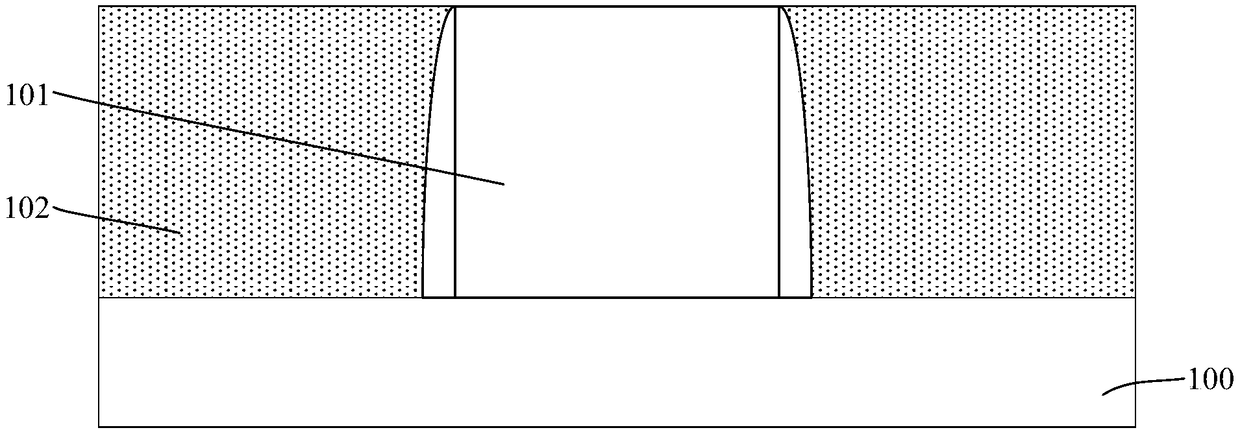

Semiconductor device and forming method thereof

InactiveCN106158634AImprove short channel effectIncrease source-drain breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesIonShort-channel effect

The invention provides a semiconductor device and a forming method thereof. The forming method of the semiconductor device comprises the steps of providing a substrate, wherein a gate structure is formed on the surface of the substrate; etching a certain thickness part of the substrate on the two sides of the gate structure so as to form a groove in the substrate; forming a diffusion barrier layer on the surface of the sidewall of the groove that is close to the gate structure; forming a stress layer on the surface of the diffusion barrier layer to fill the groove with the stress layer; conducting the doping treatment on the stress layer and forming a heavily doped region in the stress layer. According to the technical scheme of the invention, doped ions in the heavily doped region are prevented from being diffused into the substrate under the gate structure, so that the short-channel effect is improved. Meanwhile, the source / drain breakdown voltage is increased and the leakage current of the semiconductor device is reduced.

Owner:SEMICON MFG INT (SHANGHAI) CORP

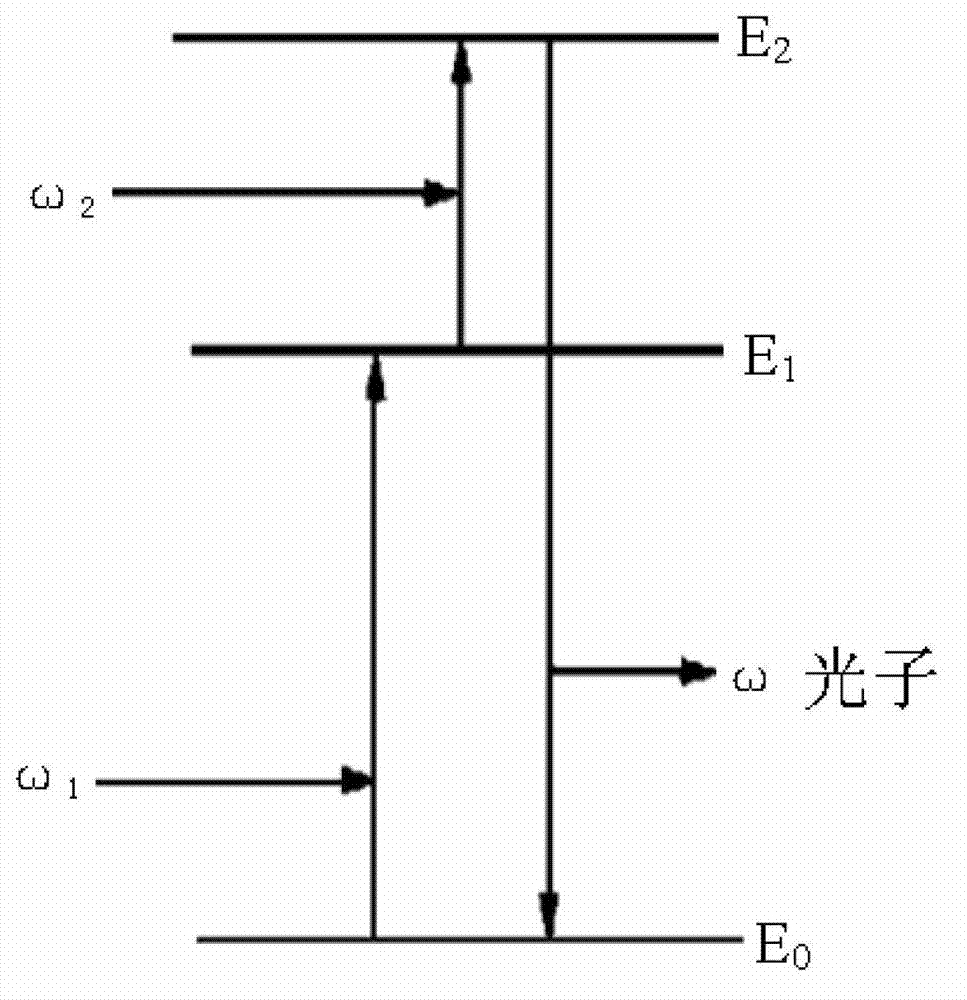

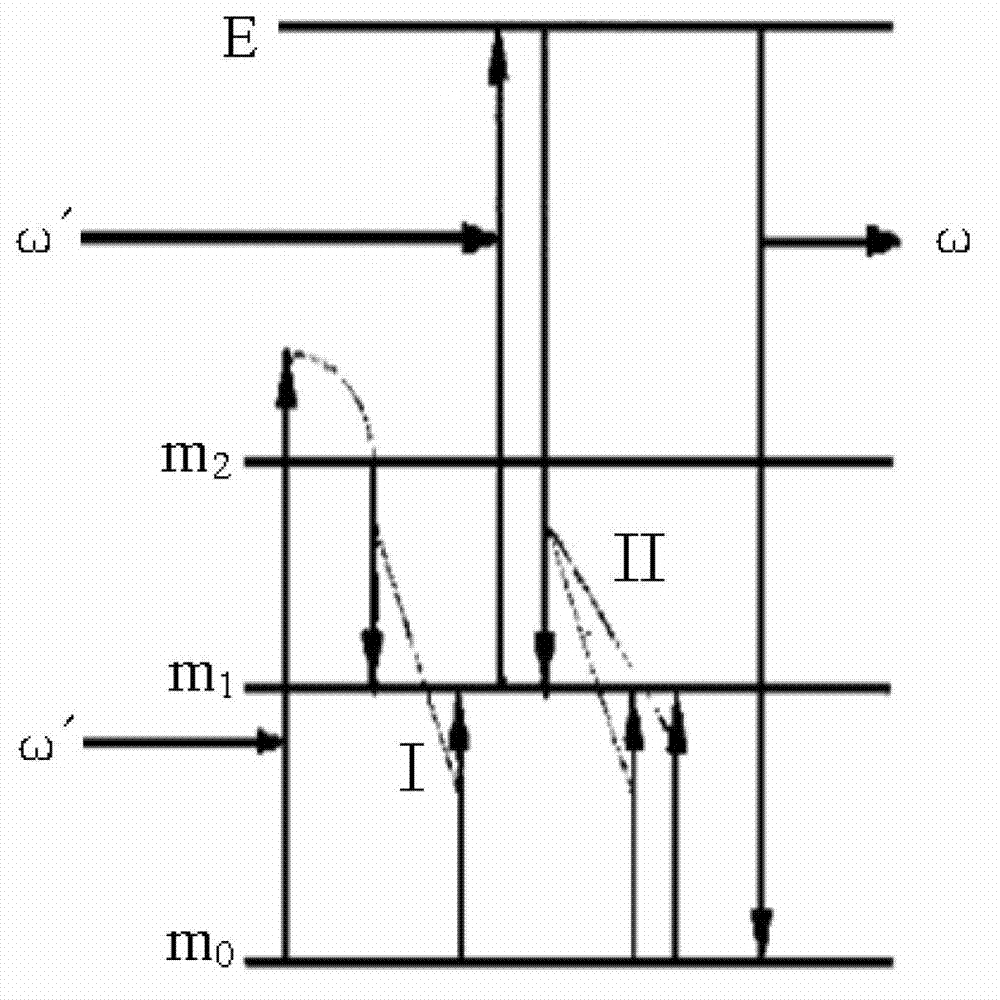

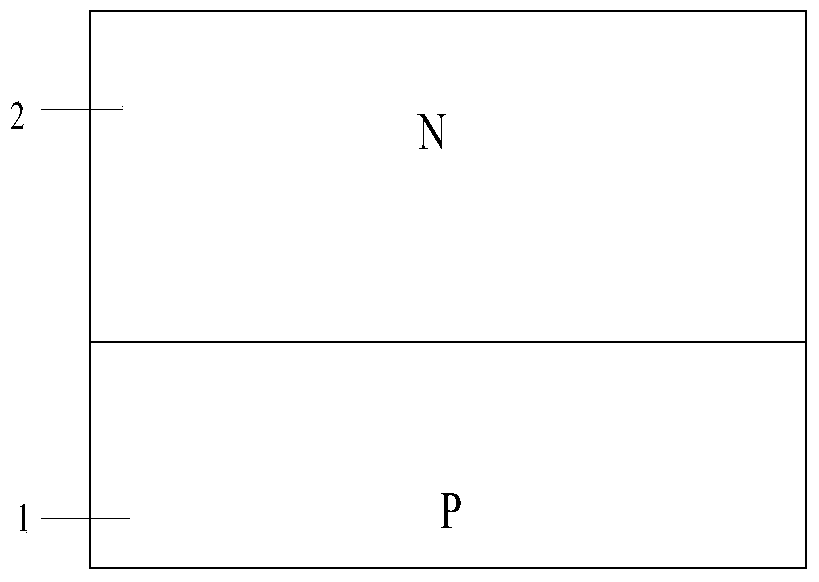

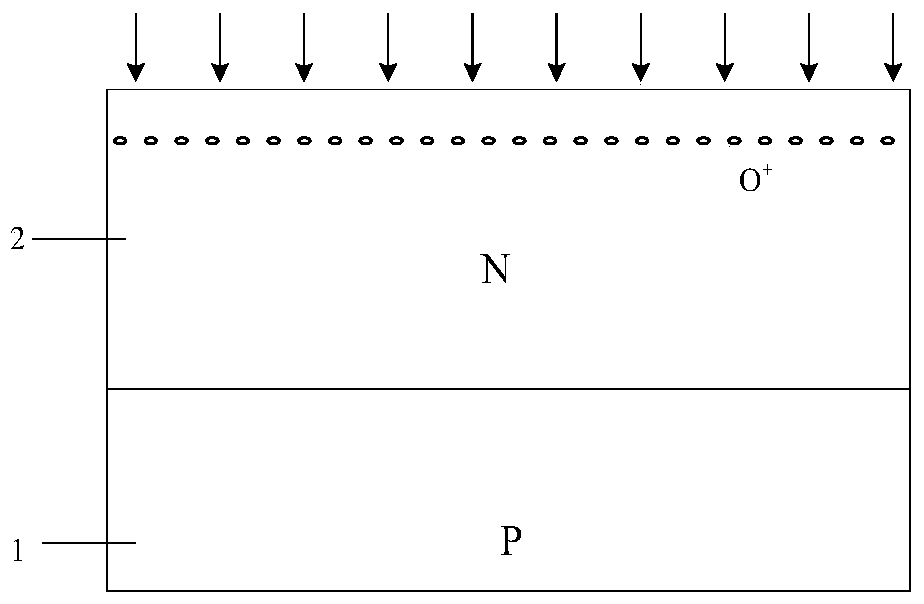

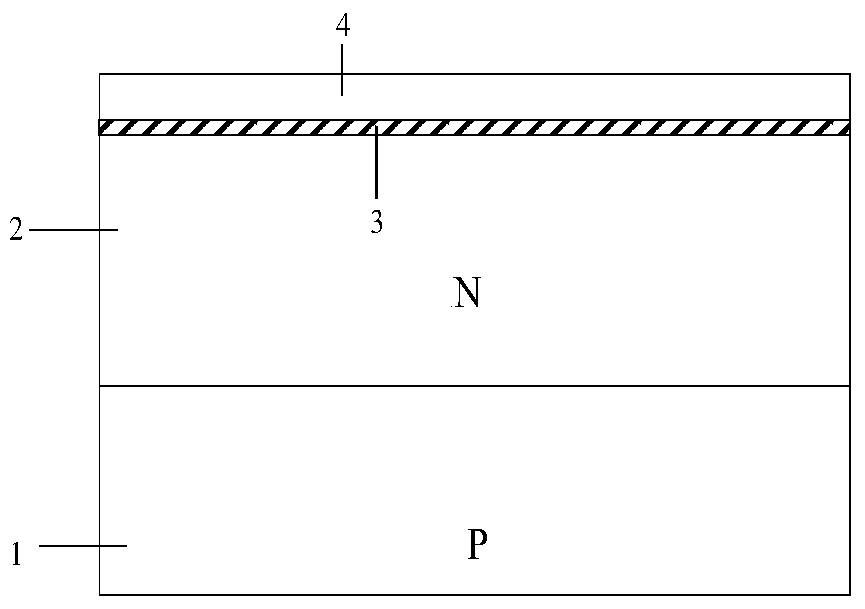

Crystalline silicon containing up-conversion luminance quantum dot and preparation method of crystalline silicon

ActiveCN102832267ASimple processLow production costFinal product manufactureSemiconductor devicesRare-earth elementMonocrystalline silicon

The invention discloses a preparation method of crystalline silicon containing up-conversion luminance quantum dots. The preparation method comprises the following steps: step 1. doping 8ppbw-120ppmw of rare-earth elements into solar polycrystalline silicon materials, utilizing an ordinary CZ method to prepare the monocrystalline silicon, or utilizing an ordinary ingot casting method to prepare the polycrystalline silicon, wherein the concentration of the atom quantity of the rare-earth elements in the monocrystalline silicon or the polycrystalline silicon is 1010-1016atoms / cm3; and step 2. carrying out annealing treatment on the monocrystalline silicon or the polycrystalline silicon prepared in the step 1 at 700-1000 DEG C, so as to obtain the monocrystalline silicon or the polycrystalline silicon containing the up-conversion luminance quantum dots. The invention also discloses the monocrystalline silicon prepared by the method, and the concentration of the rare-earth elements in the monocrystalline silicon or the polycrystalline silicon is 1010-1016atoms / cm3. With the adoption of the preparation method, the absorption of silicon materials to an infrared spectrum is increased, and the conversion efficiency is improved greatly.

Owner:LONGI GREEN ENERGY TECH CO LTD

Formation method of semiconductor structure

ActiveCN106409751AAvoid etch damageClose contactSemiconductor/solid-state device manufacturingSemiconductor structureDielectric layer

A formation method of a semiconductor structure comprises the steps of providing a substrate in which a bottom-layer metal layer is formed; forming a dielectric layer covering the surfaces of the substrate and the bottom-layer metal layer, wherein the material of the dielectric layer has a porous structure; forming a patterned mask layer on the surface of the dielectric layer; taking the patterned mask layer as a mask to etch the dielectric layer, forming an opening penetrating the dielectric layer, and exposing the top surface of the bottom-layer metal layer out of the bottom of the opening; adopting a carbon-containing gas to carry out the first etching postprocessing on the opening, and forming a sealing layer on the surface of the side wall of the opening; after the sealing layer is formed, adopting a wet etching process to etch and remove the patterned mask layer; forming a conductive layer filling the opening, wherein the top of the conductive layer is parallel and level with the top of the dielectric layer. According to the present invention, a technical window for forming the conductive layer is added, and the electrical property of the semiconductor structure is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Semiconductor structure and formation method thereof

ActiveCN108257916AReduce manufacturing costReduce the impactTransistorSolid-state devicesDopantSemiconductor structure

Disclosed are a semiconductor structure and a formation method thereof. The formation method comprises the steps of forming a base, wherein the base comprises a substrate, a gate structure positionedon the substrate, source and drain doped regions positioned in the base on the two sides of the gate structure, and an interlayer dielectric layer positioned on the base and for covering the top of the gate structure, and the substrate comprises a first region for forming a P type device and a second region for forming an N type device; forming a first contact opening for exposing the source and drain doped regions in the interlayer dielectric layer on the two sides of the gate structure; performing a P type dopant segregated schottky doping process on the source and drain doped regions exposed from the first contact opening in the first region and the second region; forming a metal silicide layer at the bottom of the first contact opening; and forming a first contact hole inserting plug in the first contact opening. By adjusting the doping concentration of the source and drain doped regions in the second region, use of a photomask can be avoided when the P type dopant segregated schottky doping process is performed, so that lowering of the process cost is realized, and the N type device suffers from relatively low influence.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

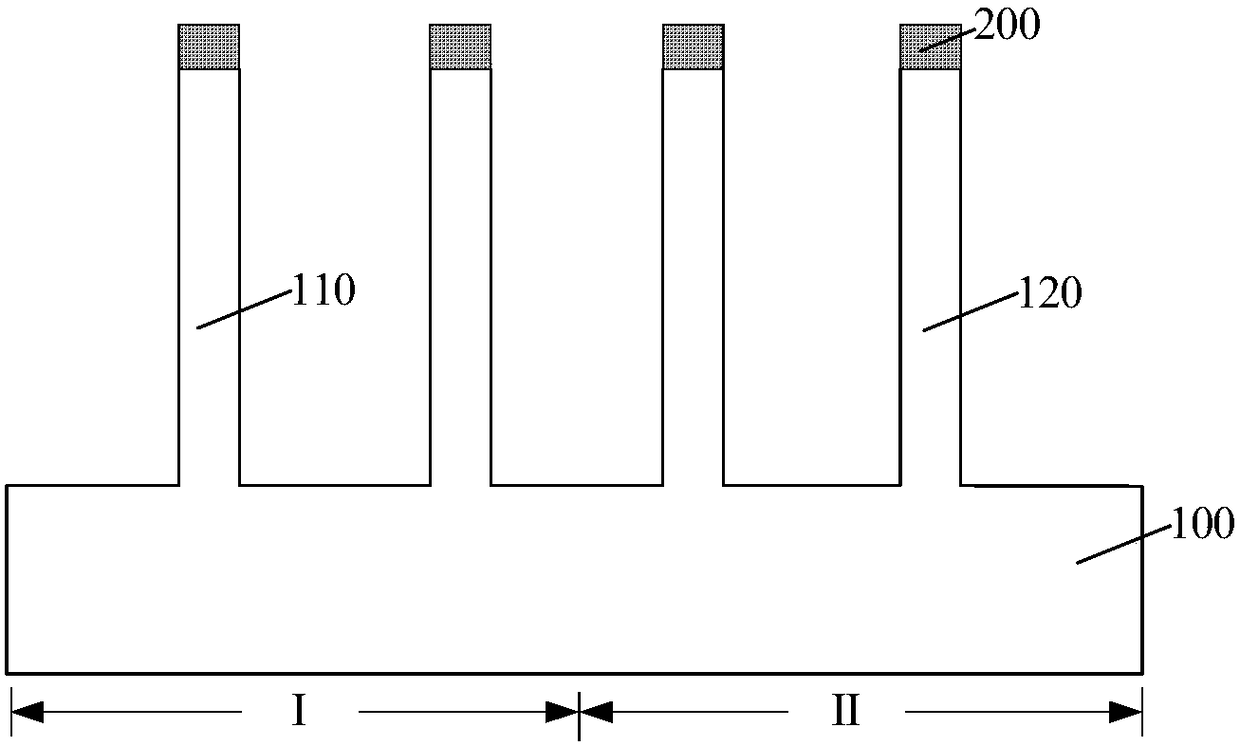

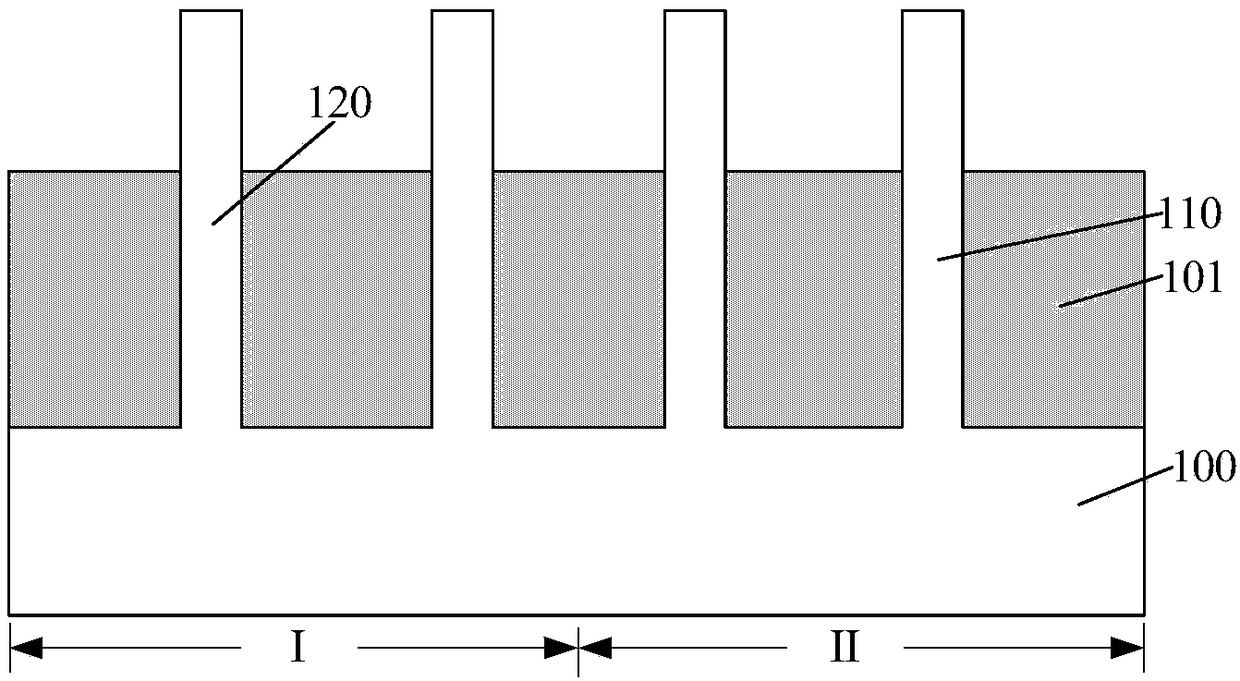

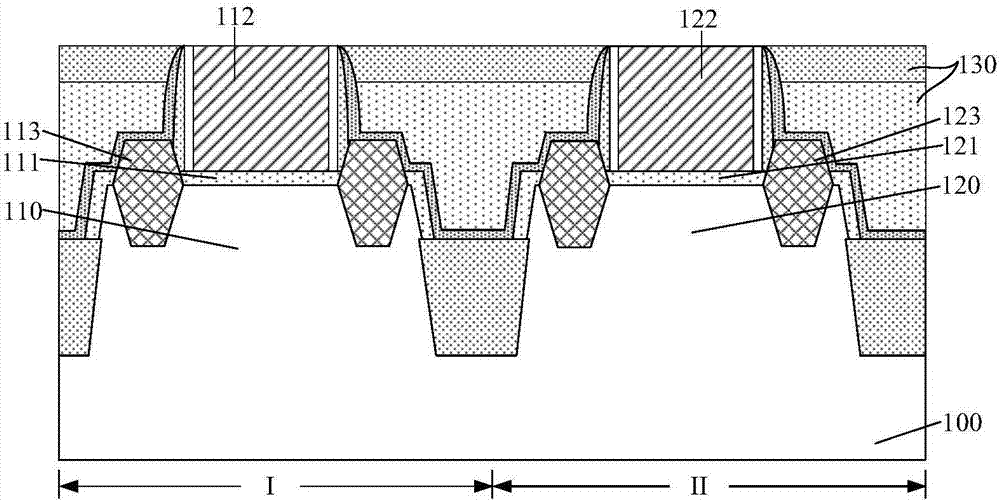

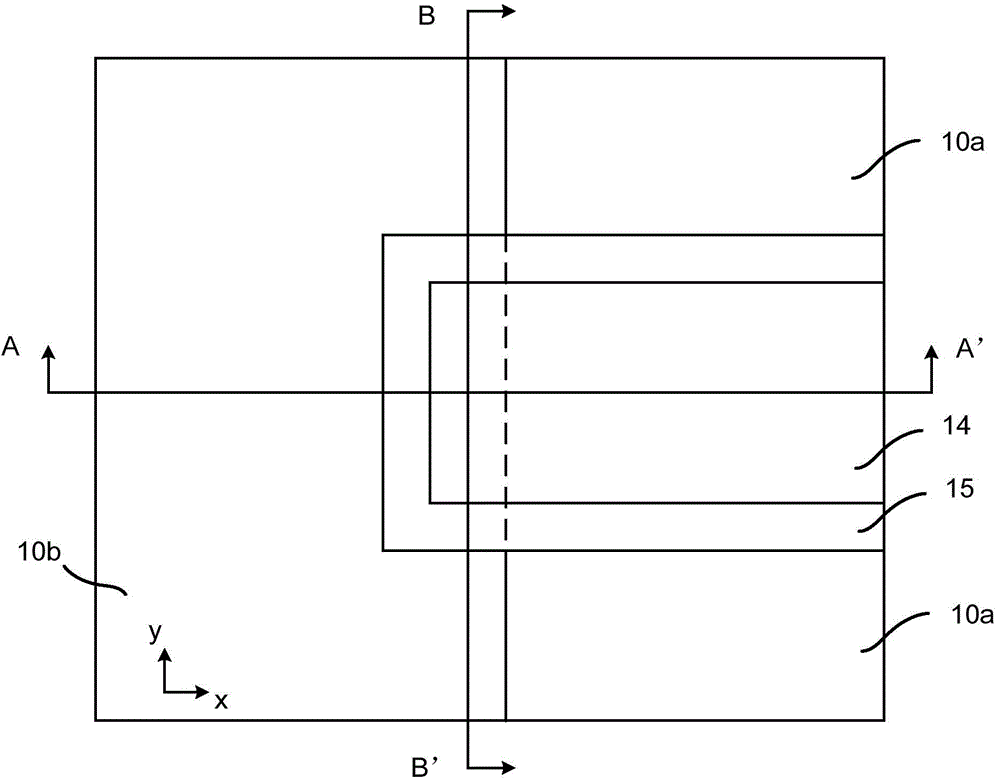

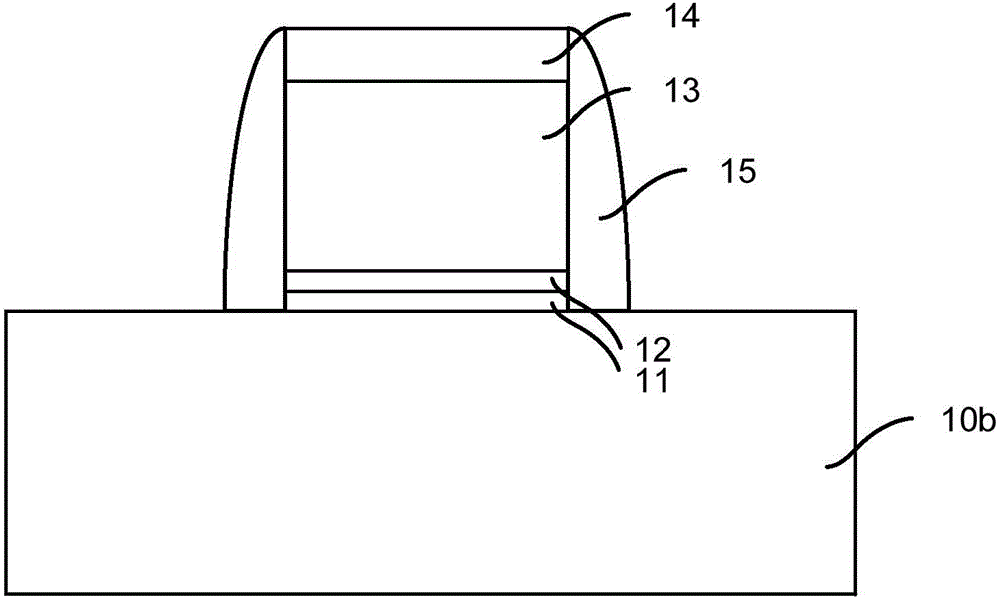

Semiconductor structure and manufacturing method thereof

InactiveCN107293488AImprove electrical performanceAvoid damageSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSemiconductor structure

The invention discloses a semiconductor structure and a manufacturing method thereof. The manufacturing method comprises the steps of forming a substrate including a first region and a second region and fin portions protruding out of the substrate; forming a first pseudo gate structure at the surface of the fin portion in the first region, wherein the first pseudo gate structure comprises a gate oxide layer and a first pseudo gate electrode layer; forming a second pseudo gate structure at the surface of the fin portion in the second region, wherein the second pseudo gate structure comprises a gate oxide layer and a second pseudo gate electrode layer; forming a dielectric layer; removing the first pseudo gate electrode layer, and forming a first opening in the dielectric layer; forming a compensation side wall at the side wall of the first opening; removing the second pseudo gate structure, and forming a second opening in the dielectric layer; forming a gate dielectric layer at the surface of the gate oxide layer, the side wall of the compensation side wall and the bottom and the side wall of the second opening; and filling a metal layer in the first opening and the second opening. The compensation side wall covers a damaged part of the gate oxide layer, so that the damaged part of the gate oxide layer is enabled to become a non-effective gate oxide layer above a channel region, and thus the electrical property of the device is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

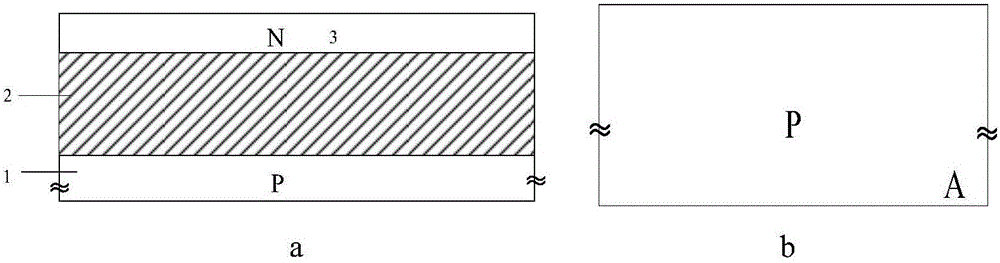

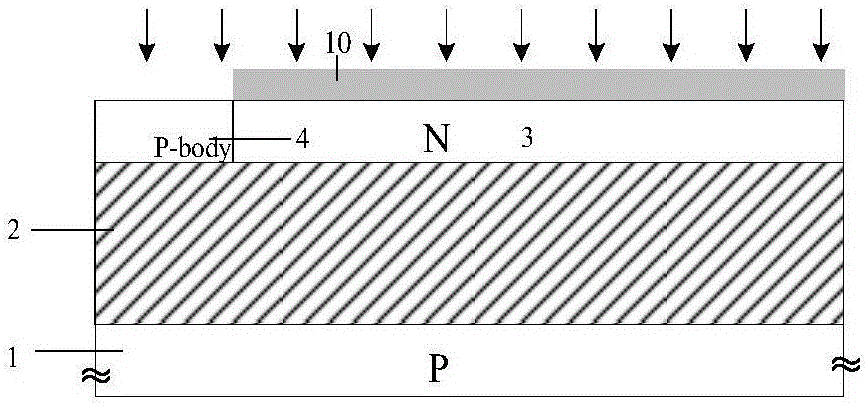

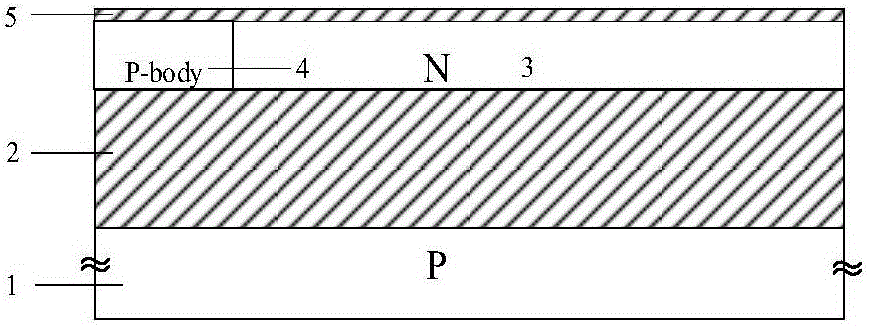

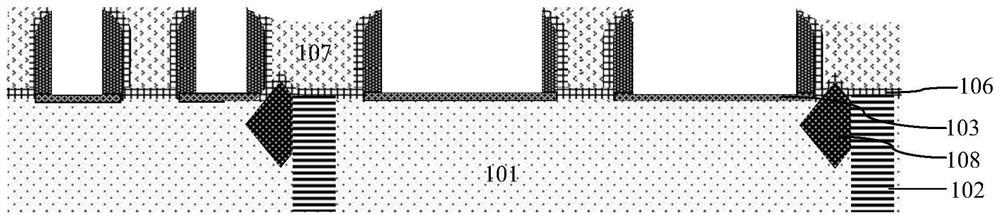

LDMOS device manufacturing method

ActiveCN105304693AEffect on electrical performanceEasy to achieve linear dopingSemiconductor devicesLDMOSElectrical performance

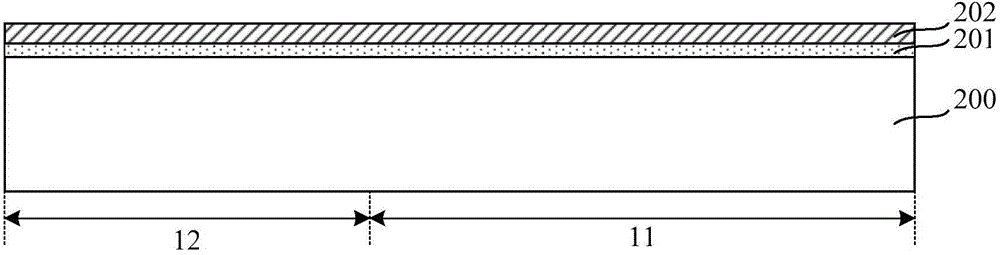

The invention belongs to the semiconductor technology, and particularly relates to an LDMOS device manufacturing method. The LDMOS device manufacturing method mainly comprises steps: a semiconductor active layer of a first conductive type grows on the upper surface of a semiconductor substrate of a second conductive type; bonding and stripping are carried out on the upper layer of the semiconductor active layer of the first conductive type to form a dielectric barrier layer, and an auxiliary semiconductor layer is formed on the semiconductor active layer of the first conductive type on the upper surface of the dielectric barrier layer; semiconductor impurities of a second conductive type are injected in the auxiliary semiconductor layer; two ends of the auxiliary semiconductor layer are etched to the surface of the dielectric barrier layer to form a first active region window and a second active region window; a body region is manufactured in the first active region window, and a source metal grows; and a drain contact region is manufactured in the second active region window, and a drain metal grows. The LDMOS device manufacturing method has the beneficial effects that an extended gate can be ensured to be a monocrystalline silicon material, and influences on electrical performance of an extended gate device by a poly gate can be avoided.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

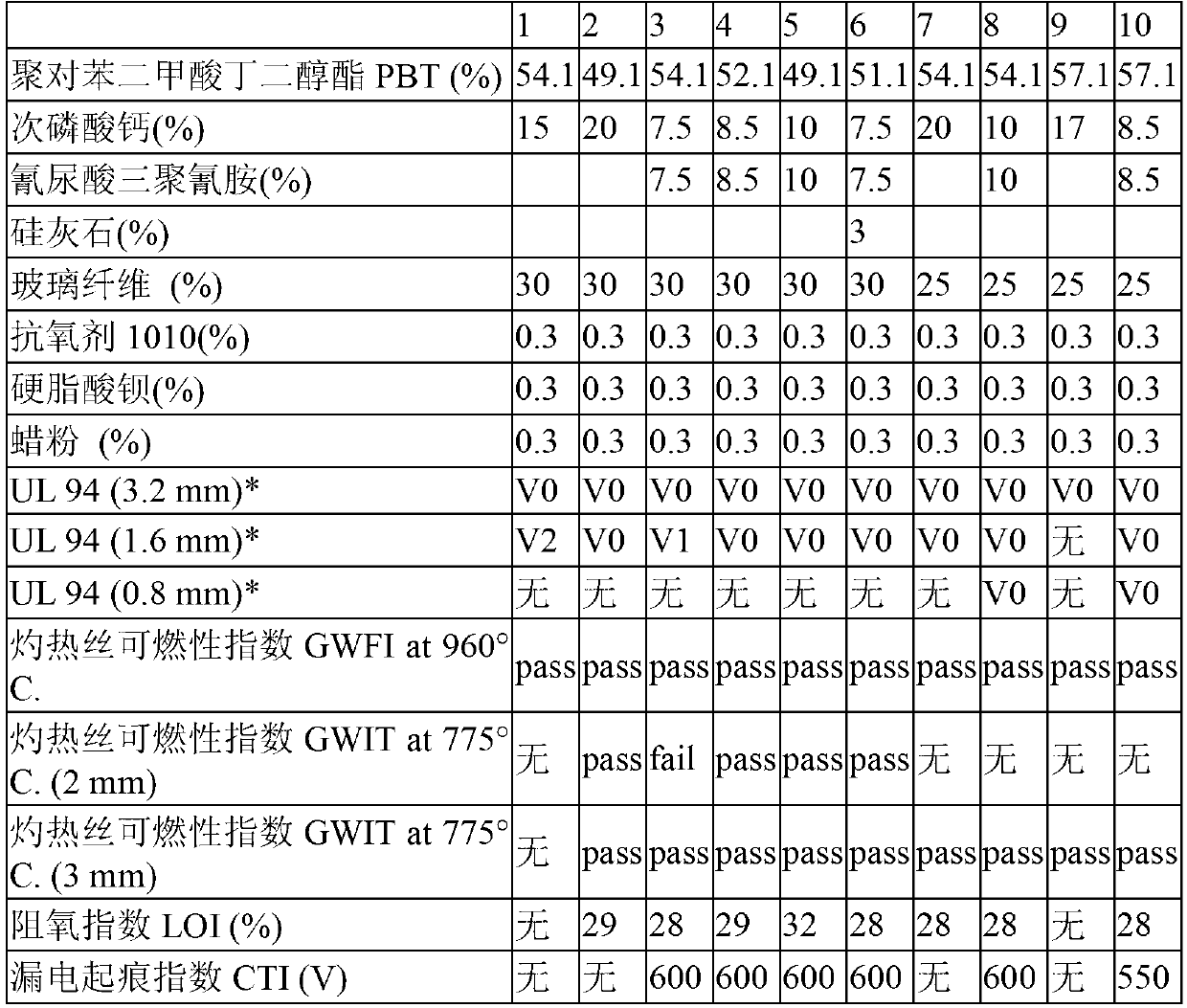

Halogen-free environment-friendly flame-retardant modified thermoplastic polyester resin

InactiveCN103102658AEffect on electrical performanceDoes not affect decompositionChemistryProcessing aid

The invention discloses a halogen-free environment-friendly flame-retardant modified thermoplastic polyester resin. The thermoplastic polyester resin comprises the following components in parts by weight: 5-95% of polyester resin, 0.1-30% of calcium hypophosphite, 0-10% of halogen-free flame-retardant additive, 0.5-10% of one or more of processing aid, thermal and process stabilizing agent, ultraviolet stabilizer, antidripping agent, pigment, releasing agent, rubber elastomeric polymer and nucleating agent and 0-50% of inorganic filler. The product provided by the invention has favorable halogen-free flame-retardant performance, particularly favorable thermal resistance at 775 DEG C under the length of 1.6mm and the thickness of 0.8mm according to the UL94 standard, excellent mechanical property, particularly good impact strength and elasticity modulus and favorable stretchability and electrical property and can pass a CTI (Computer Telephony Integration) value under the condition of 600V.

Owner:天津然跃环保创新科技有限公司

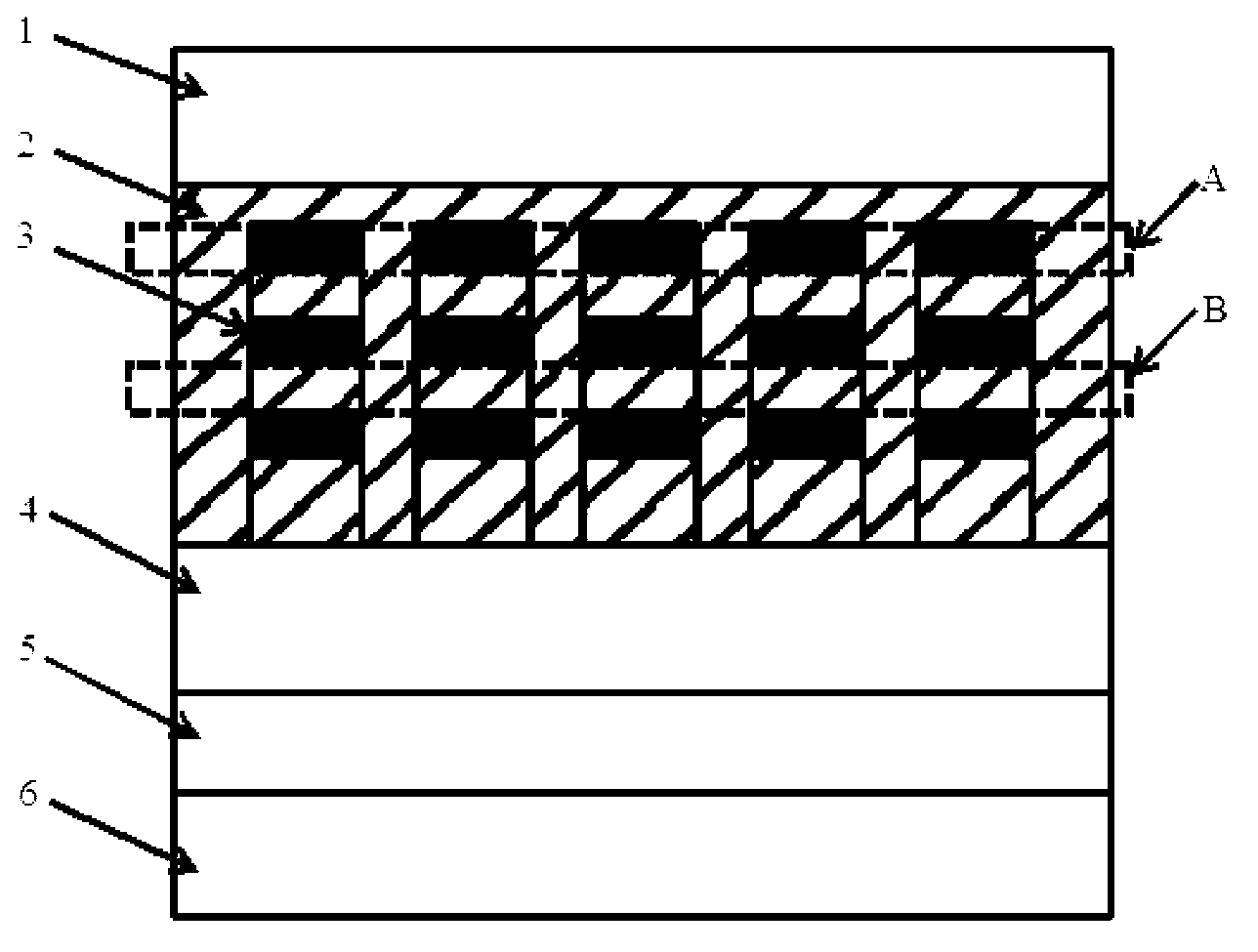

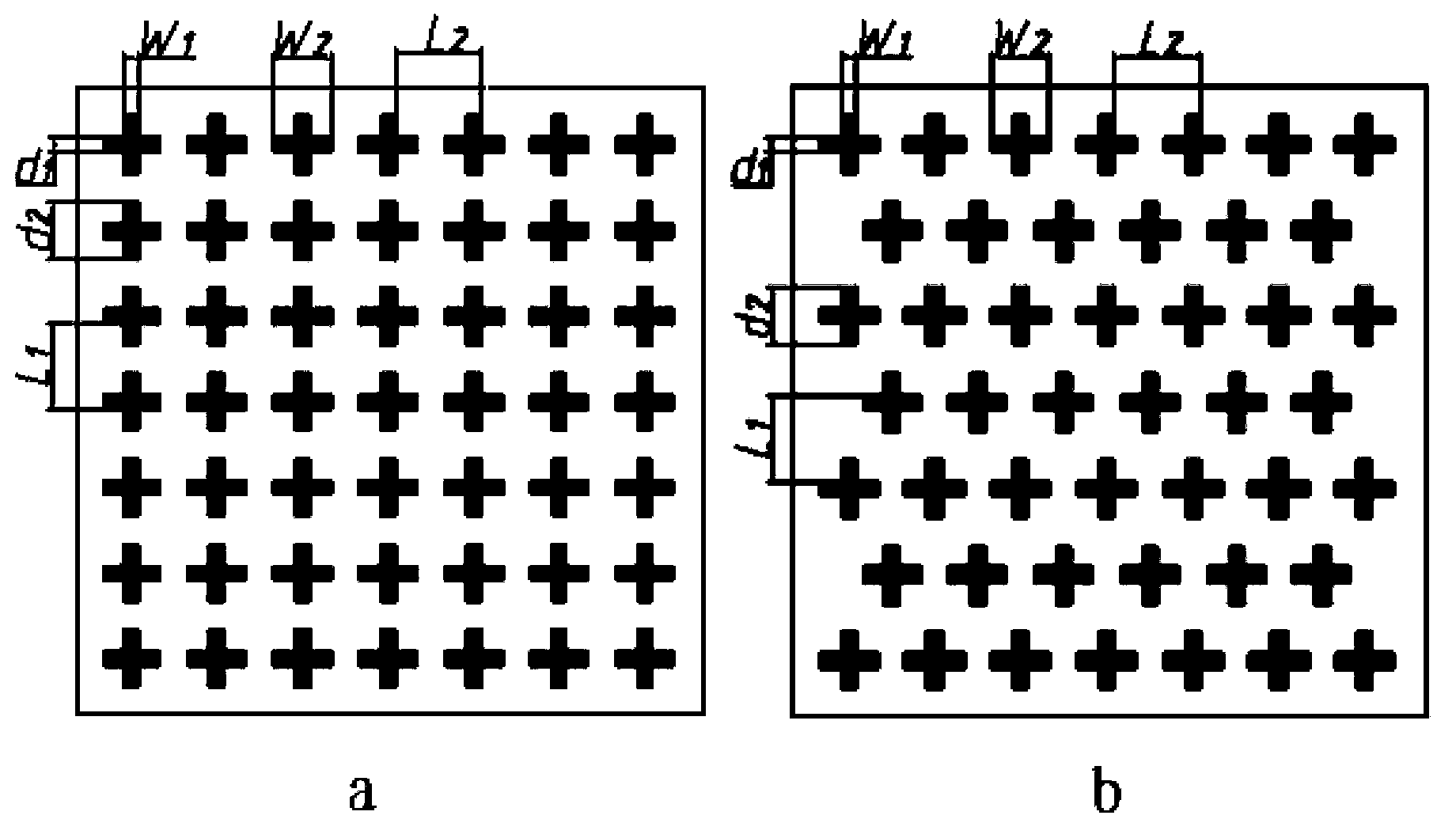

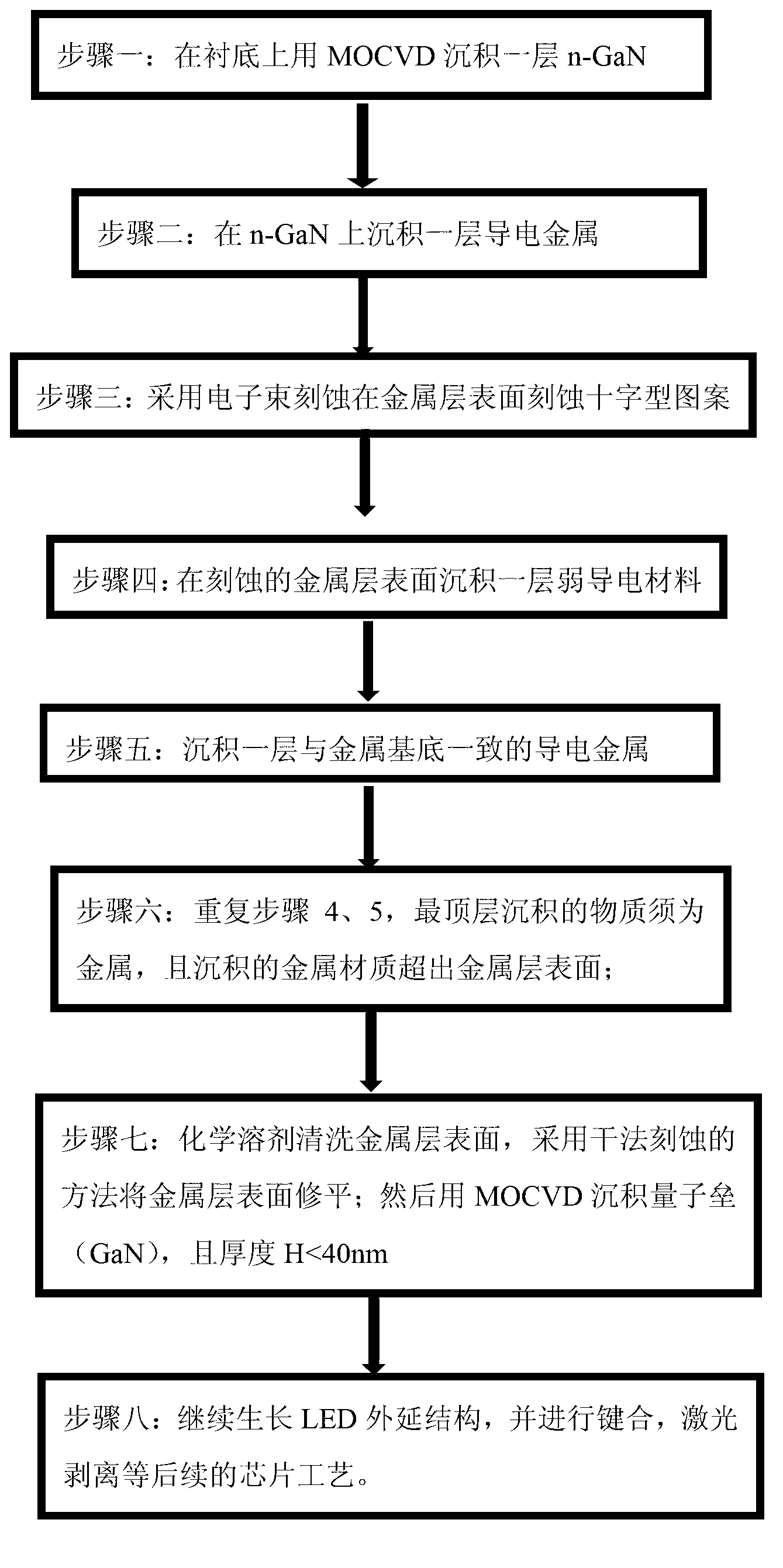

LED photonic crystal containing left-handed material and preparation method

ActiveCN103227254AHigh preparation precisionImprove and tune performanceSemiconductor devicesSurface plasmon polaritonBand gap

The invention relates to an LED (light emitting diode) photonic crystal containing a left-handed material and a preparation method. The LED photonic crystal is characterized in that (1), the photonic crystal is formed by arraying a right-handed material and the left-handed material alternately; (2), gaps in a left-handed material layer are in Swiss cross structures, can be arrayed rectangularly or triangularly, and are filled with weak conducting materials; (3), a substrate of the photonic crystal is made of conducting metal; and (4), the thickness of a quantum barrier GaN between the photonic crystal and an active layer is less than 40nm. According to the LED photonic crystal and the preparation method, the LED photonic crystal is prepared by combining higher-accuracy technologies such as electron beam etching, electron beam evaporation, PECVD (plasma enhanced chemical vapor deposition), and dry etching, so that a surface plasmon enhancement effect can be generated to couple out an evanescent wave in the active layer, and wider photonic band gaps can be generated; the luminous wavelength and a light emitting angle are controlled better; and the luminous efficiency and the light emitting power of an LED are improved and increased.

Owner:XI AN JIAOTONG UNIV

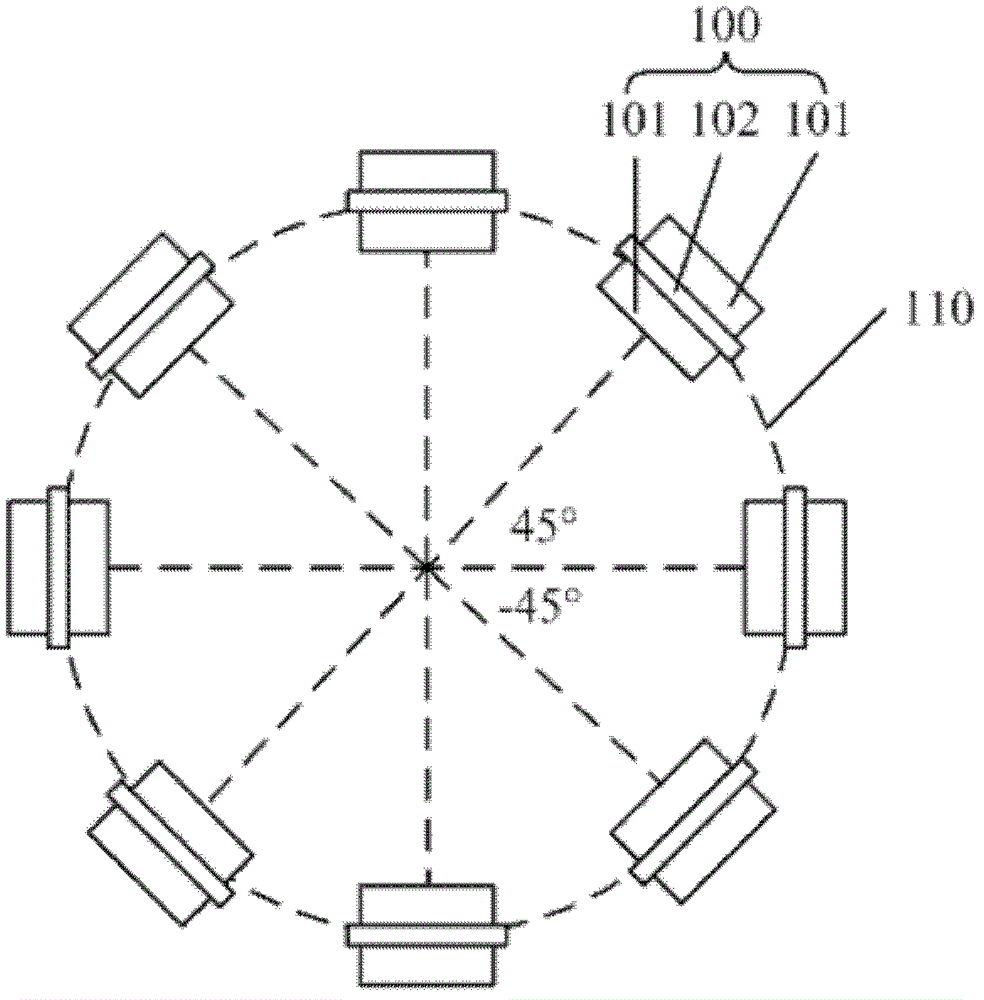

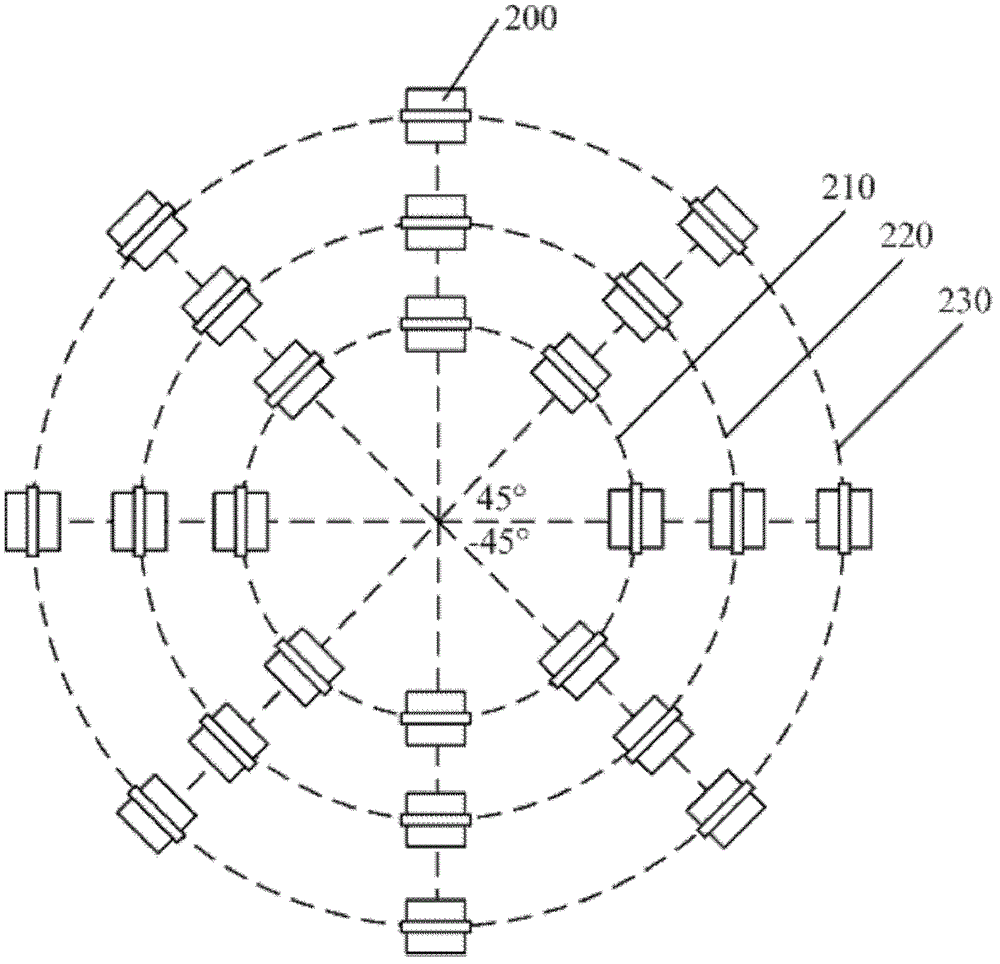

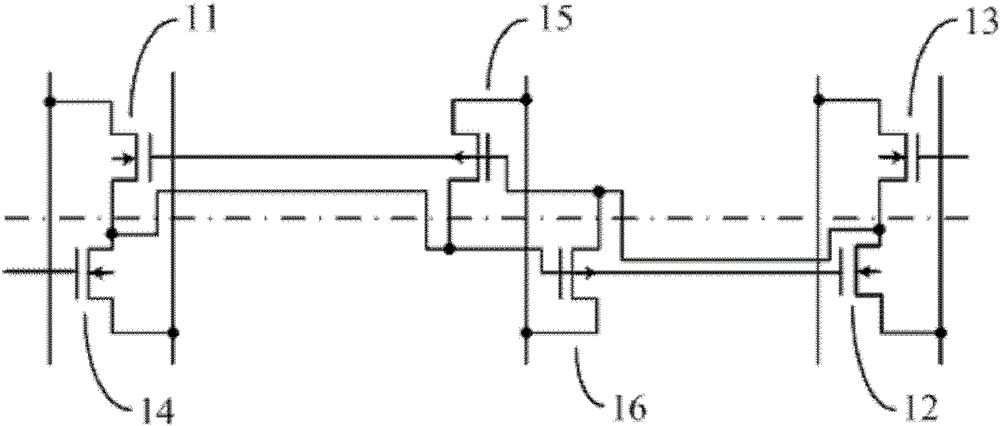

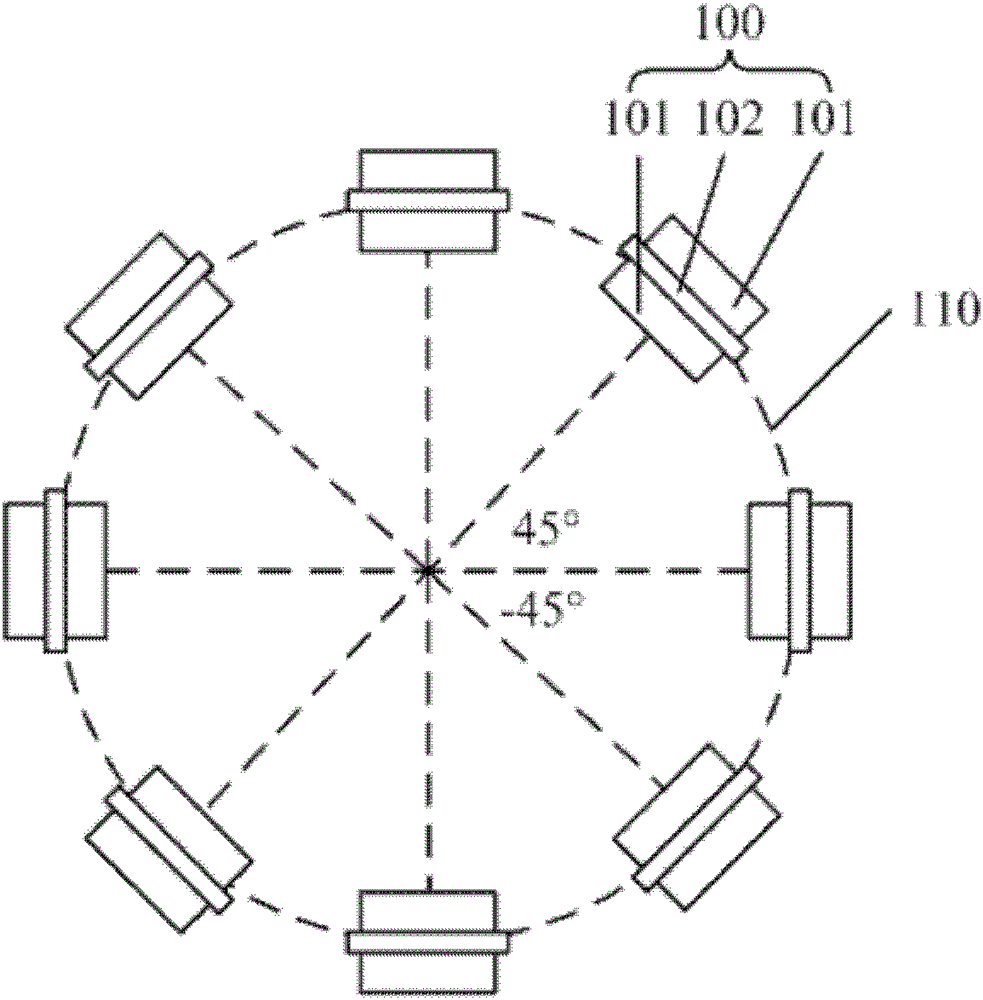

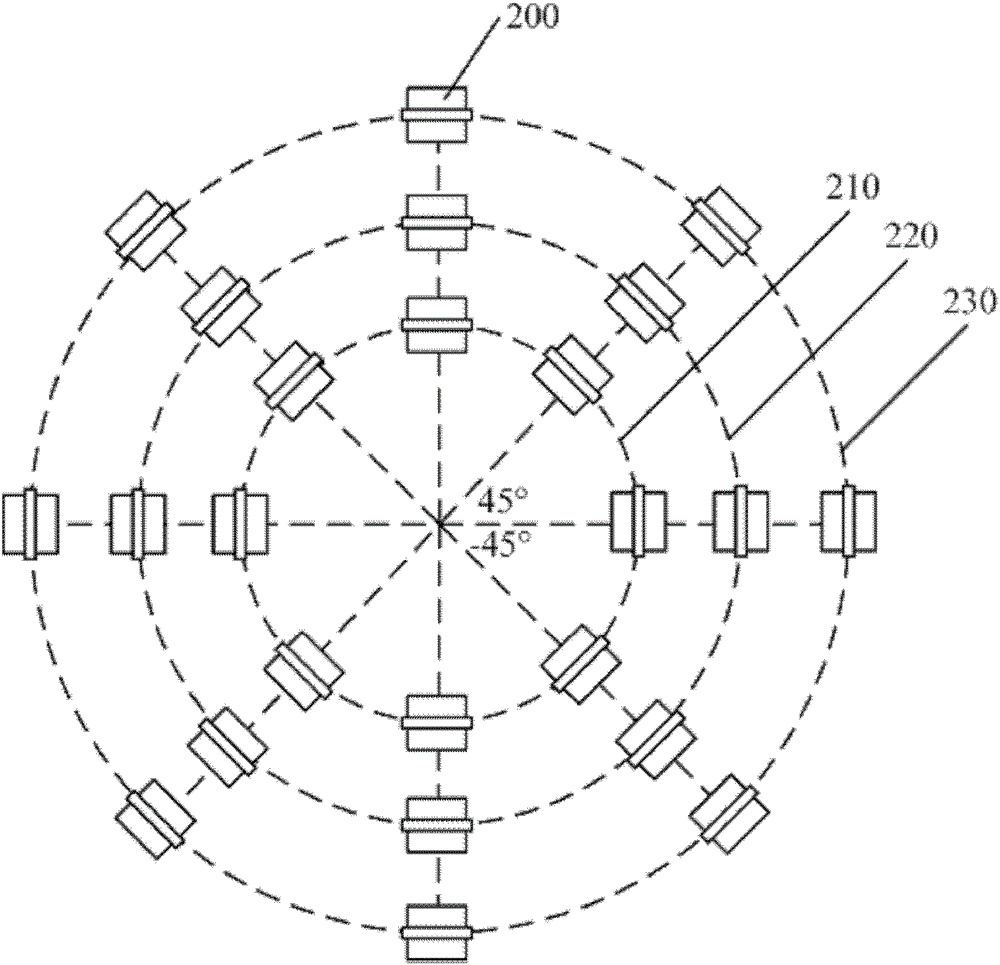

Detection structure and detection method of semiconductor device mismatch characteristic

ActiveCN103066060AEffect on electrical performanceJudgment of differences in the degree of influence of mismatch characteristicsSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipIntegrated circuit layout

Disclosed are a detection structure and a detection method of a semiconductor device mismatch characteristic. The detection structure of the semiconductor device mismatch characteristic comprises a semiconductor substrate, a plurality of identical semiconductor devices which are located on the surface of the semiconductor substrate and at least one circular ring which is surrounded by the semiconductor devices in an equal angle mode. In the detection structure of the semiconductor device mismatch characteristic, the semiconductor devices have different laying angles, by comparing the difference value or the standard deviation of the semiconductor devices with the different laying angles, the influence of the different laying angles on a semiconductor silicon wafer on the mismatch characteristic of the semiconductor devices is judged, and thereby the influence of manufacturing technique and semiconductor chips on the electrical parameter mismatch of the semiconductor devices are obtained, great help about the best locating place of the semiconductor devices is offered for designers in the designing process of an integrated circuit board, and moreover, reference is offered for reducing the mismatch characteristic of a metal oxide semiconductor (MOS) transistor caused in the manufacturing process.

Owner:SEMICON MFG INT (SHANGHAI) CORP

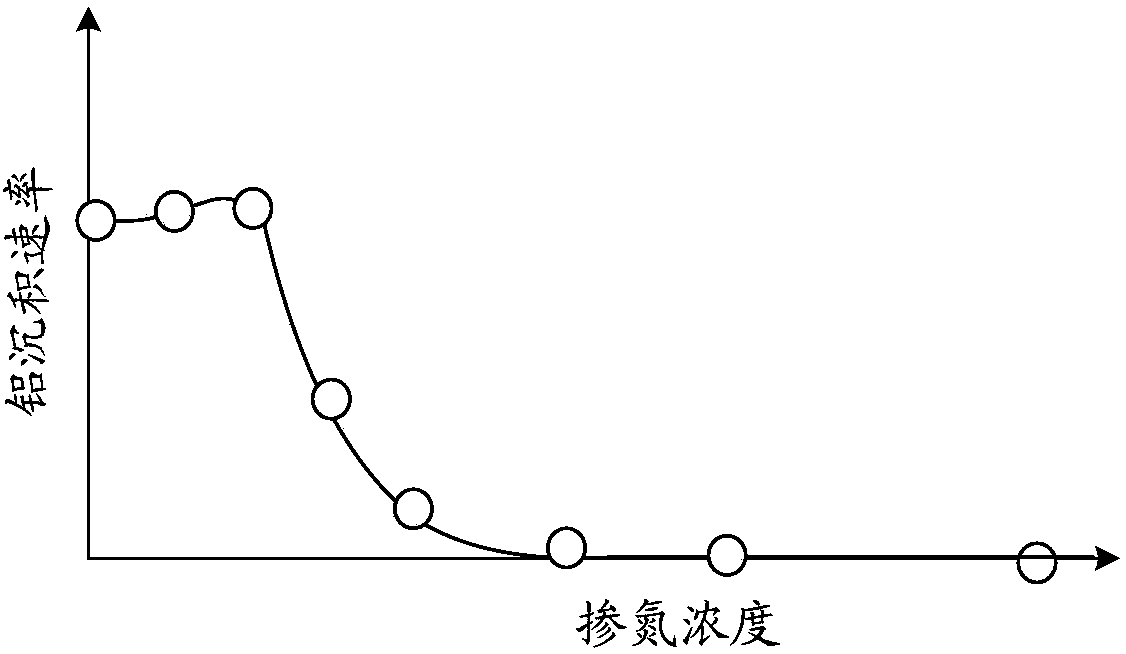

Semiconductor structure and forming method therefor

ActiveCN107919323AReduce sedimentationAvoiding High Threshold Voltage ProblemsTransistorSemiconductor/solid-state device manufacturingSemiconductor structureWork function

The invention provides a semiconductor structure and a forming method therefor, and the method comprises the steps: providing a substrate which comprises a first region for forming a first transistorand a second region for forming a second transistor, wherein the trench length of the first transistor is less than the trench length of the second transistor; forming an interlayer dielectric layer on the substrate; forming a first opening and a second opening in the interlayer dielectric layer; forming gate medium layers on the bottom and side walls of a first opening and the bottom and side walls of the second opening; forming a first nitrogenous layer on a gate medium layer of the second region; and forming work function layers containing aluminium on the gate medium layer of the first region and the first nitrogenous layer. According to the invention, the first nitrogenous layer is formed, thereby reducing the deposition capability of aluminium atoms in the second opening, so as to solve a problem that the inconsistency of the longitudinal width ratios of the openings causes the inconsistency of the deposition capability of aluminium atoms, enable the thickness values of the workfunction layers of the first and second transistors to be approximately equal and enable the aluminium contents to be approximately equal.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Semiconductor structure and forming method therefor

ActiveCN105762103AAvoid enteringImprove breakdown voltageTransistorSemiconductor/solid-state device manufacturingSemiconductor structureIon implantation

The invention discloses a semiconductor structure and a forming method therefor. The method comprises the steps: providing a substrate; forming an isolation structure on the substrate, wherein the isolation structure is used for dividing the substrate into a first region and a second region; forming a first well region in the first region of the substrate; forming a second well region in the second region of the substrate, wherein the doping type of the second well region is different from the doping type of the first well region; forming a pseudo grid structure located on the isolation structure; taking the pseudo grid structure as a mask, and forming a second heavily-doped region in the second well region, wherein the doping type of the second heavily-doped region is the same as the doping type of the second well region; taking the pseudo grid structure as the mask, and forming a first heavily-doped region in the first well region, wherein the doping type of the first heavily-doped region is the same as the doping type of the first well region. The method forms the pseudo grid structure on the isolation structure at the junction of the first and second regions, and the pseudo grid structure can serve as an ion injection mask during the forming of the doped regions, thereby preventing doping ions in the heavily-doped regions from entering the adjacent well region or heavily-doped region, and improving the breakdown voltage of an adjacent device.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

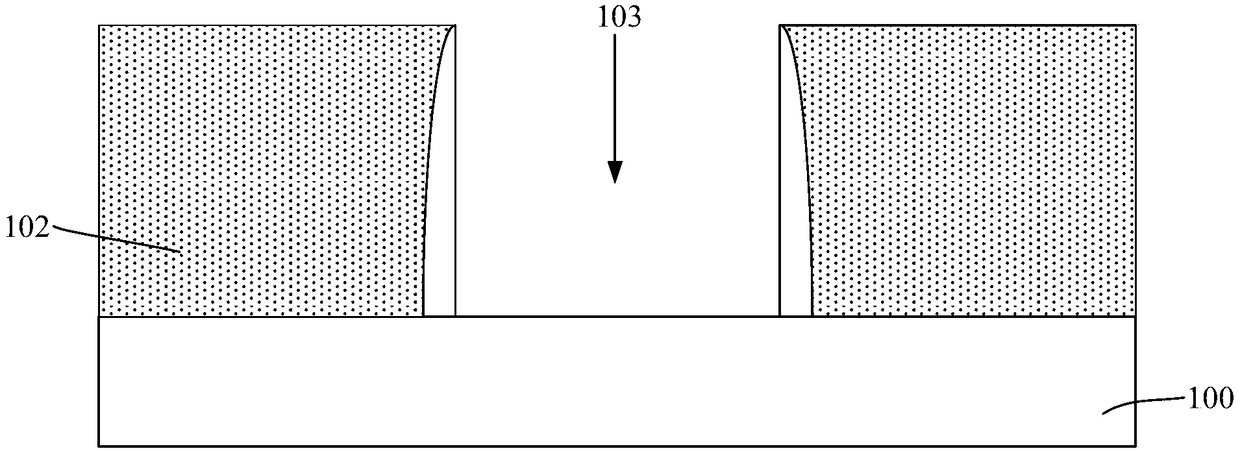

Formation method of semiconductor device

ActiveCN105719971AReduce width sizeImprove electrical isolationSemiconductor/solid-state device manufacturingEngineeringSemiconductor

The invention provides a formation method of a semiconductor device. The formation method of a semiconductor device comprises the steps: providing a substrate with isolation structures; forming a gate structure on the surface of part of the substrate between the adjacent isolation structures; forming a groove exposing the side wall of the isolation structure in the substrate at two sides of each gate structure; nitriding the side wall of the exposed isolation structure, and forming an anti-corrosion layer on the surface of the side wall of the isolation structure; after forming the anti-corrosion layer, cleaning the surface of the bottom and the side wall of the groove; and forming a stress layer filling the groove. The formation method of a semiconductor device can prevent cleaning from etching the isolation structure so as to enable the isolation structure to maintain good shape and provide good interface performance for forming the stress layer, and can enable the isolation structure to maintain good electrical isolation performance and can optimize the electrical properties for the formed semiconductor device.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Semiconductor structure and forming method thereof

ActiveCN105655253AImprove the immunityAvoid failureSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSemiconductor structure

The invention provides a semiconductor structure and a forming method thereof. The forming method of the semiconductor structure comprises the following steps: a semiconductor substrate comprising an active region structure and a shallow trench isolation structure is provided; a gate structure and spacers on the sidewalls of the gate structure are formed on the surface of the semiconductor substrate, the gate structure comprises a gate dielectric layer on the surface of the semiconductor substrate, the gate dielectric layer comprises a dielectric layer on the surface of the semiconductor substrate and a metal layer on the surface of the dielectric layer, and part of the gate structure and part of the spacers are disposed on the surface of the shallow trench isolation structure; and part of the metal layer on the shallow trench isolation structure is modified to make the part of the metal layer converted into a protective layer. The protective layer protects the gate dielectric layer on the surface of the active region structure from being corroded and consumed by acid, and failure of semiconductor devices is avoided.

Owner:SEMICON MFG INT (SHANGHAI) CORP

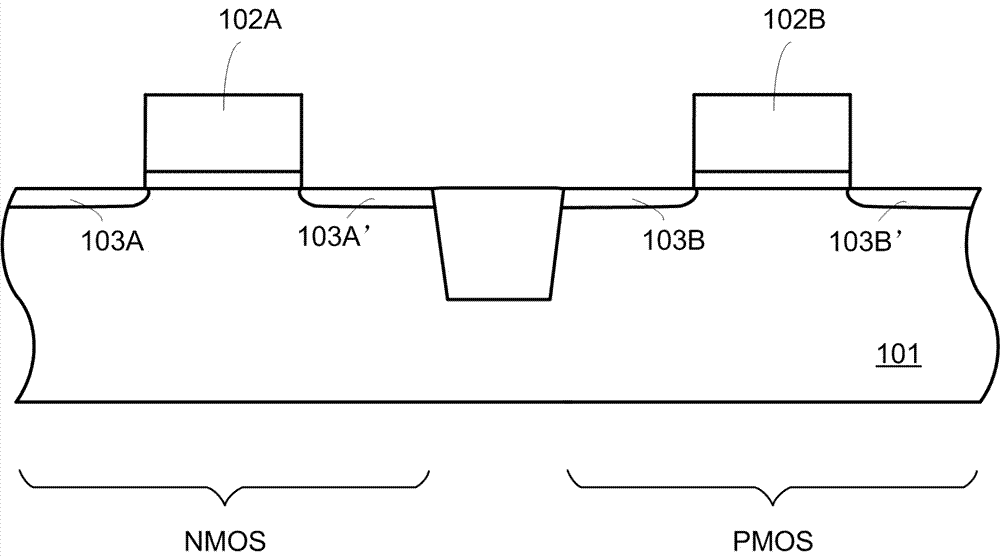

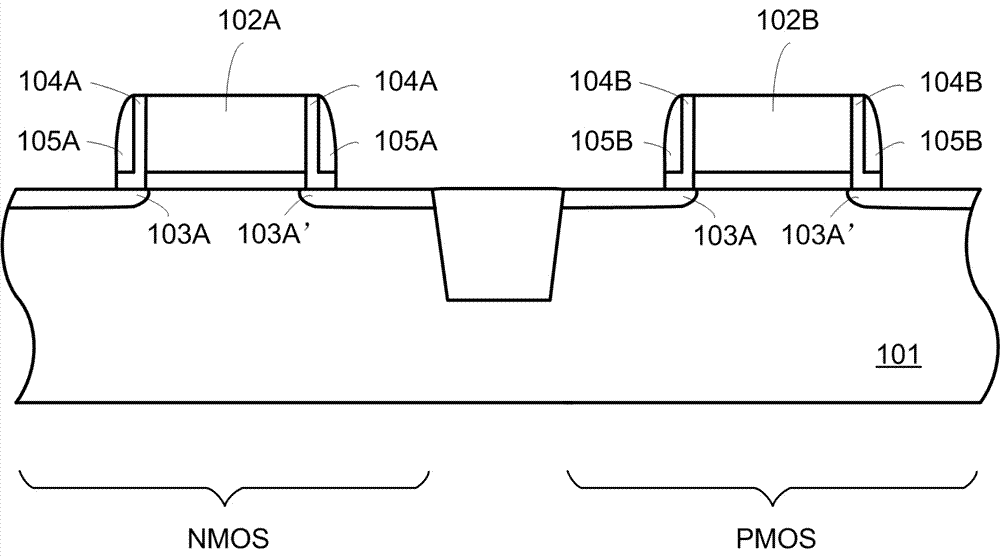

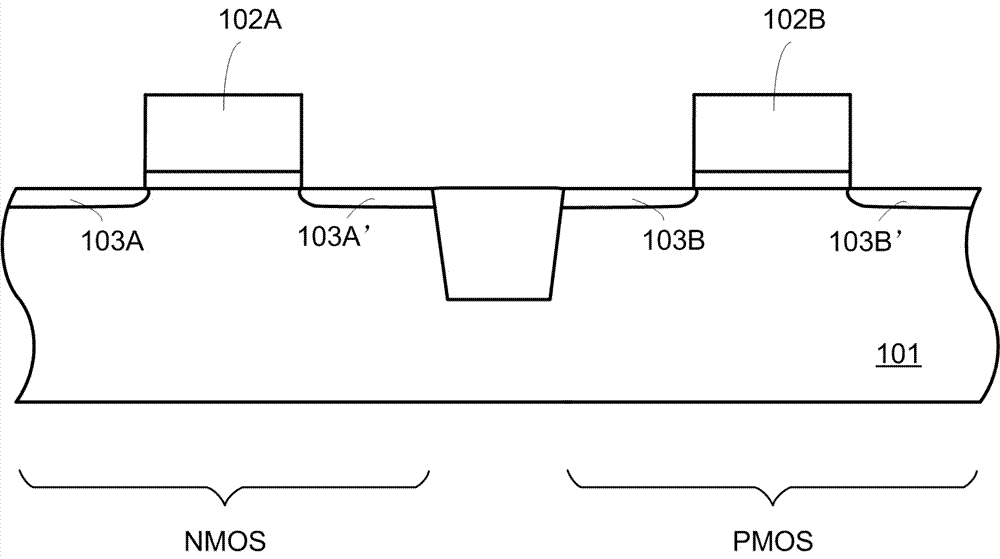

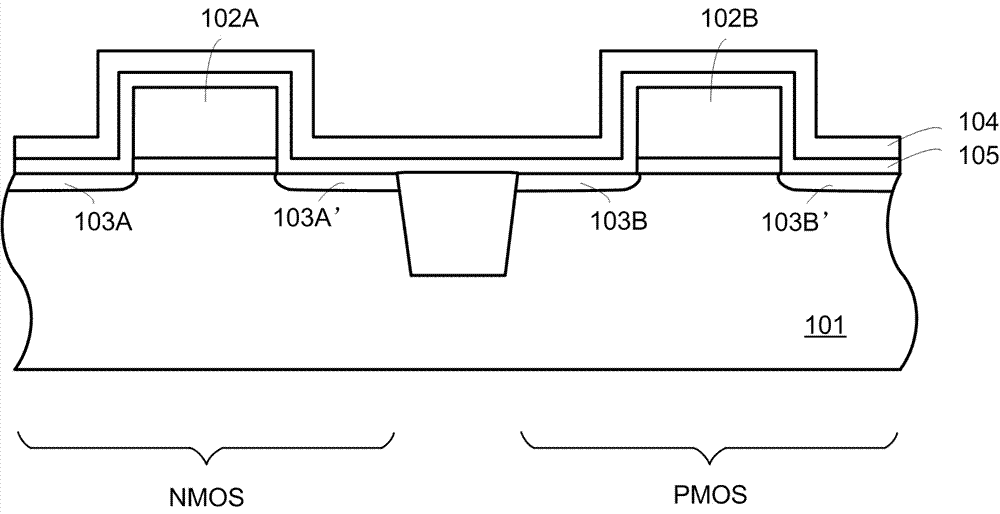

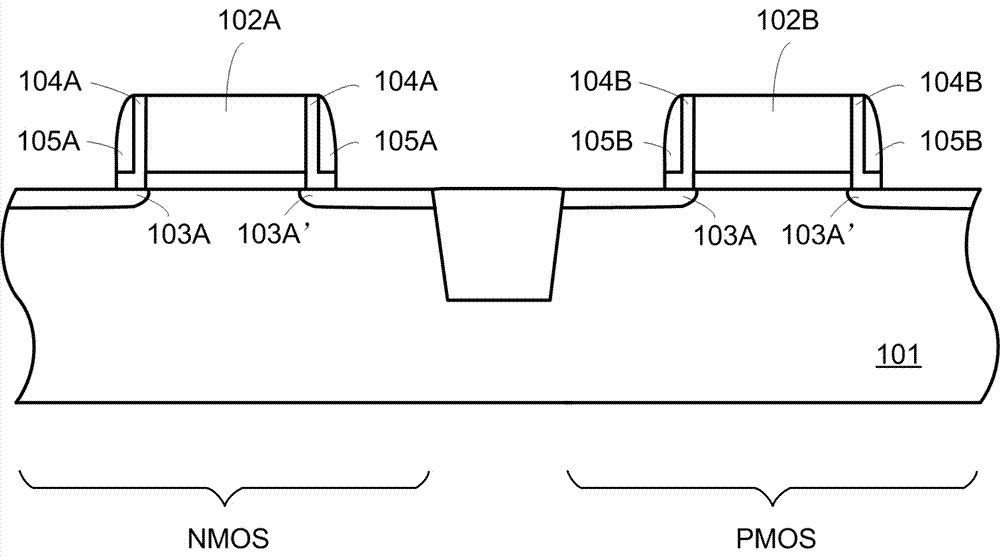

Manufacturing method of semiconductor devices

InactiveCN102956558AImprove electrical performanceEffect on electrical performanceSemiconductor/solid-state device manufacturingPower semiconductor deviceCharge carrier mobility

The invention discloses a manufacturing method of semiconductor devices. The manufacturing method includes steps of a), providing a semiconductor substrate with an NMOS(N-channel metal oxide semiconductor) transistor and a PMOS(P-channel metal oxide semiconductor) transistor; b), forming a stress capping layer on the NMOS transistor, the PMOS transistor and the semiconductor substrate; c), doping Ge in the stress capping layer covering the PMOS transistor; and d), annealing. Since the capping layer is formed on the NMOS transistor and the PMOS transistor simultaneously, and stress is released by Ge doped in the stress capping layer covering the PMOS transistor, carrier mobility of trench areas of the NMOS transistor is improved and electrical performance of the NMOS transistor is improved while affection to electrical performance of the PMOS transistor is avoided on the premise of reduction of processing steps. Besides, compared with the prior art, the manufacturing method has the advantages that processing steps are reduced evidently, production cycle is shortened, and running cost is reduced.

Owner:SEMICON MFG INT (SHANGHAI) CORP

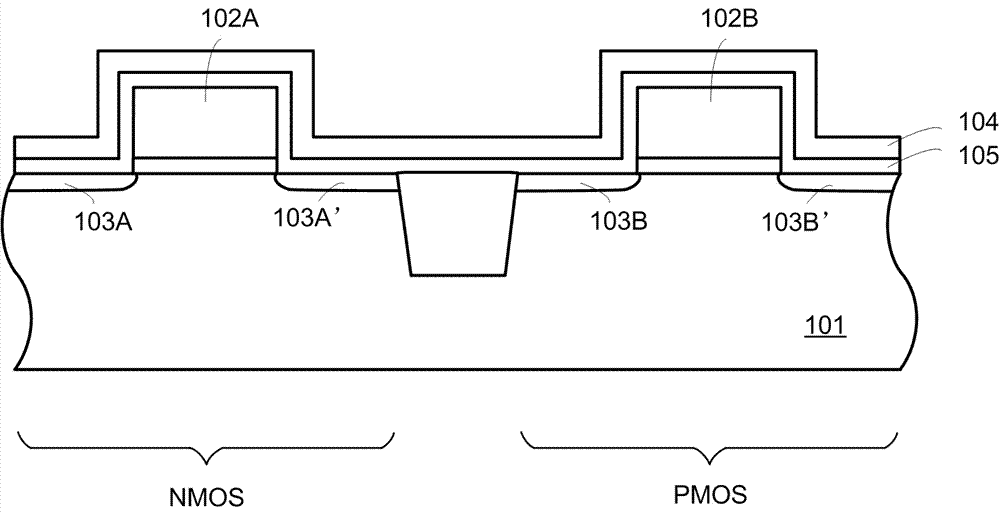

Manufacturing method of semiconductor devices

ActiveCN102956557AReduce process stepsHigh carrier mobilitySemiconductor/solid-state device manufacturingOxide semiconductorPower semiconductor device

The invention discloses a manufacturing method of semiconductor devices. The manufacturing method includes steps of a), providing a semiconductor substrate with a first grid positioned in an NMOS (N-channel metal oxide semiconductor) area and a second grid positioned in a PMOS (P-channel metal oxide semiconductor) area on the semiconductor substrate; b), forming a side-wall oxide layer in the NMOS area and the PMOS area and forming a high-stress nitride layer on the side-wall oxide layer; c), doping germanium into the high-stress nitride layer in the PMOS area; d), etching the high-stress nitride layer to form side walls on two sides of the first grid and the second grid; and e), annealing. On the premise of reduction of processing steps, carrier mobility of trench areas of the NMOS area is improved, electrical performance of NMOS devices is improved, while affection to electrical performance of the PMOS area is avoided. Besides, since separated etching to the high-stress nitride layer is avoided in the method, thickness consistence of the high-stress nitride layers in the NMOS area and the PMOS area is guaranteed, and adverse affection to the subsequent process is avoided.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Formation method of semiconductor structure

ActiveCN108074801AReduce the equivalent gate oxide thicknessImprove interface performanceSemiconductor/solid-state device manufacturingSemiconductor devicesHigh energyPlasma processing

A formation method of a semiconductor structure comprises the steps of providing a substrate; forming an interface layer on the substrate; and performing a film layer formation process on the substrate for at least one time, and forming a high-k grid dielectric layer on the interface layer, wherein step of the film layer formation process comprises the steps of forming an intermediate high-k griddielectric layer on the interface layer by a chlorine-containing precursor; performing plasma processing on the intermediate high-k grid dielectric layer by employing a hydrogen-containing gas; and forming a grid electrode layer on the high-k grid dielectric layer. After forming the intermediate high-k grid electric layer and under plasmas processing, H atoms with high energy can be absorbed to Climpurity atoms in the intermediate high-k grid dielectric layer, the Cl impurity atoms deviate from a surface of the intermediate high-k grid dielectric layer, so that the content of the Cl impurityatoms in the finally-formed high-k grid dielectric layer is reduced to 0; and moreover, other impurity elements are not introduced, so that the interface performance between the high-k grid electric layer and the interface layer is improved, and the equivalent grid oxygen thickness of the high-k grid electric layer is reduced.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Semiconductor structure and formation method

ActiveCN108155235AWork function value dropsLower threshold voltageSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSemiconductor structure

A semiconductor structure and a formation method are disclosed. The method comprises the following steps of providing a substrate; forming a gate dielectric layer on the substrate; forming a work function layer on the gate dielectric layer; forming an oxide layer on the work function layer; forming a barrier layer on the oxide layer; and forming a metal layer on the barrier layer, wherein the metal layer, the gate dielectric layer, the work function layer, the oxide layer and the barrier layer are used for forming a gate structure. In the invention, the oxide layer is formed between the work function layer and the barrier layer; the oxide layer is a non-crystallizing film and a diffusion capability of diffusible ions in the metal layer is weak in the oxide layer so that the oxide layer canwell block diffusion of the diffusible ions into the work function layer, the work function value of the work function layer can be reduced and the threshold voltage of the formed semiconductor structure can be decreased. Compared with the scheme in which a barrier layer thickness is increased so as to improve a blocking effect, the oxide layer can prevent the increase of the thickness of the barrier layer from adversely affecting the electrical properties of a semiconductor device.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

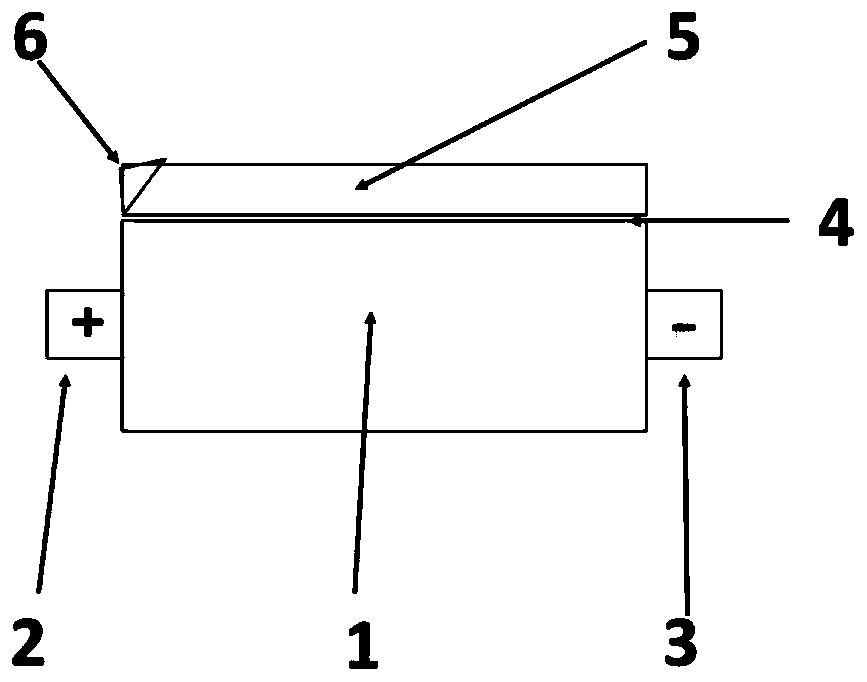

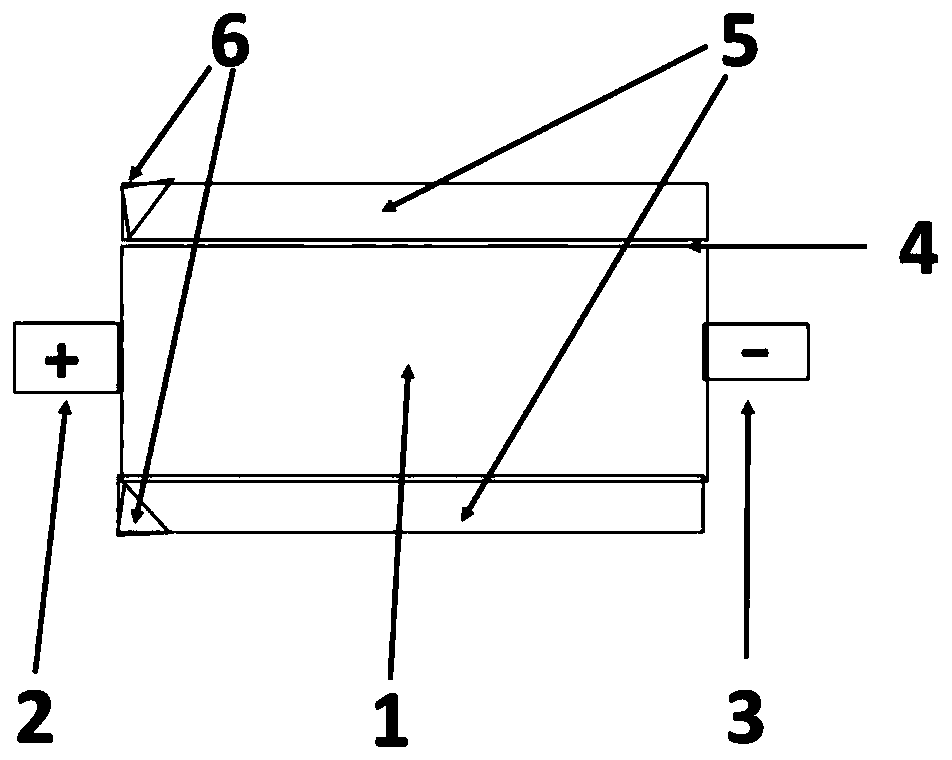

Lithium ion battery and preparation method thereof

InactiveCN111584926AAvoid fireEffect on electrical performanceFinal product manufactureSmall-sized cells cases/jacketsPhysical chemistryEngineering

The invention discloses a lithium ion battery and a preparation method thereof. The lithium ion battery comprises a battery cell body and a flame-retardant safety bag connected with the battery cell body, wherein the flame-retardant safety bag and the battery cell body are isolated from each other through a first sealing area, and the flame-retardant safety bag is filled with flame-retardant liquid. The air bag of the battery cell is refitted into the flame-retardant safety bag, the flame-retardant liquid is added into the flame-retardant safety bag, the flame-retardant safety bag and the battery cell body are separated by the seal on the aluminum-plastic film in a normal state, and the flame-retardant liquid cannot flow into the battery cell body; when gas is generated in the battery cellbody due to high temperature, the internal pressure of the battery cell is increased, and the seal on the aluminum-plastic film is cracked, the flame-retardant liquid in the flame-retardant safety bag can flow into the battery cell body, so that a flame-retardant function is achieved, the battery cell is prevented from being on fire at high temperature, or a battery already on fire is extinguished, and self-extinguishing is realized.

Owner:ZHUHAI COSMX POWER CO LTD

Charge storage unit and image sensor pixel circuit

InactiveCN102544050ANon-volatileReduce power consumptionSolid-state devicesDigital storageControl signalExposure control

The invention provides a charge storage unit, comprising an input end and an output end. The charge storage unit comprises an exposure control transistor, an output transistor and a phase-change resistor, wherein the drain / source electrode of the exposure control transistor is the input end of the charge storage unit, and the drain / source electrode is connected to the first end of the phase-change resistor; the second end of the phase-change circuit is grounded; the drain / source electrode of the output transistor is connected to a co-connecting end of the drain / source electrode of the exposure control transistor with the cathode of a photodiode, the drain / source electrode is the output end of the charge storage unit, and the grid electrode is connected to an output control signal. The charge storage unit has the advantage that a phase-change resistor can be switched between an amorphous state and a crystal state, therefore, optical signals can be stored and voltage signals can be read through externally supplied driving current at last; furthermore, the state of phase-change material is not changed along external temperature or irradiation, and the phase-change material itself has the advantages of no volatility, low energy consumption and rapid reading and writing speed.

Owner:SHANGHAI ADVANCED RES INST CHINESE ACADEMY OF SCI

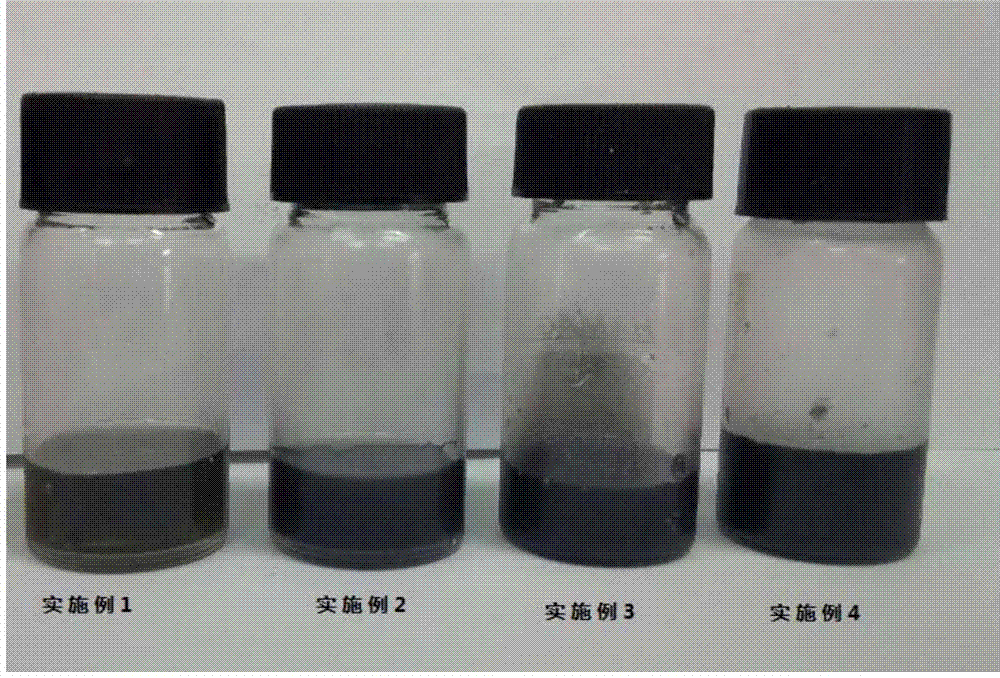

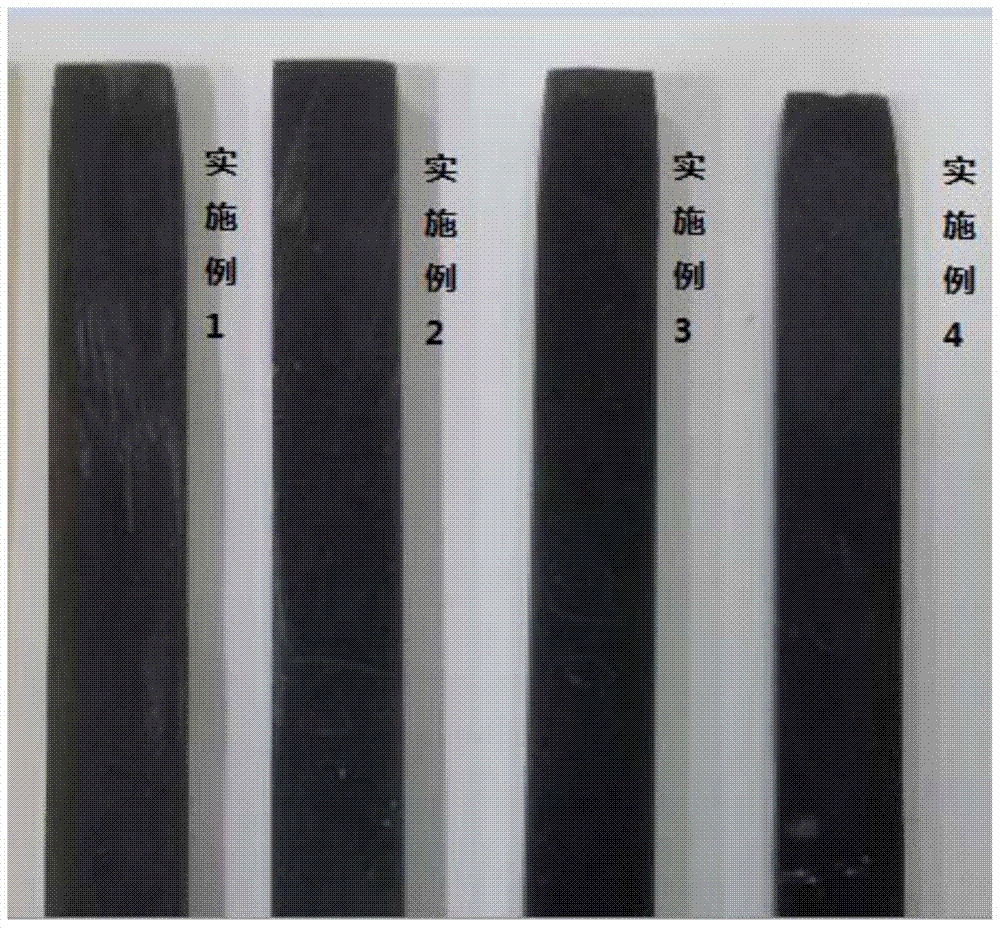

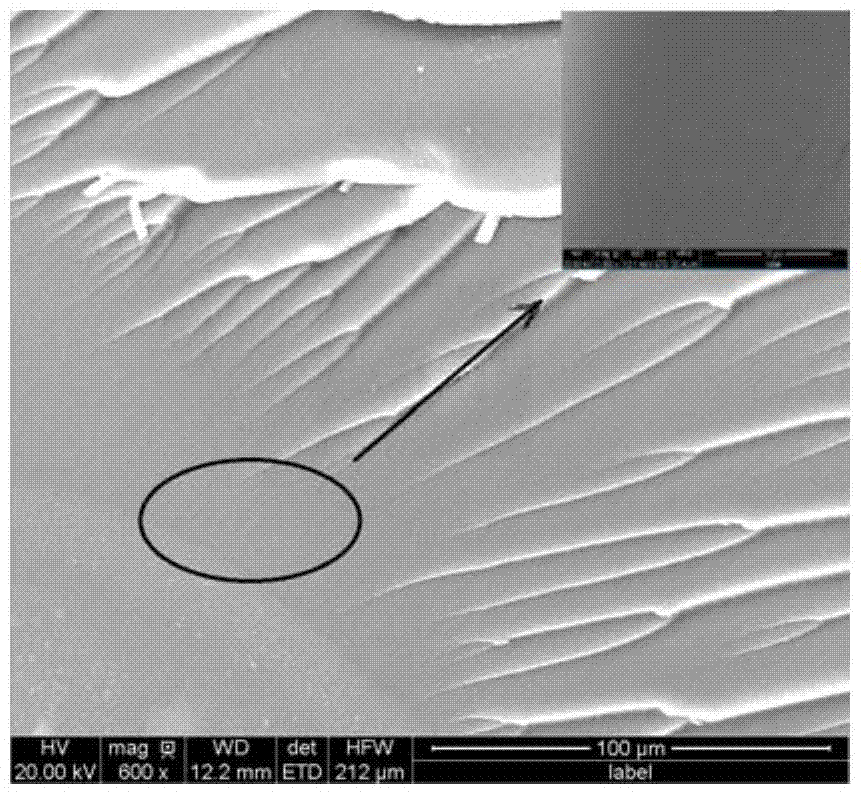

Graphene dispersion method, graphene dispersion system and its preparation method and application

The invention discloses a graphene dispersion method, a graphene dispersion system, a preparation method and application thereof. The present invention mainly forms a stable graphene dispersion by uniformly dispersing graphene in an epoxy diluent, further, uniformly mixing the graphene dispersion with other substrates, such as epoxy resin, to form a graphene dispersion systems, such as graphene-epoxy composites. Wherein the epoxy diluent comprises an epoxy compound directly connected with a cyclic group. The present invention can solve the problem of poor dispersibility of graphene in conventional organic solvents and epoxy resins, especially high-viscosity epoxy resins, and obtain a graphene dispersion system with a large amount of graphene dispersion and good stability, especially with excellent Graphene-epoxy resin composite material with mechanical properties, and the related process route is simple, the reaction conditions are mild, the source of raw materials is abundant, and it is safe and environmentally friendly.

Owner:NINGBO INST OF MATERIALS TECH & ENG CHINESE ACADEMY OF SCI

Detection Structure and Method for Mismatch Characteristics of Semiconductor Devices

ActiveCN103066060BReduced mismatch characteristicsEffect on electrical performanceSemiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceDevice material

Disclosed are a detection structure and a detection method of a semiconductor device mismatch characteristic. The detection structure of the semiconductor device mismatch characteristic comprises a semiconductor substrate, a plurality of identical semiconductor devices which are located on the surface of the semiconductor substrate and at least one circular ring which is surrounded by the semiconductor devices in an equal angle mode. In the detection structure of the semiconductor device mismatch characteristic, the semiconductor devices have different laying angles, by comparing the difference value or the standard deviation of the semiconductor devices with the different laying angles, the influence of the different laying angles on a semiconductor silicon wafer on the mismatch characteristic of the semiconductor devices is judged, and thereby the influence of manufacturing technique and semiconductor chips on the electrical parameter mismatch of the semiconductor devices are obtained, great help about the best locating place of the semiconductor devices is offered for designers in the designing process of an integrated circuit board, and moreover, reference is offered for reducing the mismatch characteristic of a metal oxide semiconductor (MOS) transistor caused in the manufacturing process.

Owner:SEMICON MFG INT (SHANGHAI) CORP

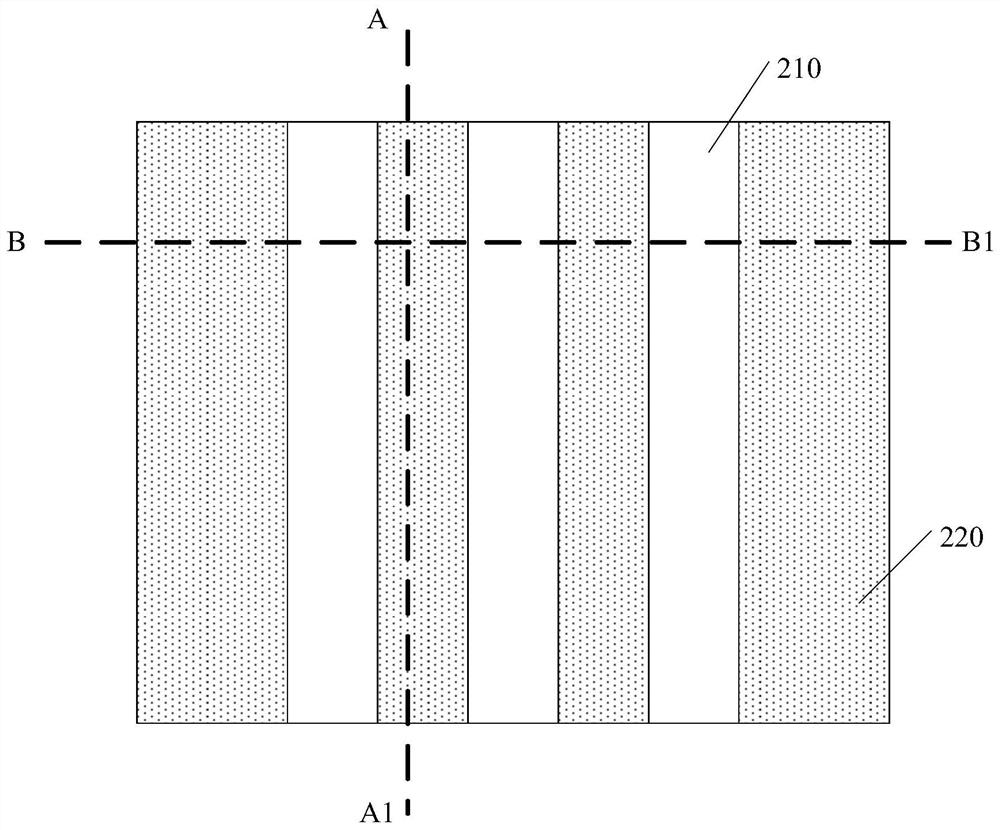

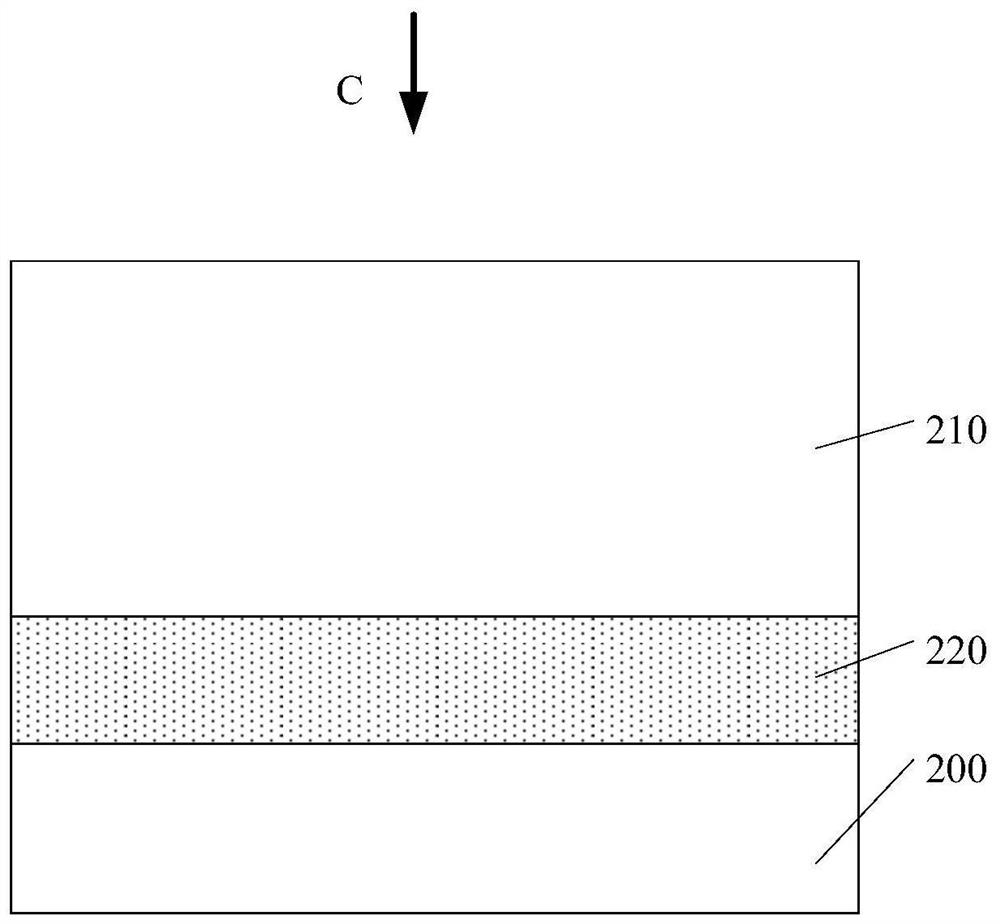

Manufacturing method of interlayer film

ActiveCN108878288BIncrease grinding rateGuaranteed thicknessSemiconductor/solid-state device manufacturingDevice materialMembrane surface

The invention discloses an interlayer film manufacturing method. The interlayer film manufacturing method comprises the following steps: step one, providing a semiconductor substrate on which a pattern structure of a semiconductor device is formed; step two, forming a first insulating layer on the bottom surface and side surfaces of the pattern spacer and the surface of the pattern structure outside the pattern spacer; step three, forming a second insulating layer to completely fill the pattern spacer and extend outside the pattern spacer; and step four: performing chemical mechanical polishing on the second insulating layer and the first insulating layer with the pattern structure as a stop layer, and forming the interlayer film formed by stacking the first and second insulating layers filled in the pattern spacer. The interlayer film manufacturing method can reduce or eliminate dishing defects on the interlayer film surface at the top of the pattern spacer, can improve the flatness of the entire interlayer film, and can improve the electrical properties of semiconductor devices.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

A graphene high-energy battery

ActiveCN107369828BImprove internal conductivityImprove conductivityCell electrodesLi-accumulatorsSolid state electrolyteHigh energy

The invention discloses a high energy graphene battery which comprises a battery anode prepared from graphene wrapped Li0.89Ti0.11FePO4, a solid electrolyte membrane prepared from a Li11Si2PS12 material and a battery cathode prepared from a graphene wrapped silica-based material; the solid electrolyte membrane is arranged between the battery anode and the battery cathode, and the Li11Si2PS12 solid electrolyte membrane is prepared by taking Li2S particles, SiS2 particles and P2S5 particles at a mole mass ratio of 11:4:1 as raw materials, performing grinding and mixing by a high energy ball milling method, preparing sheets by taking molten polyphenyl ether, and performing roll squeezing, hot press molding and chloroform soaking. The prepared graphene battery has the advantages of safety, stability, and high weight energy density, the high pressure is not required in a preparation process, and the preparation cost is low.

Owner:深圳市荣利伟业科技有限公司

A kind of manufacturing method of ldmos device

ActiveCN105047702BEffect on electrical performanceFlexible length adjustmentSemiconductor devicesLDMOSDouble diffusion

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Semiconductor structure and forming method thereof

PendingCN114256347AImprove performanceImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureField effect

The invention discloses a semiconductor structure and a forming method thereof, and the method comprises the steps: providing a substrate which comprises a substrate and a plurality of fin parts which are located on the substrate and are separated from one another, and the materials of the fin parts are provided with first atoms; forming an opening in the fin part; a source-drain doping layer is formed in the opening through the epitaxial growth technology, the source-drain doping layer comprises a seed layer located on the surface of the inner wall of the opening and a body layer located on the surface of the seed layer, first atoms, second atoms and third atoms are arranged in the material of the seed layer, and the first atoms and the second atoms are arranged in the material of the body layer. Therefore, the performance and the reliability of the fin field effect transistor are improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1