A kind of manufacturing method of ldmos device

A manufacturing method and device technology, applied to semiconductor devices, electrical components, circuits, etc., can solve the problems of affecting the electrical performance of extended gates, large polysilicon leakage current, and unsuitable extended gates, so as to ensure reverse blocking characteristics and reduce Production costs and the effect of reducing production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0059] The manufacturing process of the LDMOSFT device in this example is as follows:

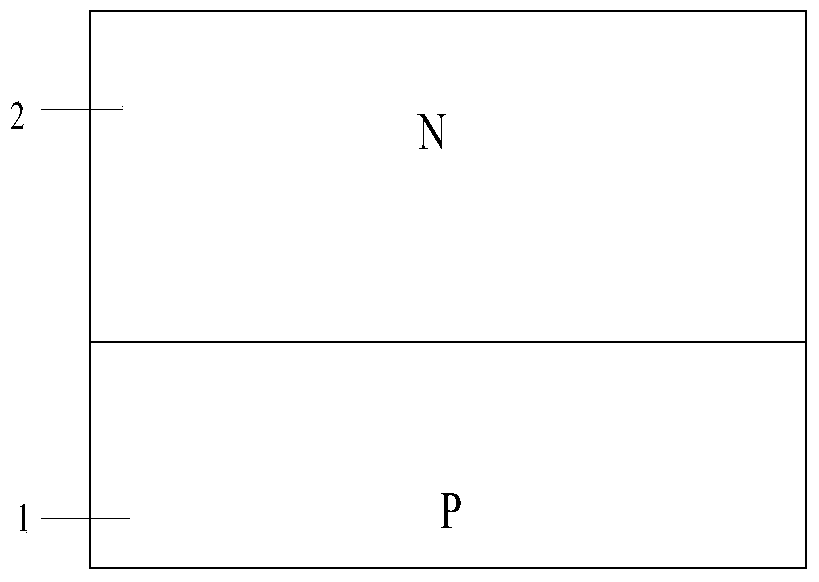

[0060] The first step: prepare a semiconductor material, the semiconductor material includes a substrate layer 1 and an active layer 2, the active layer 2 is located on the substrate layer 1, wherein the conductivity type of the substrate layer 1 is the second conductivity type, there are The conductivity type of the source layer 2 is the first conductivity type (such as figure 1 shown);

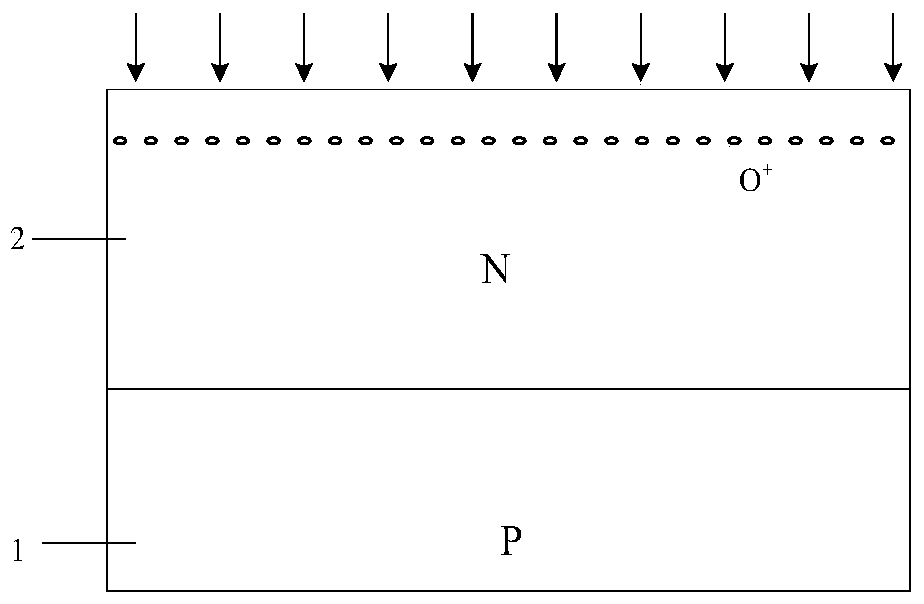

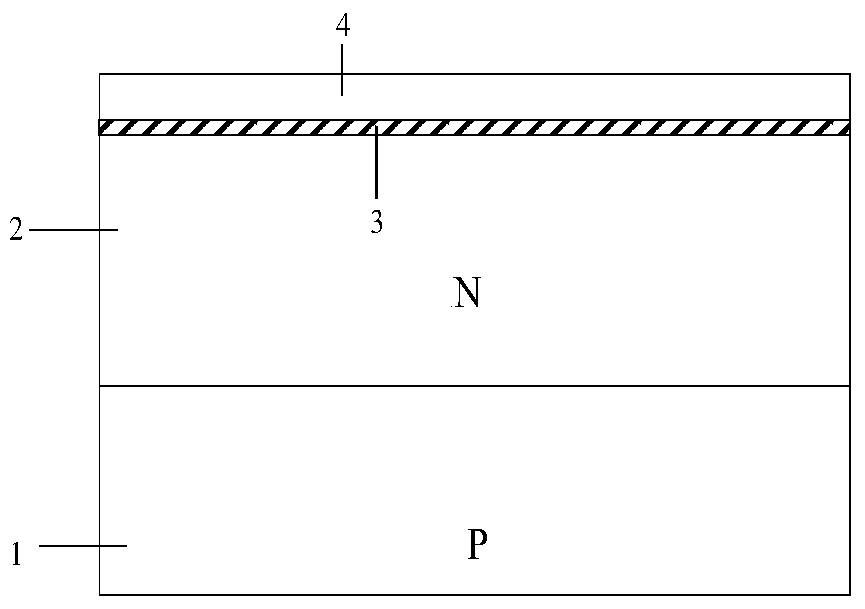

[0061] Step 2: Implant O on the surface of active layer 2 by ion implantation process + Ions (temperature 500-700 degrees, total dose 0.7e18cm -2 ~1.8e18cm -2 , implantation energy 70~200keV), form O in the active layer 2 + ionic layer (such as figure 2 shown); the annealing process is used to make the implanted ions react with the active layer material to form 80-200nm SiO 2 Isolation layer 3, SiO 2 An auxiliary semiconductor layer 4 (eg image 3 shown);

[0062] The third step: using ion impla...

Embodiment 2

[0069] The difference between this example and Example 1 is that the semiconductor material prepared in the first step also includes:

[0070] A dielectric buried layer 10, the dielectric buried layer 10 is located between the second conductivity type semiconductor substrate 1 and the first conductivity type semiconductor active layer 2 (such as Figure 10 shown). Figure 11 Shown is the complete LDMOS device fabricated.

Embodiment 3

[0072] The difference between this example and Example 1 lies in that the ions implanted on the upper layer of the semiconductor active layer 2 of the first conductivity type are N+.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More