Patents

Literature

110results about How to "Reduce process difficulty" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Subcritical liquid extraction device and subcritical liquid extraction method of active ingredients of natural products

InactiveCN101642632AHigh degree of automationReduce process difficultySolid solvent extractionSolventPressure feedback

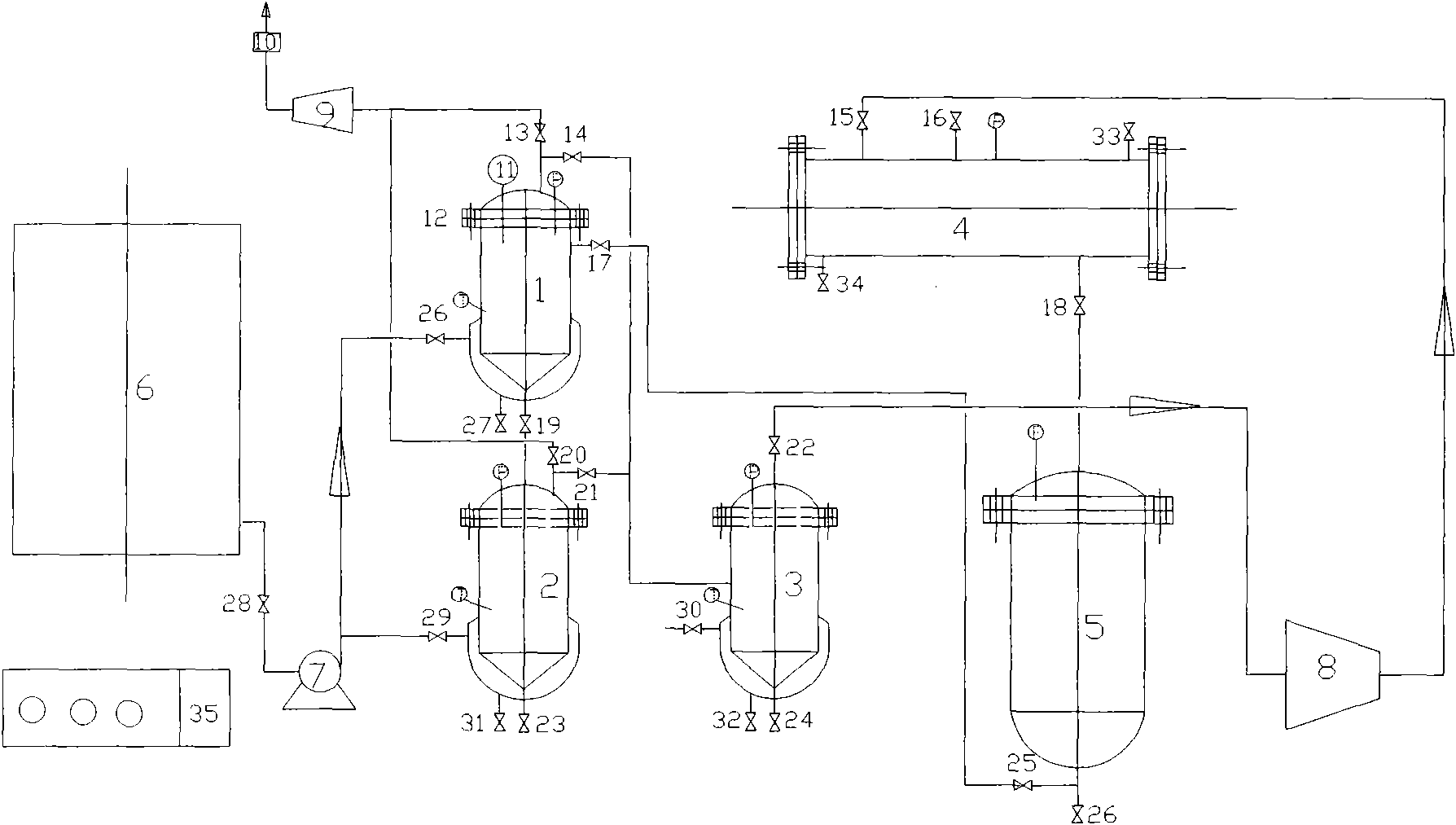

The invention provides a subcritical liquid extraction device and a subcritical liquid extraction method of active ingredients of natural products, relating to a device and a method for extracting active ingredients of natural products. The device comprises a control system part and a leaching system part, wherein the leaching system part comprises an extraction tank 1, an evaporating tank 2, a buffer tank 3, a condenser 4, a solvent tank 5, an ultrasound generating device 11, a vacuum pump 9, a fire arrester 10, a compressor 8, a hot water pump 7 and a hot water box 6; the control system partcomprises a leaching temperature controller, a leaching time controller, a leaching frequency controller, a material dissolving ratio controller, an exsolution temperature regulation controller, an exsolution pressure feedback controller, an electric appliance controller of the device and an excess-temperature excess-pressure leaking alarm. The method can select different subcritical extraction media according to different extraction products, combines a subcritical liquid extraction technology and an ultrasonic extraction technology to increase extraction rate and reduce extraction time andis a new high-efficiency low-consumption environment-friendly technology for extracting active ingredients of natural products.

Owner:HENAN YALINJIE BIOLOGICAL TECH

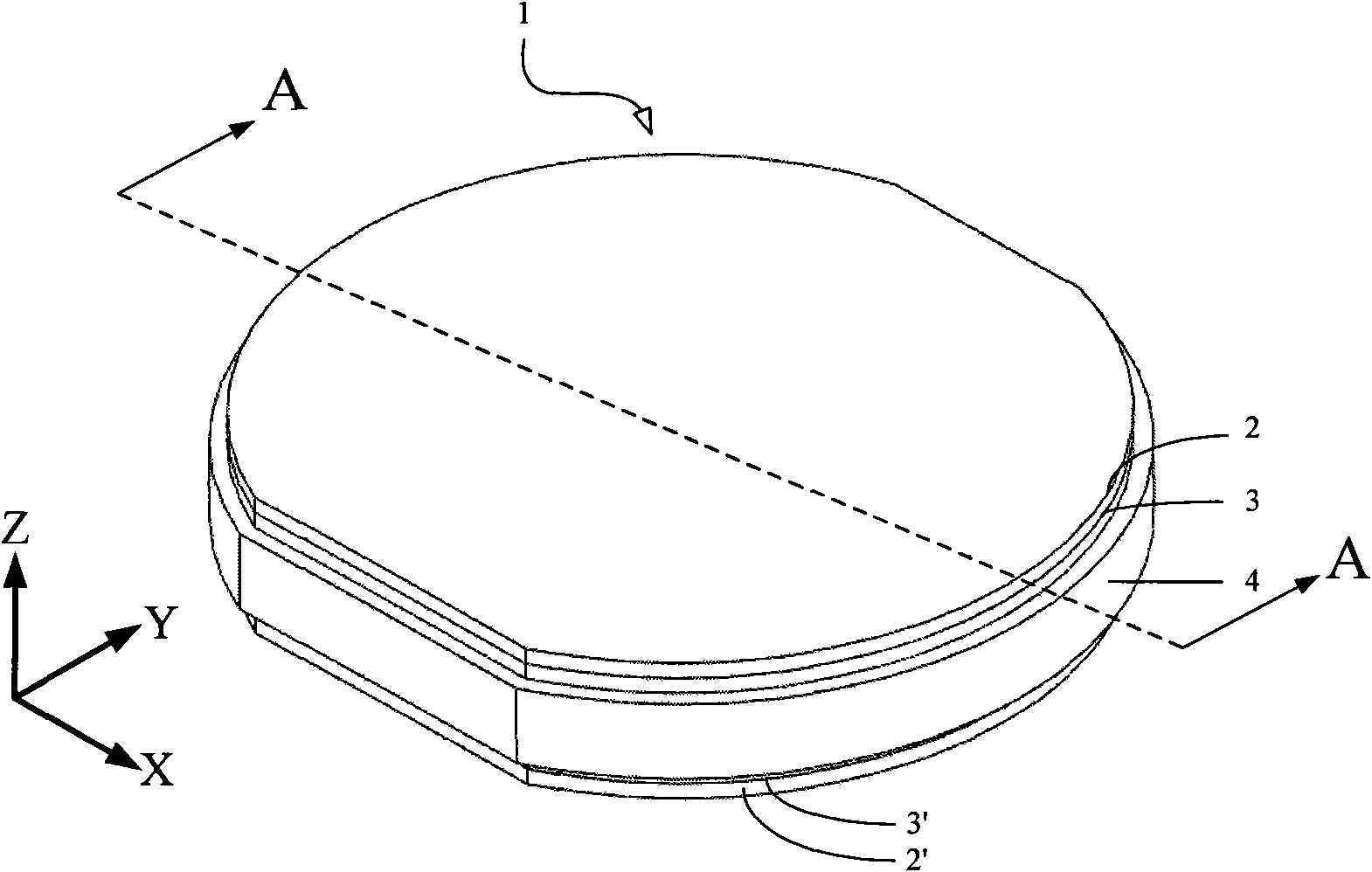

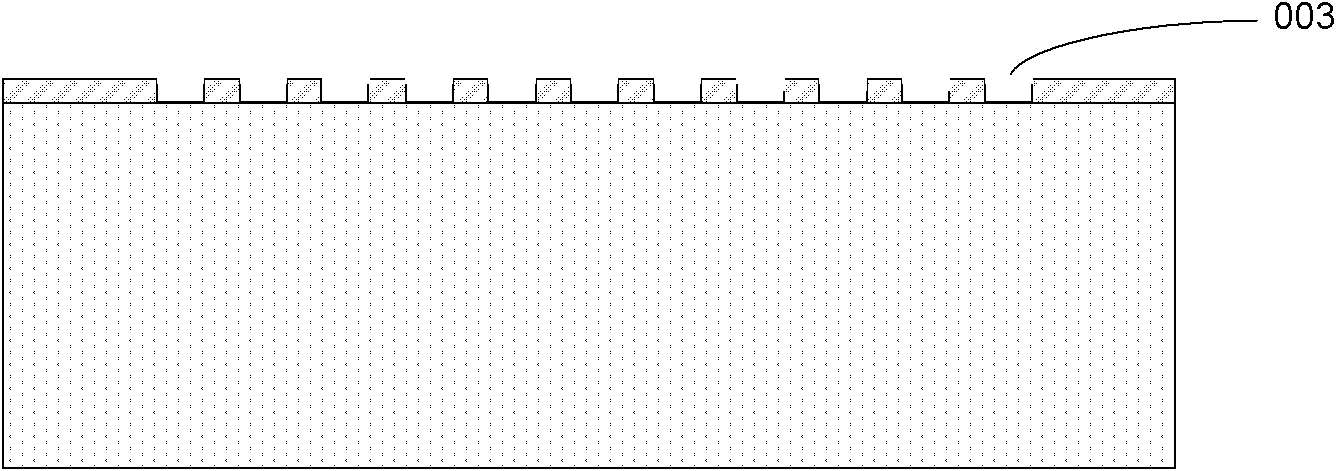

Semitransparent fluorescent powder/glass composite luminescent ceramic wafer and preparation method thereof

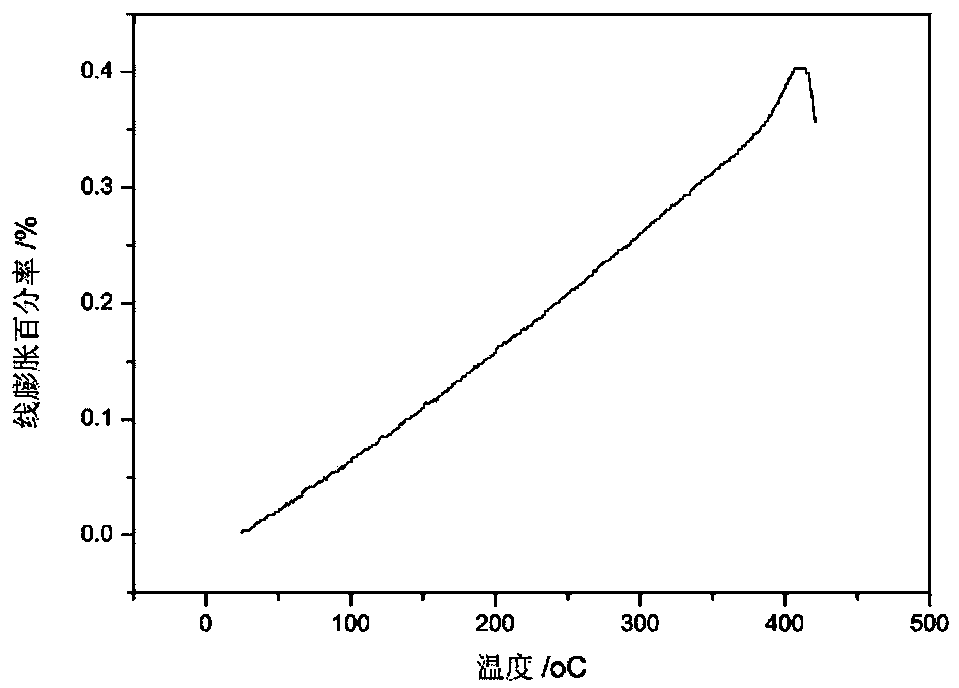

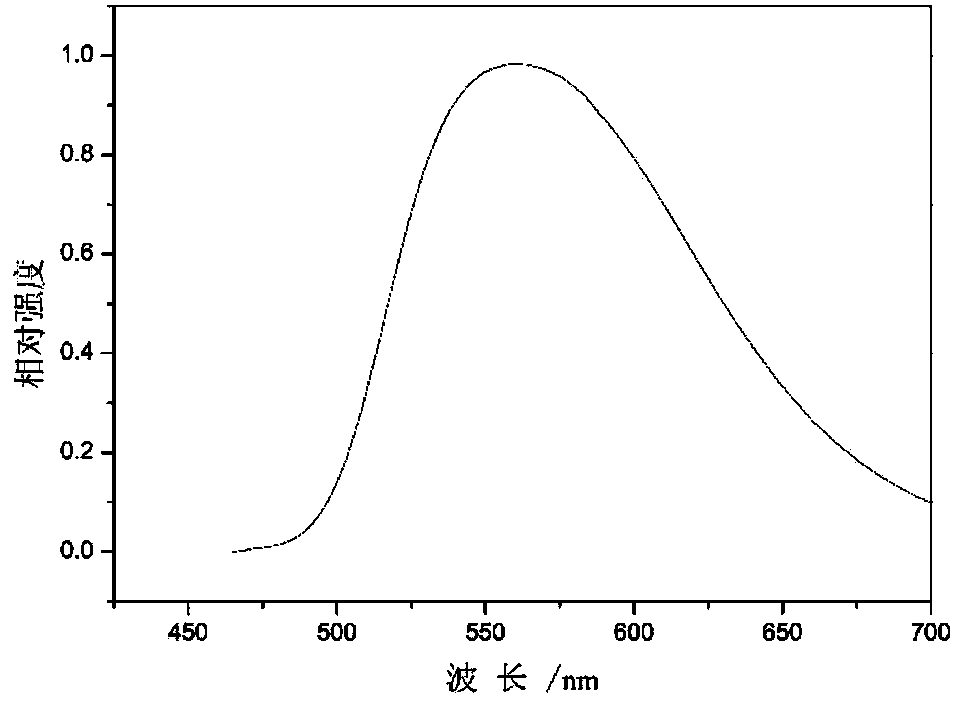

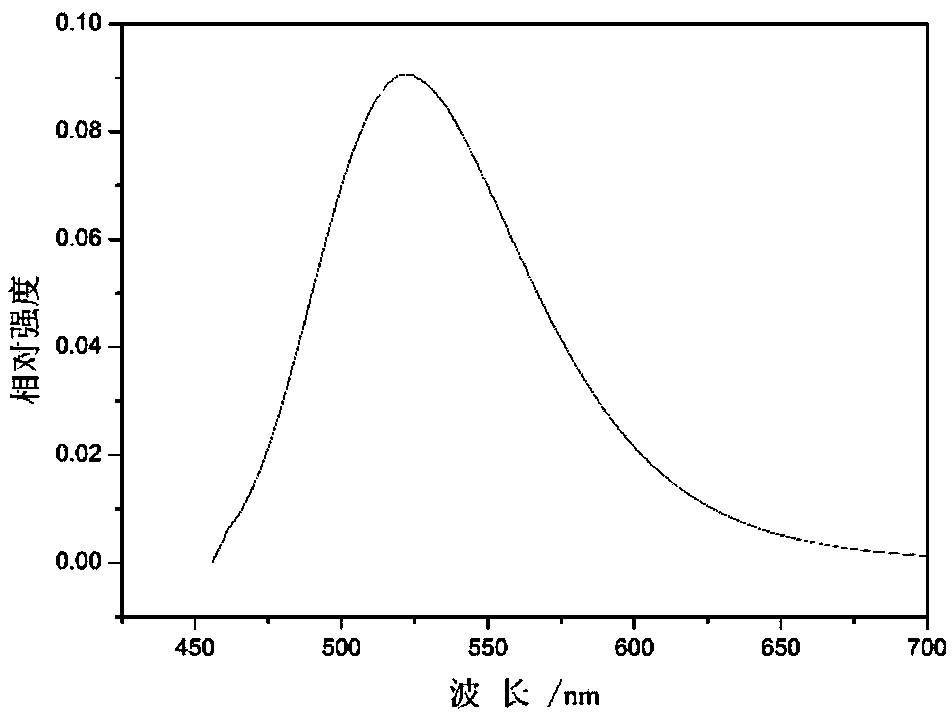

The invention relates to a semitransparent fluorescent powder / glass composite luminescent ceramic wafer and a preparation method thereof. The semitransparent fluorescent powder / glass composite luminescent ceramic wafer is obtained by carrying out 'pelletizing, compression moulding and sintering' on fluorescent powder and low-melting-point glass powder, wherein content of the fluorescent powder is 30-85wt%, and the content of the low-melting-point glass powder is 70-15wt%. The preparation method of the semitransparent fluorescent powder / glass composite luminescent ceramic wafer comprises the following steps: firstly, uniformly mixing fluorescent powder with glass powder in certain proportion, and adding a binding agent required by pelletizing and demoulding, so that pelletized powder of 60-100 meshes is obtained; secondly, carrying out compression moulding on the obtained pelletized powder by virtue of a mould, so that a green body of a certain shape is obtained; thirdly, carrying out heat treatment, namely carrying out glue drainage on the green body for 2-4 hours at the temperature of 300-395 DEG C, and sintering for 1-2 hours at the temperature of 395-410 DEG C, wherein the whole heat treatment process is carried out in the air atmosphere; and finally the fluorescent powder / glass composite luminescent ceramic wafer is obtained.

Owner:厦门百嘉祥微晶材料科技股份有限公司

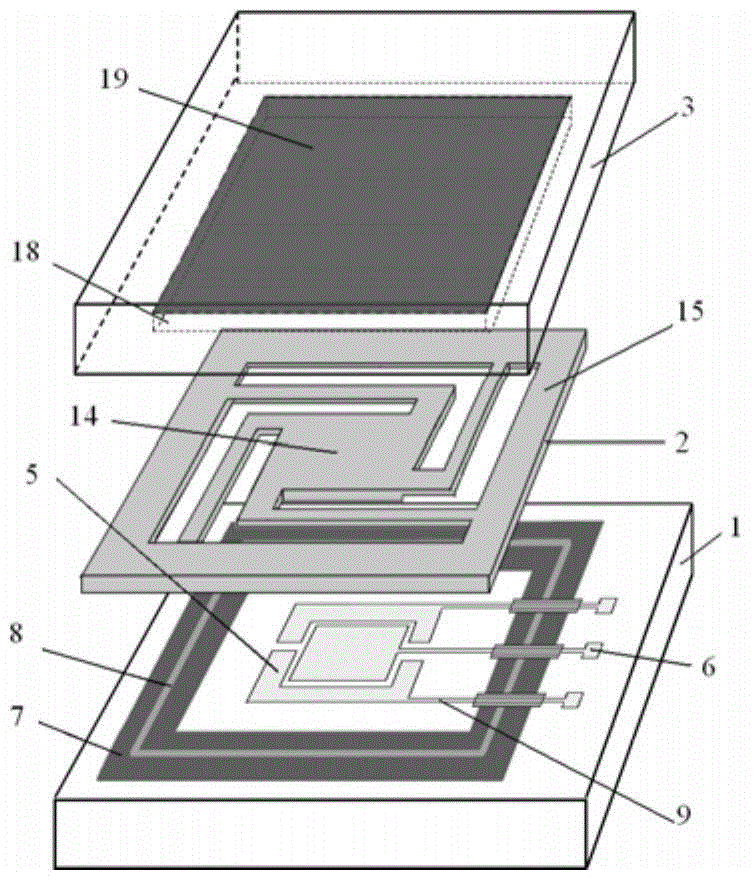

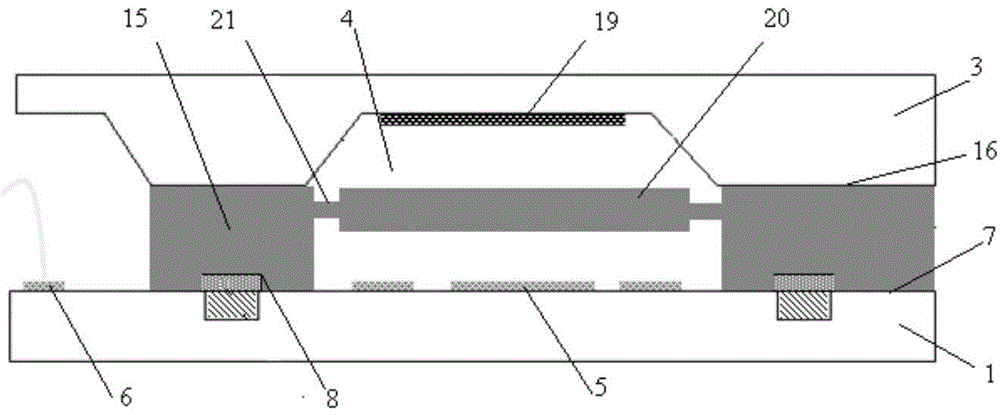

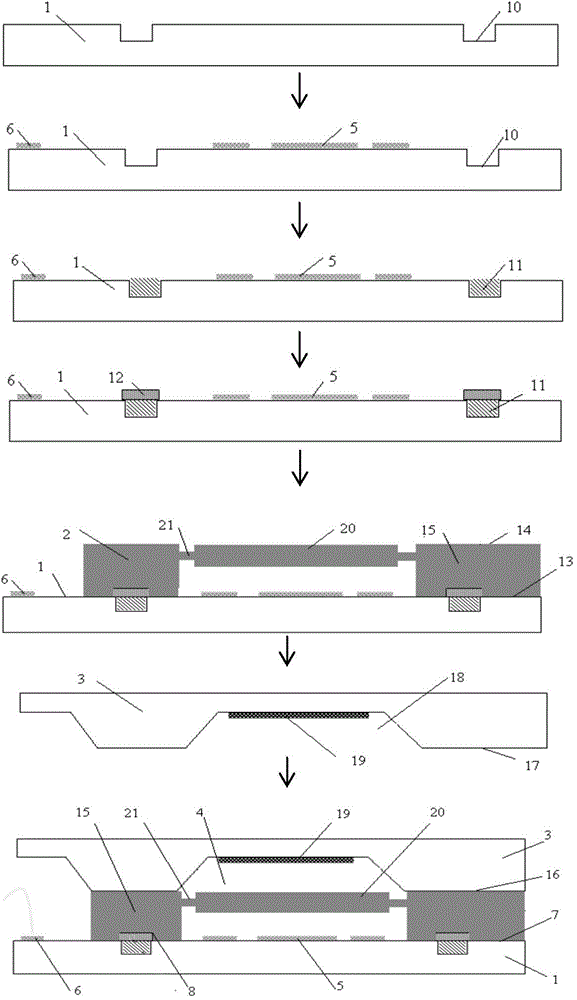

Processing method of differential type high-precision accelerometer

ActiveCN101786593AReduce process difficultyLow process temperatureTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesStress ProblemMonocrystalline silicon

The invention discloses a processing method of a differential type high-precision accelerometer. The accelerometer comprises an upper electrode cover plate, a movable silicon structural assembly with a beam-mass block structure and a lower electrode cover plate which are sequentially connected from top to bottom. The method comprises the following steps of: processing the upper electrode plate and the lower electrode plate by using a glass sheet or a monocrystalline silicon wafer as a substrate; processing the movable silicon structural assembly with the beam-mass block structure by using a double-device-layer SOI (Silicon-On-Insulator) monocrystalline silicon wafer as a substrate; and connecting the upper electrode plate and the lower electrode plate which are processed by using the substrates with the movable silicon structural assembly based on a bonding mode. In the invention, only one monocrystalline silicon wafer is adopted to process the movable silicon structural assembly, thereby avoiding the condition that a frequently used high-temperature silicon-silicon bonding process is used for preparing the movable silicon structural assembly, reducing the process difficulty, lowering the highest process temperature and eliminating bonding stress problems introduced by silicon-silicon bonding; and moreover, the beam-mass block structure has generality.

Owner:PEKING UNIV

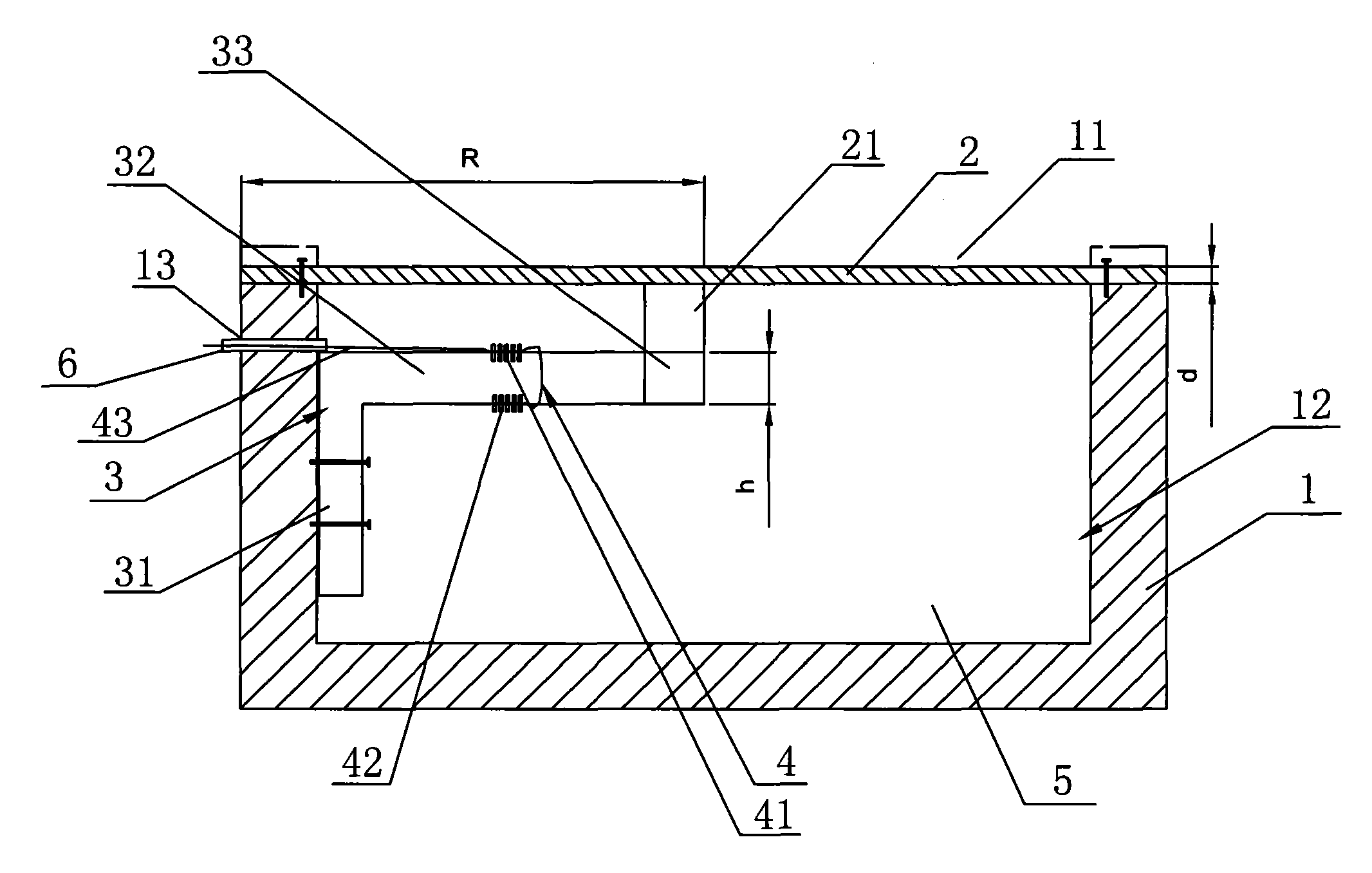

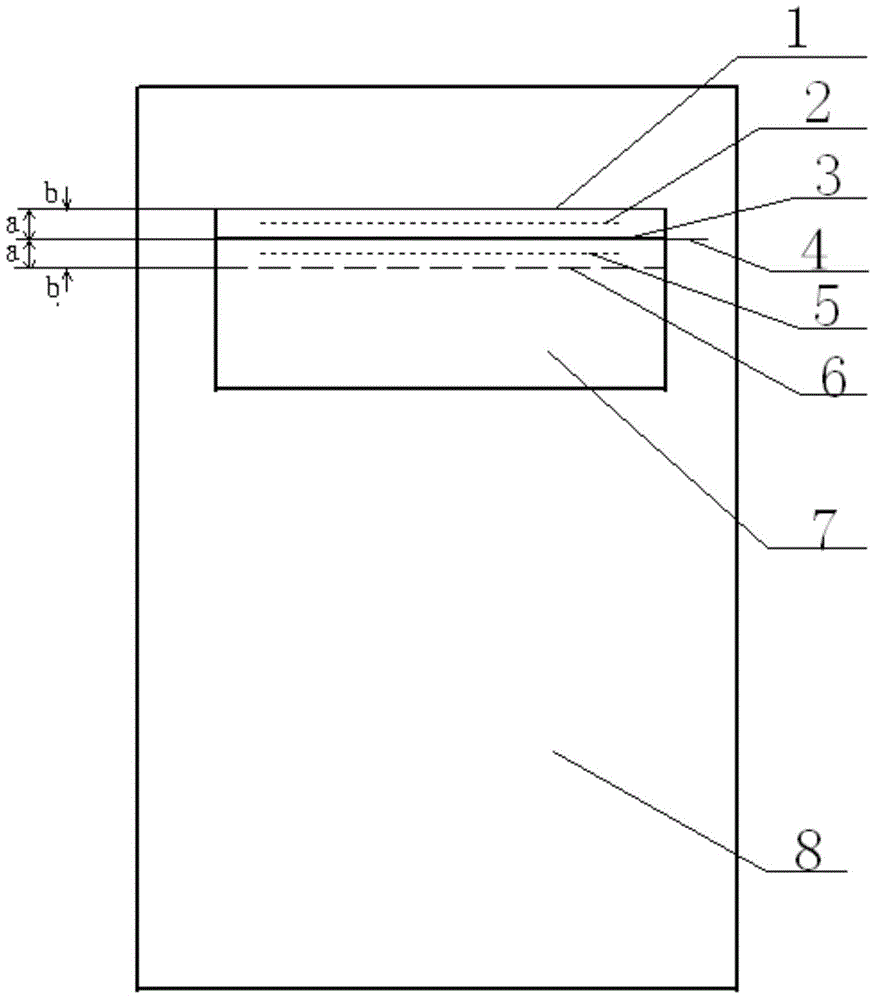

Optical fiber Bragg grating pressure sensor and corresponding measurement method thereof

ActiveCN101900616AHigh measurement accuracyReduce process difficultyForce measurement by measuring optical property variationFluid pressure measurement by optical meansEngineeringAccuracy and precision

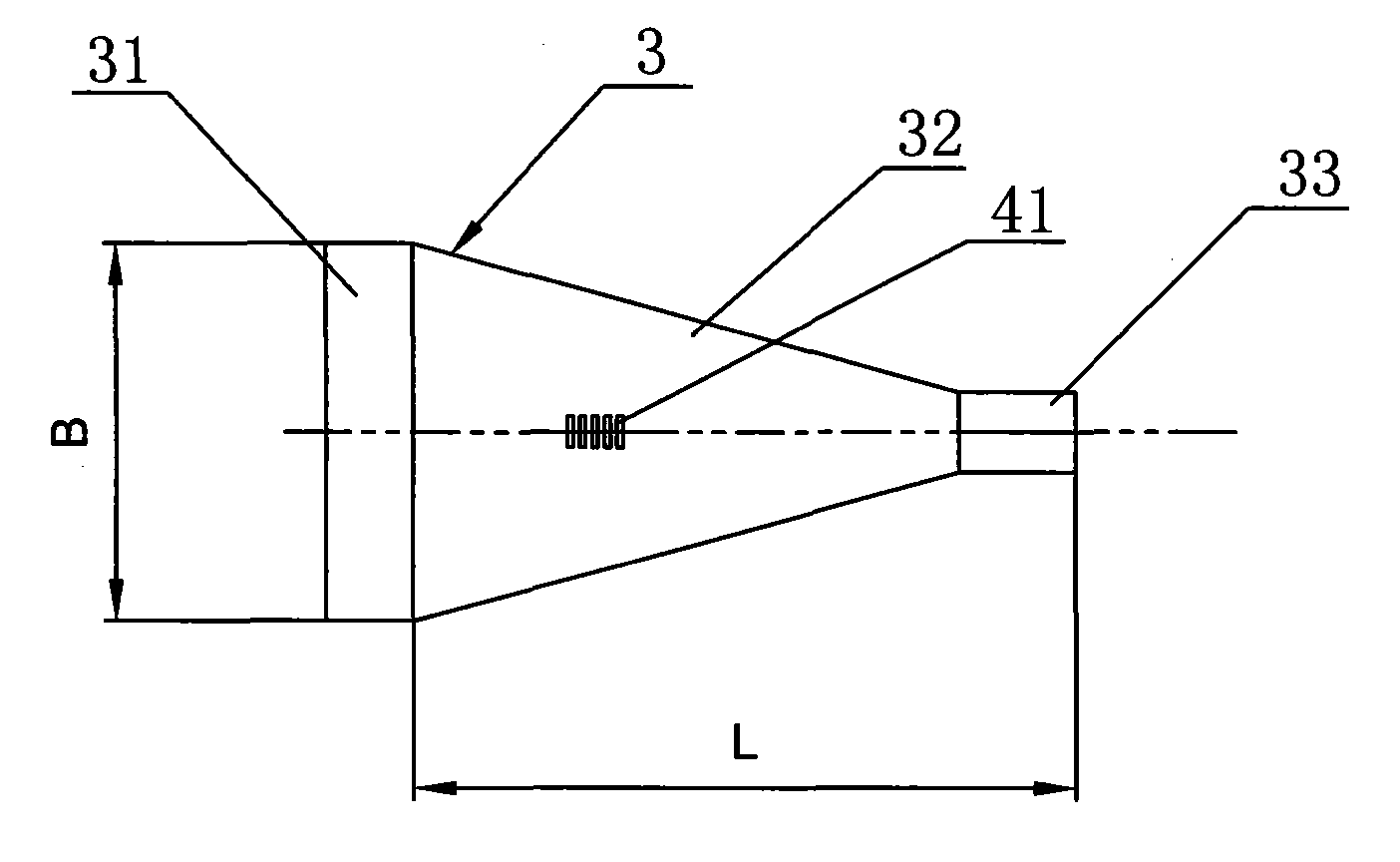

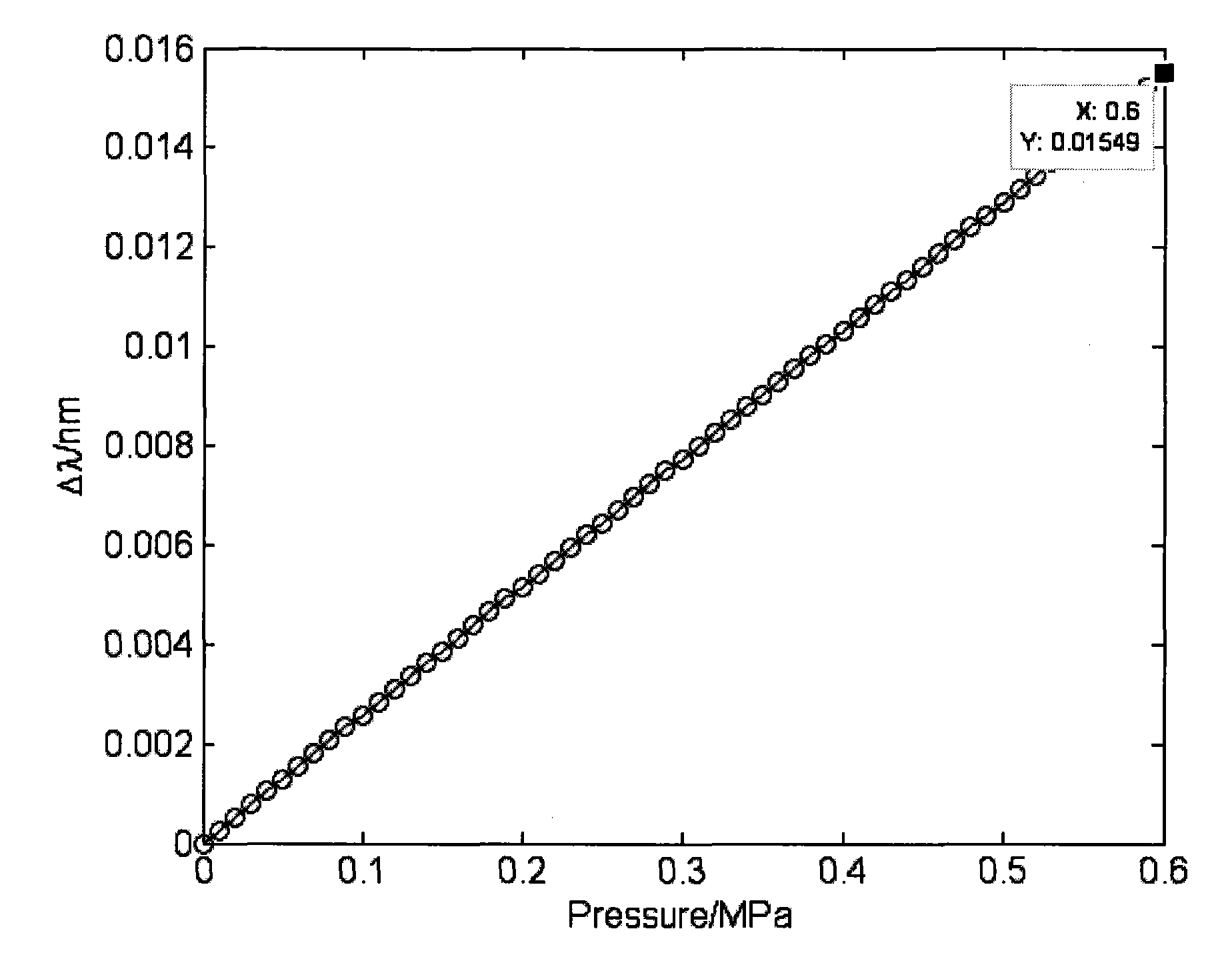

The invention discloses an optical fiber Bragg grating pressure sensor and a corresponding measurement method thereof, and the sensor comprises a housing, an elastic diaphragm, an L-shaped uniform strength beam and an optical fiber Bragg grating, wherein an opening is arranged at the top end of the housing, the opening and internal space of the housing constitute a cavity body, the elastic diaphragm covers the opening, the uniform strength beam is arranged in the cavity body, a pressure block is arranged at the free end of a beam arm of the uniform strength beam, a hard boss which is tightly connected with the pressure block is arranged on the lower surface of the elastic diaphragm, the optical fiber Bragg grating is mainly constituted by connecting two Bragg gratings with the identical temperature gradient in series through an optical fiber, and the two Bragg gratings are respectively connected on the upper surface and the lower surface of the beam arm. The sensor has the advantages that the elastic diaphragm is in rigid connection with the beam arm during the design, thereby not only improving the measurement precision, but also reducing the process difficulty; as the optical fiber Bragg grating is mainly constituted by the two Bragg gratings with the identical temperature gradient, the sensor can solve the temperature cross sensitivity problem during the measurement.

Owner:NINGBO SHANGONG CENT OF STRUCTURAL MONITORING &CONTROL ENG

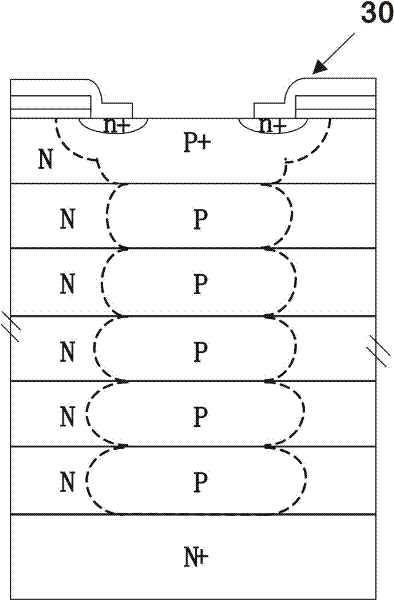

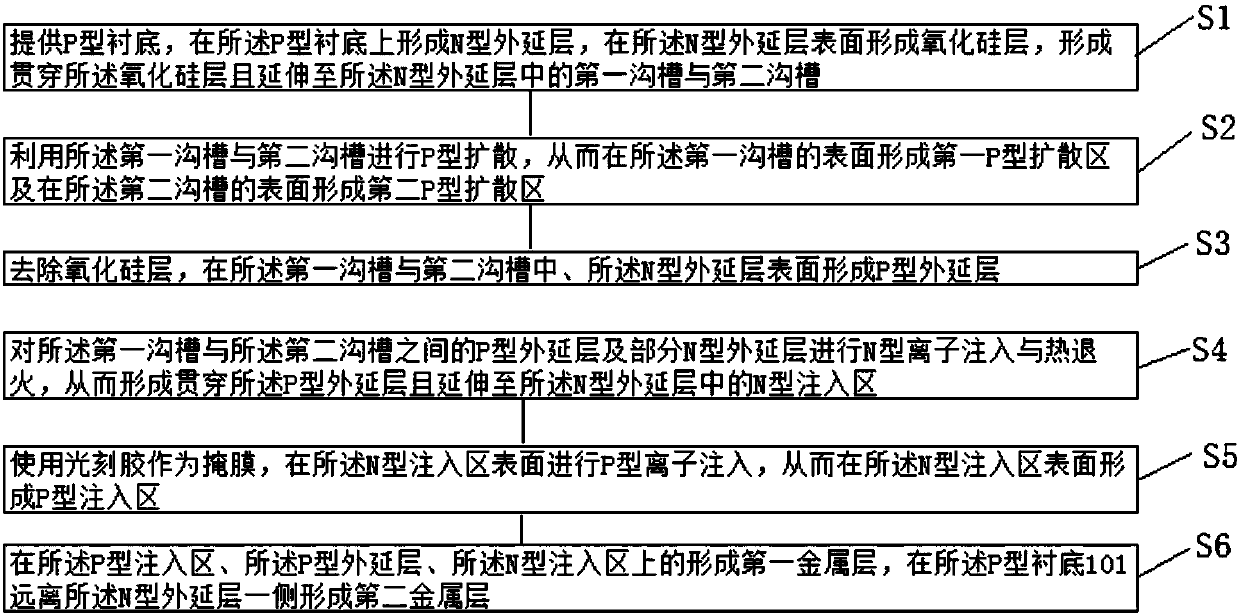

Super junction semiconductor element and manufacture method thereof

InactiveCN102479805AAvoid too many extensionsReduce process difficultySemiconductor/solid-state device manufacturingSemiconductor devicesEtchingSemiconductor components

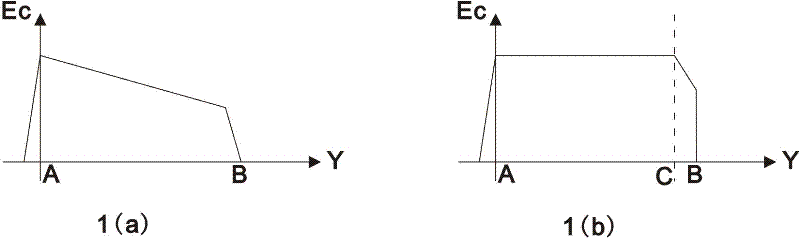

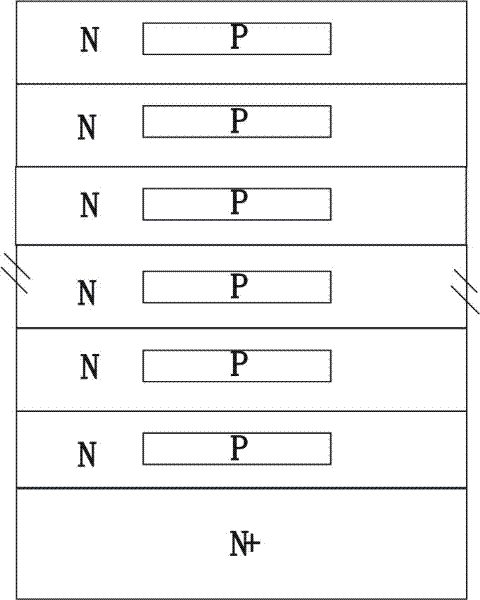

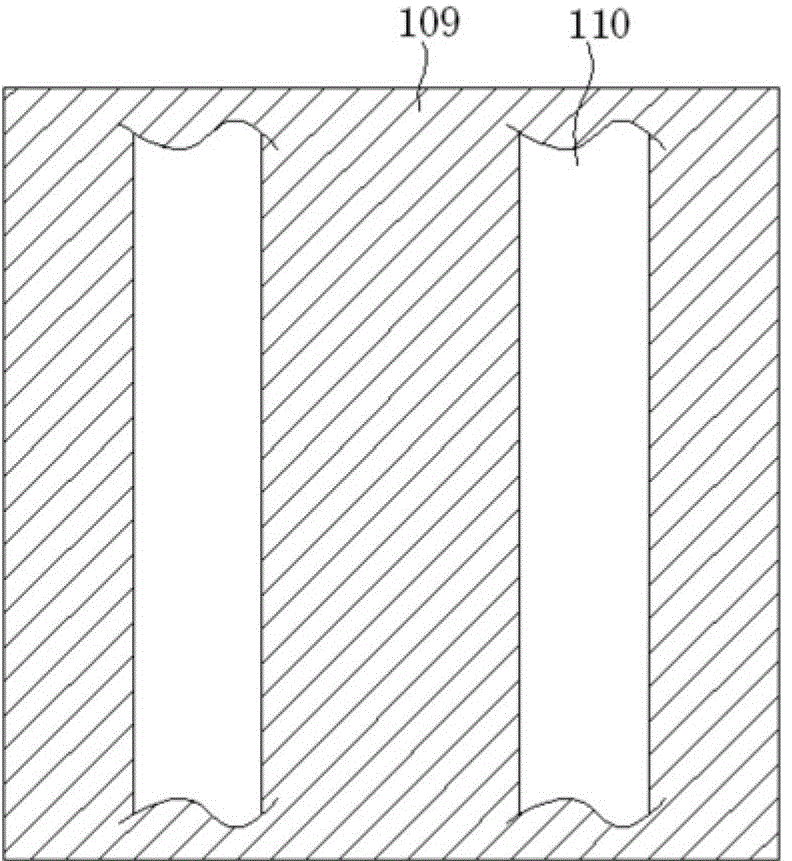

The invention relates to a super junction semiconductor element and a manufacture method thereof. The super junction semiconductor element comprises a first conduction type substrate, at least one first conduction type first epitaxial layer and at least one first conduction type second epitaxial layer, wherein the first conduction type first epitaxial layer is arranged on the first conduction type substrate and comprises second conduction type doping, the first conduction type second epitaxial layer is arranged on the first conduction type first epitaxial layer and comprises second conduction type doping, and a device characteristic layer is arranged on the second epitaxial layer. The lattice defect problem caused by multi-time epitaxial growth, ion injection and diffusion can also be reduced to a certain degree, and high cost generated by too many epitaxial times is avoided. Simultaneously, the process difficulty of the etching and the groove filling is also greatly reduced along with grooves, and the stress and wafer curling problems caused by excessive depth of the grooves are also reduced.

Owner:BYD CO LTD

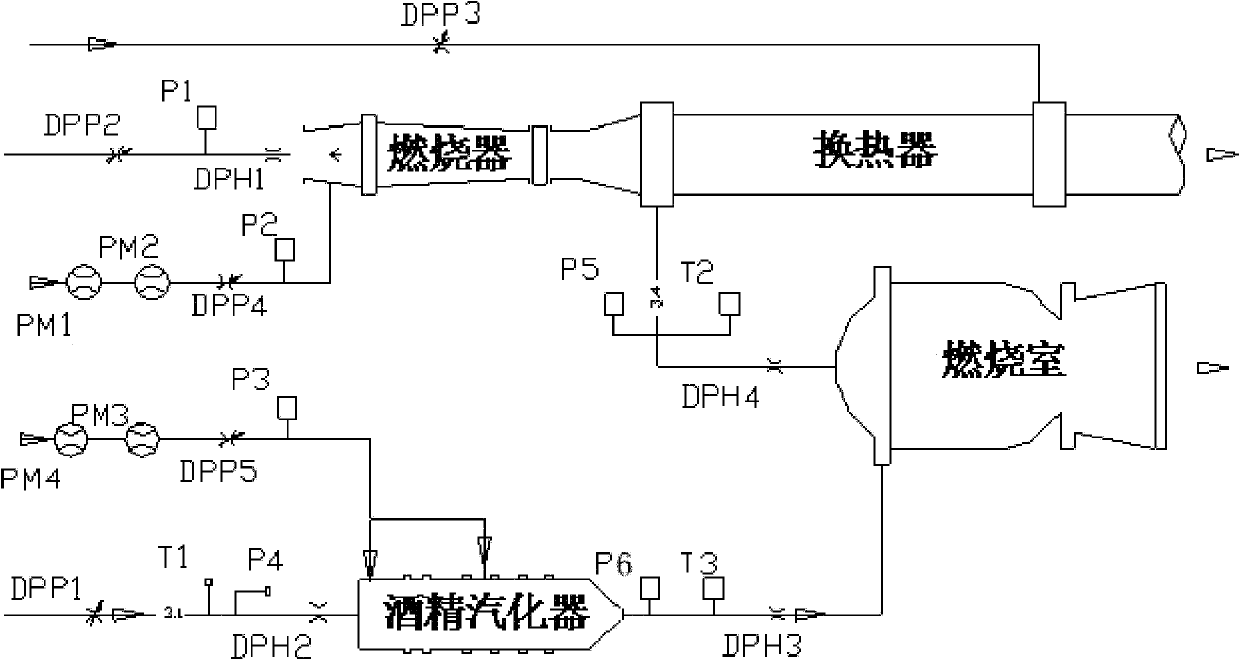

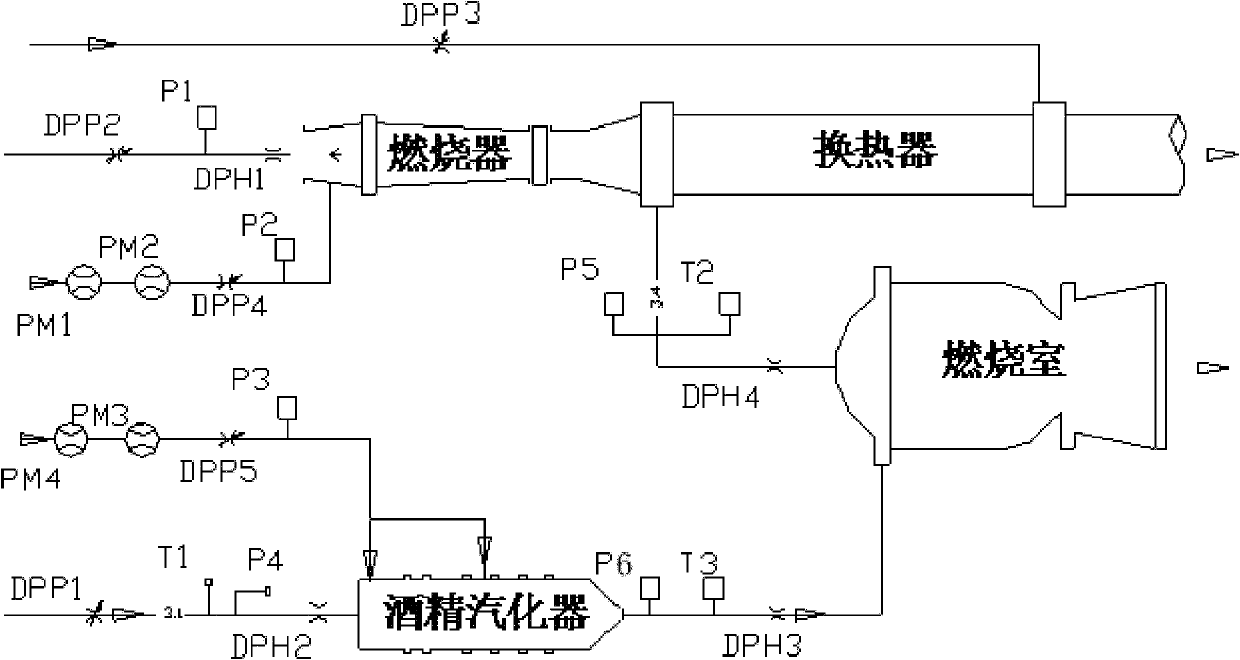

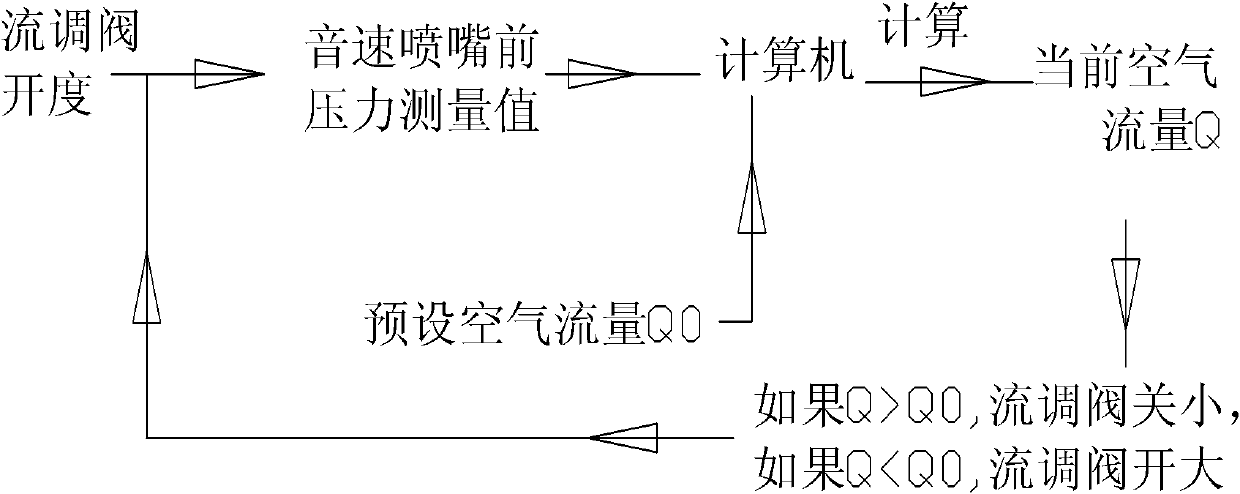

High-frequency combustion instability coverall process simulation test automatic regulating system and method

ActiveCN101907043AReduce test costsReduce process difficultyRocket engine plantsCombustion instabilityInstability

The invention relates to high-frequency combustion instability coverall process simulation test automatic regulating system and method. The system comprises a control system, a combustor, a heat exchanger, an alcohol vaporizer and a combustion chamber, wherein the control system is used for regulating working conditions in the combustion chamber by a parameter input and flow regulating valve; the combustion chamber is an engine head with real size, an oxidant inlet and a fuel inlet of the combustion chamber are respectively communicated with the heat exchanger and the alcohol vaporizer, the oxidant inlet of the combustion chamber is provided with a sound velocity pore plate, a pressure measuring point and a temperature measuring point; the fuel inlet of the combustion chamber is provided with a sound velocity pore plate, a pressure measuring point and a temperature measuring point; and a cold air inlet of the heat exchanger is provided with a cold air flow regulating valve, and a heatsource of the heat exchanger is a combustor. The invention solves the technical problems of high cost, long period and poor safety property caused by adopting a real engine and a real working condition in the traditional simulation test, is very low in test cost, and lowers economic and labor costs.

Owner:NO 11 INST OF NO 6 ACADEMY OF CHINA AEROSPACE SCI & TECH

Technical method for forming semi-axle housing tube for large-diameter flange

ActiveCN102513791AReduce equipment investment costsReduce process difficultyForming forceEngineering

The invention discloses a technical method for forming a semi-axle housing tube for a large-diameter flange. The technical method comprises the following steps of: sawing hot-rolled round steel serving as a blank, heating, and upsetting by using an extruding machine; performing rotary forging for forming by using a rotary forging press; and performing forward extrusion once and backward extrusion to form a forged piece of the semi-axle housing tube. According to technical method, in the maximum process step of forming force required by the semi-axle housing tube, the flange is formed by the rotary forging press; and only an outer step axle and an inner step hole are formed when the head flange is formed by the rotary forging and is extruded. The technical method has the advantages that: the full filling of flange corners is ensured effectively, the investment cost of equipment is reduced effectively, the process difficulty of the subsequent extrusion process step is reduced, the coaxiality of finished products is easy to ensure, and the production cost of the forged piece is reduced while the yield of the products is improved.

Owner:SHIYAN YUANJUN IND & TRADE

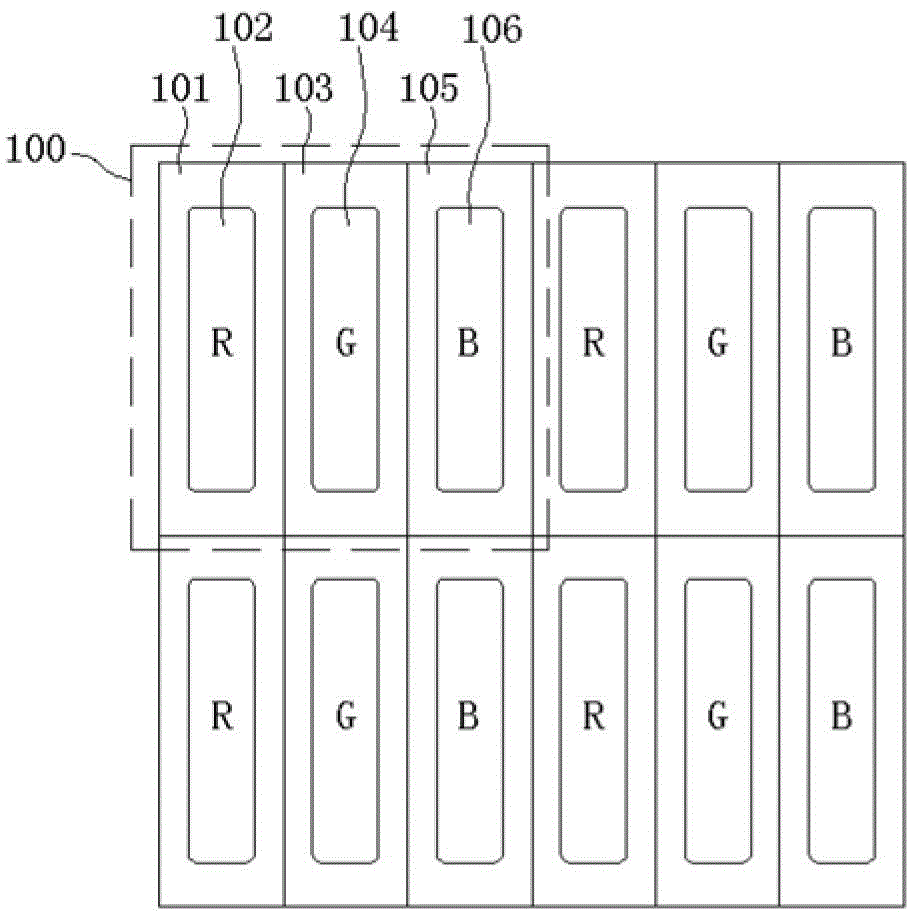

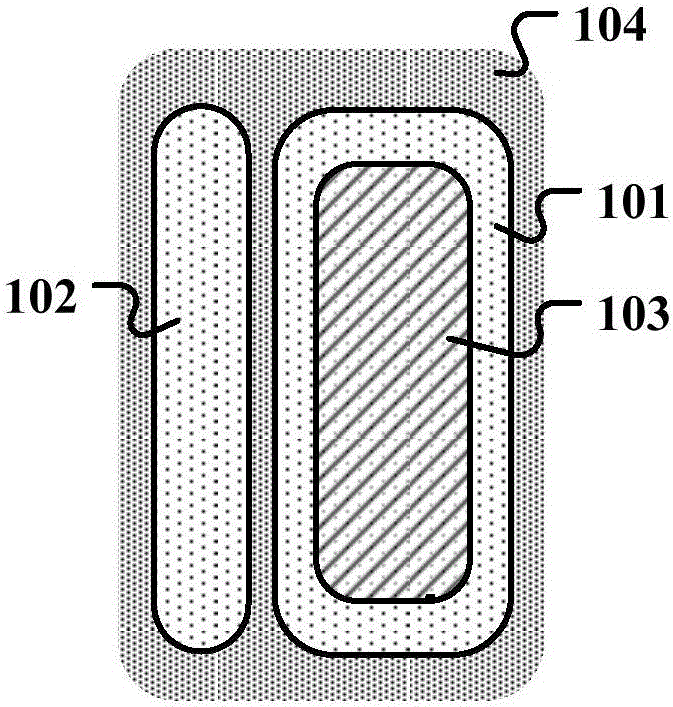

Pixel structure and organic light emitting display adopting same

ActiveCN104576696AIncrease widthReduce process difficultySolid-state devicesSemiconductor devicesDisplay deviceLower half

The invention discloses a pixel structure and an organic light emitting display adopting the same. The pixel structure comprises a plurality of pixel units, wherein each pixel unit takes a rhombus structure formed by an upper half part and a lower half part; the adjacent pixel units are arranged in a staggered manner; each pixel unit comprises a plurality of sub pixels; a first sub pixel forms one of the upper half part and the lower half part of the rhombus pixel unit; a second sub pixel and a third sub pixel are arranged side by side to form the other of the upper half part and the lower half part of the rhombus pixel unit together; pixels in the same color of the pixel units in the adjacent rows are arranged adjacently. By integrating the same sub pixels together, the width of the corresponding vapor deposition Mask hole diameter can be enlarged, the difficulty of the Mask technology can be reduced, and the display PPI (Pixel Per Inch) can be improved; meanwhile, because of the staggered arrangement manner of the pixel units in the adjacent rows, the adjacent edges of the second sub pixel and the third sub pixel with the first sub pixel can be longer, main light emitting of the pixel units can be relatively concentrated, and the light mixing effect is good.

Owner:KUNSHAN GO VISIONOX OPTO ELECTRONICS CO LTD

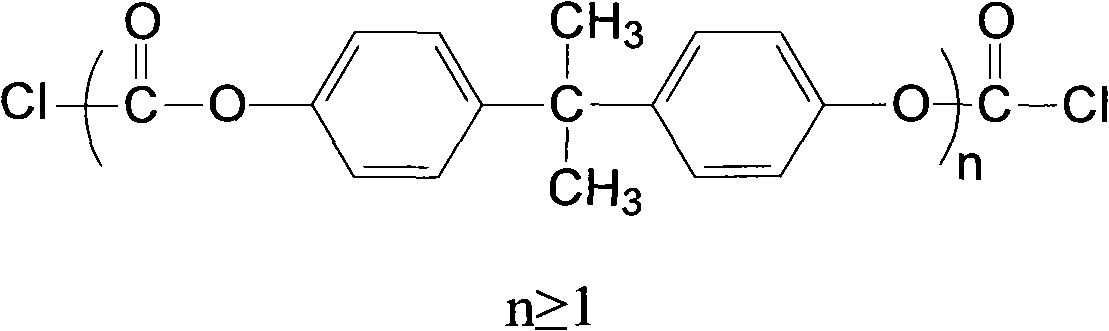

Method for preparing polycarbonate with continuous two-phase interface phosgene method

The invention relates to a novel method for preparing polycarbonate with a continuous two-phase interface phosgene method, comprising the following steps: carrying out photochemical reaction on alkali metal hydroxide solution and organic phase to prepare polycarbonate oligomer emulsion, wherein bisphenol or polyphenol or mixture of the bisphenol and the polyphenol is dissolved in the alkali metal hydroxide solution, the alkali metal hydroxide solution accounts for 95-99.5 percent of the weight in the formula, and the organic phase contains phosgene; and carrying out coupling reaction on the polycarbonate oligomer emulsion and the residual alkali metal hydroxide solution to finally prepare polycarbonate resin. The method for preparing the polycarbonate with the continuous two-phase interface phosgene method is simpler in process than the existing method for preparing the polycarbonate, and the loss of the phosgene and the alkali liquor is reduced effectively.

Owner:WANHUA CHEM GRP +1

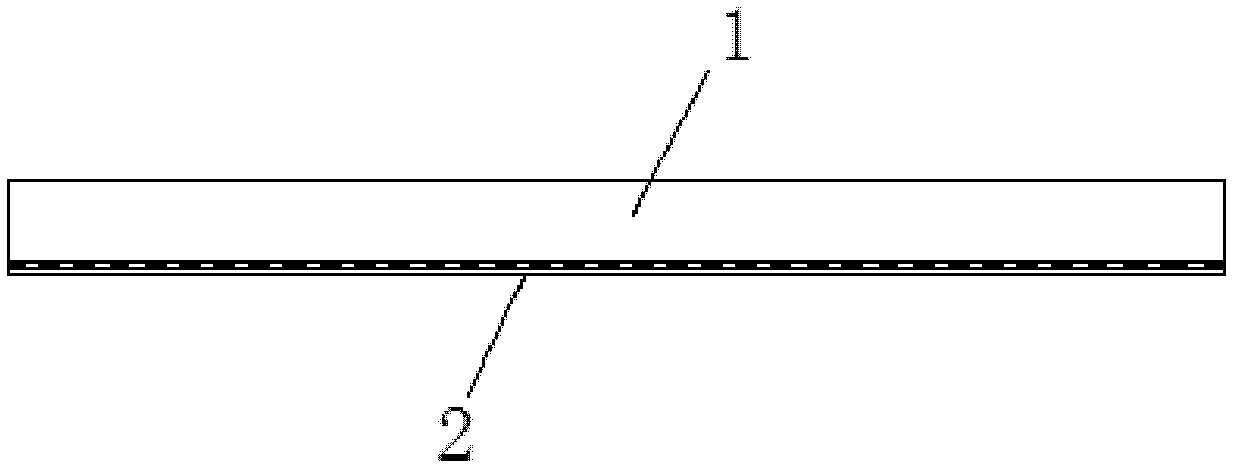

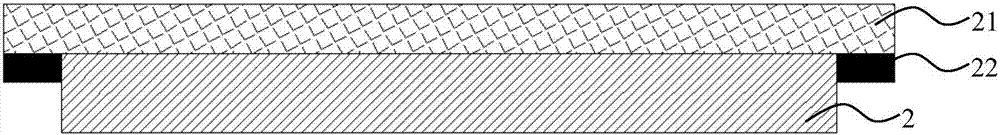

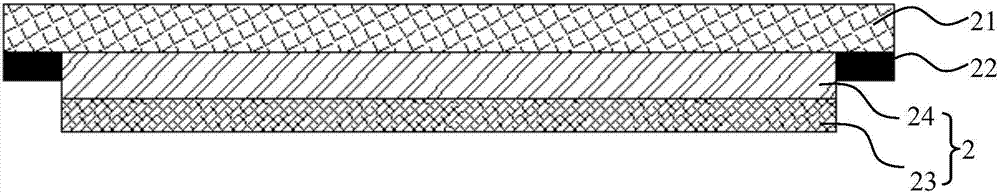

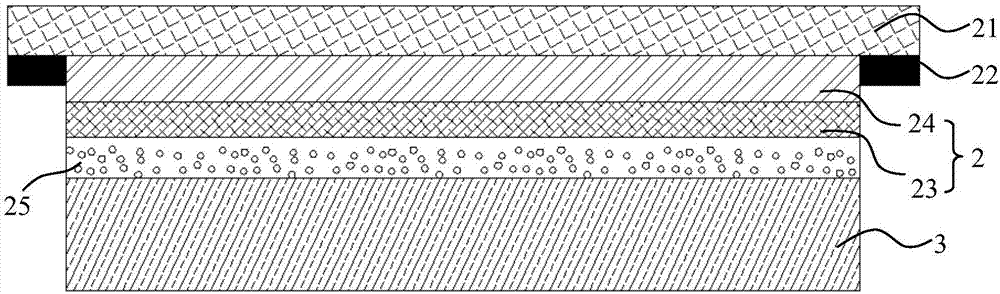

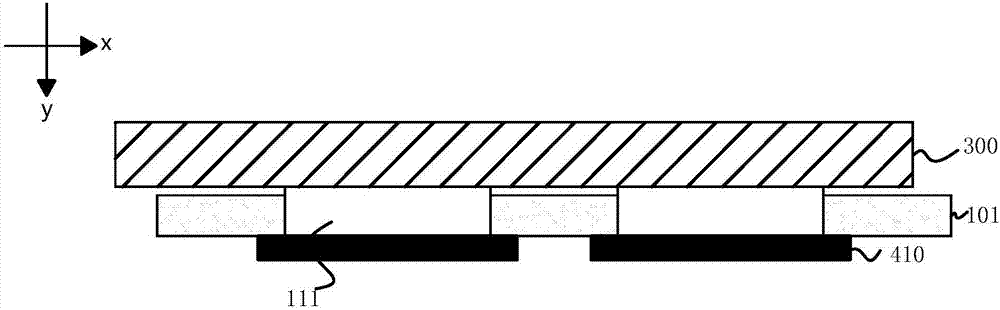

Composite light guide plate

InactiveCN102565923AEasy to implementReduce process difficultyOptical light guidesOptoelectronicsLight guide

The invention discloses a composite light guide plate, which comprises a transparent base plate and a transparent film, wherein a plurality of light guide points are printed on the transparent film and attached to the back of the transparent base plate. The light guide points are firstly printed on the transparent film, and then the transparent film printed with the light guide points is combined with the transparent base plate, so as to form the light guide plate, the light guide points are easier to be printed on the transparent film than to be directly printed on the transparent base plate in the prior art, the difficulty in the manufacturing process is further lowered, the process yield is improved, even if a defect product exists, only the transparent film is discarded, and the transparent base plate is intact, therefore, the cost can be reduced.

Owner:KUNSHAN CHENGTAI ELECTRIC

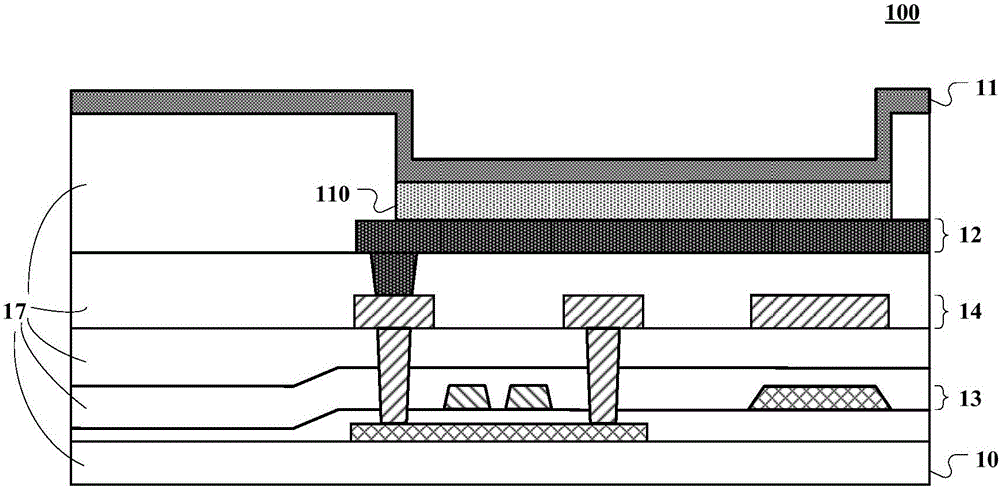

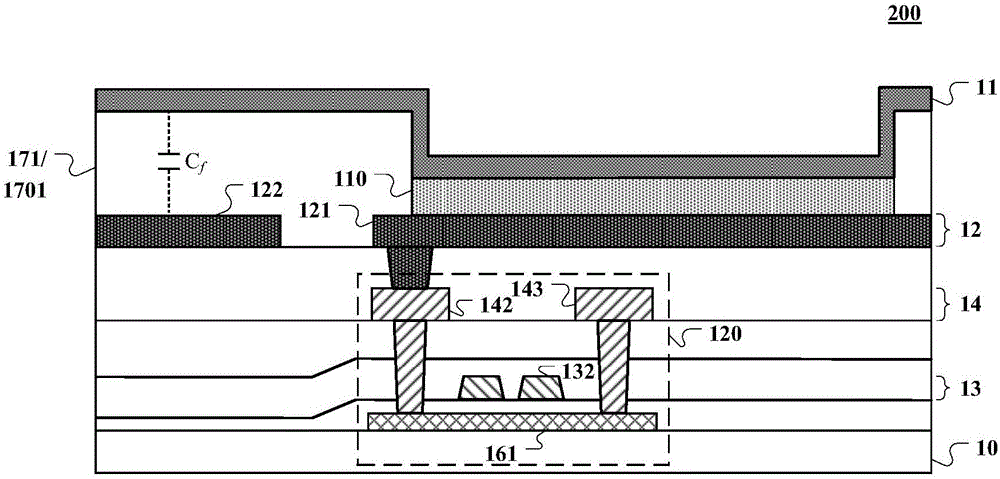

Organic light-emitting display panel and organic light-emitting display device

ActiveCN106206666AReduce thicknessReduce process difficultySolid-state devicesInput/output processes for data processingPressure sensitiveOptoelectronics

The invention discloses an organic light-emitting display panel and an organic light-emitting display device. The organic light-emitting display panel comprises a substrate, a cathode layer, an anode layer, a plurality of metal layers and an insulating medium, wherein the anode layer is located between the substrate and the cathode layer; the plurality of metal layers are located between the substrate and the anode layer; the insulating medium is located between the metal layers and the cathode layer; the anode layer comprises an anode region; the cathode layer is multiplexed as a first pressure-sensitive electrode; a second pressure-sensitive electrode is arranged on the metal layer or in a region not overlapping with the anode region of the anode layer; and the first pressure-sensitive electrode, the second pressure-sensitive electrode and the insulating medium located between the first pressure-sensitive electrode and the second pressure-sensitive electrode are used for sensing pressure. The organic light-emitting display panel and the organic light-emitting display device can achieve pressure sensing on the basis of an existing organic light-emitting display panel; the manufacturing cost is reduced; and the thickness of a pressure-sensitive display device is reduced.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD +1

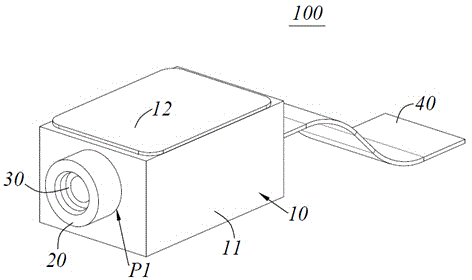

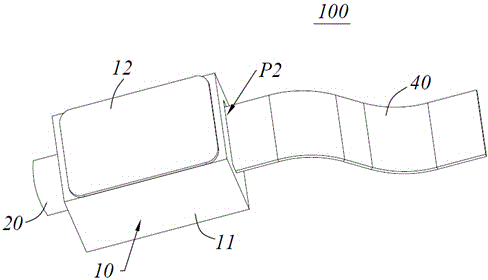

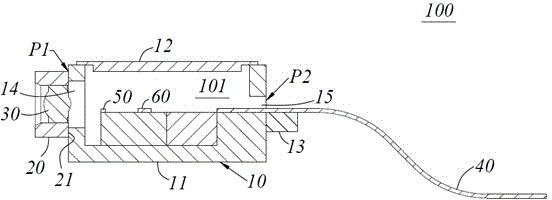

Light module and preparing method thereof

ActiveCN104459907AReduce process difficultyReduce manufacturing costCoupling light guidesEngineeringRing mode

The invention discloses a light module and a preparing method thereof. The light module comprises a metal shell body and an optical component packaged in the metal shell body. A light outlet corresponding to the optical component is formed in the metal shell body. The light module further comprises a metal sleeve which is connected to the light outlet in a ring mode. A lens is arranged in the metal sleeve. According to the technical scheme, the lens is arranged in the metal sleeve, by connecting of the metal sleeve and the metal shell body, corresponding of the lens and the light outlet in the metal shell body is achieved, the fact that the lens can allow passing of a light path of the light module is guaranteed, meanwhile, the metal sleeve and the metal shell body can be fixedly connected in a conventional welding mode, technology difficulty is lowered, and then the production cost of the light module is lowered.

Owner:旭创科技有限公司

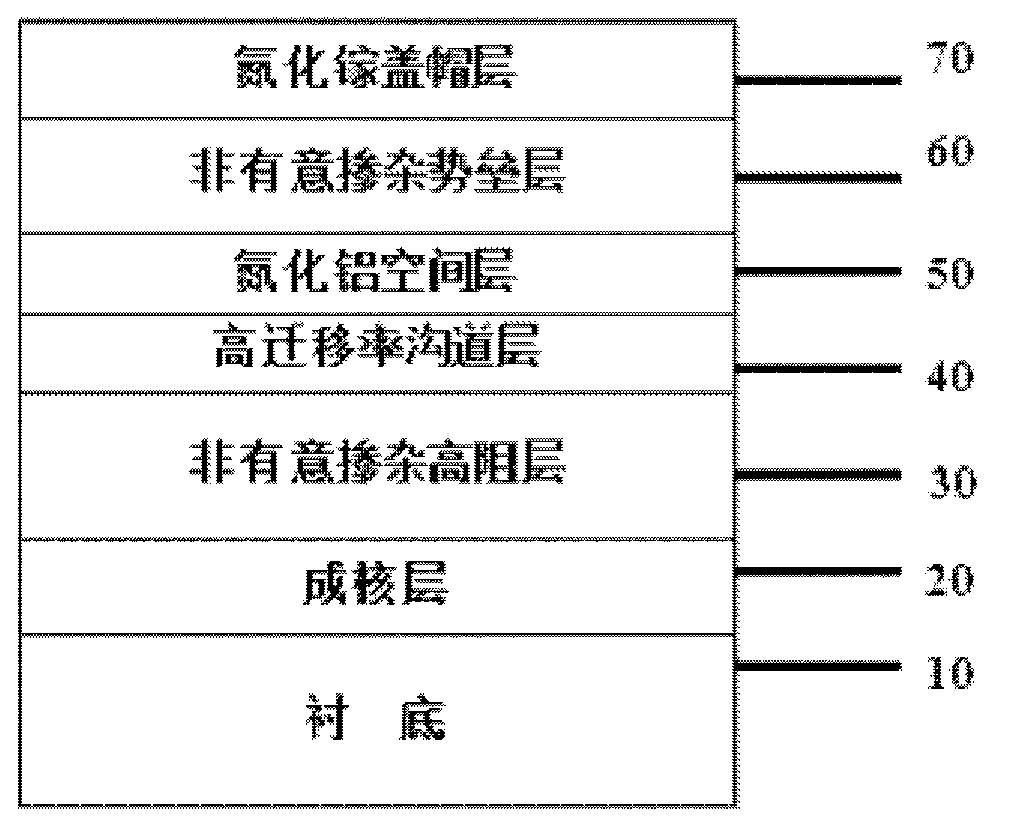

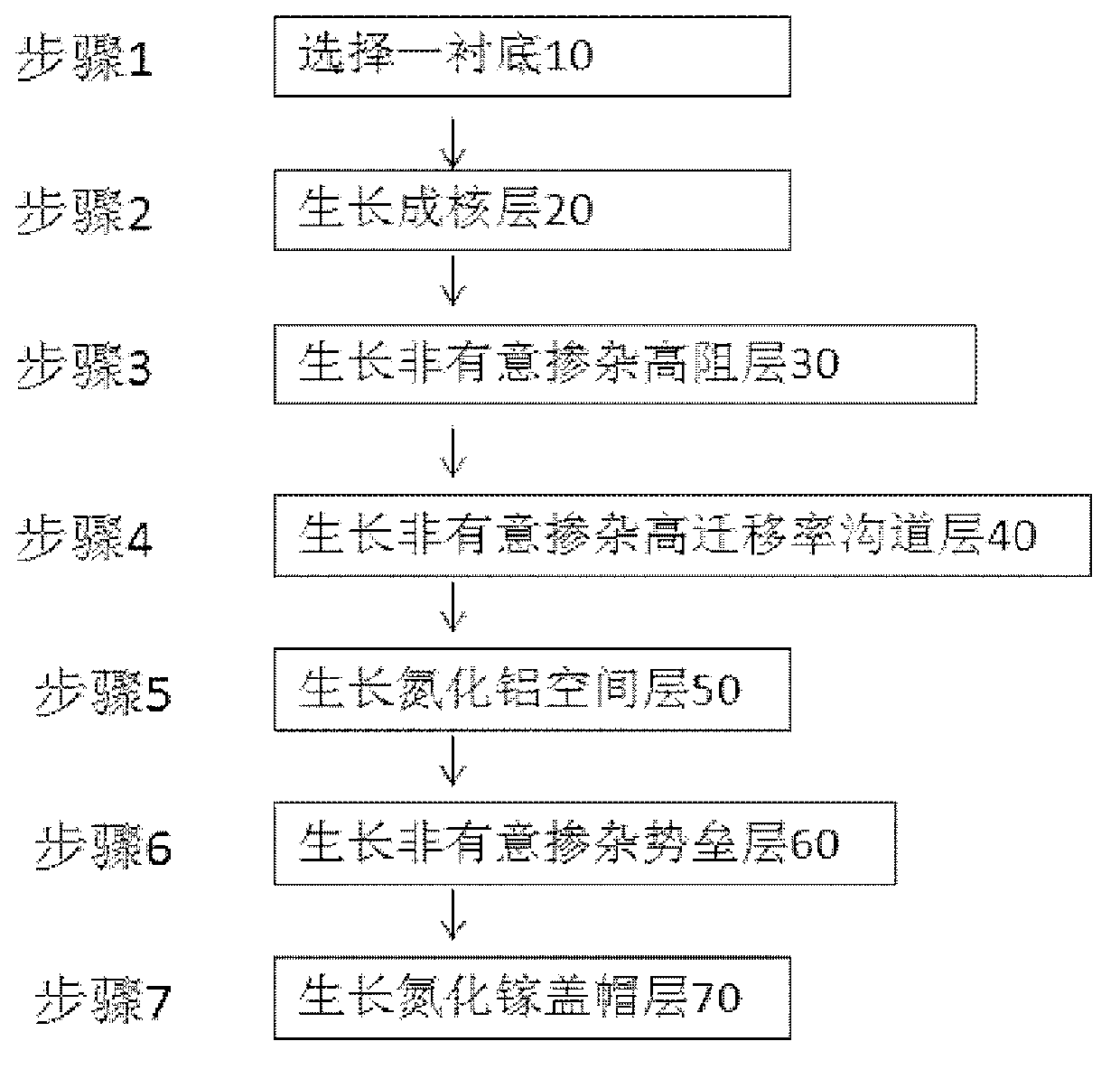

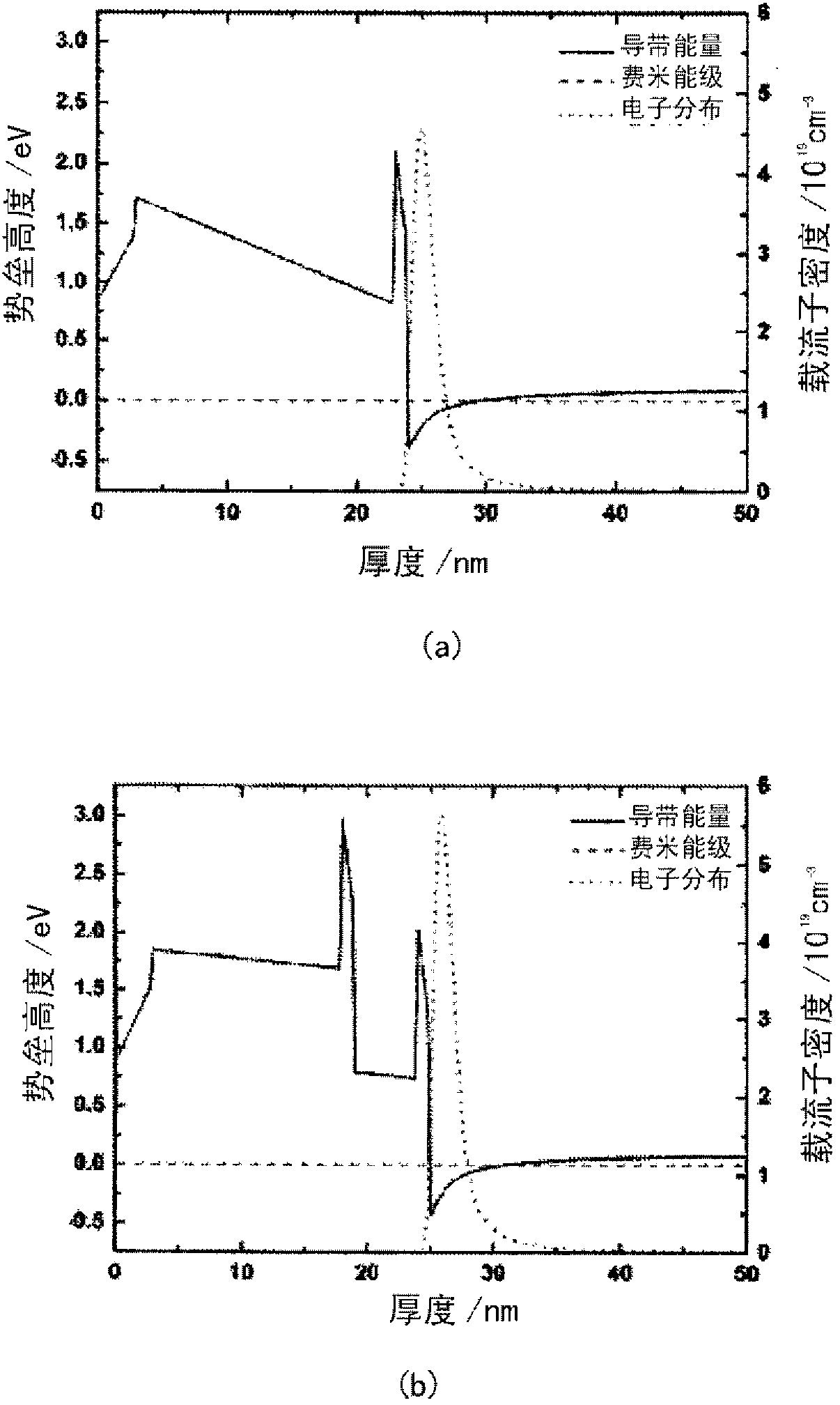

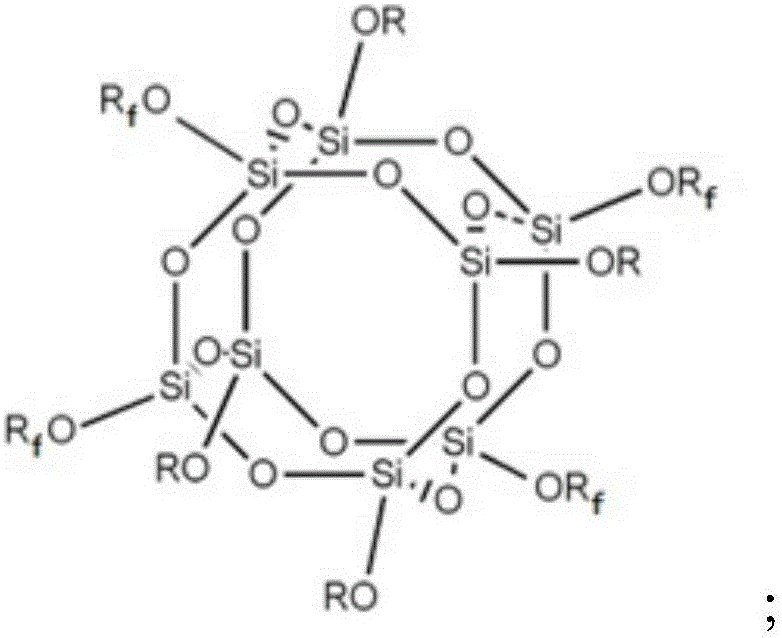

Gallium-nitride-based high electronic mobility transistor structure with barrier layer and manufacture method thereof

ActiveCN103123934AReduce process difficultyReduce process stepsSemiconductor/solid-state device manufacturingSemiconductor devicesGallium nitrideHigh-electron-mobility transistor

A gallium-nitride-based high electronic mobility transistor structure with a barrier layer comprises a substrate, a nucleating layer manufactured on the substrate, an unintentionally doped high resistance layer manufactured on the nucleating layer, an unintentionally doped high mobility channel layer manufactured on the unintentionally doped high resistance layer, an unintentionally doped aluminum nitride space layer manufactured on the unintentionally doped high mobility channel layer, an unintentionally doped barrier layer manufactured on the unintentionally doped aluminum nitride space layer and an unintentionally doped gallium nitride cap layer manufactured on the unintentionally doped barrier layer. The gallium-nitride-based high electronic mobility transistor structure can improve a limiting effect on channel two-dimensional electron gas and increase output power of a developed device, and simultaneously grate current of the device is reduced.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

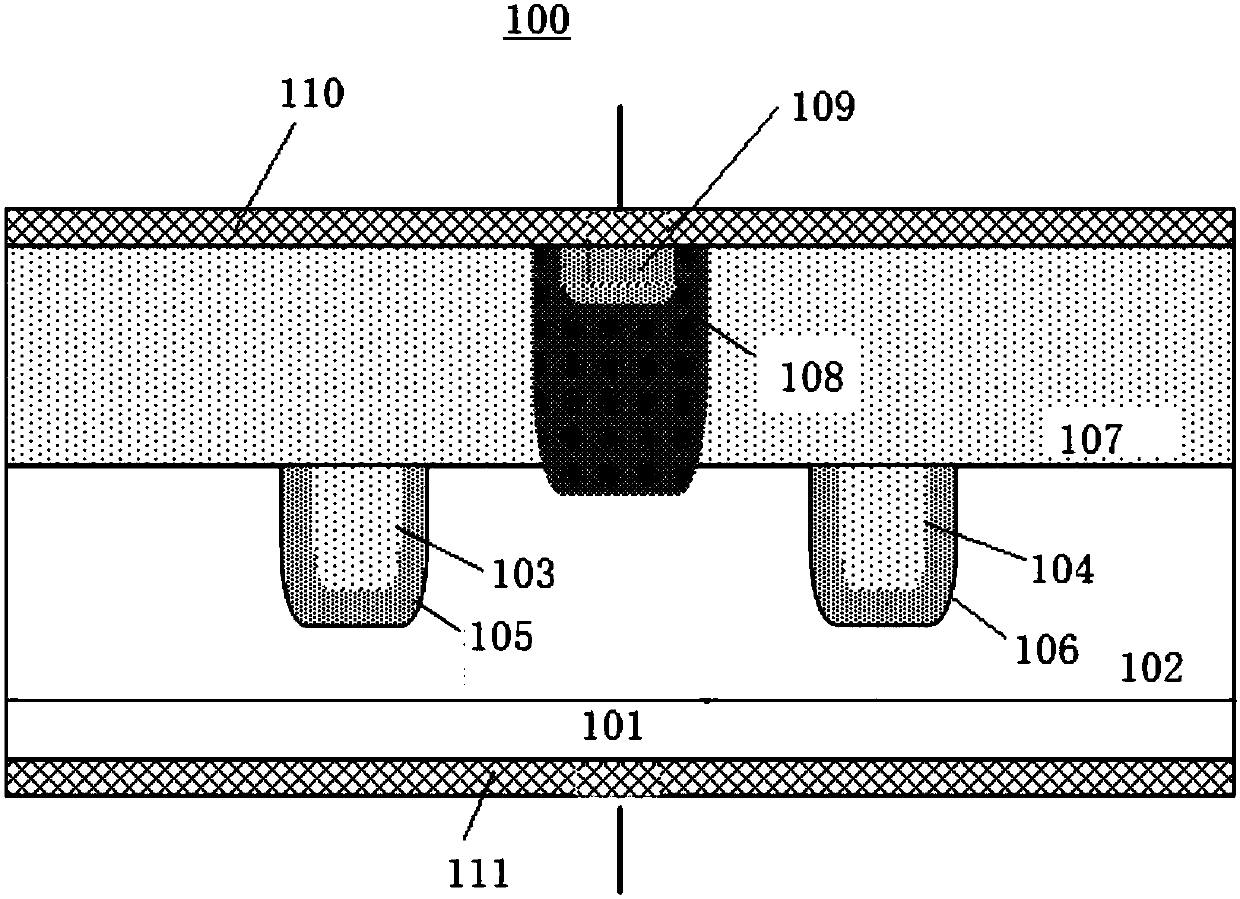

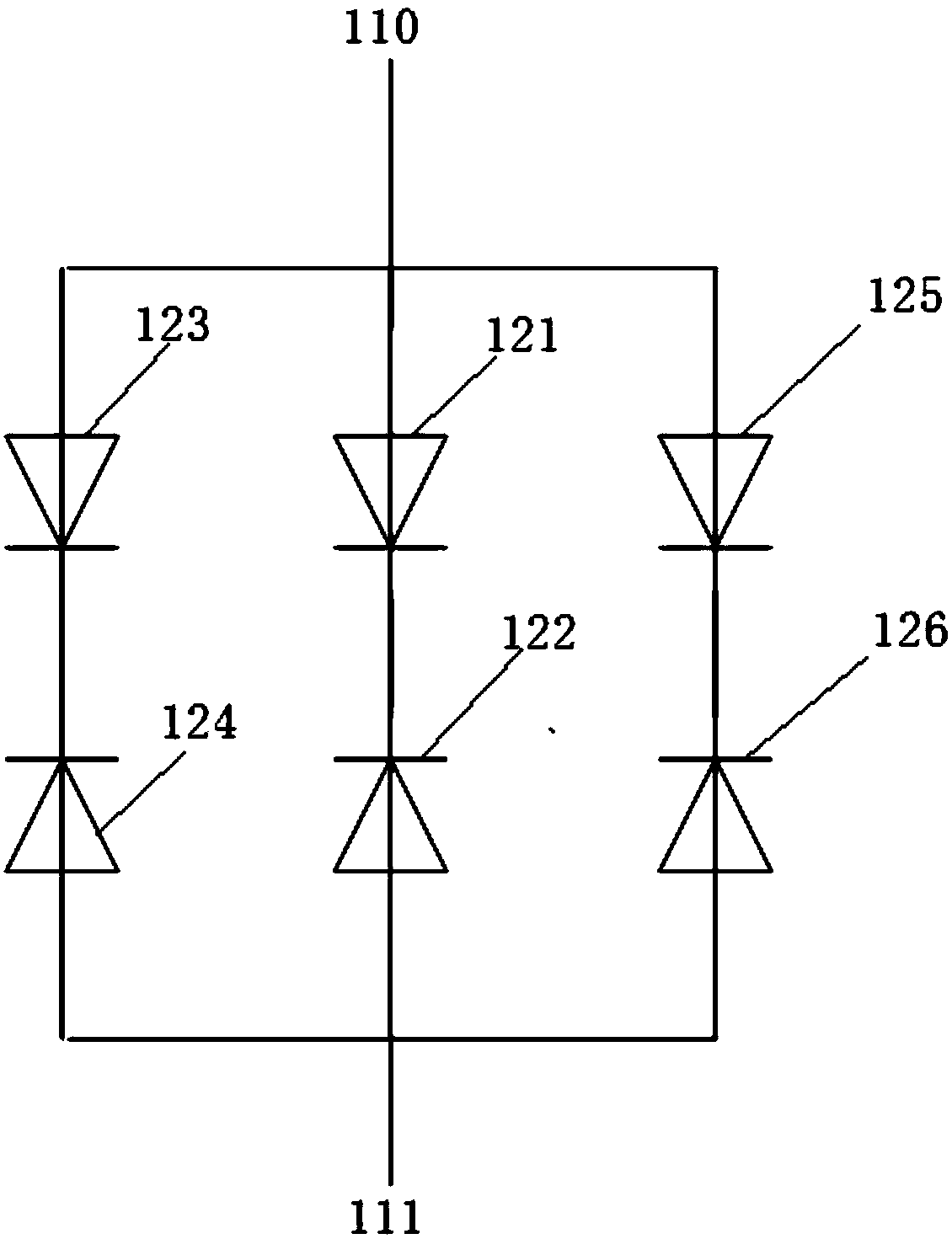

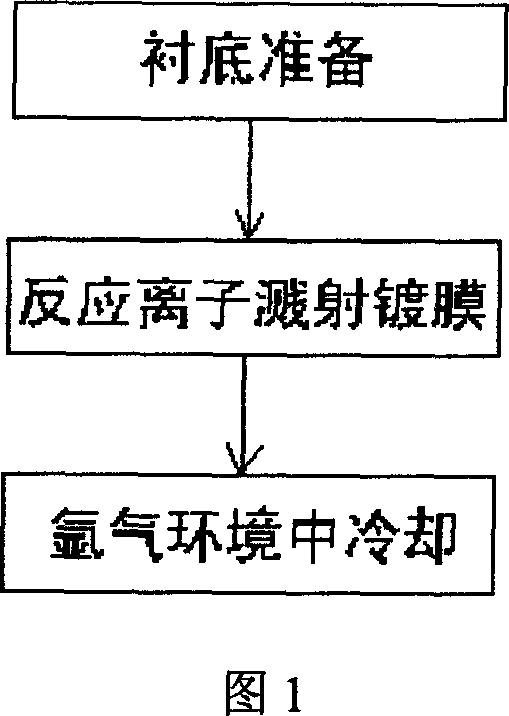

Transient voltage suppressor and fabrication method thereof

InactiveCN108054164AReduce device areaReduce process difficultySolid-state devicesSemiconductor/solid-state device manufacturingTransient voltage suppressorEngineering

The invention provides a transient voltage suppressor and a fabrication method thereof. The transient voltage suppressor comprises a P-type substrate, an N-type epitaxial layer, a first groove, a second groove, a first P-type diffusion region, a second P-type diffusion region, P-type epitaxial layers, an N-type injection region and a P-type injection region, wherein the N-type epitaxial layer is formed on the P-type substrate, the first groove and the second groove are formed in a surface of the N-type epitaxial layer, the first P-type diffusion region is formed on a surface of the first groove, the second P-type diffusion region is formed on a surface of the second groove, the P-type epitaxial layers are formed in the first groove and the second groove and on the N-type epitaxial layer, the N-type injection region penetrates through the P-type epitaxial layer and extends to the N-type epitaxial layer between the first groove and the second groove, and the P-type injection region is formed on a surface of the N-type injection region.

Owner:NANJING LISHUI HIGH-TECH VENTURE CAPITAL MANAGEMENT CO LTD

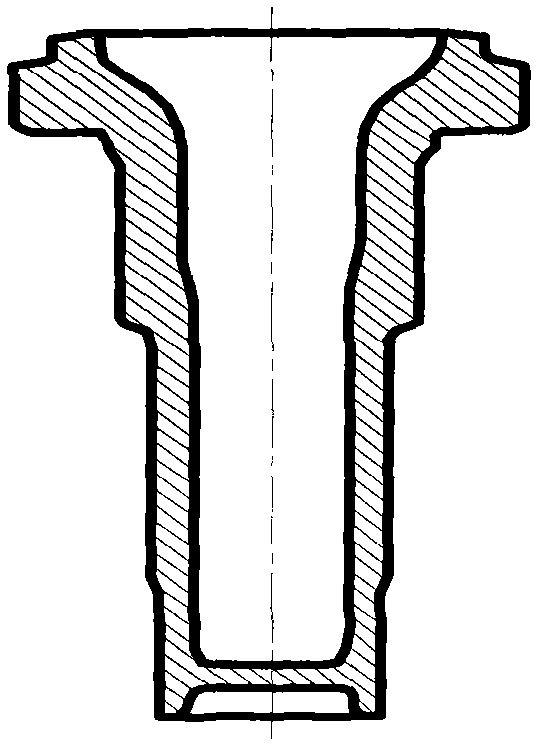

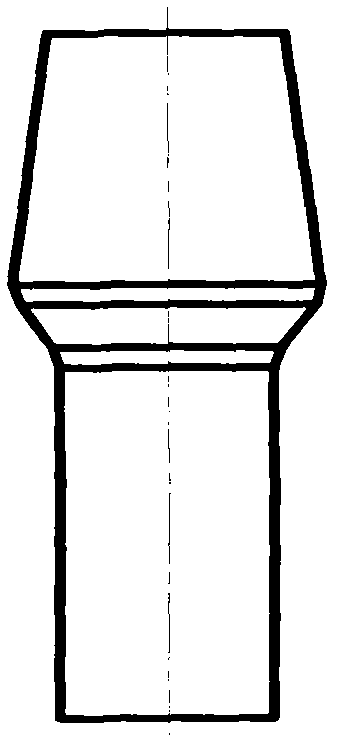

Method for producing thick-wall hollow valve cores of large-scale ball valves

The invention discloses a method for producing thick-wall hollow valve cores of large-scale ball valves. The method comprises the following specific steps of: a. selecting a steel plate as a material; b. rolling the thick steel plate selected in the step a into a circular pipe shape so as to finally obtain a thick-wall seamed steel pipe; c. respectively chamfering the outer walls of two orifices of the steel pipe obtained in the step b into circular conical surfaces; d. pre-pressing the outer walls of the two orifices of the steel pipe obtain in the step c into arc-shaped surfaces; and e. arranging an upper die and a lower die on a press, placing the steel pipe obtained in the step d in the lower die, and combining and pressurizing the upper and lower dies to obtain a finished thick-wall hollow valve core. According to the method, the complicated computing and lofting are not required and the splicing and the welding are also not required, so that the process is markedly simplified, the process difficulty is reduced, the product precision is reliably ensured, the processing cost is reduced, and excellent technological and economical values are provided, so that the method is suitable to large-scale popularization and application.

Owner:张轩

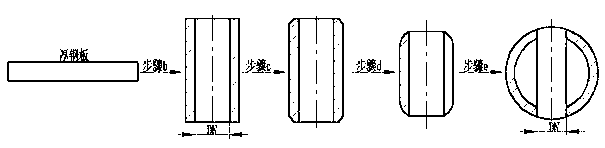

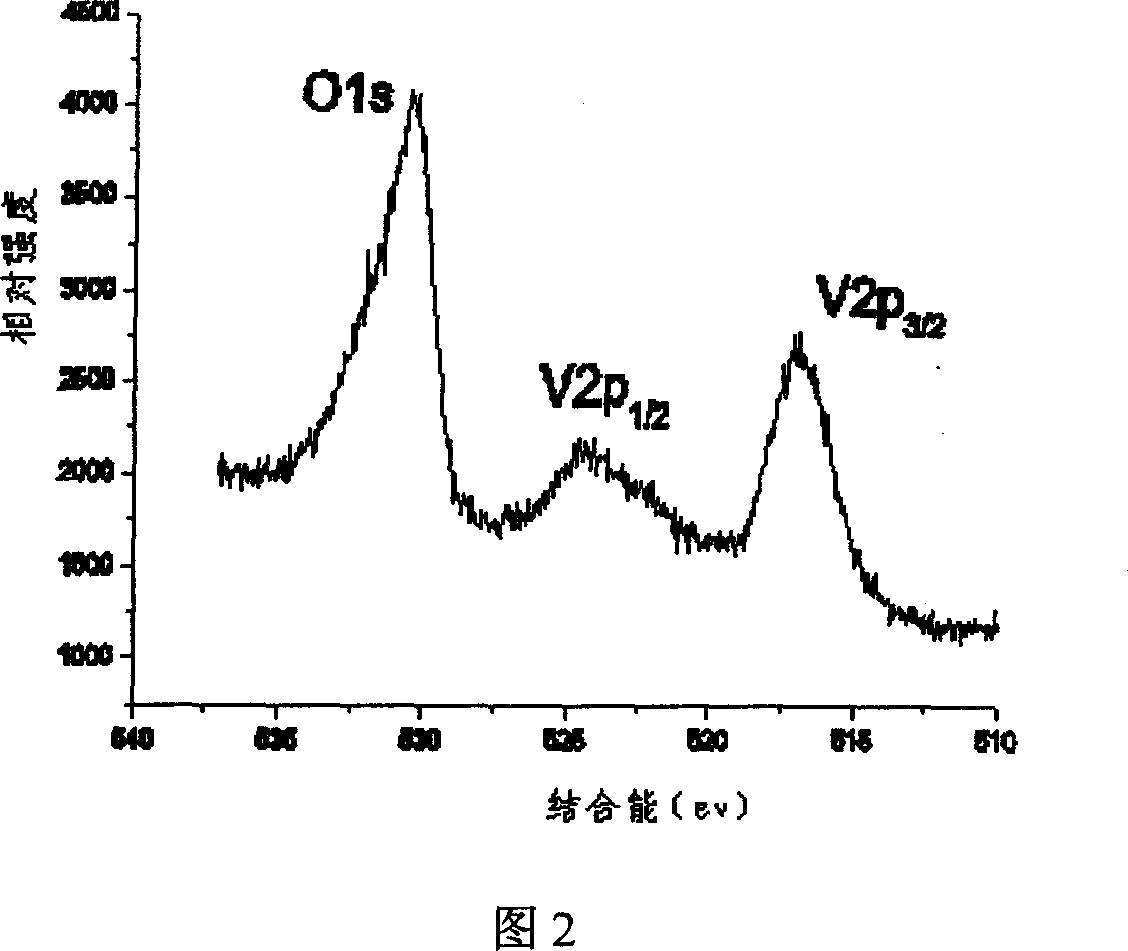

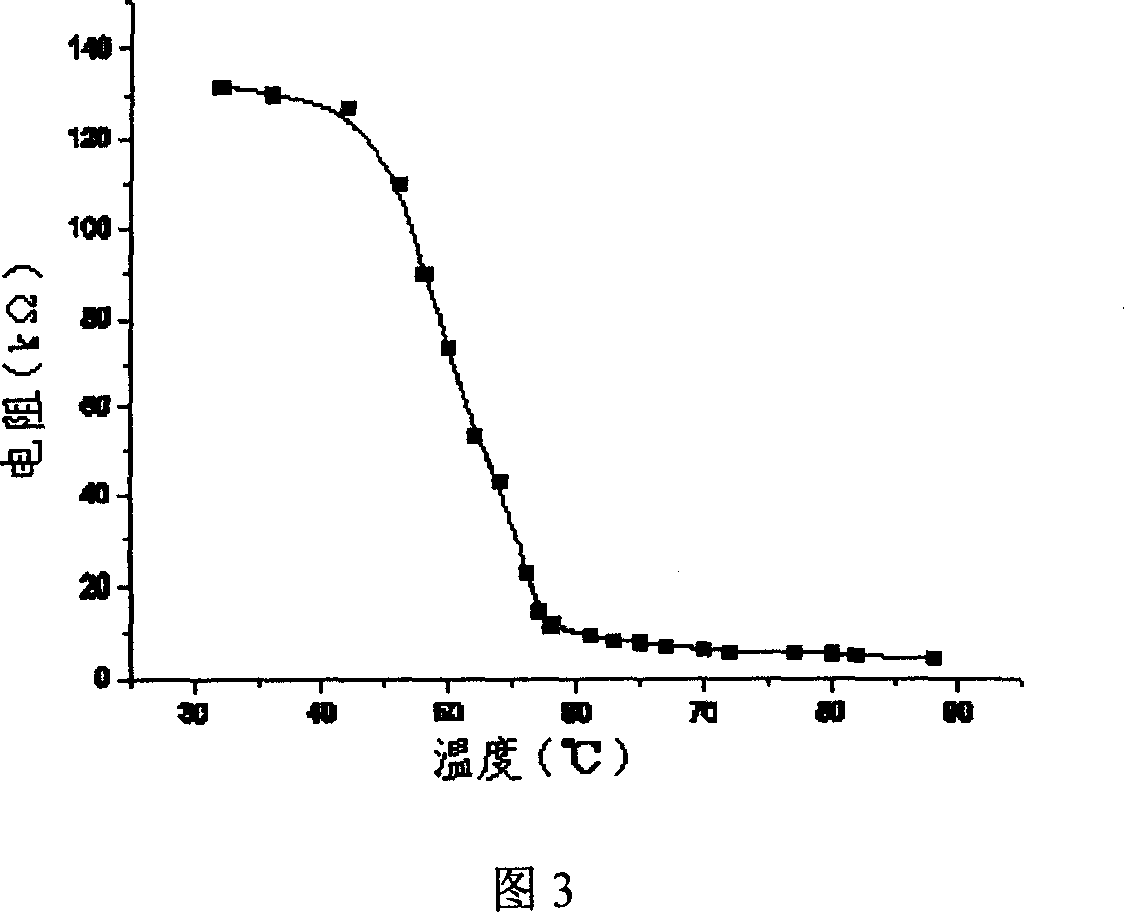

Process for preparing vanadium oxide film

InactiveCN1966758AReduce process difficultyHigh repeatabilityVacuum evaporation coatingSputtering coatingTemperature coefficientVanadium dioxide

A method for producing vanadium oxide film belongs to the field of electronic material technology, specifically relates to a method for producing vanadium oxide film. The invention adopts reaction ions sputtering coating technology to produce the film through strictly controlling the discharge of the reaction gas to reduce the production difficulty, improve the repeatability. Mixed phase polycrystal vanadium oxide film with vanadium oxide as the base and good performances can be produced through the method of the invention. The resistance-temperature coefficient can reach to over 3% at 30DEG C.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

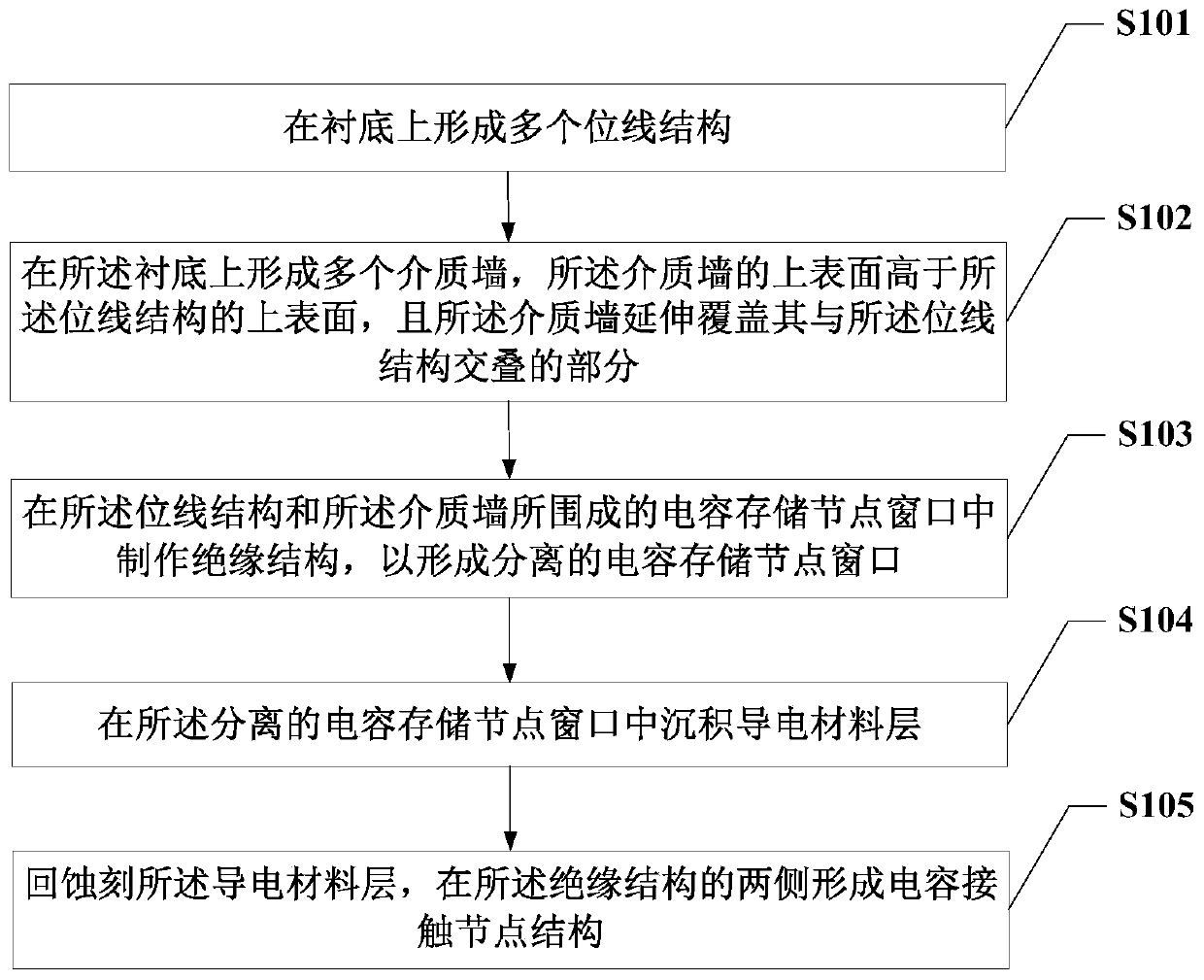

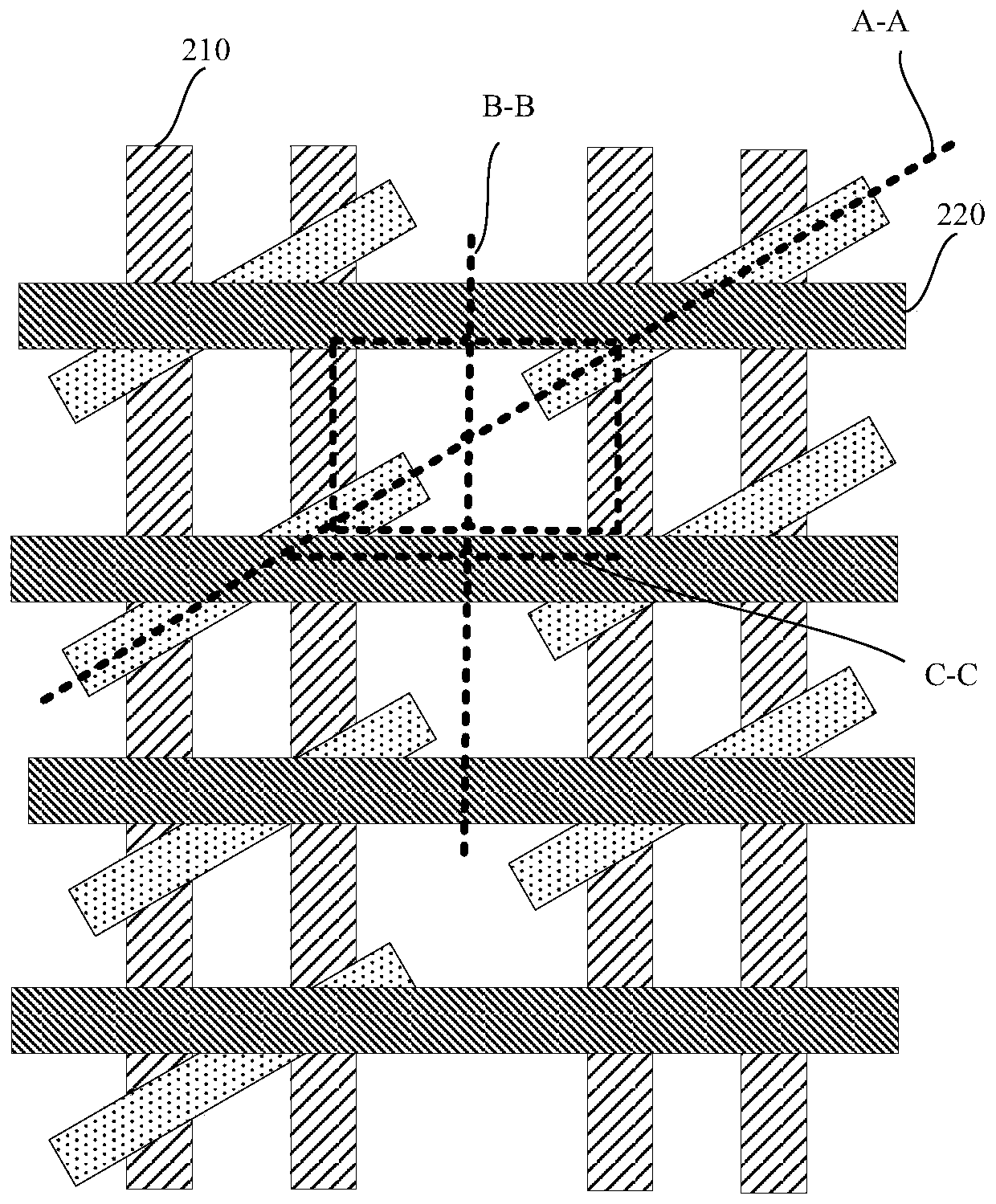

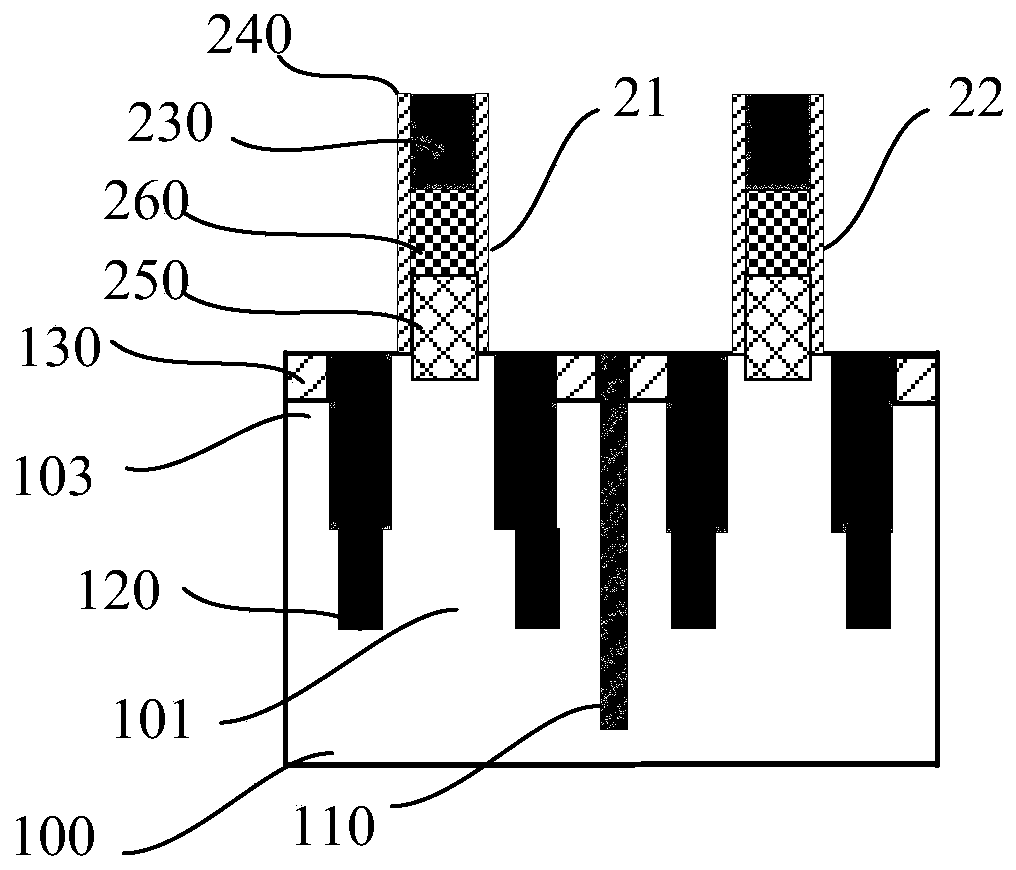

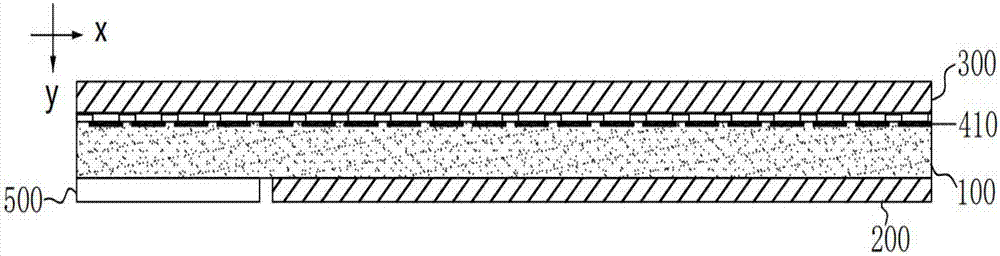

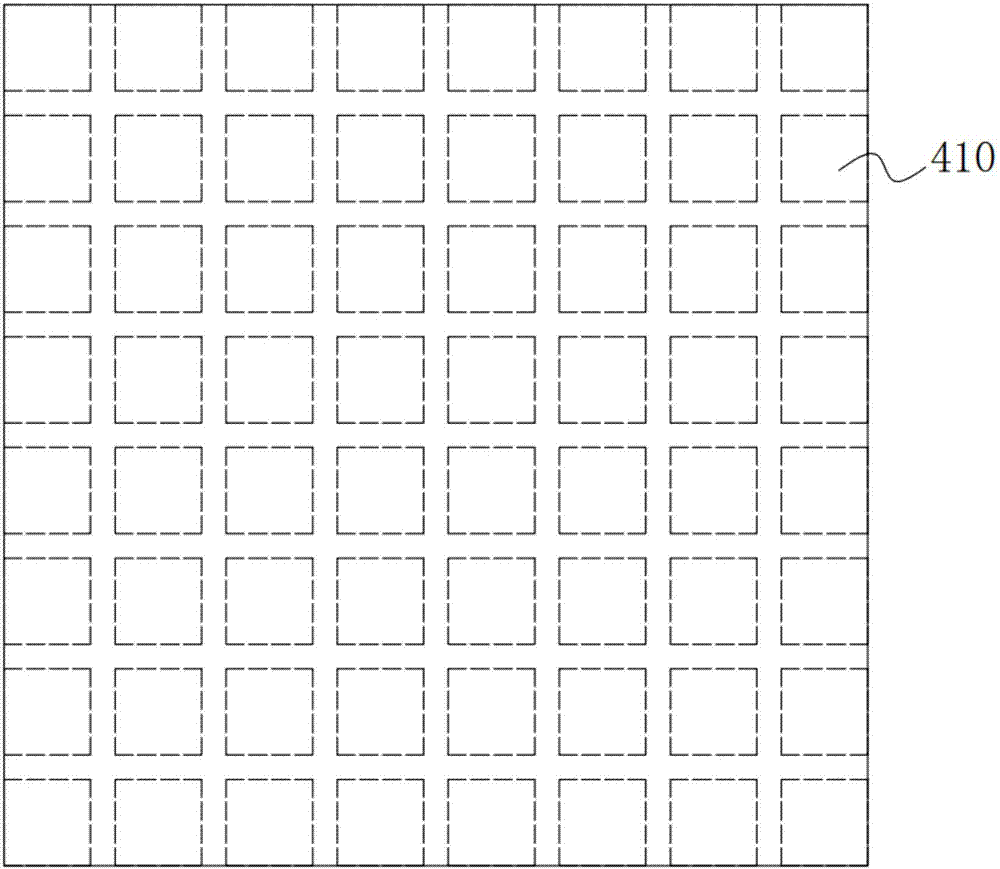

Semiconductor structure and manufacturing method thereof

PendingCN110970436AImprove yieldReduce process difficultyTransistorSemiconductor/solid-state device manufacturingPhysicsElectrically conductive

The invention provides a semiconductor structure manufacturing method, which is applied to the technical field of manufacturing of capacitor contact nodes of memories. The method at least comprises the following steps of: forming a plurality of bit line structures on a substrate; forming a plurality of dielectric walls on the substrate, wherein the upper surfaces of the dielectric walls are higherthan the upper surfaces of the bit line structures, and the dielectric walls extend to cover the parts, overlapped with the bit line structures, of the dielectric walls; manufacturing an insulating structure in a capacitor storage node window defined by the bit line structures and the dielectric walls to form a separated capacitor storage node window; depositing a conductive material layer in theseparated capacitor storage node window; and etching back the conductive material layer, and forming capacitor contact node structures on the two sides of the insulating structure. The invention alsoprovides a semiconductor structure. By applying the embodiment of the invention, the manufacturing yield of the capacitor contact node structures is improved, so that the problem that the conductivecharacteristic of a circuit is influenced because etched patterns are easy to deviate due to the fact that a thicker polycrystalline silicon layer between storage nodes is etched in the prior art is avoided.

Owner:CHANGXIN MEMORY TECH INC

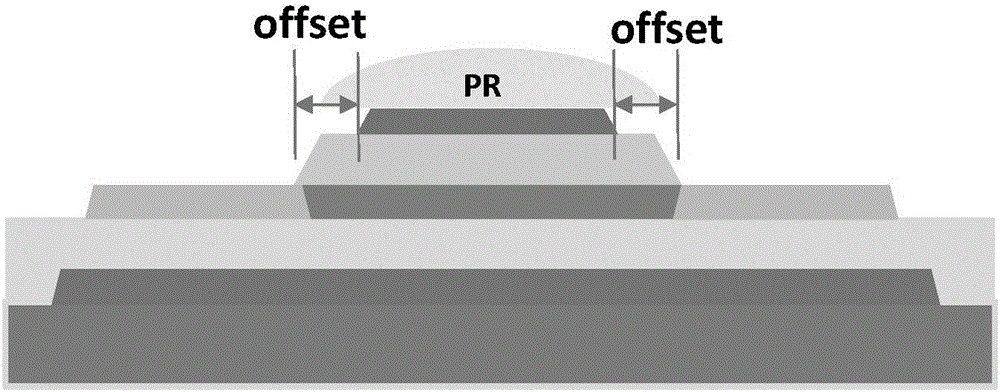

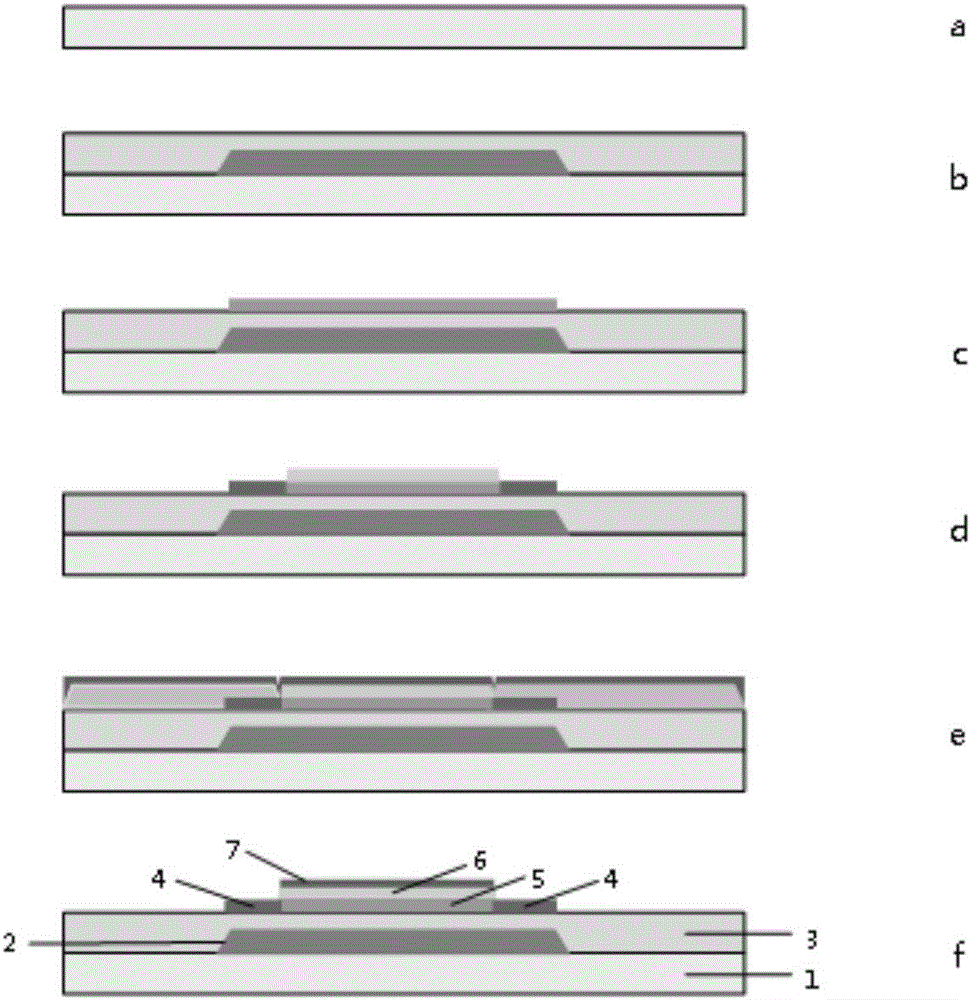

Top gate structure and preparation method thereof, thin film transistor, array substrate and display device

The invention relates to a top gate structure and a preparation method thereof. The top gate structure comprises a gate insulation layer and a gate layer arranged on the gate insulation layer, wherein the gate insulation layer is made of a light-cured organosilicon material. The invention further relates to a thin film transistor comprising the top gate structure, an array substrate and a display device. Through the gate insulation layer made of the light-cured organosilicon material, and through the optimized preparation method, an offset region can be reduced, and the problem of reduction of the electrical performance of the thin film transistor due to enlargement of the offset region and the like is prevented; and the top gate structure has wide application prospect.

Owner:BOE TECH GRP CO LTD

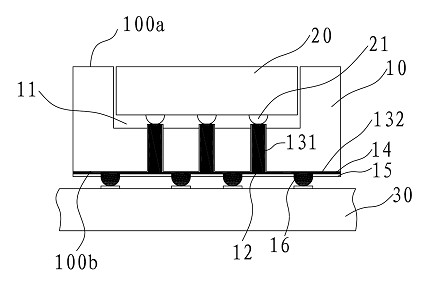

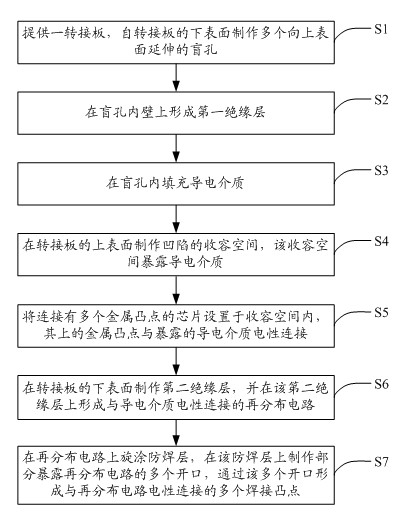

Semiconductor packaging structure and packaging method thereof

ActiveCN102623427AReduce process difficultyReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesEngineeringSalient point

The invention discloses a semiconductor packaging structure and a semiconductor packaging method. The packaging structure comprises a chip, an adapter plate and a plurality of through holes, wherein a plurality of metal salient points are arranged on the chip; an accommodation space is sunken on the upper space of the adapter plate, and the chip is accommodated in the accommodation space; the through holes penetrate through the adapter plate, and are communicated with the accommodation space; a conductive medium is arranged in each through hole, and is electrically connected to a redistribution circuit on the lower surface of the adapter plate; a plurality of solder bumps are arranged on the redistribution circuit; the metal salient points are electrically connected with the conductive medium; and pitches between the solder bumps are greater than those between the metal salient points. The accommodation space capable of accommodating the chip is formed on the adapter plate, so that process difficulty in the packaging of the adapter plate is lowered, and production cost is further decreased.

Owner:CHINA WAFER LEVEL CSP

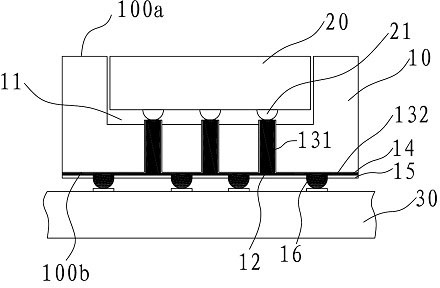

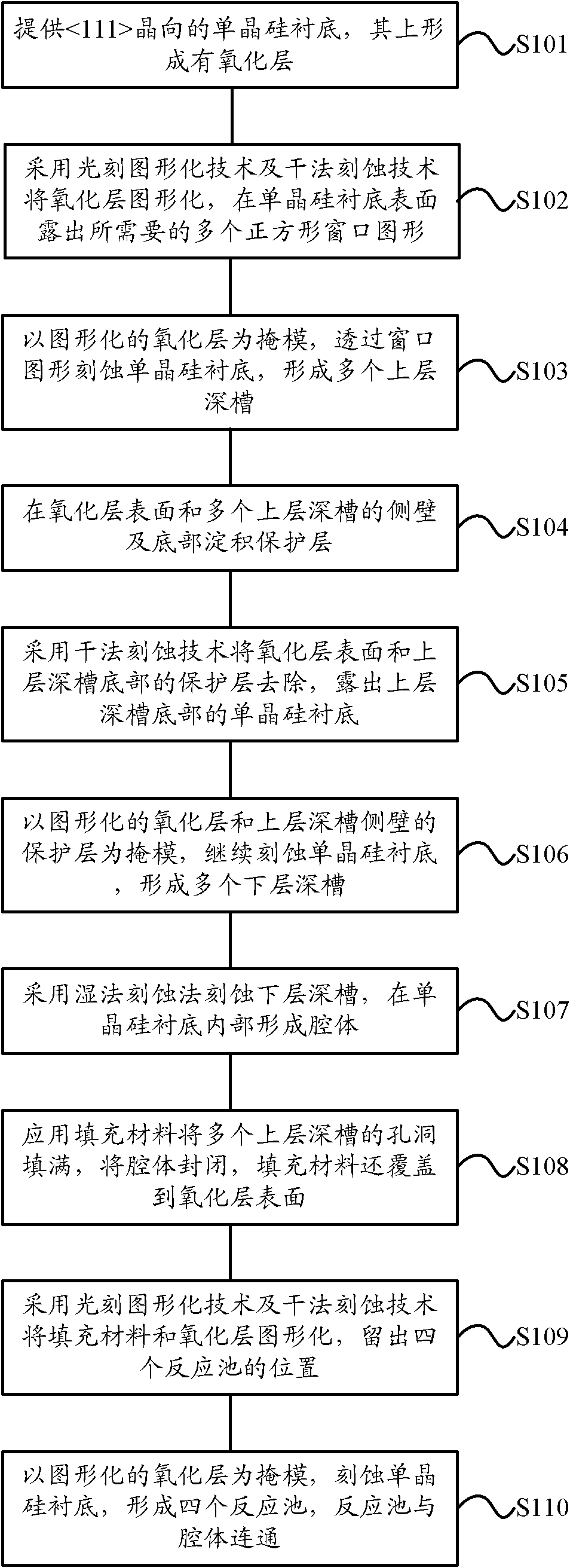

Manufacturing method for cavity of full silica-based microfluidic device

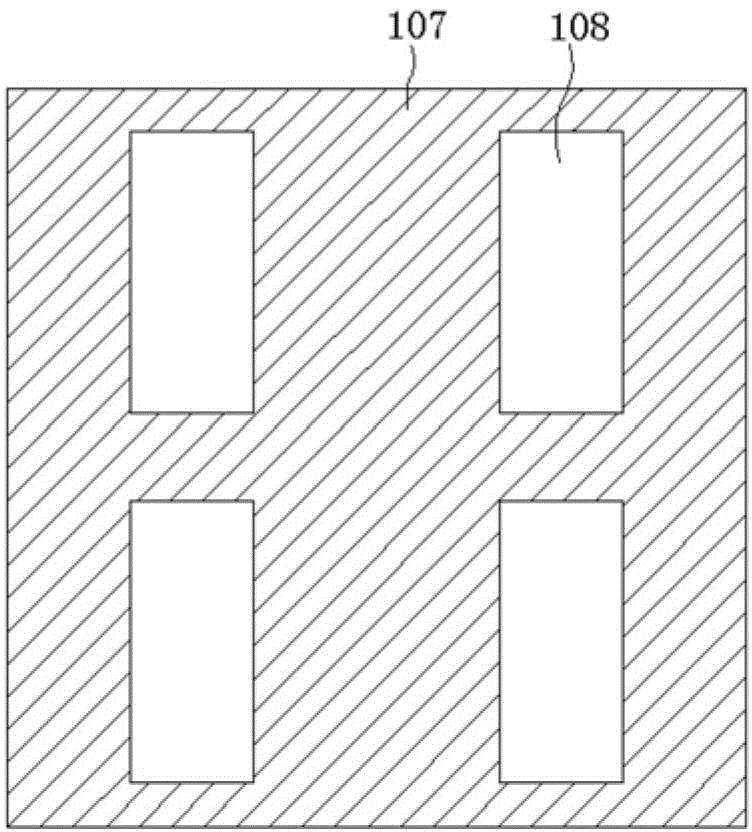

ActiveCN102320558AReduce chip areaReduce process difficultyDecorative surface effectsLaboratory glasswaresEtchingMonocrystalline silicon

The invention provides a manufacturing method for a cavity of a full silica-based microfluidic device, comprising the following steps of: providing (111) a crystal-oriented single crystal silicon substrate, on which an oxide layer is formed; patterning the oxide layer, and exposing a plurality of square window patterns; taking the oxide layer as a mask to etch the silicon substrate so as to form an upper-layer deep groove; depositing protection layers on the surface of the oxide layer and on the sidewalls and the bottom of the upper-layer deep groove; removing the protection layer on the surface of the oxide layer and the protection layer on the bottom of the upper-layer deep groove; taking the protection layers on the oxide layer and the protection layer on the sidewalls of the upper-layer deep groove as masks to etch the silicon substrate so as to form a lower-layer deep groove; etching the lower-layer deep groove through a wet etching method, and forming the cavity in the silicon substrate; fully filling holes of the upper-layer deep groove, and sealing off the cavity; and taking the oxide layer as the mask to etch the silicon substrate so as to form four reaction tanks communicated with the cavity. In the manufacturing method provided by the invention, machining is executed based on a single silicon substrate in the cavity forming process, by a mode of firstly forming a bottom cavity in a layering manner and then filling the deep groove, the cavity can be formed without being related to a silica bonding or gluing technology.

Owner:ADVANCED SEMICON MFG CO LTD

Sewing method of double-embedded-wire pocket

ActiveCN104585947AReduce process difficultyImprove sewing qualityGarmentsClothes making applicancesFlangingEngineering

The invention provides a sewing method of a double-embedded-wire pocket. A pocket center line is drawn in the front side pocket position part of a clothes piece and is used as a positioning line; the rough edge on the top of wire-embedded cloth is downwards flanged for a first distance, the flanged part is subjected to buckling ironing for forming a first flanging line, then, the edge is downwards flanged for a second distance being the twice length of the first distance, and the part which is flanged again is subjected to buckling ironing for forming a second edge flanging line; in the second step, the rough edge, downwards flanged for the first distance, of the wire-embedded cloth is aligned with the center line of the pocket, a press foot with the same width as the first distance is adopted for sewing a first embedded wire in the middle position of the flanged edge with the same width as the first distance, and during the sewing, the lower edge of the press foot is aligned with the positioning line; the press foot is adopted for sewing a second embedded wire in the middle position between the rough edge of the wire-embedded cloth and the second edge flanging line, during the sewing, the press foot is just pressed on a fabric with the same width as the first distance between the rough edge and the second edge flanging line, and the two sides of the press foot are respectively aligned with the rough edge and the second edge flanging line.

Owner:JIANGXI INST OF FASHION TECH

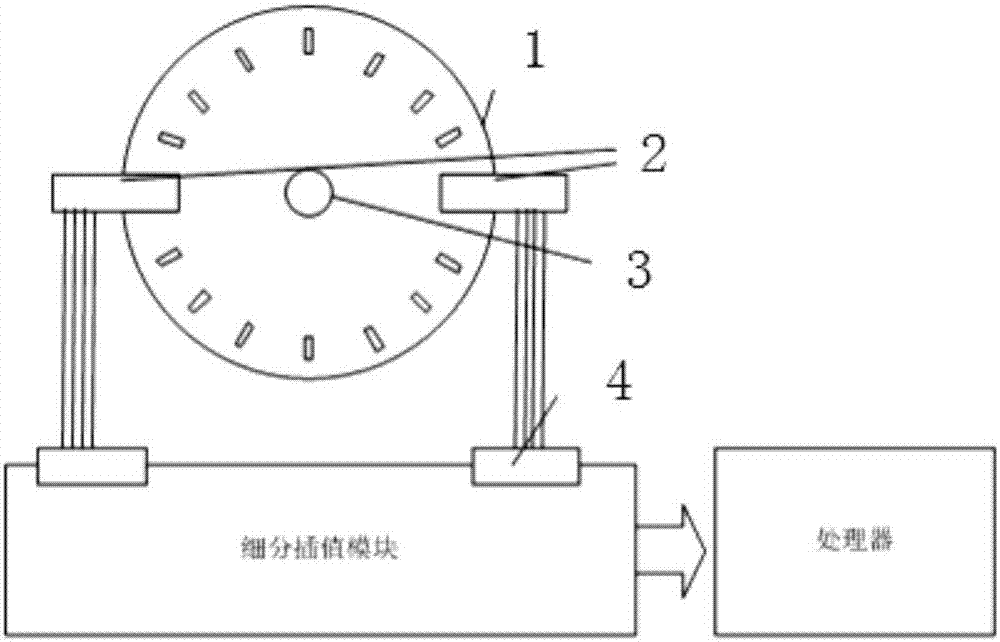

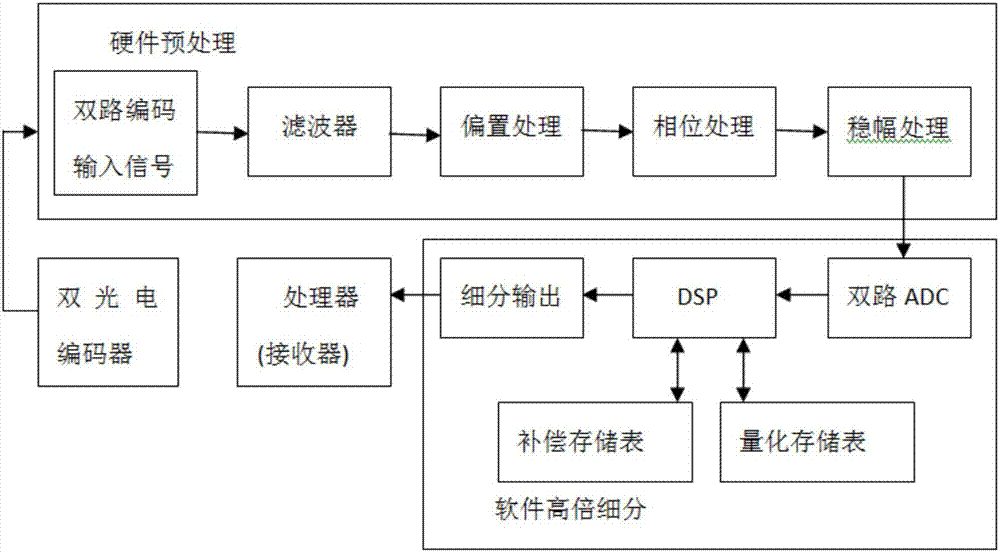

Compensation subdividing method and device for high-resolution, high-precision and dual-photoelectric encoder

ActiveCN107421569AReduce process difficultyHigh resolutionConverting sensor outputMotor driveEngineering

The invention discloses a compensation subdividing method and a device for a high-resolution, high-precision and dual-photoelectric encoder. The device comprises a photoelectric coding disk, a motor, a dual photoelectric reader and a subdividing difference module. The main rotation shaft of the photoelectric coding disk is coaxially connected with the rotating motor; the motor drives the photoelectric coding disk to rotate; the light emitted by the light emitting device of the photoelectric reader is chopped by the narrow slit of the photoelectric coding disk; a photosensitive device converts the signals formed by the penetrating light and blocking light into corresponding sine analog electrical signals; a subdividing interpolation module carries out high-power subdivision to the signals; and sampling is performed through the use of difference in phase relation of two-channel photoelectric coding signals; and at the same time, jitter compensation is performed for the coding signals.

Owner:CHINA ELECTRONIS TECH INSTR CO LTD

Touch display module and manufacturing method thereof, and touch display apparatus

ActiveCN107193413AAvoid errorsReduce process difficultyInput/output processes for data processingTouch panelBlack matrix

The invention discloses a touch display module and a manufacturing method thereof, and a touch display apparatus. The touch display module comprises a protective coverage layer, a black matrix bezel formed on one side, facing to a display panel, of the protective coverage layer, and a touch panel formed in the black matrix bezel. According to the touch display module, a touch substrate in the touch panel is formed on one side, facing to the display panel, of the protective coverage layer, so that the touch panel and the protective coverage layer are integrated together, a glue material for laminating the protective coverage layer and the touch panel is removed, and an error of laminating the protective coverage layer and the touch panel is avoided; and the touch panel also has a protective effect for the protective coverage layer.

Owner:BOE TECH GRP CO LTD

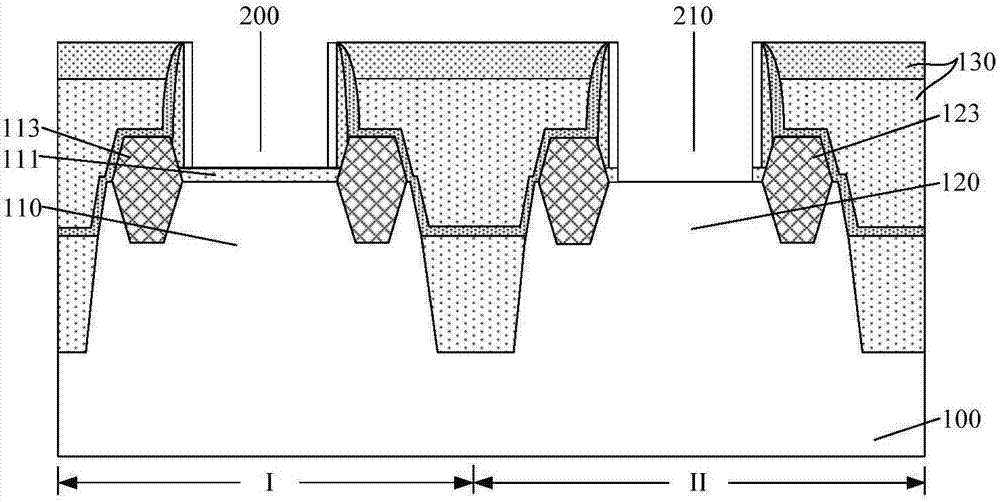

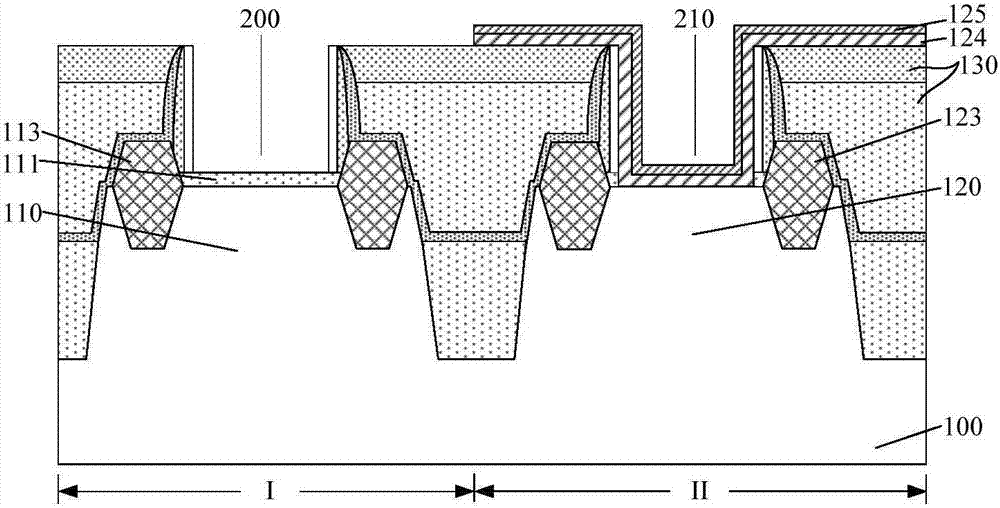

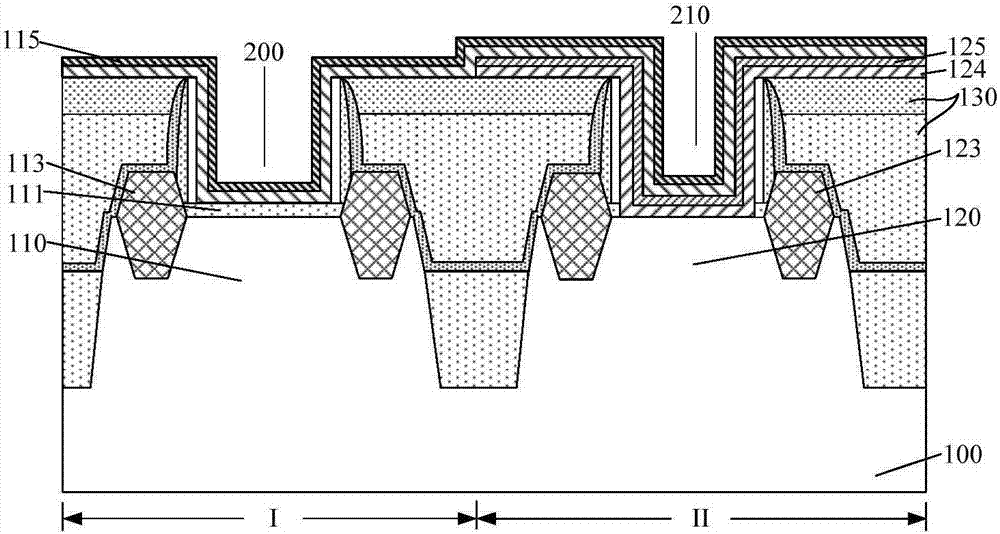

Semiconductor structure and manufacturing method thereof

ActiveCN107346783AReduce process difficultyAvoid voidsSemiconductor/solid-state device manufacturingSemiconductor devicesWork functionSemiconductor structure

The invention provides a semiconductor structure and a manufacturing method thereof. The manufacturing method comprises the steps of: providing a substrate comprising a first region and a second region; forming an interlayer dielectric layer on the substrate; forming a first opening through which the substrate is exposed in the interlayer dielectric layer in the first region, and forming a second opening through which the substrate is exposed in the interlayer dielectric layer in the second region; forming gate dielectric layers on the bottom part and the side wall of the first opening as well as that of the second opening; forming a second work function layer on the gate dielectric layer in the second region; converting a partial thickness of the second work function layer into a barrier layer; forming a first work function layer on the gate dielectric layer in the first region and the barrier layer in the second region; and forming a metal layer which fills up the first opening and the second opening. According to the semiconductor structure and the manufacturing method thereof, the partial thickness of the second work function layer is converted into the barrier layer, the barrier layer can prevent metal ions in the first work function layer from diffusing into the second work function layer, and an additional film layer is not introduced, thereby avoiding adverse influence on the performance of the second work function layer.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Fingerprint sensor and driving method thereof

ActiveCN107491774AReduce process difficultySimple processPrint image acquisitionDriven elementFingerprint

The invention discloses a fingerprint sensor and a driving method thereof. The fingerprint sensor comprises a chip, a driving element used for emitting ultrasonic signals during starting, a piezoelectric unit arranged on one face of the chip and used for converting the ultrasonic signals reflected by a target finger into electric charge quantity, multiple pixel units which are arranged in an array manner, and at least one signal detection circuit. Each pixel unit comprises a sensor electrode which is electrically connected with the piezoelectric element. Each signal detection circuit is electrically connected with a corresponding sensing electrode and is used for detecting the electric charge quantity on the sensing electrode, and outputting an electrical signal corresponding to the fingerprint information. Thus, simplification of manufacturing technique of the fingerprint sensor is achieved and an effect of power consumption reduction is achieved.

Owner:MICROARRAY MICROELECTRONICS CORP LTD

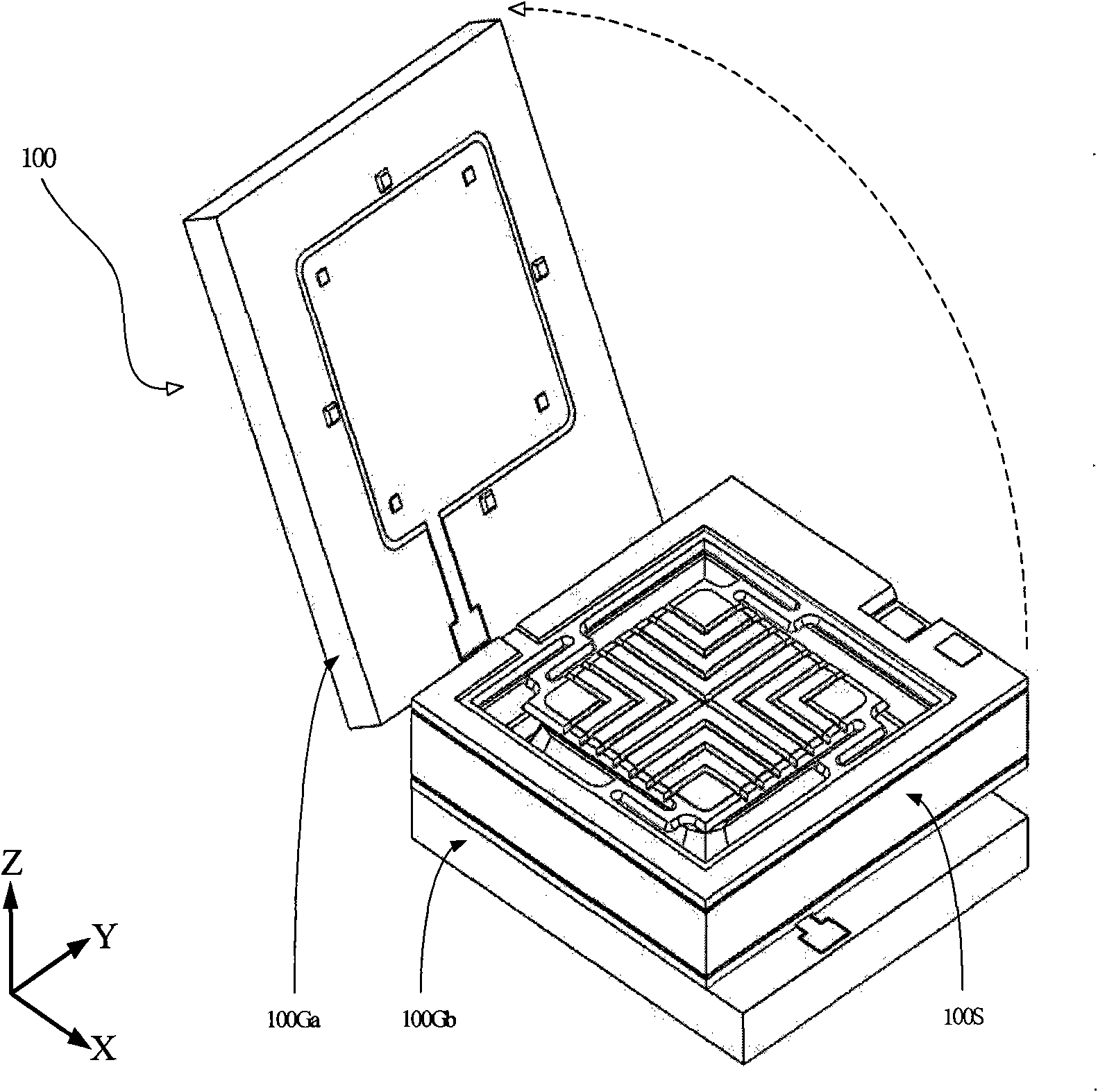

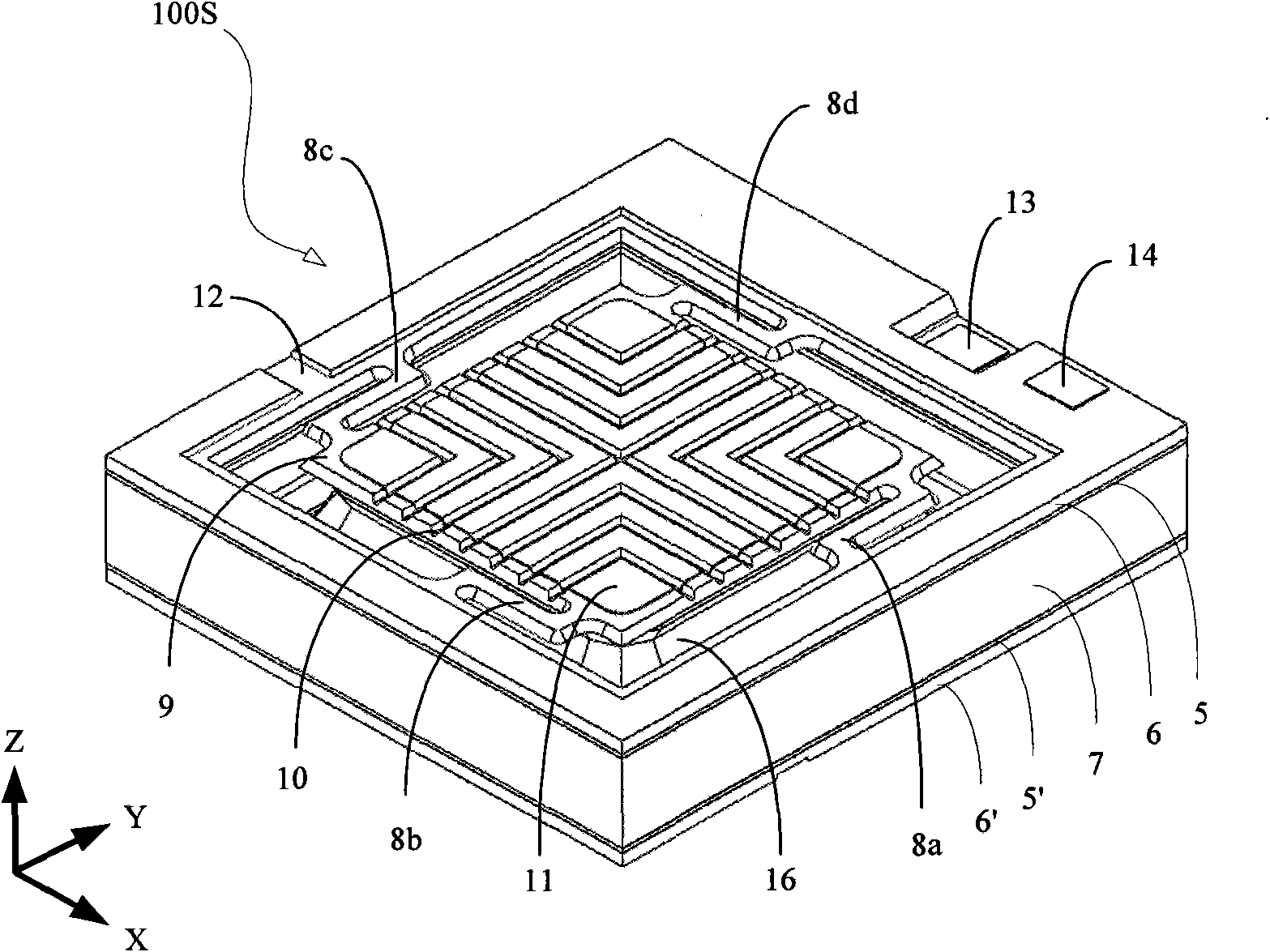

MEMS wafer level vacuum packaging structure and method

InactiveCN104986720AGuaranteed tightnessReduce process difficultyPrecision positioning equipmentDecorative surface effectsEutectic bondingAnodic bonding

The invention discloses an MEMS wafer level vacuum packaging structure and method. The packaging structure comprises an insulation substrate, an MEMS chip structural layer and a cover plate, and the above components are connected through a wafer level bonding mode to form a vacuum cavity. The center of a first bonding ring is provided with a second bonding ring which is not totally closed, two types of bonding modes can be achieved in the same technical condition, because the bonding temperatures of anode bonding, gold and silicon eutectic bonding, hot pressing bonding or adhesion bonding are similar, so a vacuum packaging structure and metal wires can be transversally connected. In addition, the designed second bonding ring is slightly higher than the first bonding ring to make two bonding ring fully contact with each other during bonding, the second bonding ring is not totally closed, so on the one hand, metal wires can be transversally connected, and on the other hand, the vacuum cavity can be separated from the external environment, to make sure that the vacuum cavity is sealed. The MEMS wafer level vacuum packaging structure and method are simple in technology, the reliability and yield of device can be raised, and the application of MEMS wafer level vacuum packaging technology in a large scale scope can be promoted.

Owner:CHONGQING UNIV

Glass passivation method for silicon mesa diodes

ActiveCN105470150AReduce residual volume and residual thicknessReduce process difficultySemiconductor/solid-state device manufacturingGlass corrosionSintering

The invention discloses a glass passivation method for silicon mesa diodes. The glass passivation method for silicon mesa diodes sequentially comprises the following steps: preparation of glass frit, glass coating, residual mesa top glass elimination, glass sintering and forming. The preparation proportion of the glass frit is optimized, mesa top glass is removed by an adhesion removal method, then a glass sintering process is carried out, difficulty of the process of eliminating the mesa top glass is reduced on the premise of achieving the ideal passivation effect, and the time of the process is shortened. According to a glass passivation device manufactured by the method, mesa top glass corrosion time can be shortened effectively, quality and precision of electrode window graphs are improved, the technology is simple and feasible, and production cost is reduced.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

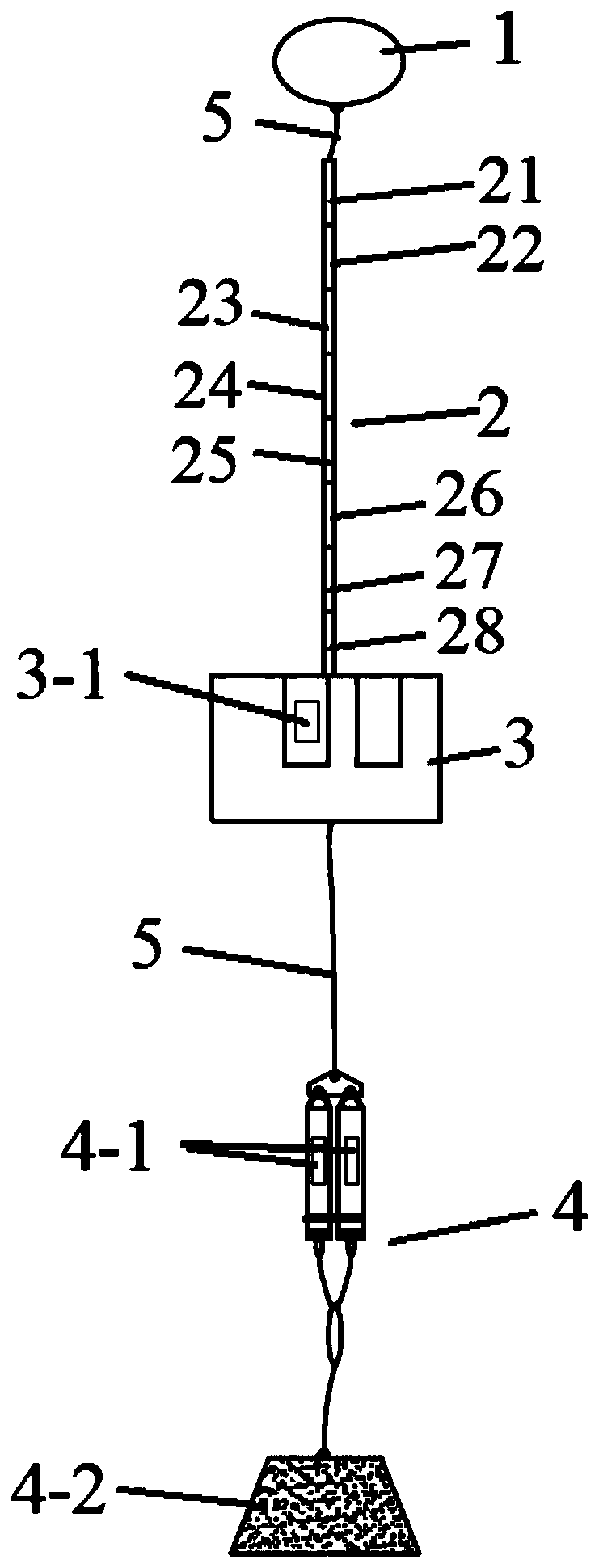

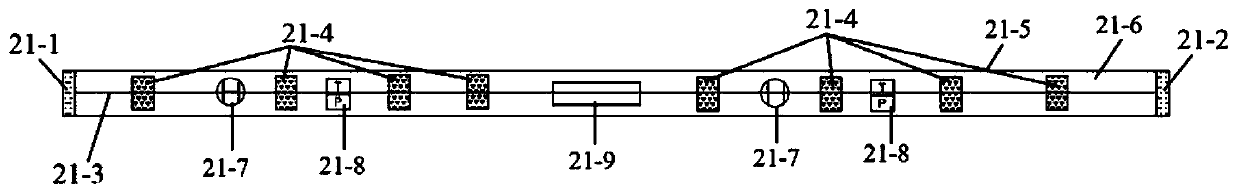

Marine environment information subsurface buoy device based on multi-parameter sensor

ActiveCN111071390AConvenient post-maintenance and repairReduce process difficultyWaterborne vesselsBuoysSeawaterVertical array

The invention discloses a marine environment information subsurface buoy device based on a multi-parameter sensor. The marine environment information subsurface buoy device mainly comprises a pressure-resistant floating ball, a measuring vertical array, a subsurface buoy system and an anchoring system which are sequentially connected from top to bottom. The measuring vertical array is formed by movably connecting a plurality of sub-sections for acquiring environmental information; a subsurface buoy module is arranged in the subsurface buoy system and used for synchronously storing and measuring data information output by the last subsection of the vertical array. The beneficial effects of the marine environment information subsurface buoy device are as follows: the requirements of design specifications for observing hydrological environment and marine environment noise in medium and shallow sea areas are met; and the device has the capabilities of marine environmental noise measurement, underwater acoustic signal measurement, seawater temperature measurement and seawater pressure measurement. An effective way is provided for measuring the hydrological environment and the marine environment noise level of the marine survey and measurement ship in the medium-shallow sea area, the marine environment noise measurement capacity, the underwater acoustic signal measurement capacity, the seawater temperature measurement capacity and the seawater pressure measurement capacity are enhanced, and the domestication technical level of applying marine instruments is improved.

Owner:THE 715TH RES INST OF CHINA SHIPBUILDING IND CORP

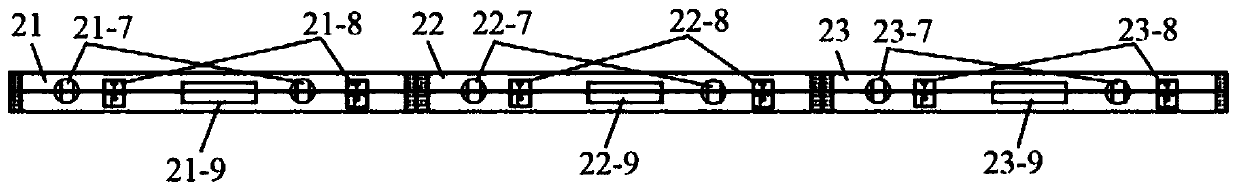

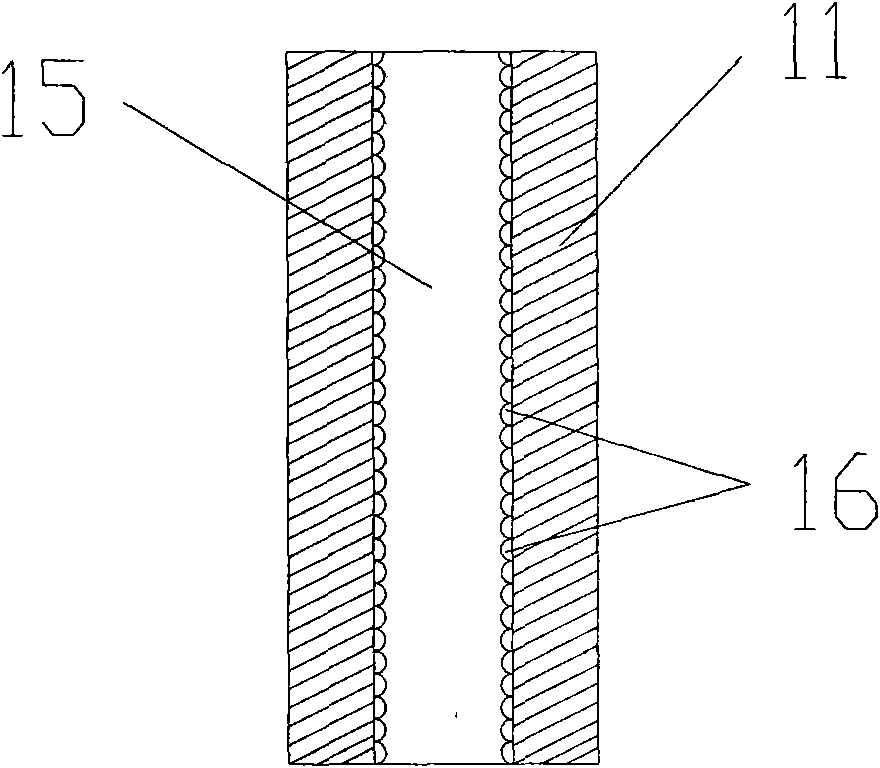

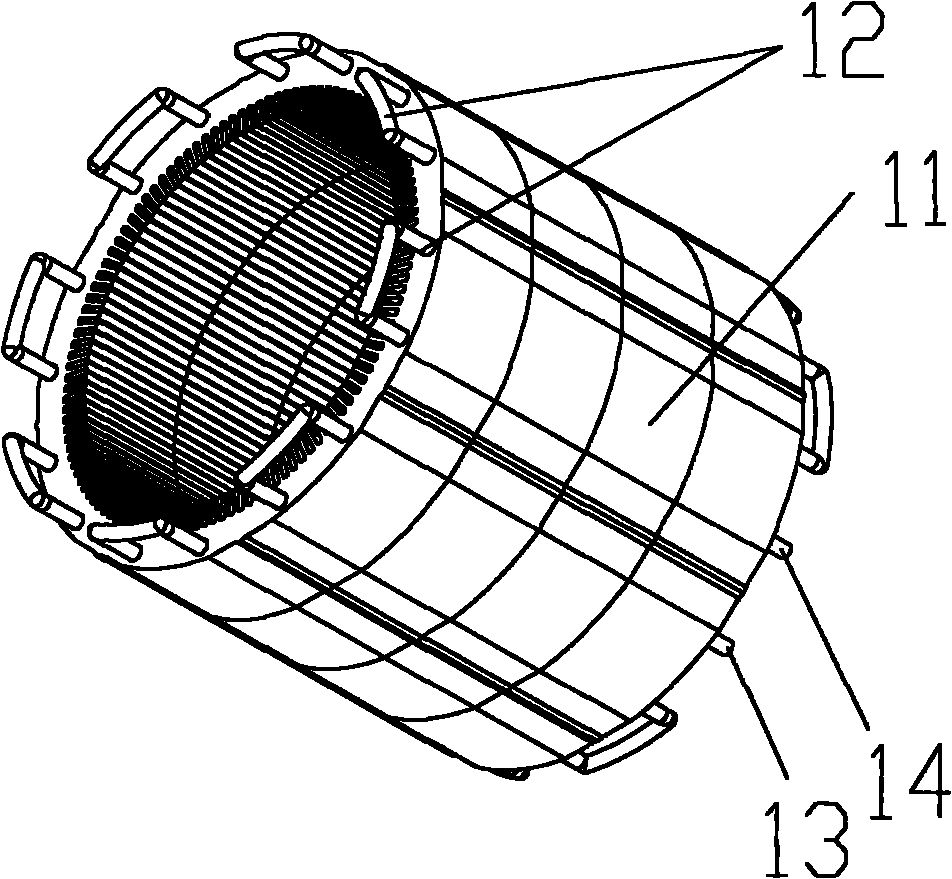

Motor cooling system and motor with same

InactiveCN101989781ASimple structureReduce process difficultyMagnetic circuit stationary partsCooling/ventillation arrangementStatorEngineering

The invention relates to a motor cooling system which comprises a stator core and a cooling circuit, wherein a plurality of mutually separated axial through holes are arranged on the stator core, and the cooling circuit passes through the plurality of through holes on the stator core, and comprises a coolant inlet and a coolant outlet. The invention also discloses a motor with the cooling system. In the invention, by the cooling circuit passing through the stator core, the coolant in the cooling circuit flows through the whole stator core and carries away heat, thereby realizing cooling the whole stator core.

Owner:SHENZHEN INOVANCE TECH

Method for manufacturing integrated circuit

ActiveCN103489830AReduce process difficultyImprove process development andTransistorSemiconductor/solid-state device manufacturingIntegrated circuitEngineering

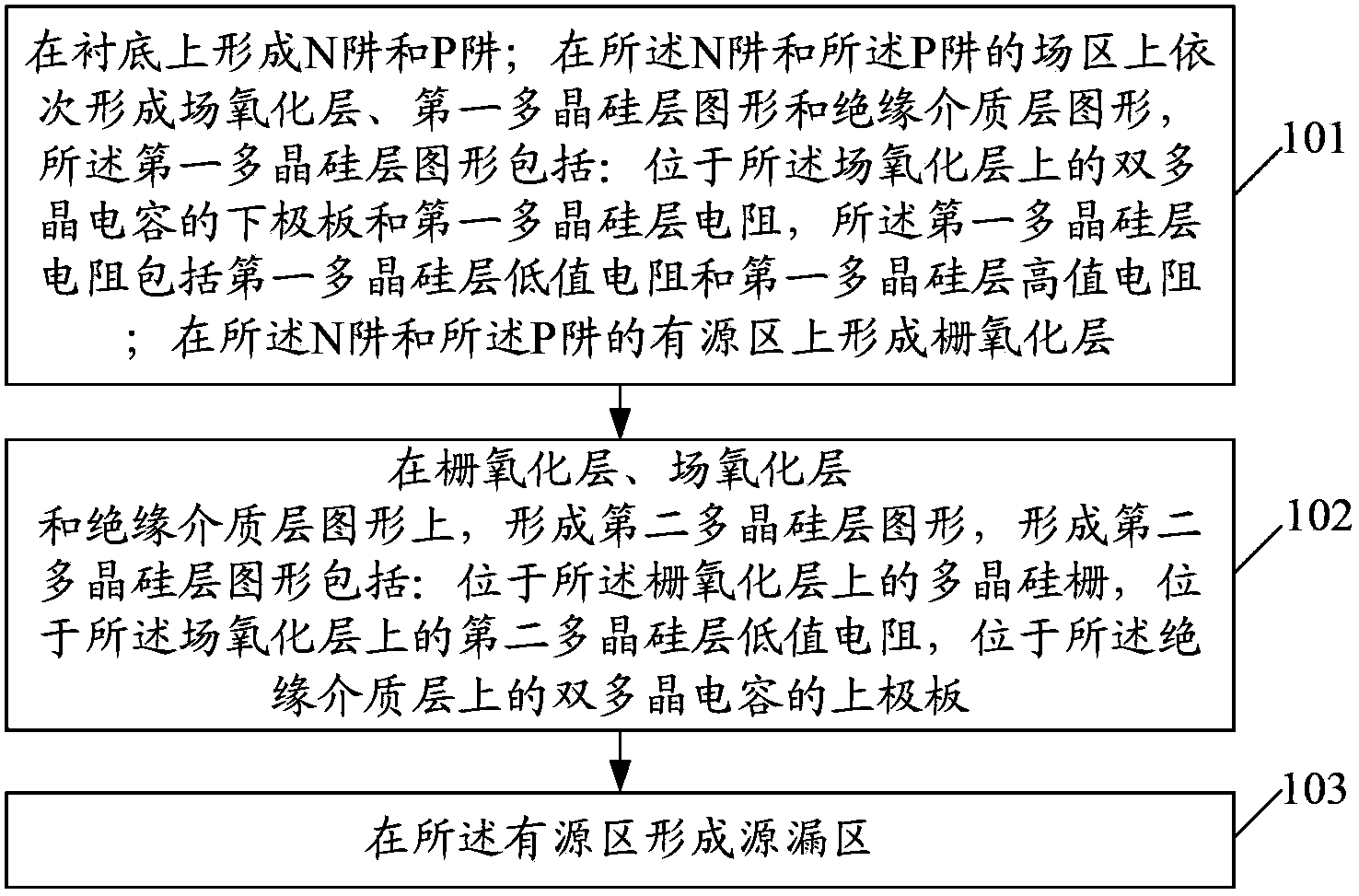

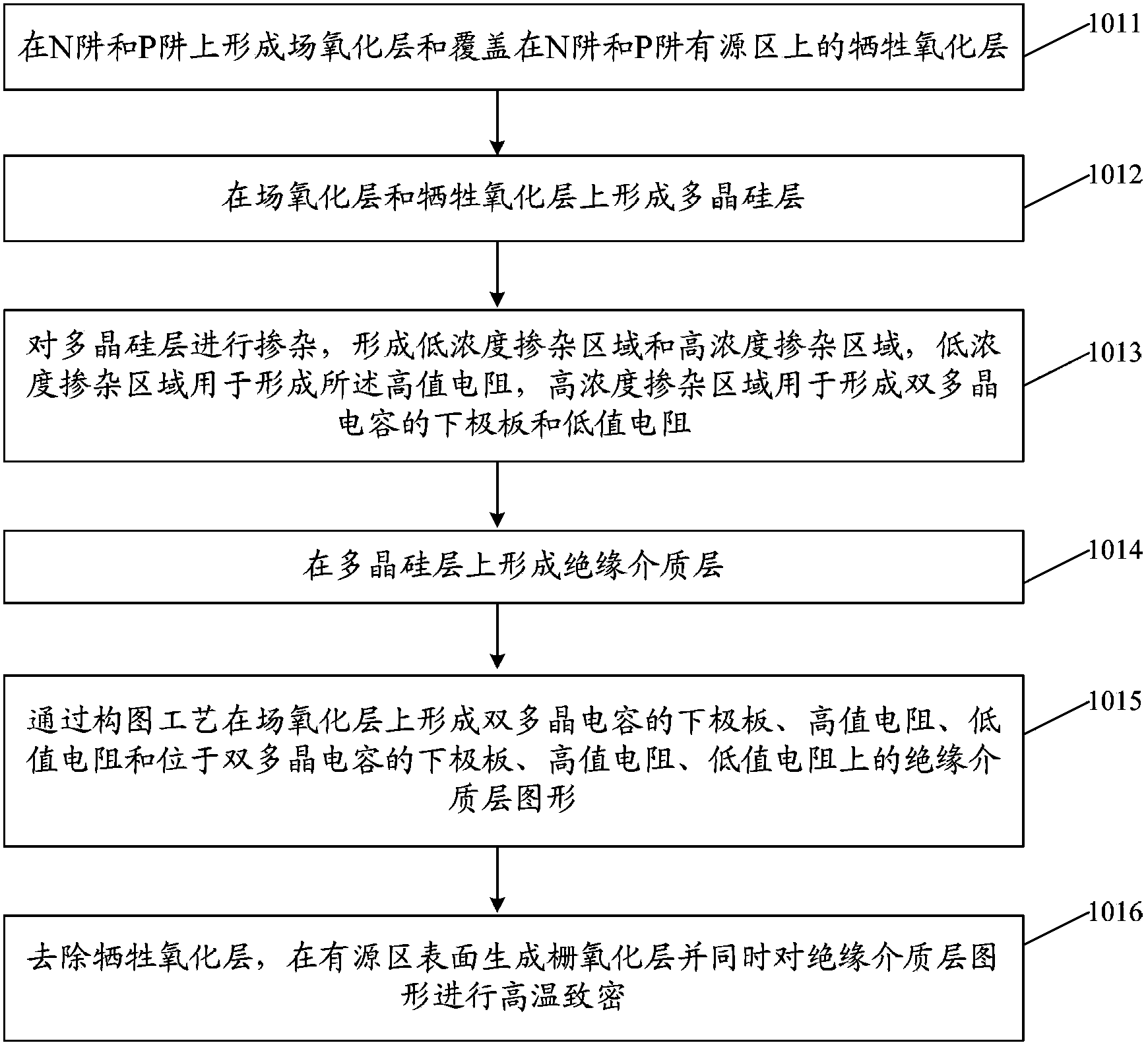

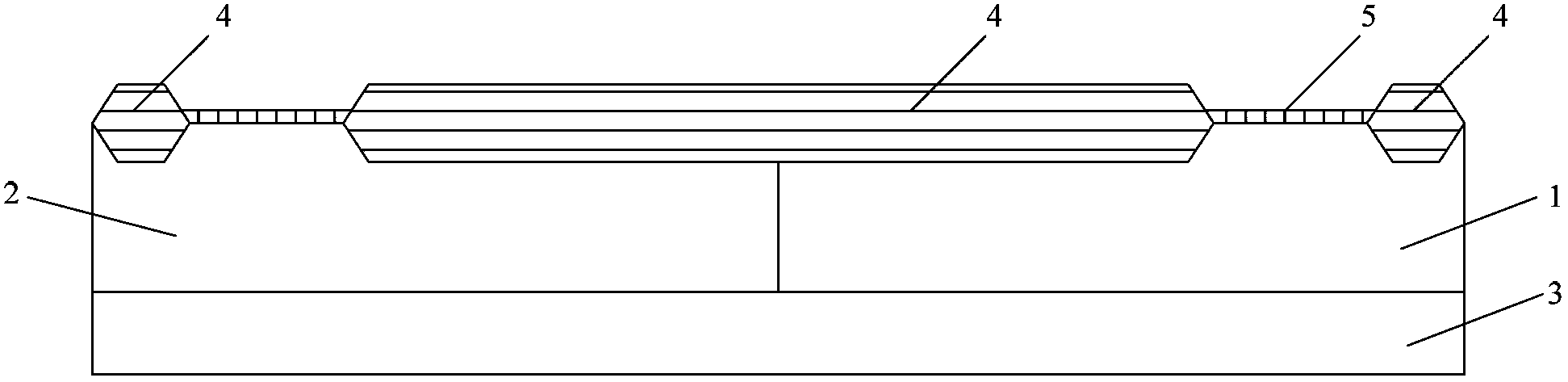

The invention provides a method for manufacturing an integrated circuit and relates to the field of integrated circuit manufacture. The method can reduce the process difficulty and improve the flexibility of integrated circuit process development and integrated circuit design. The method for manufacturing an integrated circuit comprises the following steps: forming an N well and a P well on a substrate; sequentially forming a field oxide layer, a first polycrystalline silicon layer pattern and an insulating medium layer pattern respectively on field regions of the N well and the P well, wherein the first polycrystalline silicon layer pattern includes a lower electrode plate of a double polycrystalline silicon capacitor located on the field oxide layer, and a first polycrystalline silicon layer resistor; forming a gate oxide layer on active regions of the N well and the P well; forming a second polycrystalline silicon layer pattern on the gate oxide layer, the field oxide layer and the insulating medium layer pattern, wherein the second polycrystalline silicon layer pattern includes a polycrystalline silicon gate located on the gate oxide layer, a second polycrystalline silicon layer low-value resistor located on the field oxide layer, and an upper electrode plate of the double polycrystalline silicon capacitor located on the insulating medium layer; and forming a source and drain regions in the active regions.

Owner:FOUNDER MICROELECTRONICS INT