Super junction semiconductor element and manufacture method thereof

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of affecting device reliability, high cost, and high process difficulty, avoiding excessive epitaxy times and reducing warpage. , the effect of reducing the difficulty of the process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

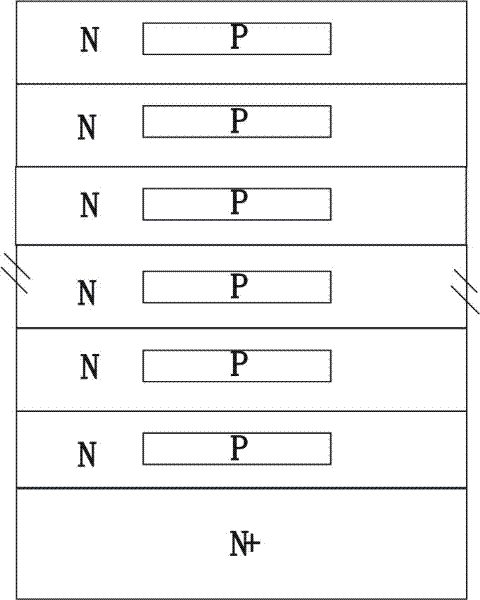

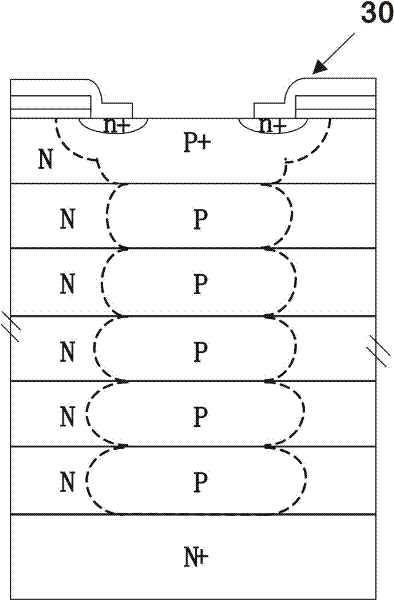

[0026] refer to Figure 12 , a super junction semiconductor element, comprising: a first conductivity type substrate 11; at least one layer of a first conductivity type first epitaxial layer 12 disposed on the first conductivity type substrate, the first epitaxial layer comprising The second conductivity type doping 122; the first conductivity type second epitaxial layer 13 disposed on the first conductivity type first epitaxial layer; the second epitaxial layer includes the second conductivity type doping 132; the second epitaxial layer A device feature layer 100 is disposed on it.

[0027] A method for manufacturing the above-mentioned super junction semiconductor element, its flow chart is as follows Figure 7 to Figure 12 As shown, it includes: step 1: providing a substrate of the first conductivity type; step 2: growing a first epitaxial layer of the first conductivity type on the substrate of the first conductivity type, and performing doping of the second conductivity ty...

Embodiment 2

[0044] refer to Figure 18 , a super junction semiconductor element, comprising: a substrate of a first conductivity type; a third epitaxial layer of the first conductivity type disposed on the substrate of the first conductivity type, wherein the third epitaxial layer includes doped materials of the second conductivity type heterogeneous; at least one fourth epitaxial layer of the first conductivity type disposed on the first epitaxial layer of the first conductivity type; the fourth epitaxial layer includes doping of the second conductivity type; device features are arranged on the fourth epitaxial layer Floor.

[0045] A method for manufacturing the above-mentioned super junction semiconductor element, comprising: step 1: providing a substrate of the first conductivity type; step 2: growing a third epitaxial layer of the first conductivity type on the substrate of the first conductivity type; layer, and make the second conductivity type doping in the etched groove; Step 3:...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More