Top gate structure and preparation method thereof, thin film transistor, array substrate and display device

A thin-film transistor and top-gate technology, applied in transistors, semiconductor devices, electrical components, etc., can solve problems such as the decline of electrical performance of thin-film transistors, and achieve the effect of reducing process difficulty, reducing manufacturing process, and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

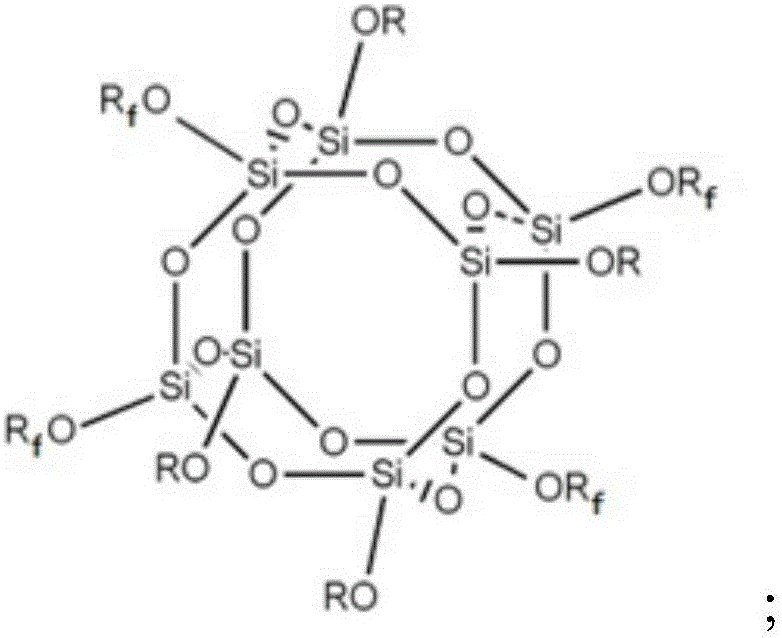

[0046] This embodiment provides a top gate structure, including a gate insulating layer and a gate layer above it, and the gate insulating layer is made of cage polysilsesquioxane;

[0047] The structure of the cage polysilsesquioxane is as follows:

[0048]

[0049] Among them, R represents the photosensitive group R f Represents the hydrophobic group-CF 3 、-CF 2 CF 3 or -CF 2 CF 2 CF 3 .

Embodiment 2

[0051] This embodiment provides a top gate structure, including a gate insulating layer and a gate layer above it, and the gate insulating layer is made of a linear silicone resin;

[0052] The structure of the linear silicone resin is as follows:

[0053]

[0054] Among them, R represents the photosensitive group R f Represents the hydrophobic group-CF 3 、-CF 2 CF 3 or -CF 2 CF 2 CF3 , n is 1, 2 or 3.

Embodiment 3

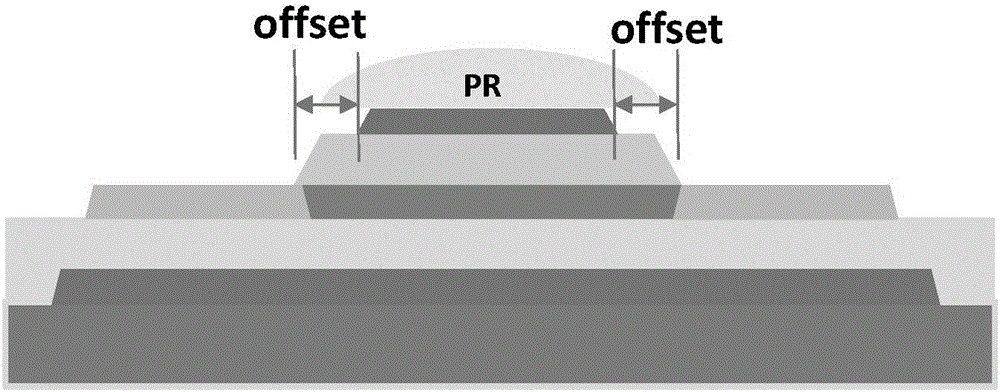

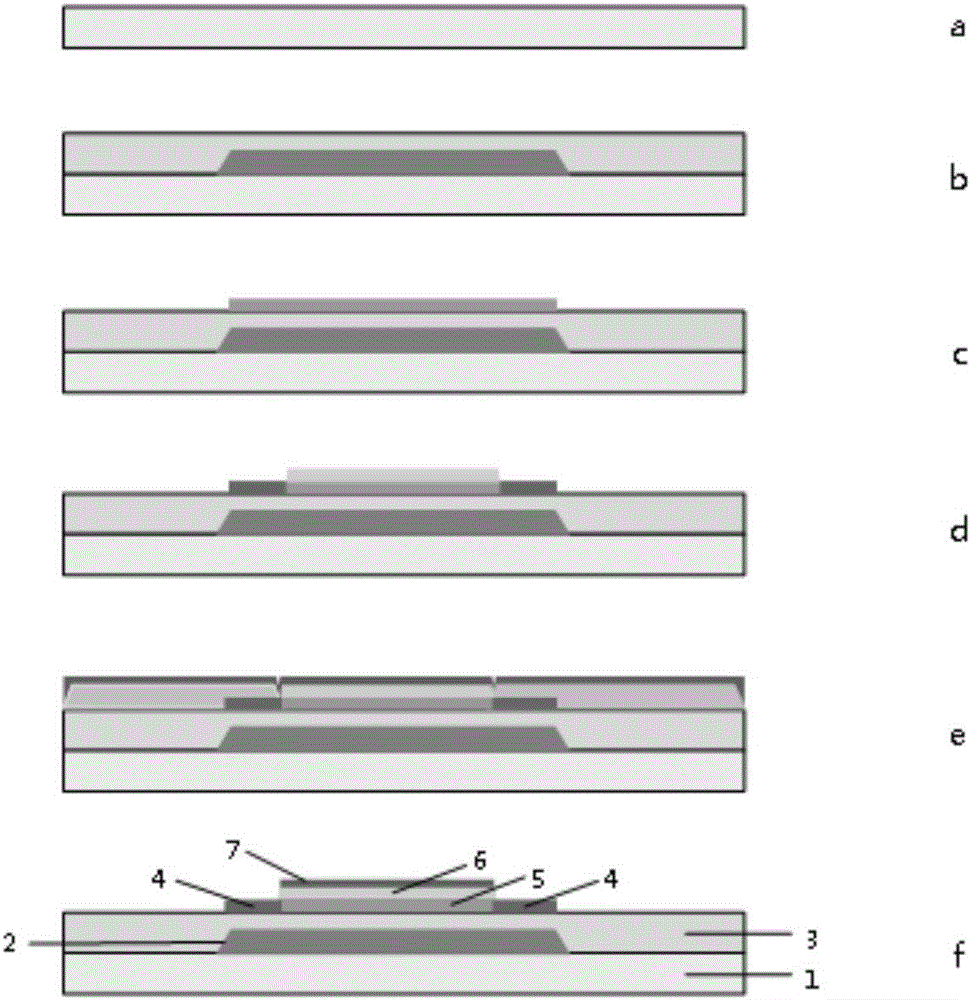

[0056] This embodiment provides a method for preparing a top-gate structure, which includes the following specific steps: apply a layer of photocurable organic silicon material by spin coating, dry after exposure and development to form a gate insulating layer; On the outside of the layer, apply a layer of thermosetting material by slit coating, place it in an oven for curing, and ensure that the gate insulating layer and the upper surface of the thermosetting material form a plane, and on this plane, use sputtering Spray coating a layer of metal used for preparing the gate layer; remove the cured heat-cured material and the metal above it by stripping.

[0057] The method described in embodiment 1 or 2 can be prepared by the method described in this embodiment.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More