Semiconductor structure and forming method therefor

A semiconductor and isolation structure technology, which is applied in the field of semiconductor structure and its formation, can solve the problems of semiconductor device electrical performance degradation, etc., and achieve the effects of improving electrical performance, optimizing electrical isolation effect, and increasing breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] It can be seen from the background art that the well isolation structure in the prior art is likely to cause the degradation of the electrical performance of the semiconductor device. Analyze the reasons for this:

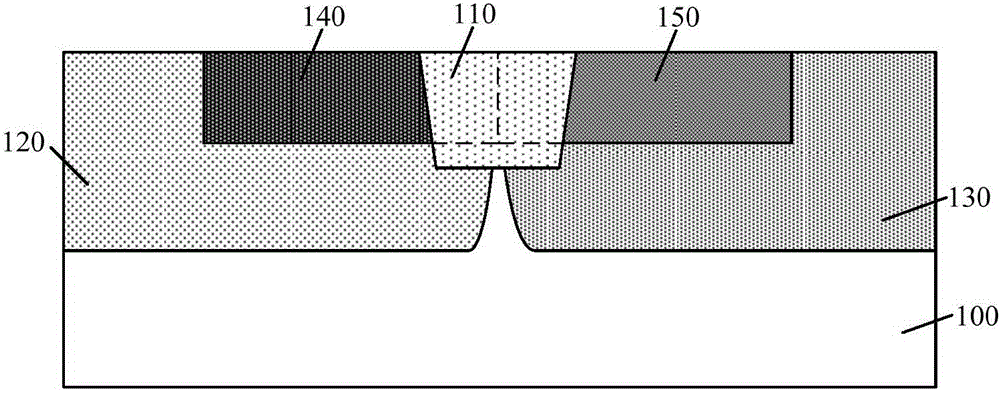

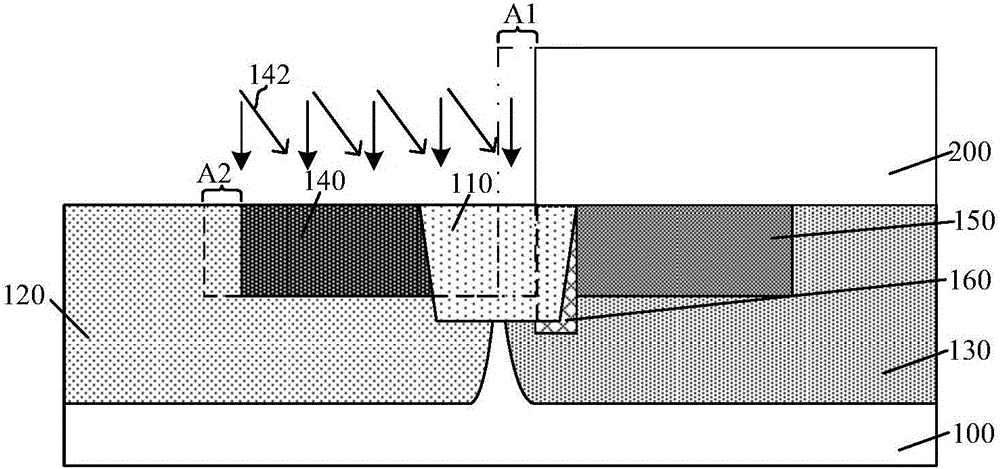

[0021] Such as figure 1 As shown, the structure of an embodiment of the well isolation structure includes: a substrate 100; an adjacent N well (Nwell) 120 and a P well (Pwell) 130 located in the substrate 100; the N well 120 and the P well An isolation structure 110 (such as ShallowTrenchIsolation, STI) is formed between 130, and the isolation structure 110 is a well isolation structure between the adjacent N well 120 and P well 130; the N well 120 is close to the isolation structure. An N-type heavily doped region 140 is formed on one side of the structure 110 for forming an N-type device; a P-type heavily doped region 150 is formed in the P well 130 near the side of the isolation structure 110 for forming a P-type device. Through the well isolation stru...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More