Semiconductor device and forming method thereof

A semiconductor and device technology, applied in the field of semiconductor manufacturing, can solve the problems of lateral double diffusion field effect transistor (LDMOS transistor performance needs to be improved, etc.), and achieve the effect of reducing gate-drain parasitic capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

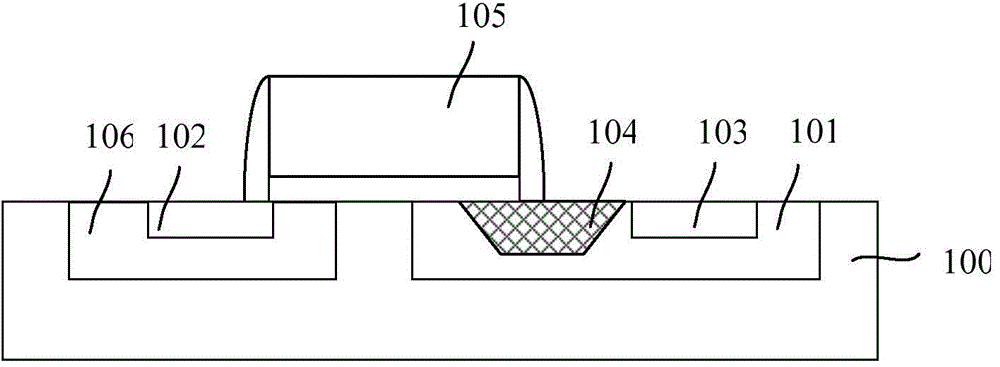

[0032] The performance of the existing LDMOS transistors still needs to be further improved. The parasitic capacitance of the gate and drain of the LDMOS transistor is the main parameter affecting the switching rate of the LDMOS transistor. Especially when the LDMOS transistor is used as a high-frequency switching device, the parasitic capacitance of the gate and drain of the LDMOS transistor The effect of switching rate is particularly prominent.

[0033] Research has found that the gate-drain parasitic capacitance of LDMOS transistors is related to parameters such as the area facing the gate electrode and the drift region, the distance between the gate electrode and the drift region, and the dielectric constant of the gate dielectric layer. The smaller the gate-drain parasitic capacitance, the better the switch The smaller the influence of the rate, usually by increasing the facing area of the gate electrode and the drift region, increasing the thickness of the gate dielect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More