LDMOS device manufacturing method

A manufacturing method and device technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of unsuitability for extended gates, poor experimental repeatability, affecting the electrical properties of extended gates, etc. The effect of reducing production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0050] The manufacturing process of the LDMOSFT device in this example is as follows:

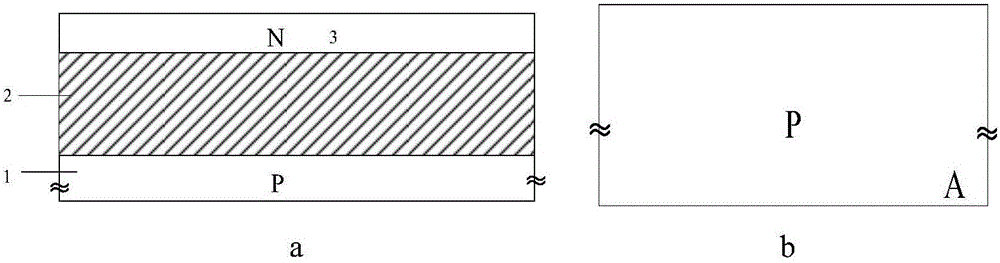

[0051] The first step: preparing SOI material: the SOI material includes a substrate layer 1, a dielectric buried layer 2 and an active layer 3, wherein the conductivity type of the substrate layer 1 is not limited, and the conductivity type of the active layer 3 is the first conductivity type, The dielectric buried layer 2) is located between the substrate layer 1 and the active layer 3 (such as figure 1 as shown in a);

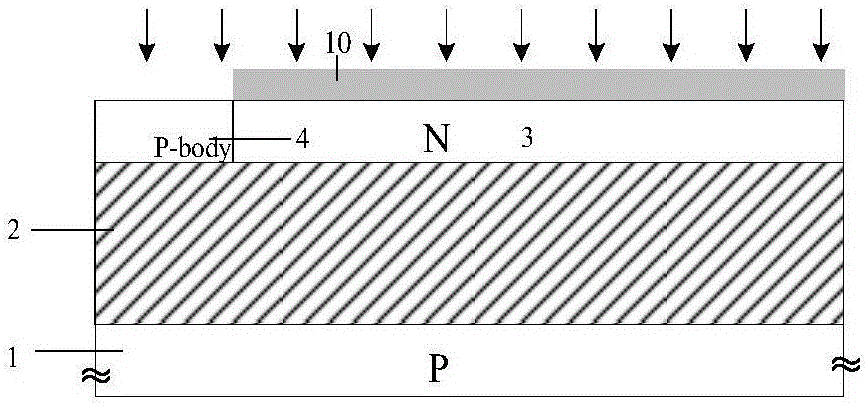

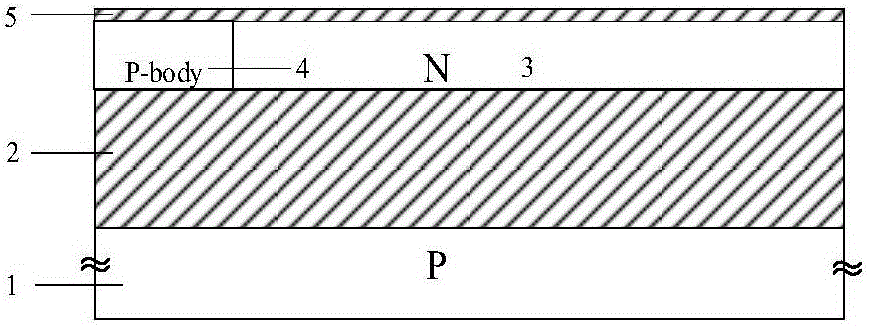

[0052] The second step: adopt ion implantation process on the above SOI material, implant the second conductivity type impurity in the active layer 3, and form the second conductivity type body region 4 (such as figure 2 shown), and then thermally oxidized on top of the active layer 3 to form a dielectric isolation layer 5 (such as image 3 shown);

[0053] The third step: in another second conductivity type semiconductor material A (such as figure 1 As shown in b) t...

Embodiment 2

[0061] The difference between this example and Example 1 is that

[0062] The fifth step is: use an etching process to etch the two ends of the auxiliary semiconductor layer 6 to the upper surface of the active layer 3 to form a first active region window and a second active region window. A gate dielectric 11 is grown on the upper surface of the active region window and the second active region window, such as Figure 12 As shown, polysilicon 12 is deposited on the upper surface of part of the gate dielectric 11 located on the upper surface of the semiconductor body region 4 of the second conductivity type and connected to the auxiliary semiconductor layer 6, and the polysilicon gate is formed after etching the polysilicon 12 and the gate dielectric 11, as shown in FIG. Figure 13 shown;

[0063] The eighth step is: making a source metal in the first active region window, with a passivation layer dielectric 9 between the source metal and the gate contact region 82; making a ...

Embodiment example 3

[0066] The difference between this example and Example 2 is that

[0067] There is a gate dielectric 11 between the formed polysilicon gate and the auxiliary semiconductor layer 4, such as Figure 14 shown;

[0068] The seventh step also includes: implanting semiconductor impurities of the second conductivity type into the part of the auxiliary semiconductor layer 4 connected to the gate dielectric 11 to form a second gate contact region 84, such as Figure 15 shown;

[0069] The eighth step further includes: forming a second source metal on the upper surface of the second gate contact region 84 .

[0070] The first doping type and the second doping type of the semiconductor are opposite doping types. When the first doping type is n-type doping, the second doping type is p-type doping; correspondingly , when the first doping type is p-type doping, the second doping type is n-type doping.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More