Signaling with multiple clock lines

A signal and reference time technology, applied in the direction of synchronous information channel, line failure/interference reduction, digital transmission system, etc., can solve problems such as high cost, cost of increasing power and circuit board wiring space, limiting channel throughput, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

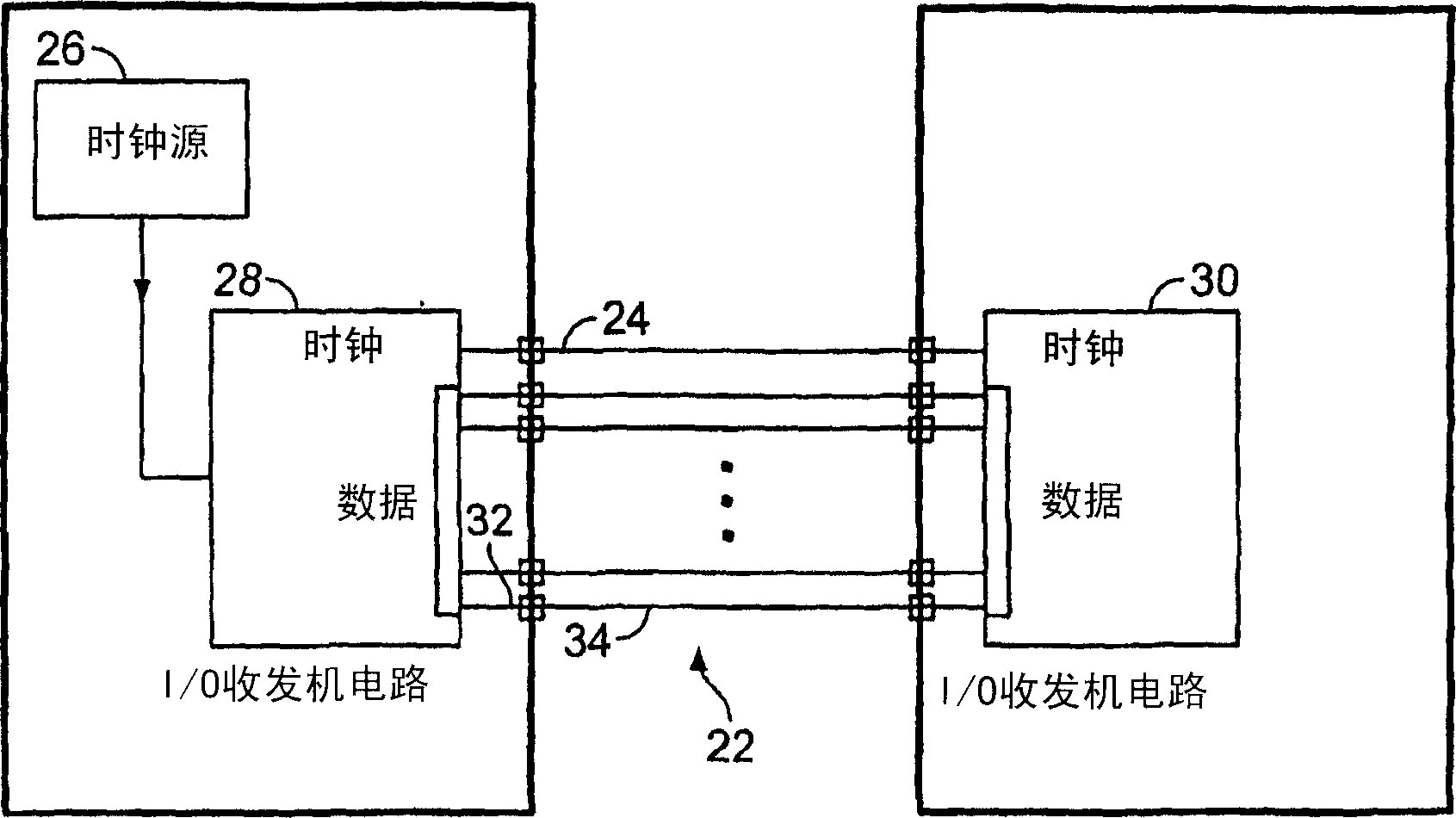

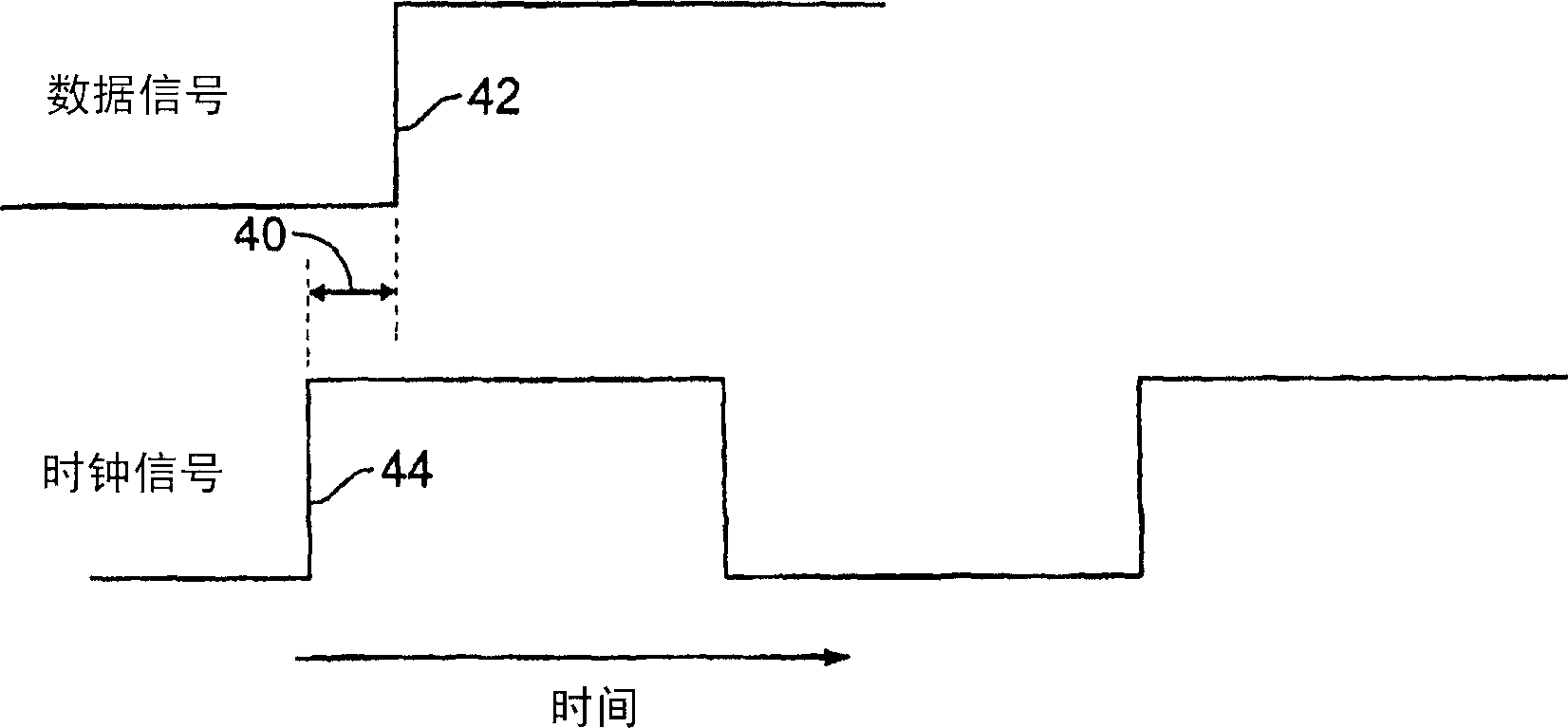

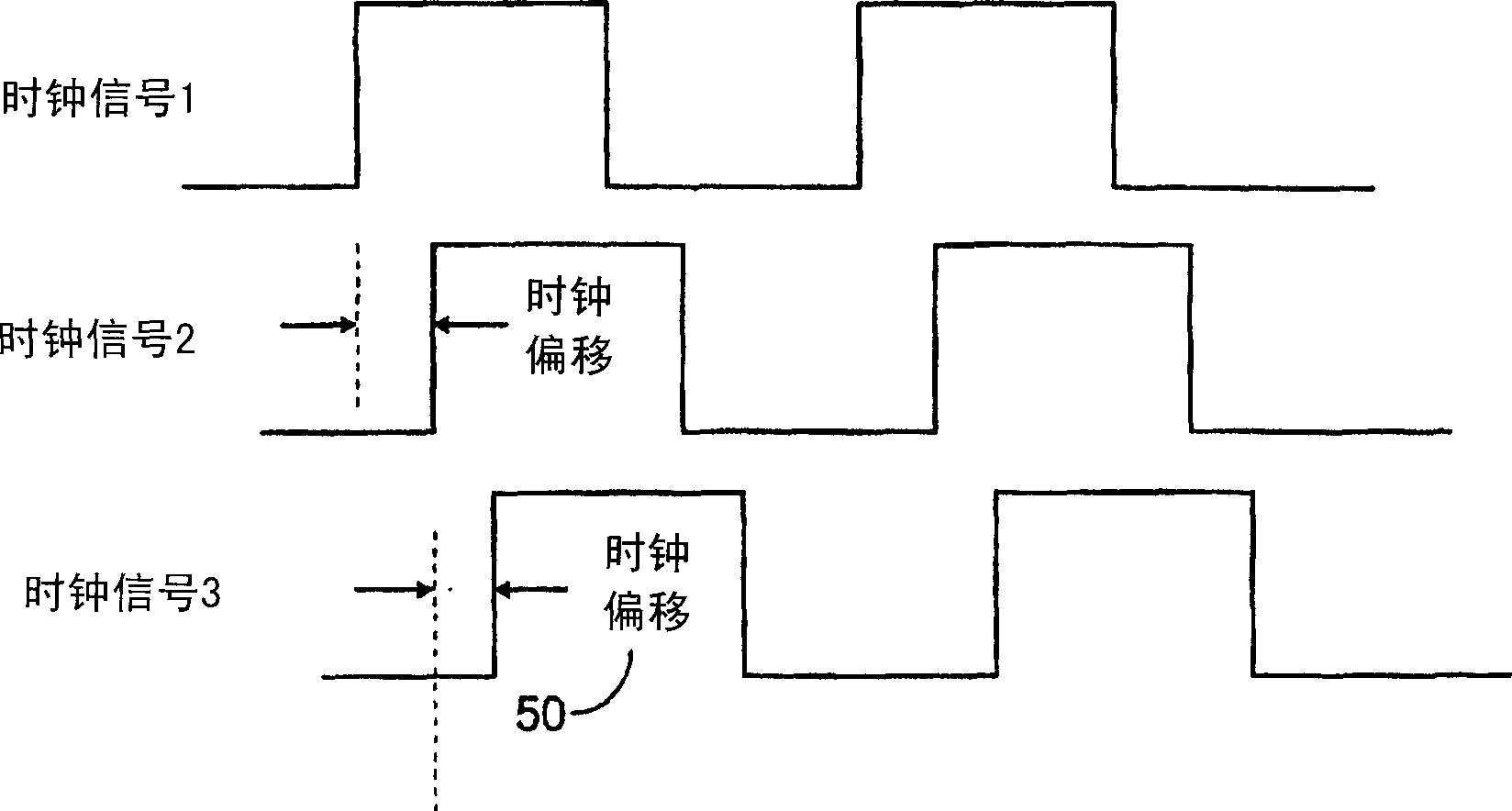

[0028] Multiple time reference signals (clocks) can be used to improve the timing resolution of eg phase and pulse width modulated signals. Such as image 3 As shown, clock signals can be derived from the same source, but the clock signals are phase shifted with respect to each other by a pre-designed amount 50. The modulator circuit can then reference the data transition to the clock signal whose edge is closest to the transition. Because there are more clock transitions, the time interval from a data signal transition to the nearest clock transition can be reduced. The integral of jitter, which increases with the event distance between a data transition and its reference clock transition, will also decrease, resulting in an overall reduction in circuit jitter. This results in a higher available bandwidth. In some embodiments, the addition of more than one clock signal may require sacrificing a considerable data line for each additional clock signal due to wire routing con...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More