Method for avoiding wafer damage in molding process of wafer level packaging

一种晶圆、工序的技术,应用在晶圆级封装体的制备领域,能够解决晶圆不完全被塑封料覆盖、粘附不佳等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

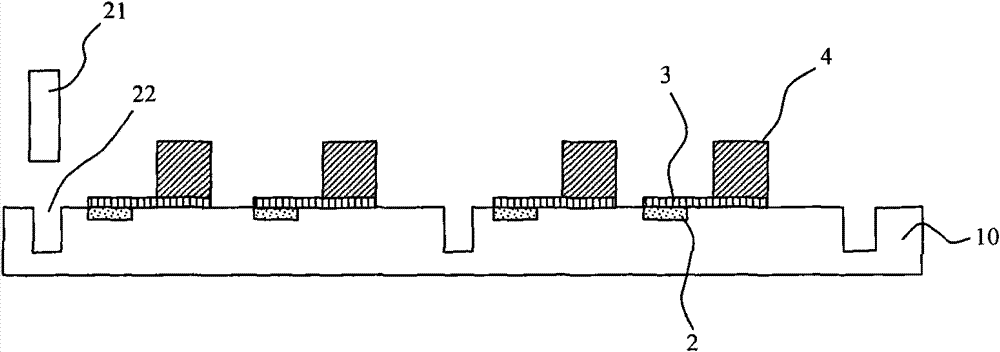

[0049] see image 3 As shown, the front side 100a of the wafer 100 includes a plurality of chips 110, and the plurality of chips 110 are cast and connected to each other. The adjacent chips 110 define the boundaries between each other through the dicing groove 115. Part is edge 120 .

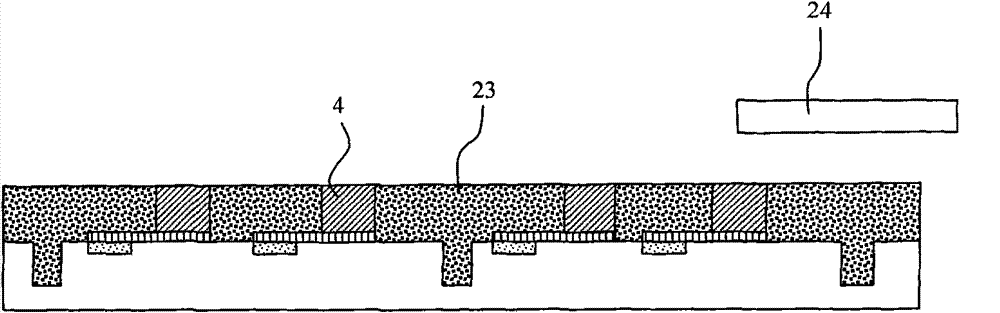

[0050] see Figure 4As shown, in the cross-sectional diagram of the wafer 100 and the chip 110 , the integrated circuit is formed on the front side 100 a of the wafer 100 , and the other side of the wafer 100 is the back side 100 b. The bonding pad (Bond Pad) 101 is used as an input / output contact terminal (I / O Pad) of the internal circuit of the chip 110, and can be a signal input / output, or an interface of Power and Ground. In wafer-level packaging, redistribution technology RDL (Redistribution Technology) can be used to redesign the aluminum pads arranged around the top of the existing chip into a matrix arrangement. In the wafer 100, the top of any chip 110 is provided with a plurality of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com