Grid resistor test structure for MOS transistor

A technology of MOS transistors and gate resistors is applied in the field of test structures for quantifying the influence of gate resistors on device characteristics, and can solve problems such as inability to intuitively obtain

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

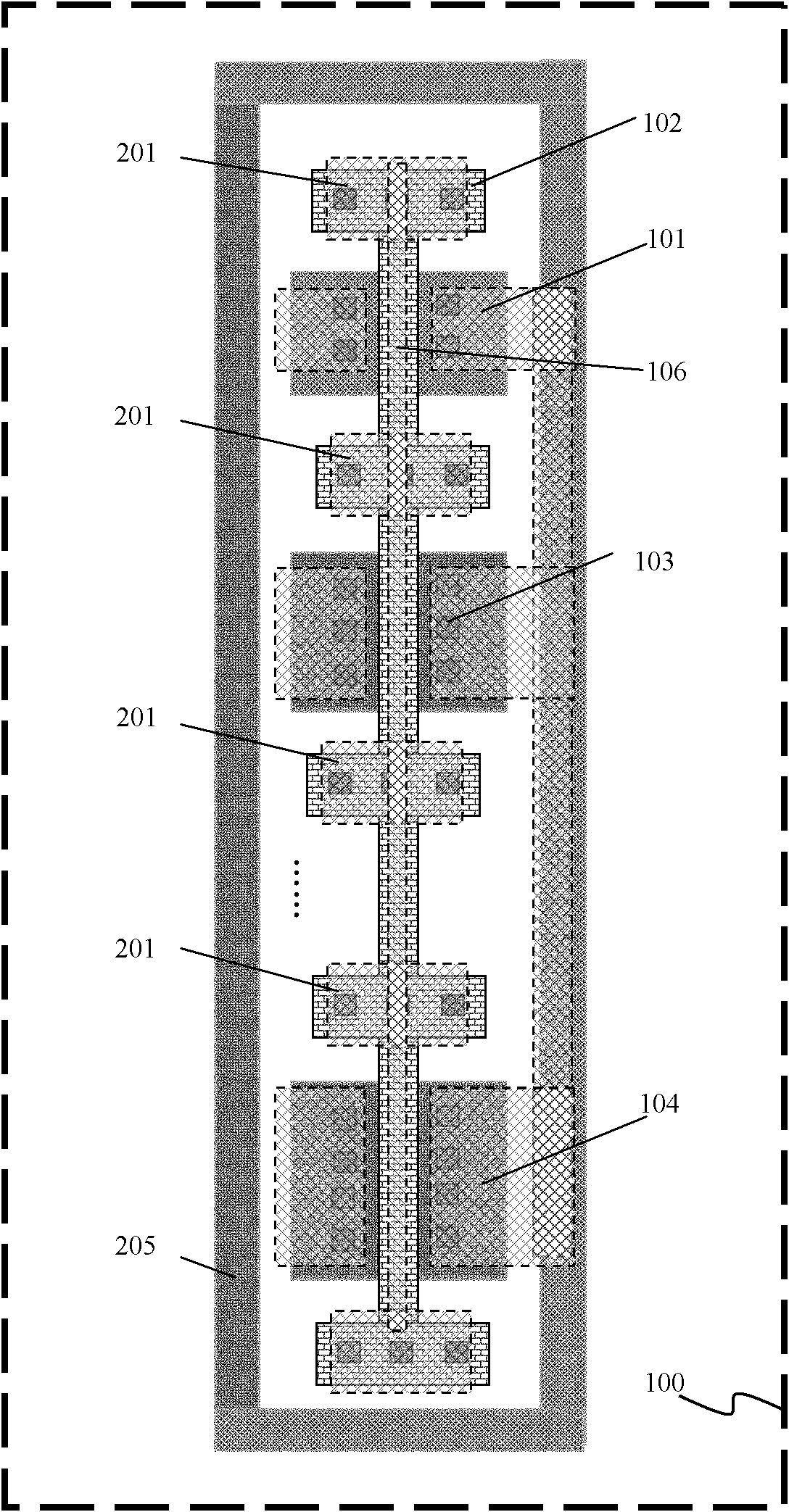

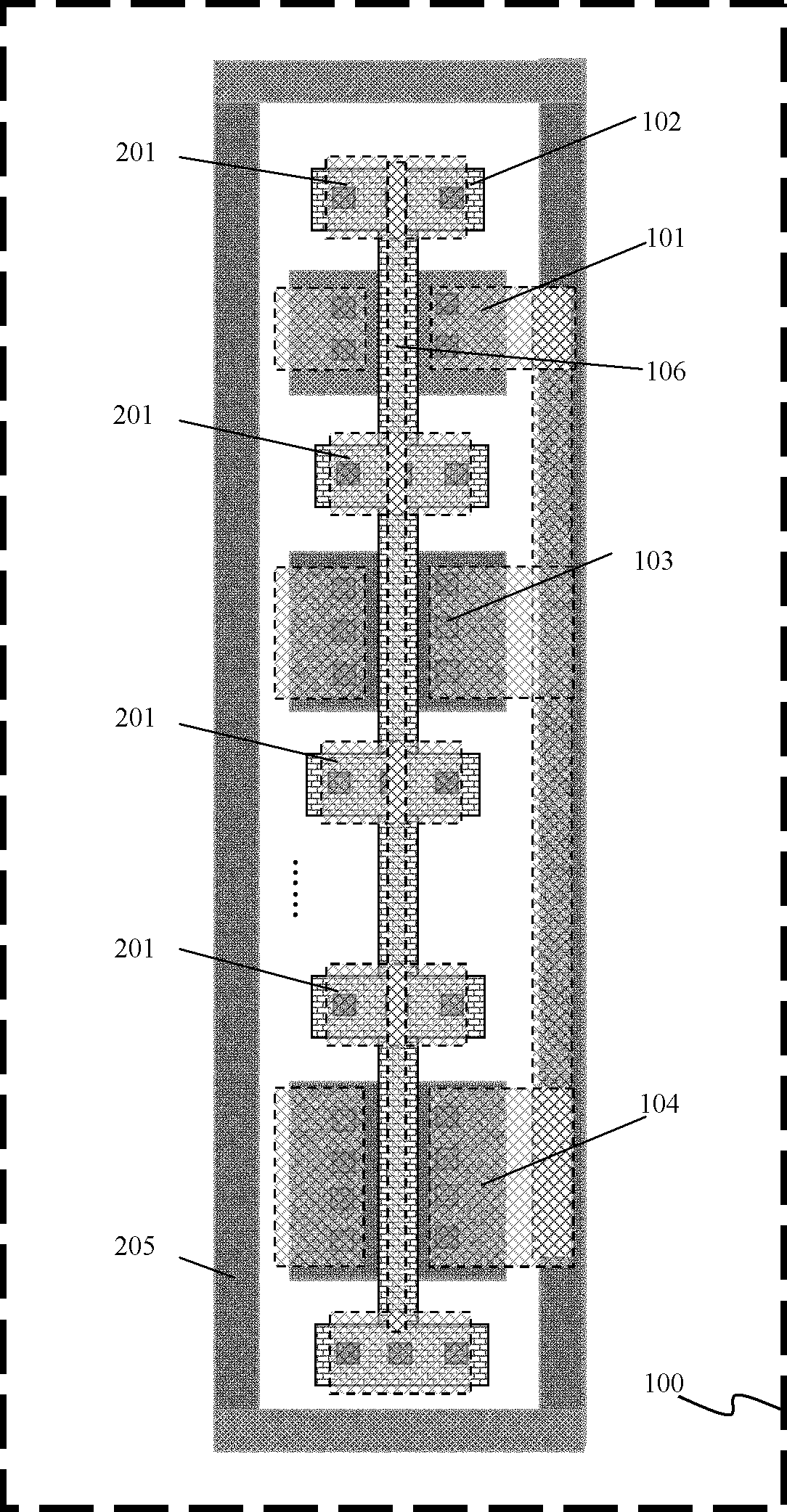

[0032] The MOS transistor gate resistance test structure of the present invention includes m groups of MOS transistors, each group of MOS transistors includes n MOS transistors with different channel widths, the same group of MOS transistors has the same channel length, and different groups of MOS transistors have different channel widths. The length of the track, the type of each MOS transistor is the same (both N-type or both P-type), m and n are positive integers;

[0033] The channel length L of the e-group MOS transistor e For: L e = L min +e*ΔL,L min is the minimum channel length, ΔL is the channel length difference, e is an integer greater than or equal to 0 and less than or equal to m-1, that is, the channel lengths of each group of MOS transistors are: L 0 = L min , L 1 = L min +ΔL, L 2 =Lmin+2ΔL,...,L m-1 = L min +(m-1)ΔL; the channel length of each group of MOS transistors is based on compliance with the design rules, and a short channel device is selected....

PUM

| Property | Measurement | Unit |

|---|---|---|

| Channel length | aaaaa | aaaaa |

| Channel width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More