ASIP (application-specific instruction-set processor) based on extensible processor architecture and realizing method thereof

A technology of processor architecture and special instructions, applied in the electronic field, can solve the problems that the four-stage pipeline structure cannot be applied to the addressing mode, is not suitable for large-scale parallel processing of processors, and has no processor architecture support, so as to overcome the single function and discomfort For embedded applications, rich addressing modes, overcoming insufficient addressing modes and slow running speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The present invention will be described in further detail below in conjunction with the accompanying drawings.

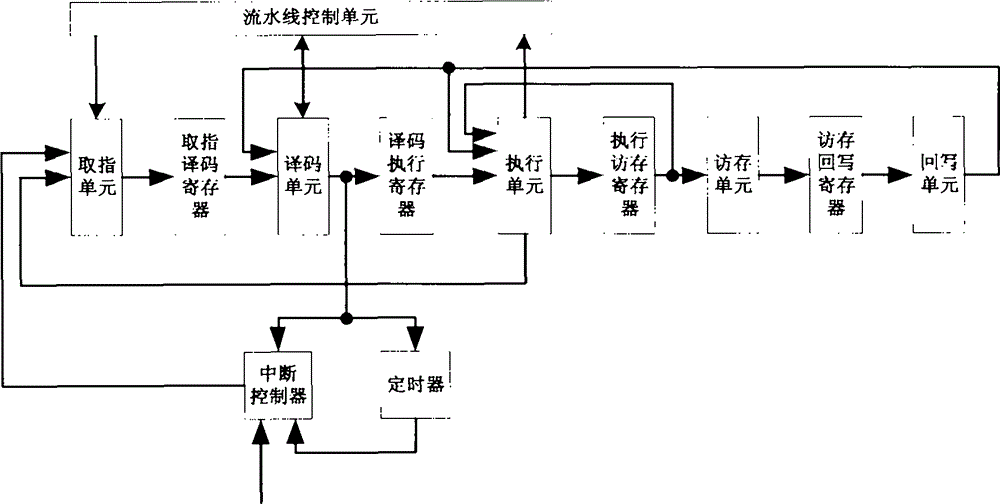

[0042] refer to figure 1 , The dedicated instruction set processor of the present invention includes an instruction fetch unit, a decoding unit, an execution unit, a memory access unit, a write-back unit, a pipeline control unit, a timer and an interrupt controller.

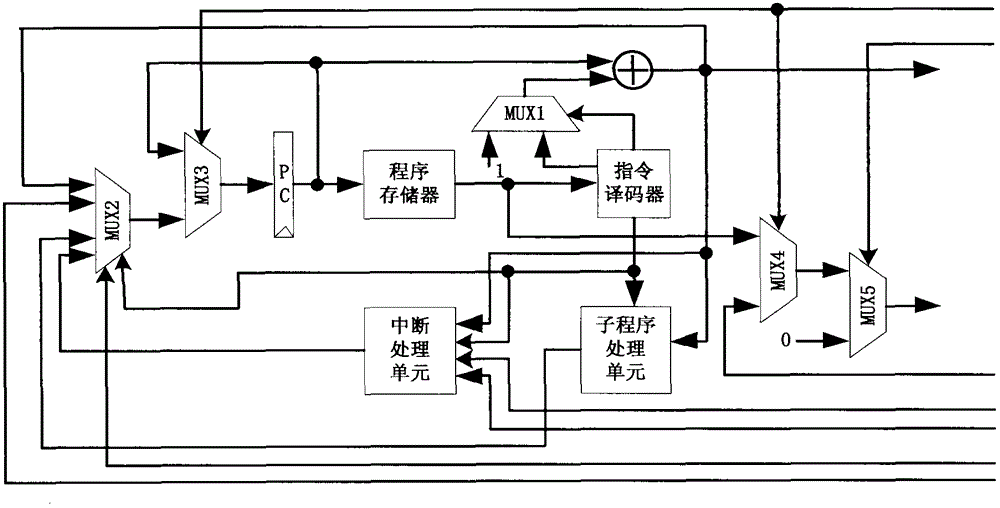

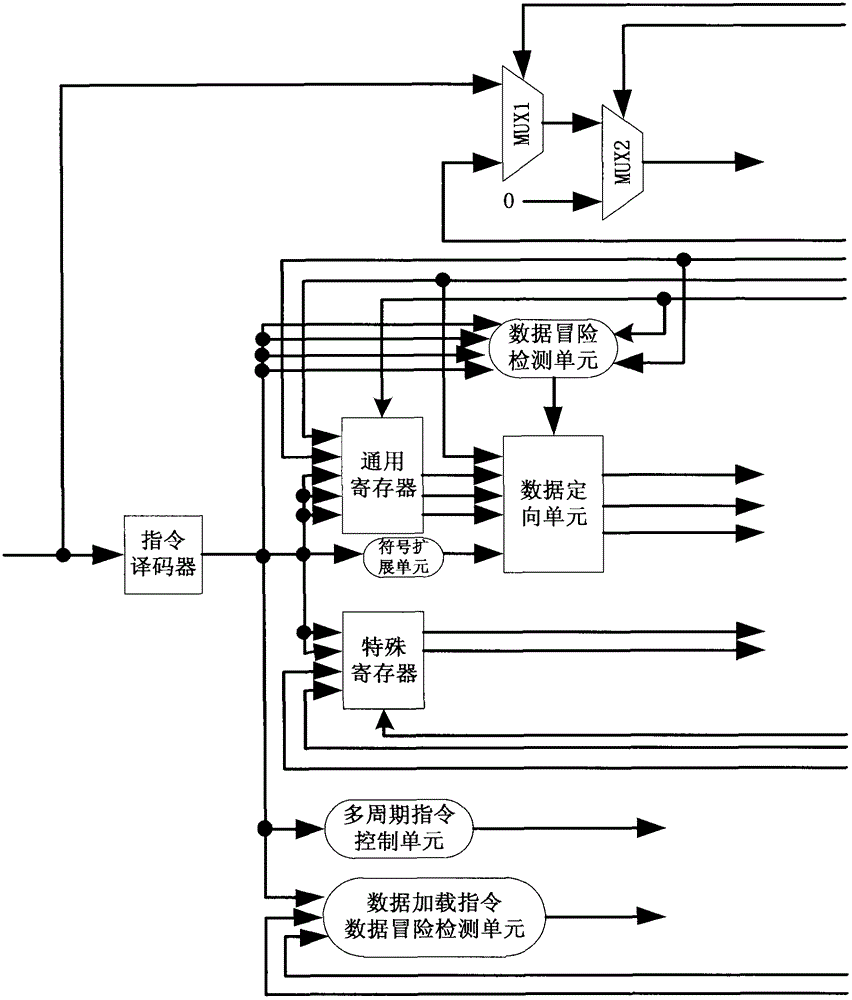

[0043] The output terminal of the instruction fetching unit is connected to the decoding unit through the instruction fetching and decoding register, and is used to access the program memory, fetch the instruction pointed to by the current program counter, provide instructions for the decoding unit, and generate the address of the next instruction to be executed ; The output terminal of the decoding unit is connected with the timer, the interrupt controller and the pipeline control unit, and the output terminal of the decoding unit is connected with the execution unit through the decoding execut...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More