Patents

Literature

38 results about "Application-specific instruction-set processor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

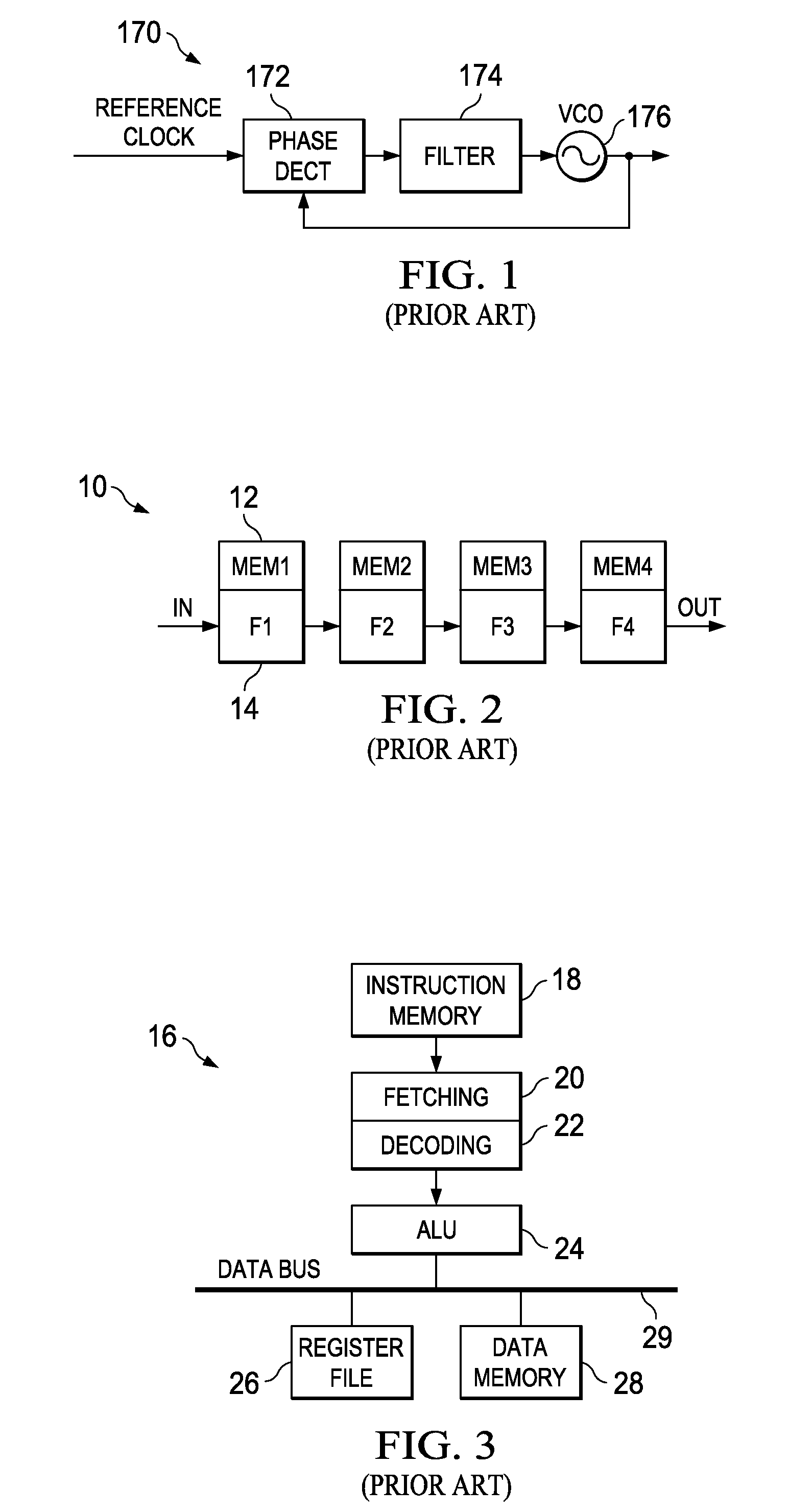

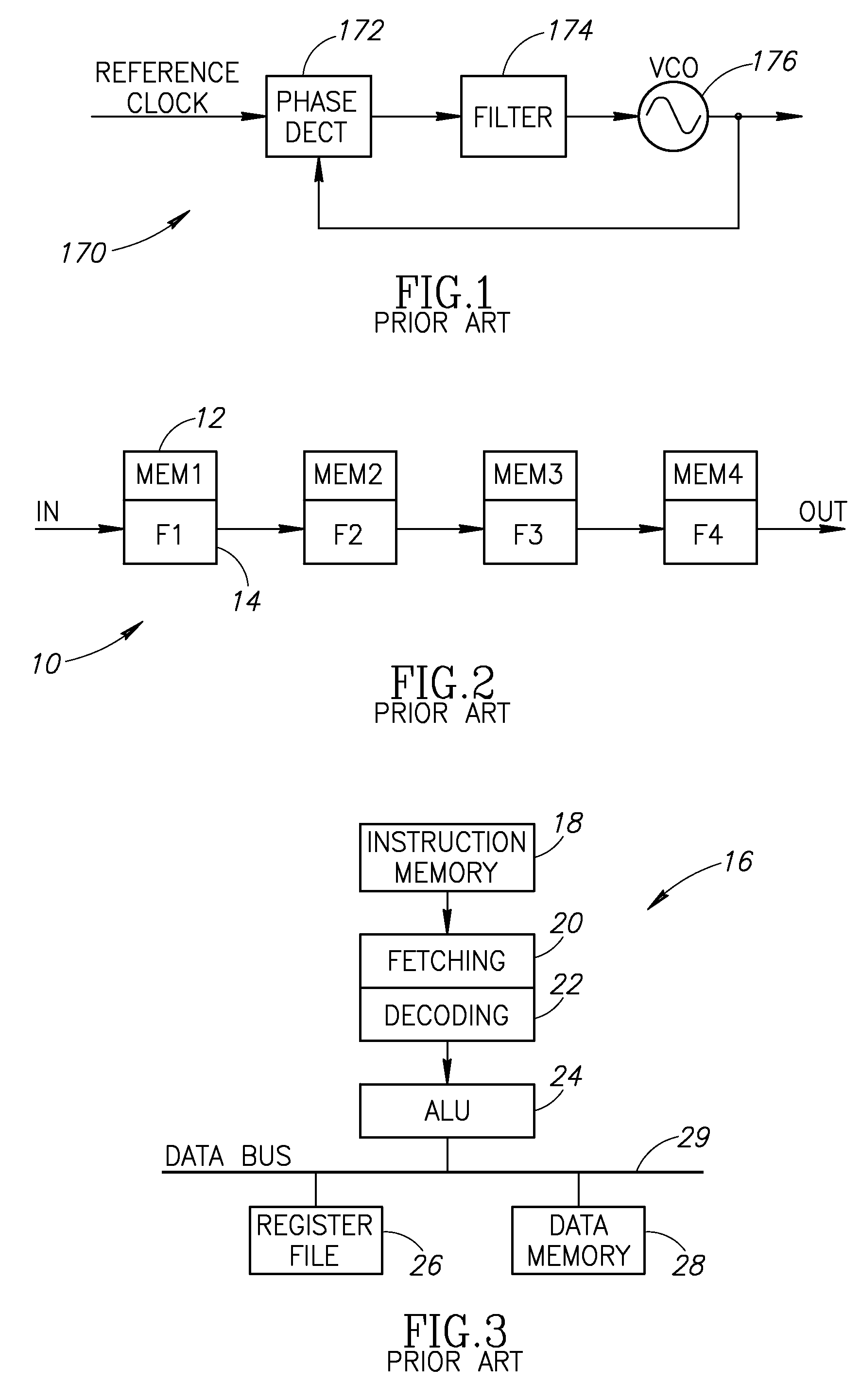

An application-specific instruction set processor (ASIP) is a component used in system-on-a-chip design. The instruction set of an ASIP is tailored to benefit a specific application. This specialization of the core provides a tradeoff between the flexibility of a general purpose CPU and the performance of an ASIC.

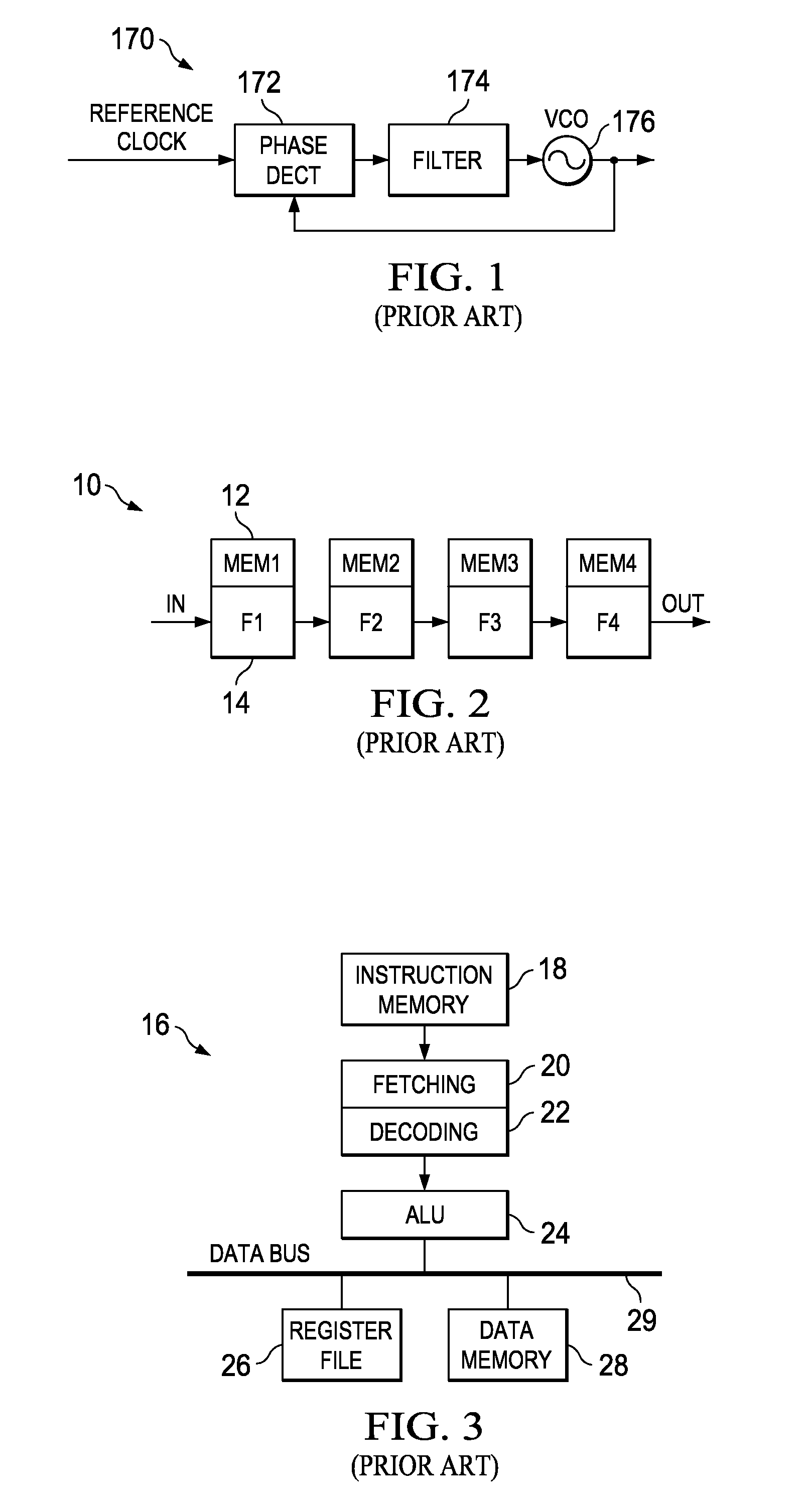

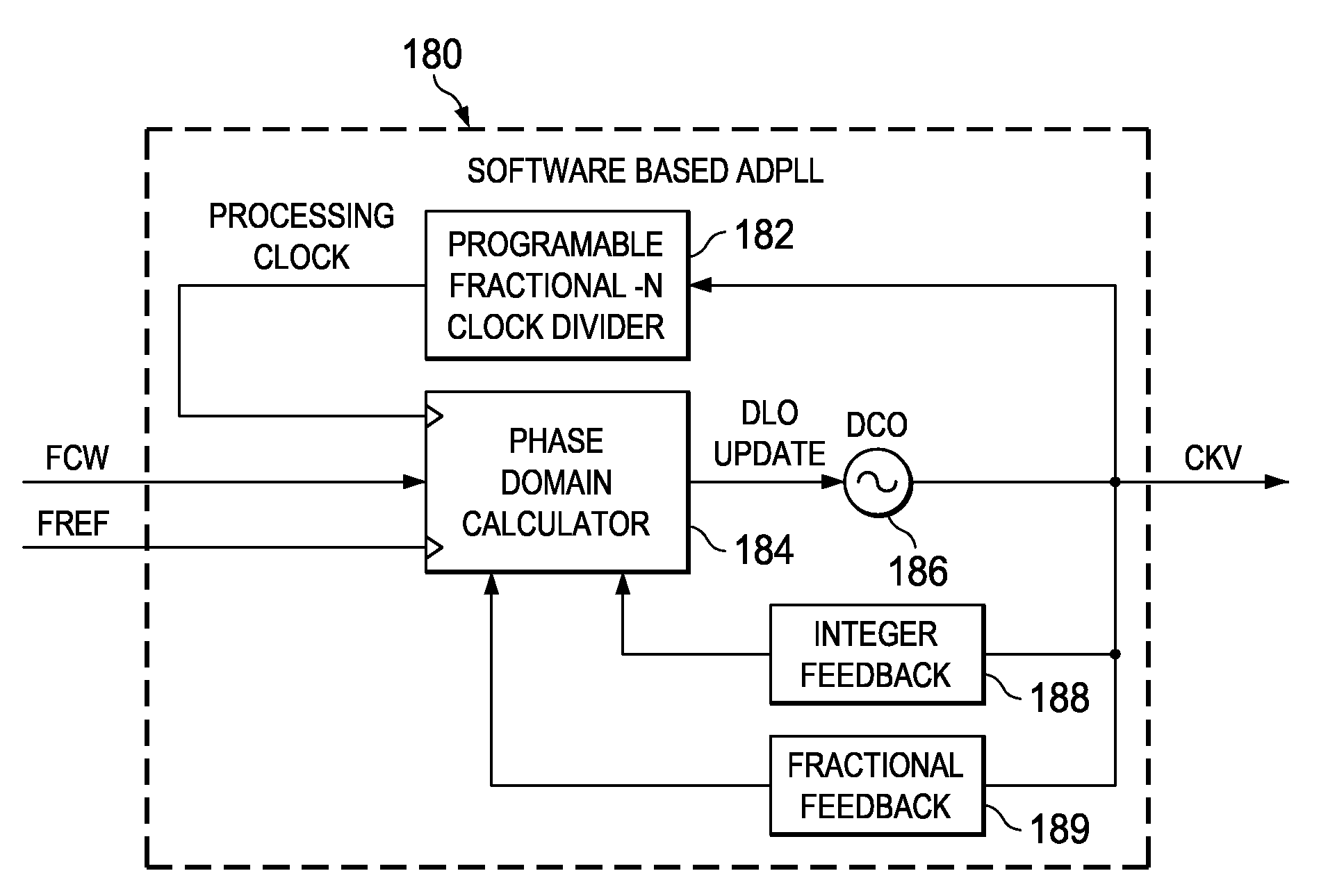

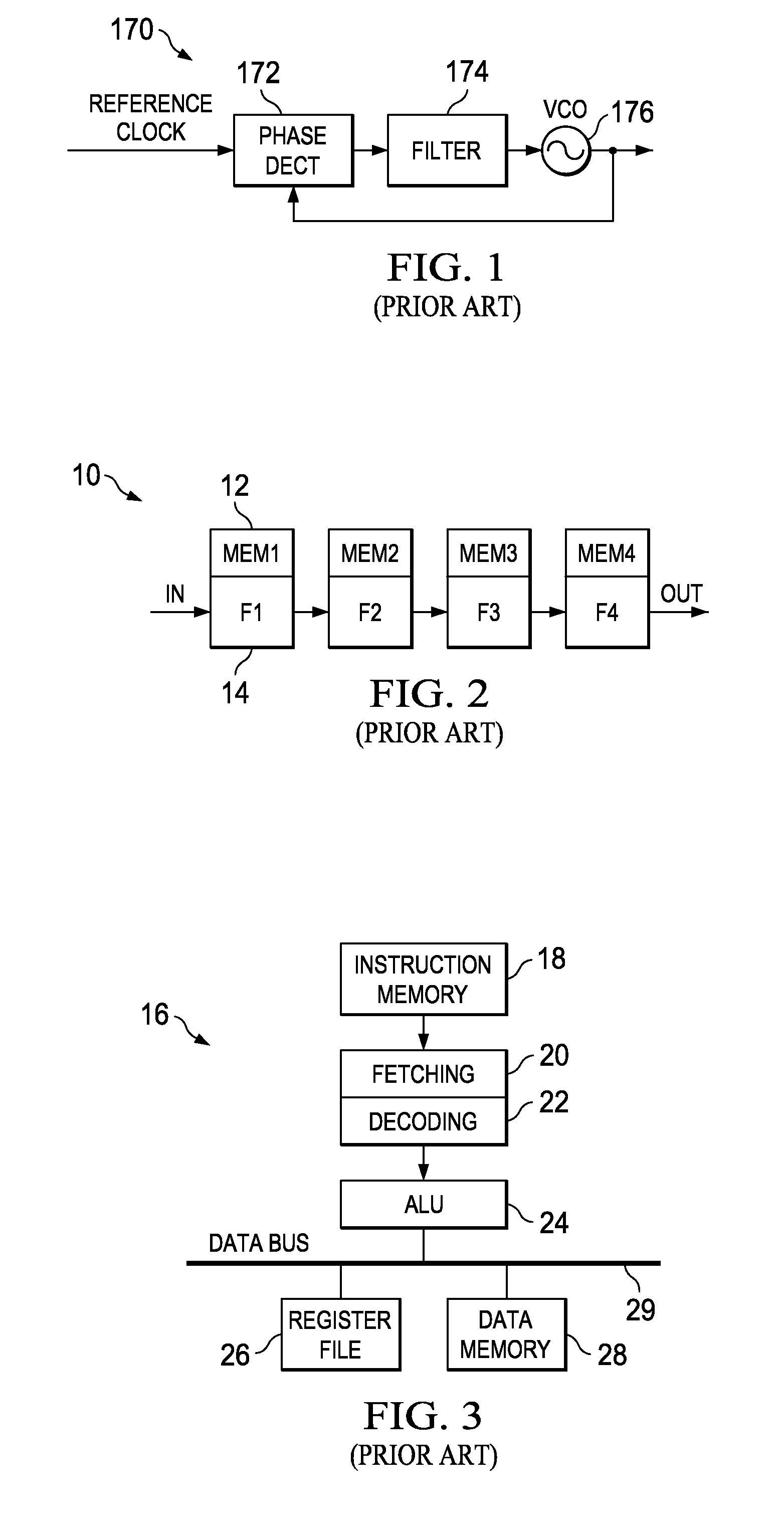

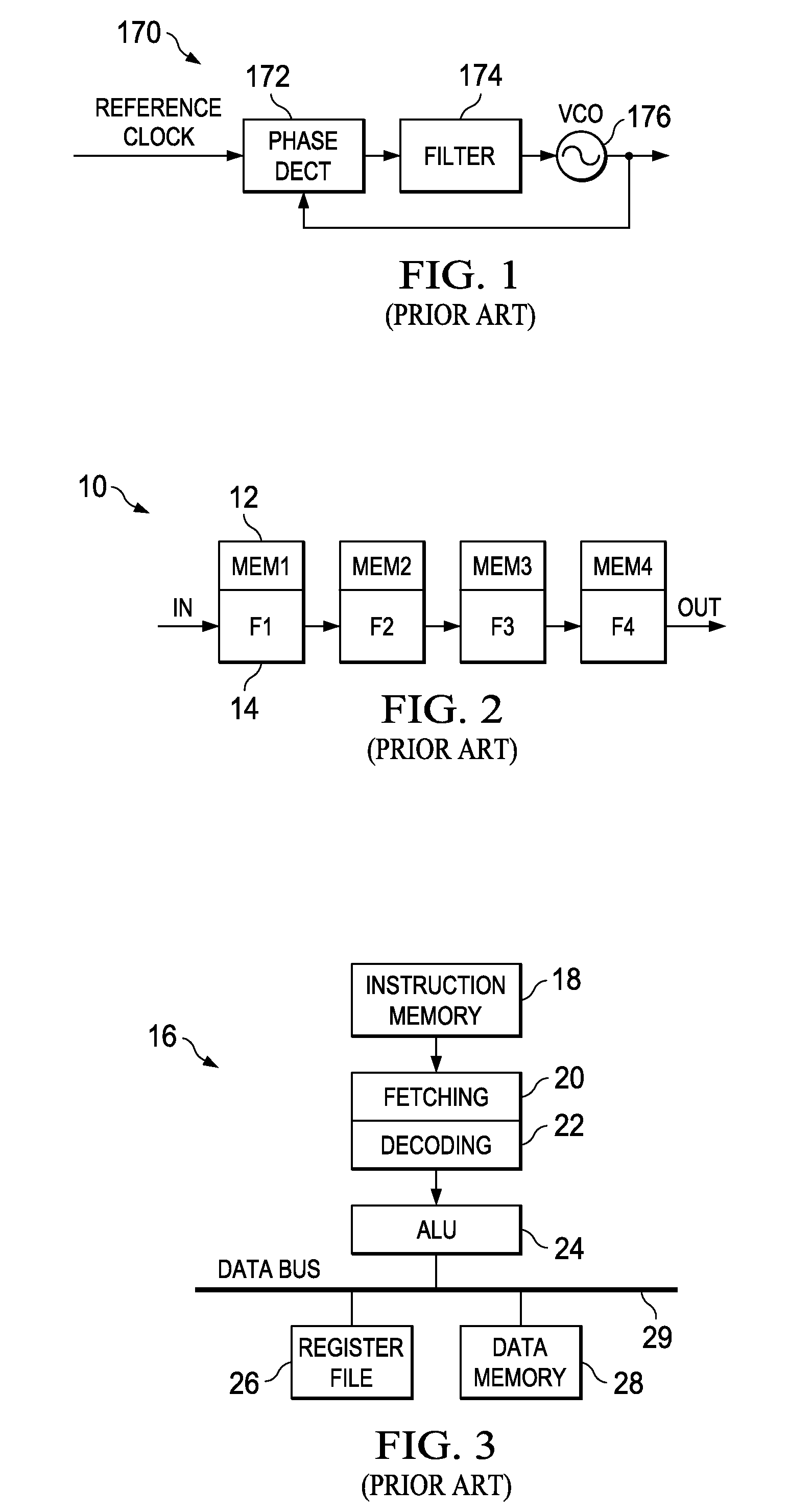

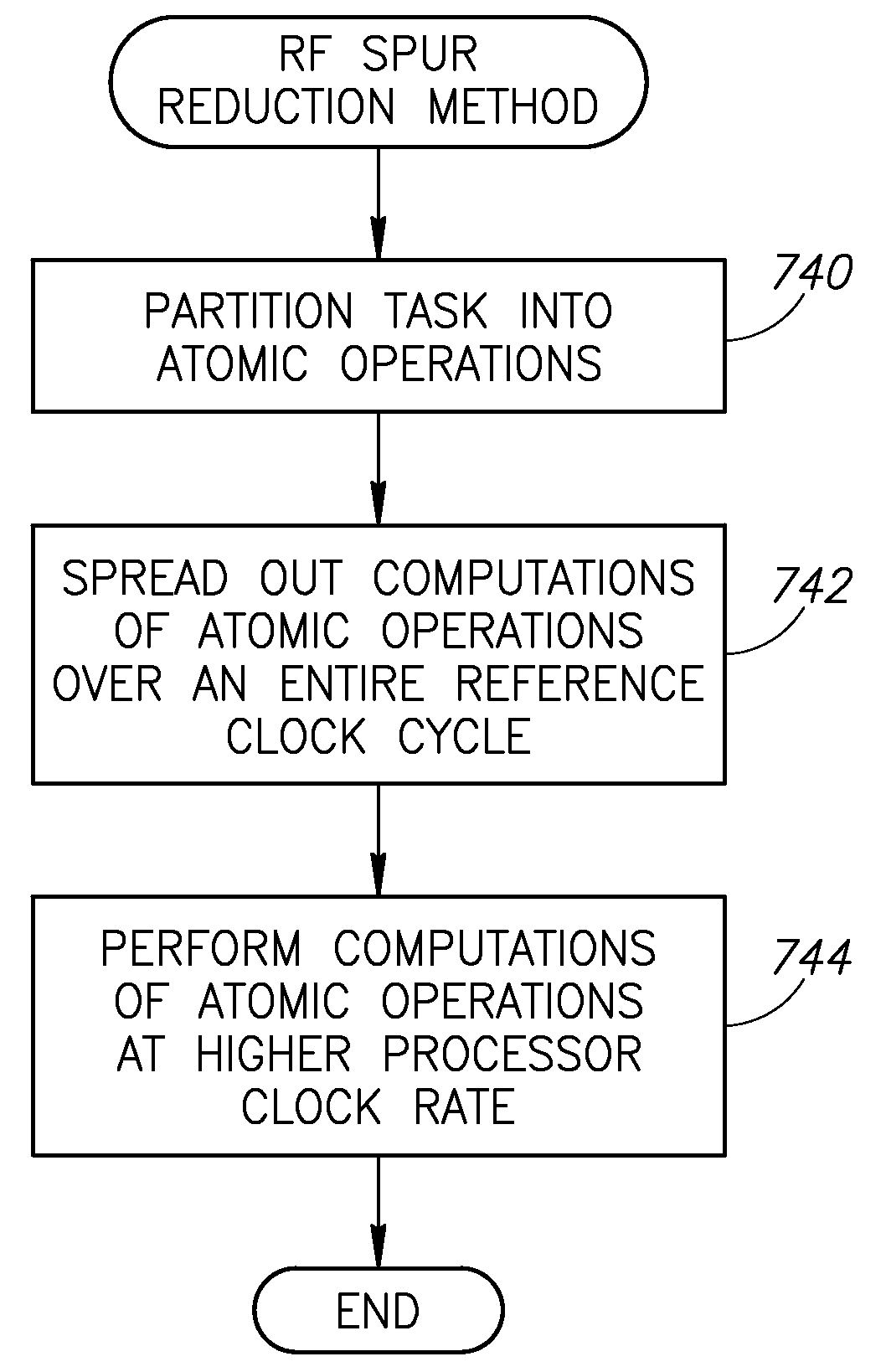

Computation spreading utilizing dithering for spur reduction in a digital phase lock loop

ActiveUS20090262877A1Easy to reconfigureReduce generationPulse automatic controlGenerator stabilizationFrequency spectrumClock rate

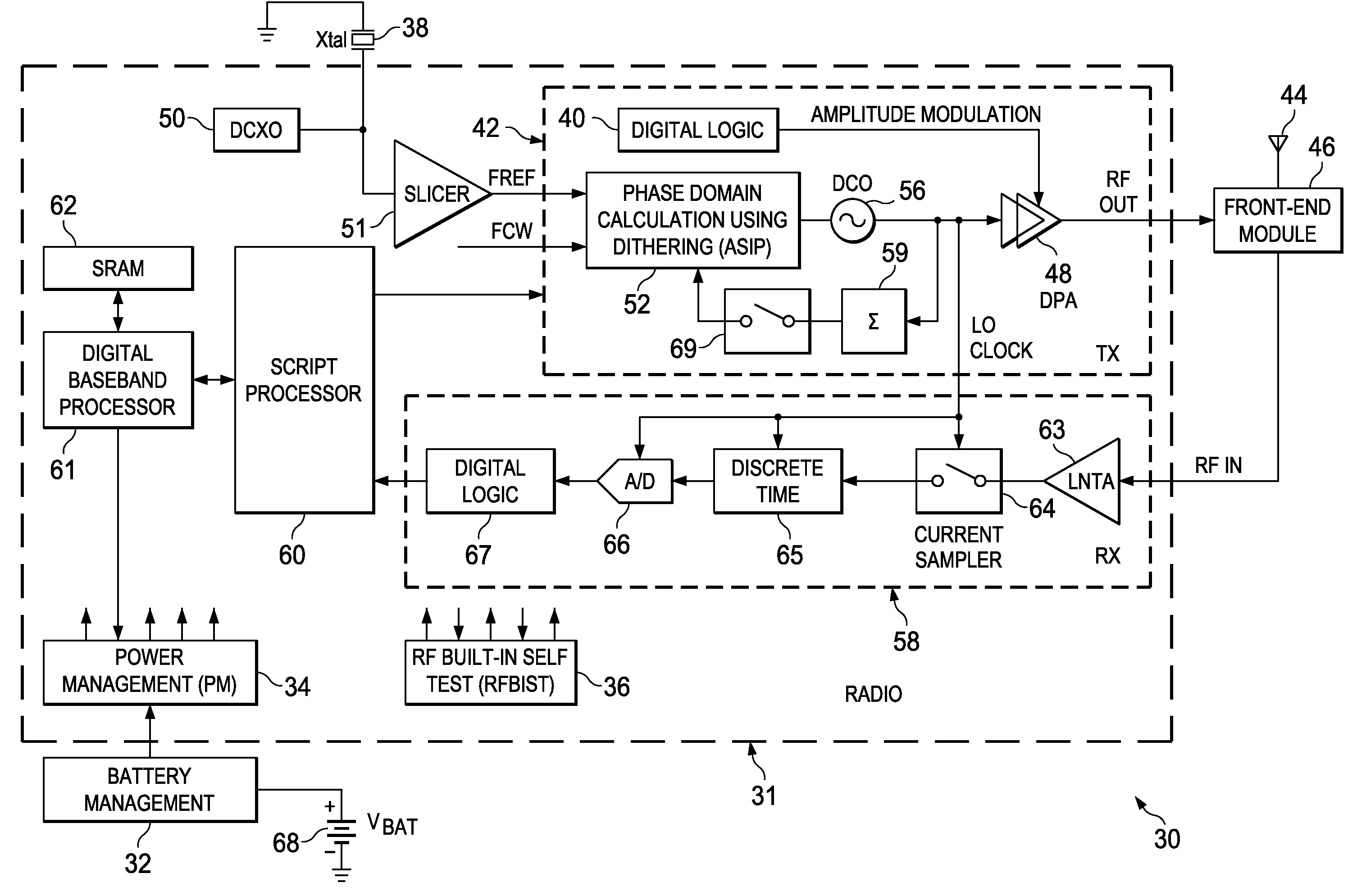

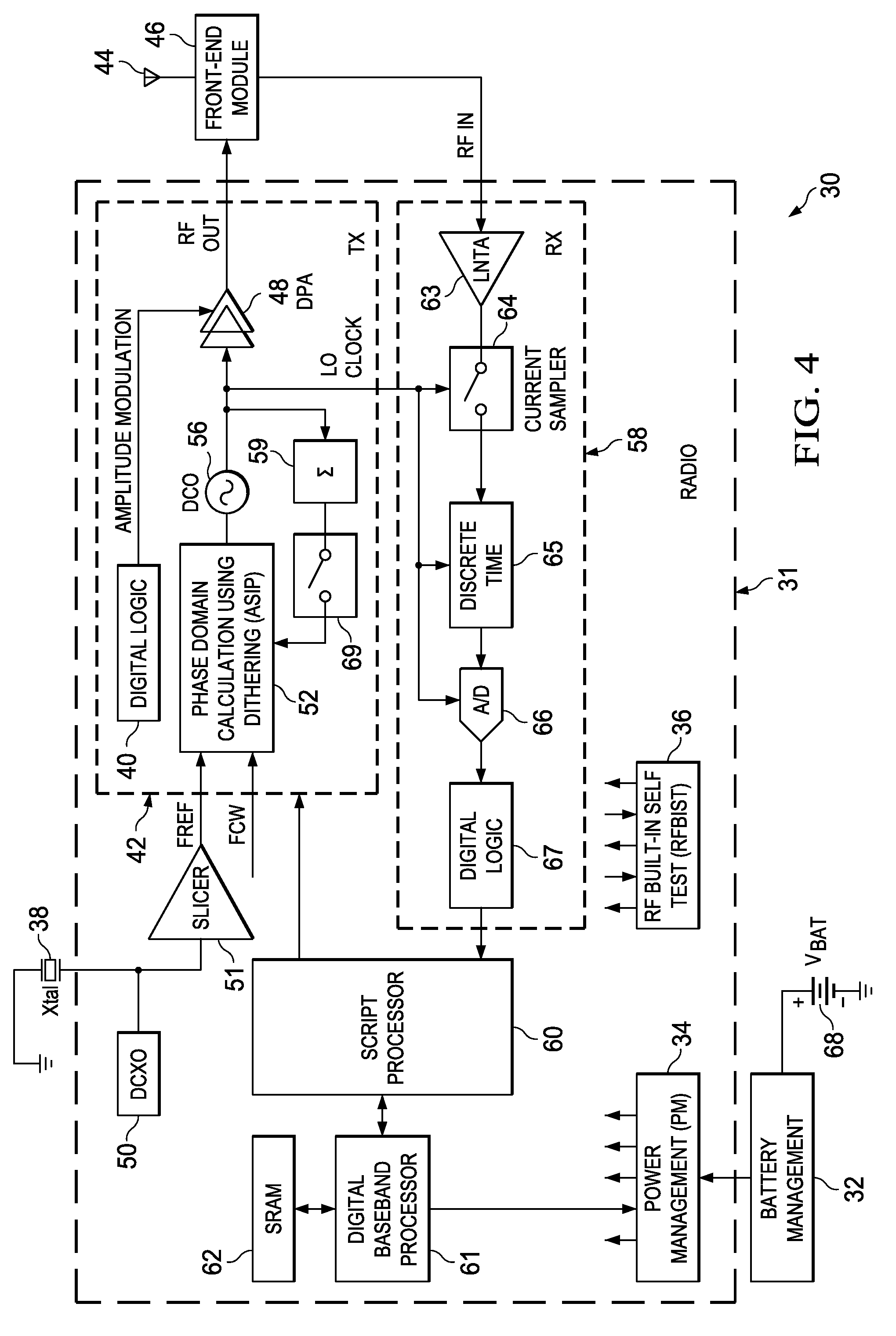

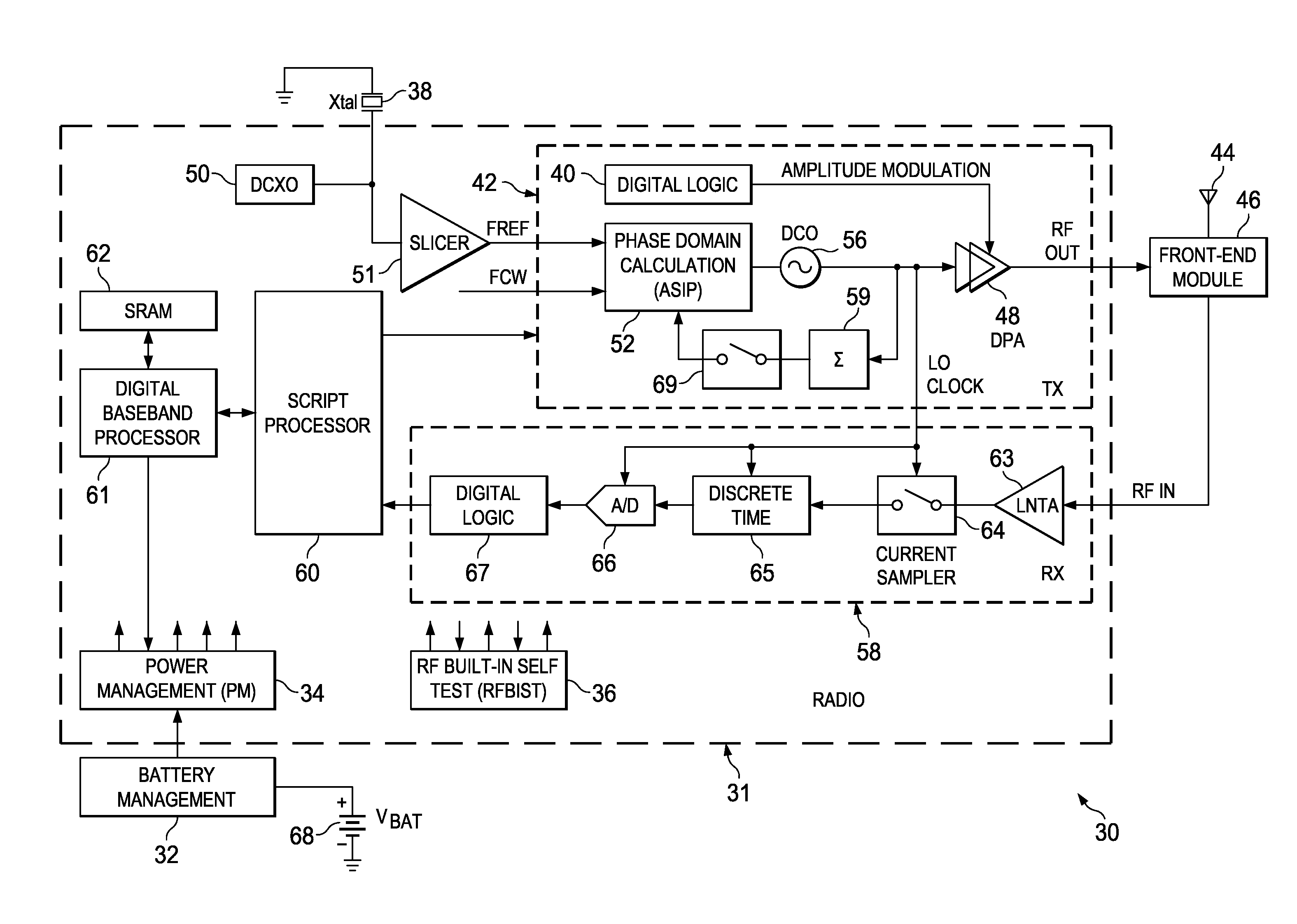

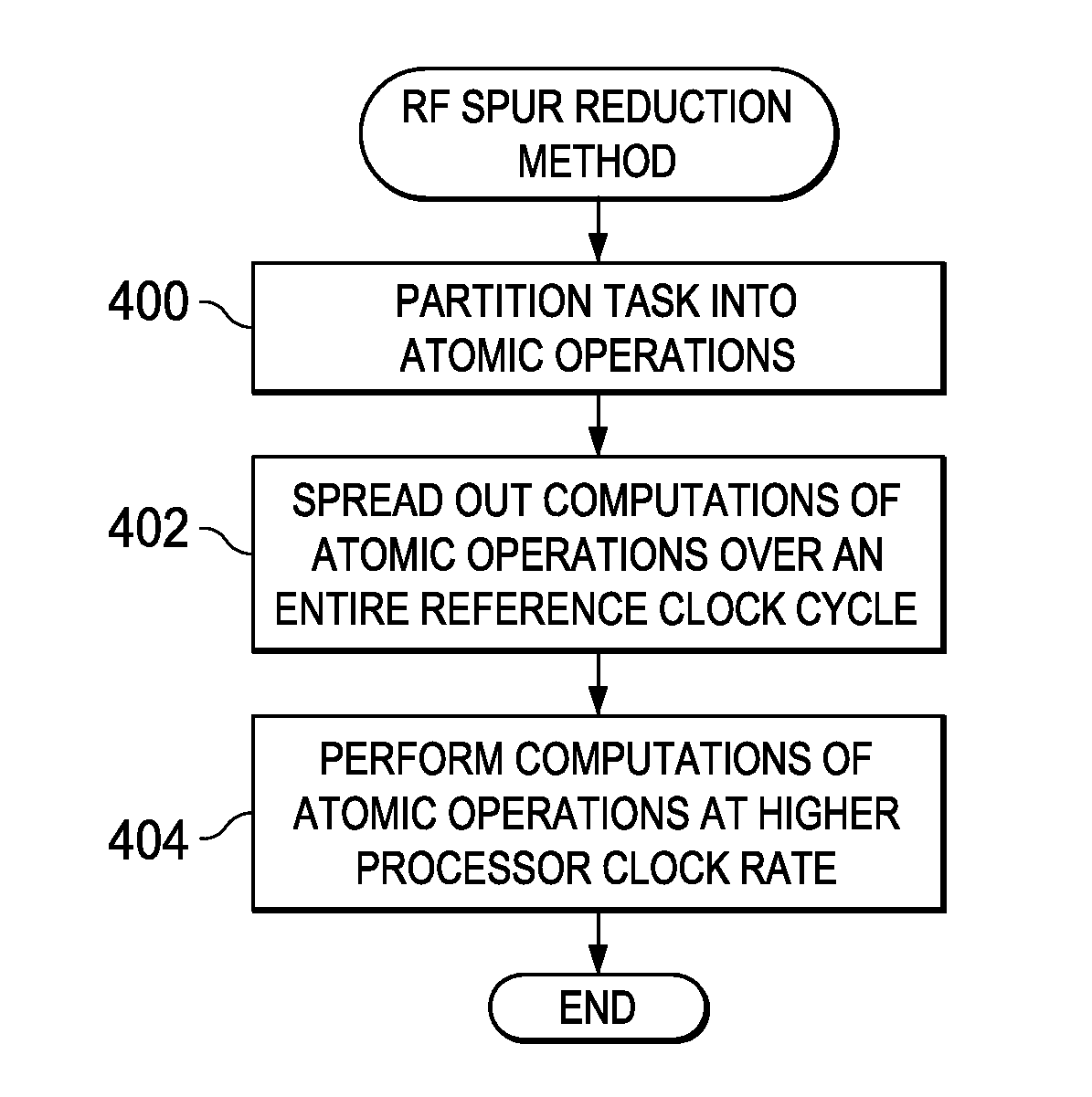

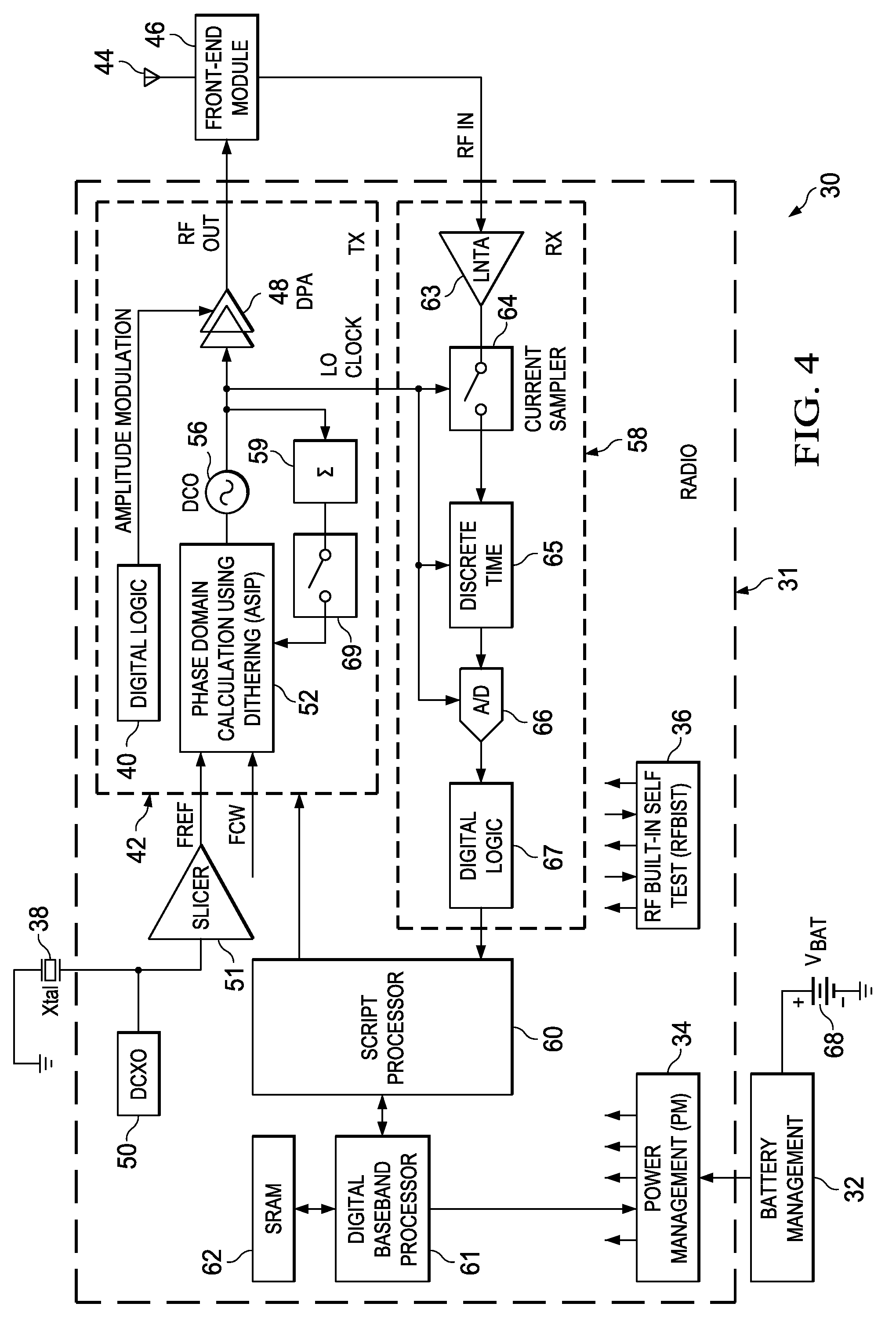

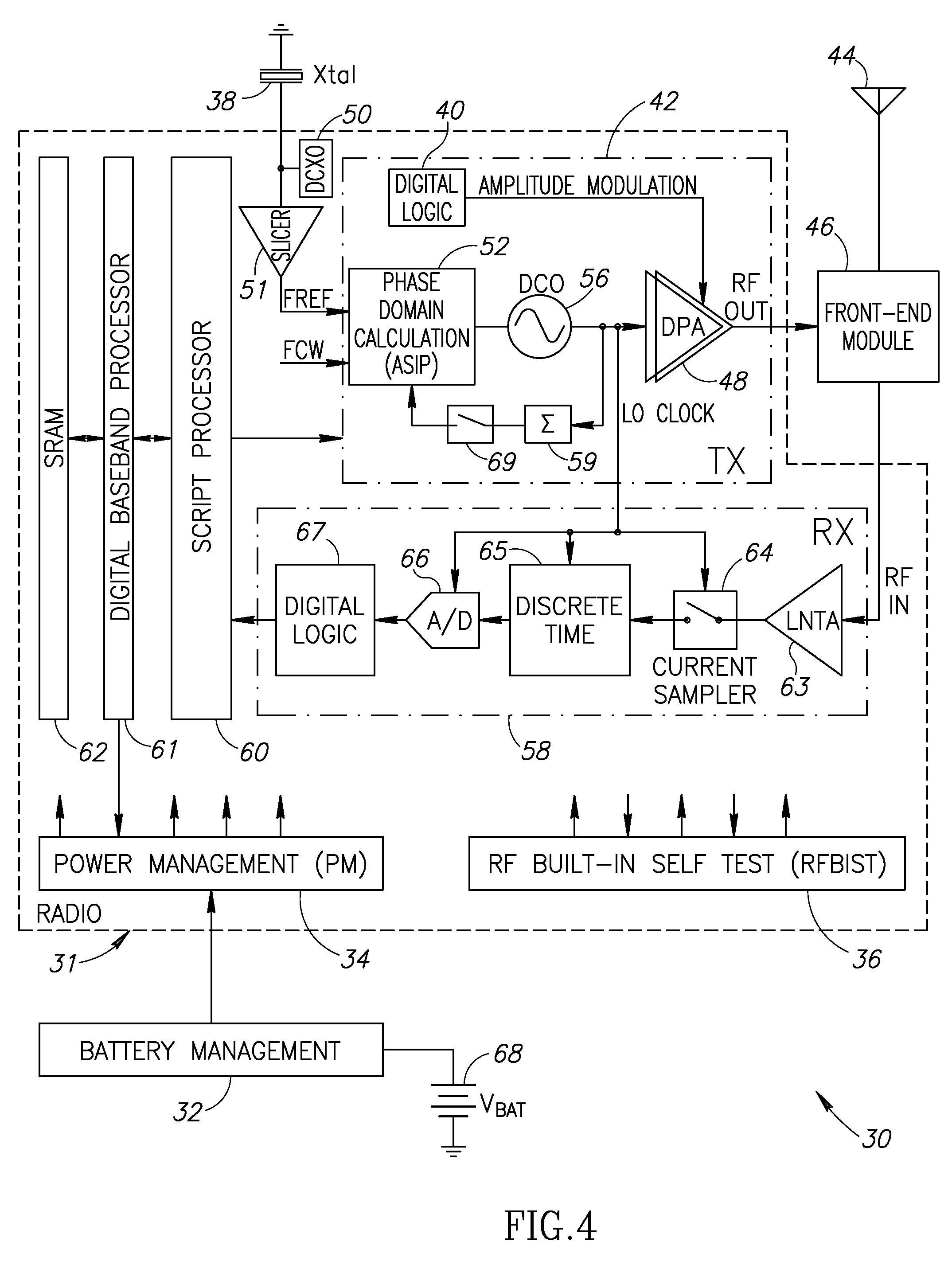

A novel and useful apparatus for and method of spur reduction using computation spreading with dithering in a digital phase locked loop (DPLL) architecture. A software based PLL incorporates a reconfigurable calculation unit (RCU) that is optimized and programmed to sequentially perform all the atomic operations of a PLL or any other desired task in a time sharing manner. An application specific instruction-set processor (ASIP) incorporating the RCU is adapted to spread the computation of the atomic operations out over a PLL reference clock period wherein each computation is performed at a much higher processor clock frequency than the PLL reference clock rate. This significantly reduces the per cycle current transient generated by the computations. The frequency content of the current transients is at the higher processor clock frequency which results in a significant reduction in spurs within sensitive portions of the output spectrum. Further reduction in spurs is achieved by dithering the duration of the software loop of atomic operations and / or by randomly shuffling one or more non-data dependent instructions within each iteration of the software loop.

Owner:TEXAS INSTR INC

Computation parallelization in software reconfigurable all digital phase lock loop

ActiveUS20090070568A1Easy to reconfigureReduce per cycle current transientPulse automatic controlGeneral purpose stored program computerData stream processingTime-sharing

Owner:TEXAS INSTR INC

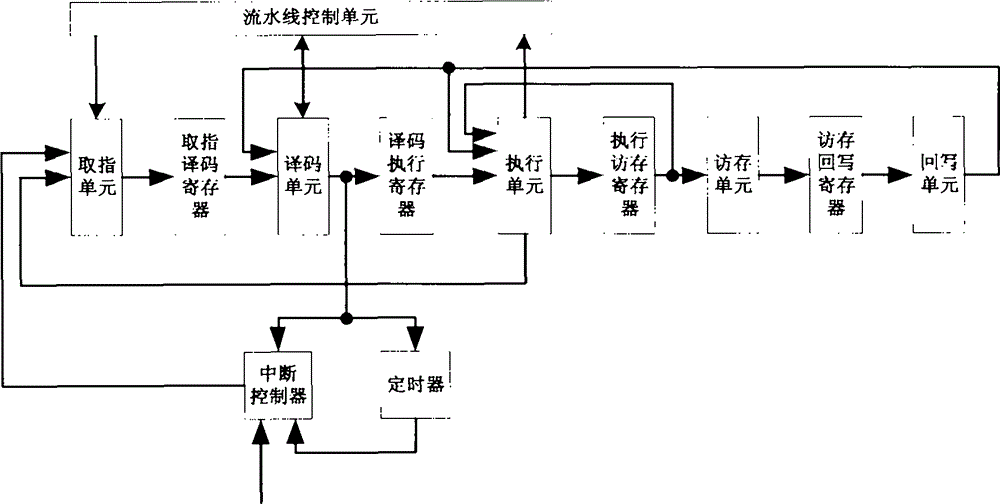

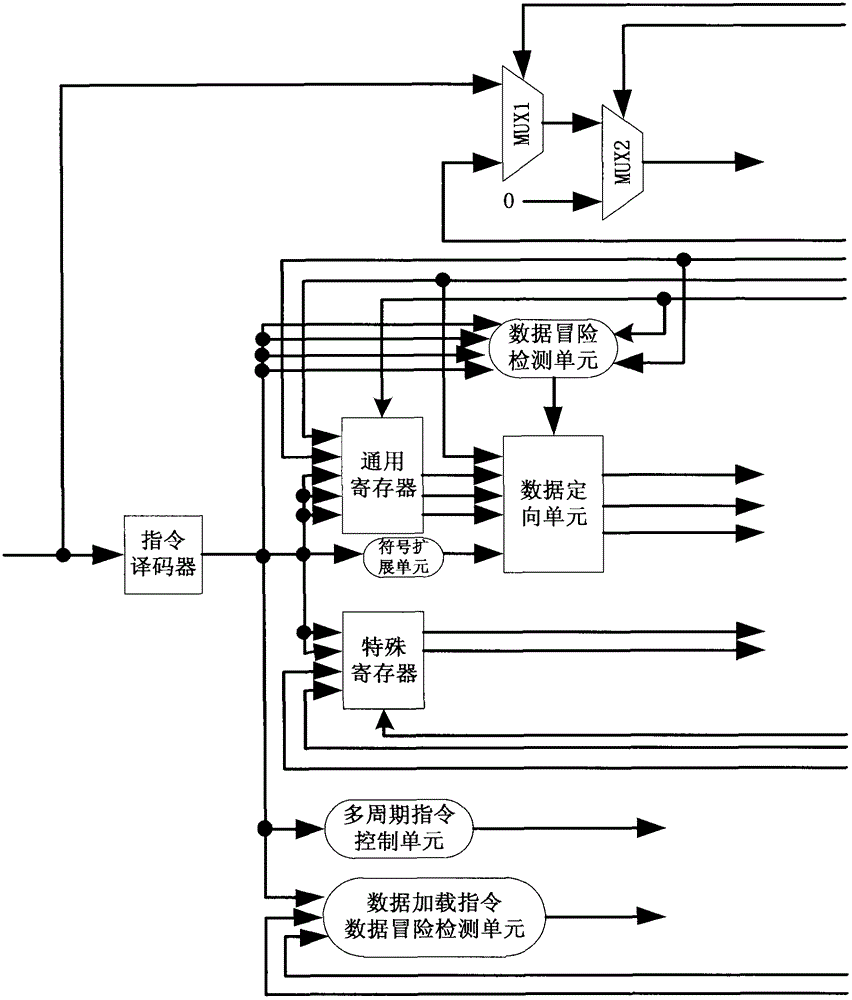

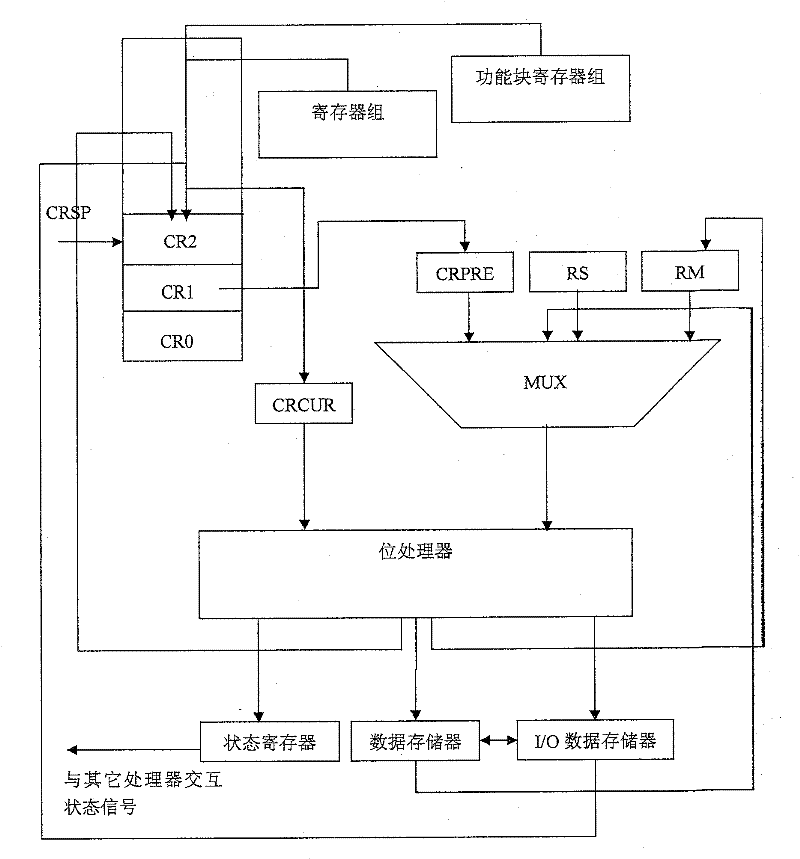

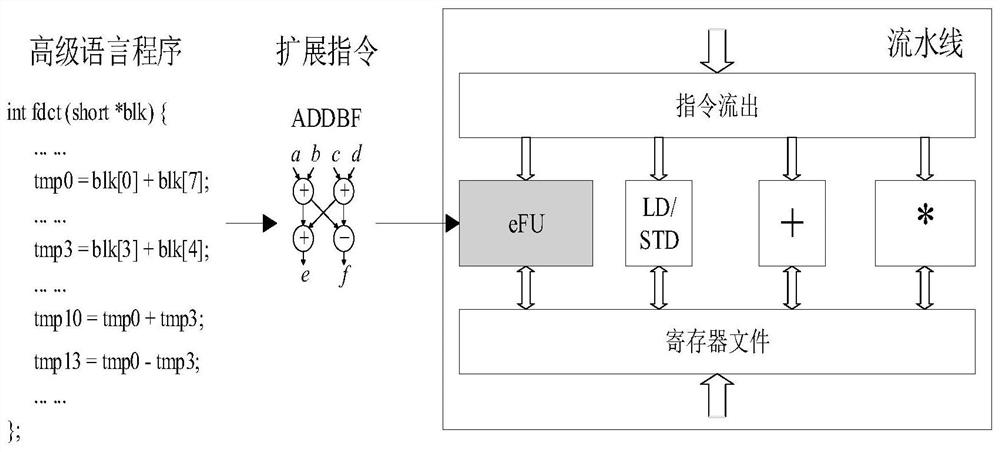

ASIP (application-specific instruction-set processor) based on extensible processor architecture and realizing method thereof

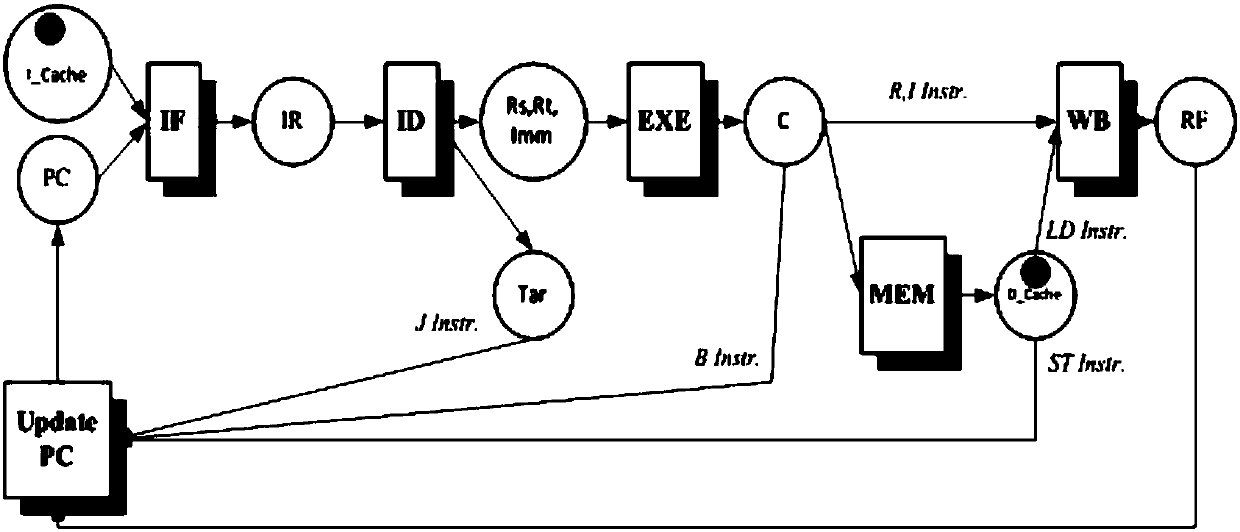

InactiveCN103150146AOvercoming complexityOvercome resourcesConcurrent instruction executionMemory systemsCircuit complexityComputer architecture

The invention discloses an ASIP based on an extensible processor architecture and a realizing method thereof, which mainly solve the problem of high circuit complexity and large resource consumption in the prior art. Aiming at the extensible processor architecture after optimization, the invention adopts a five-level-pipeline realizing method, and adopts a data orientation technology and a branch non-execution strategy to solve data hazards and control hazards in pipeline treatment respectively. The ASIP comprises an instruction fetch unit, a decoding unit, an execution unit, a memory access unit, a write-back unit, a pipeline control unit, a timer and an interrupt controller. According to the ASIP and the method, the characteristics of a pipeline processor and an FPGA (field-programmable gate array) are considered sufficiently, the pipeline structure is partitioned reasonably, and the hardware resources of the FPGA are utilized to the utmost extent; and the ASIP and the method have the advantages of simple circuit design, low resource consumption, high processor performance and low power consumption, and are highly suitable for large-scale parallel processing.

Owner:XIDIAN UNIV

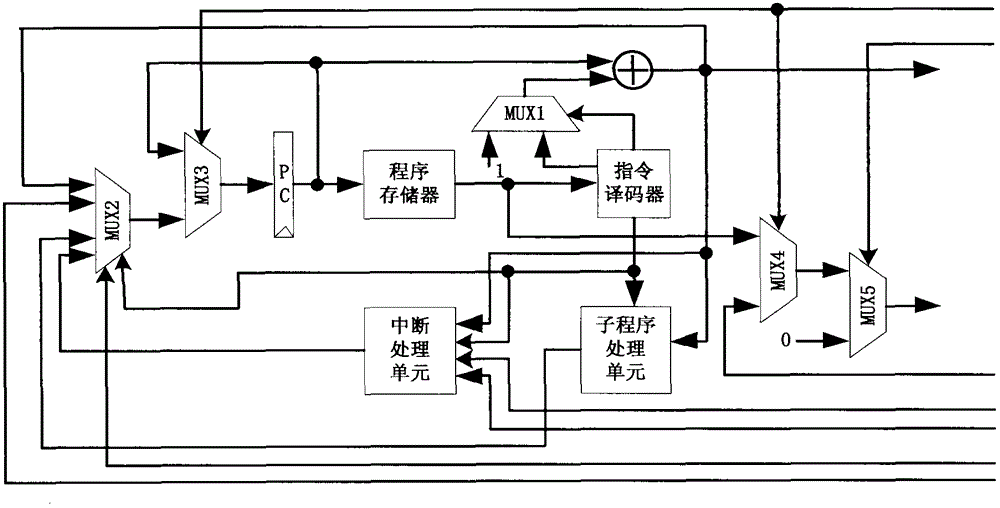

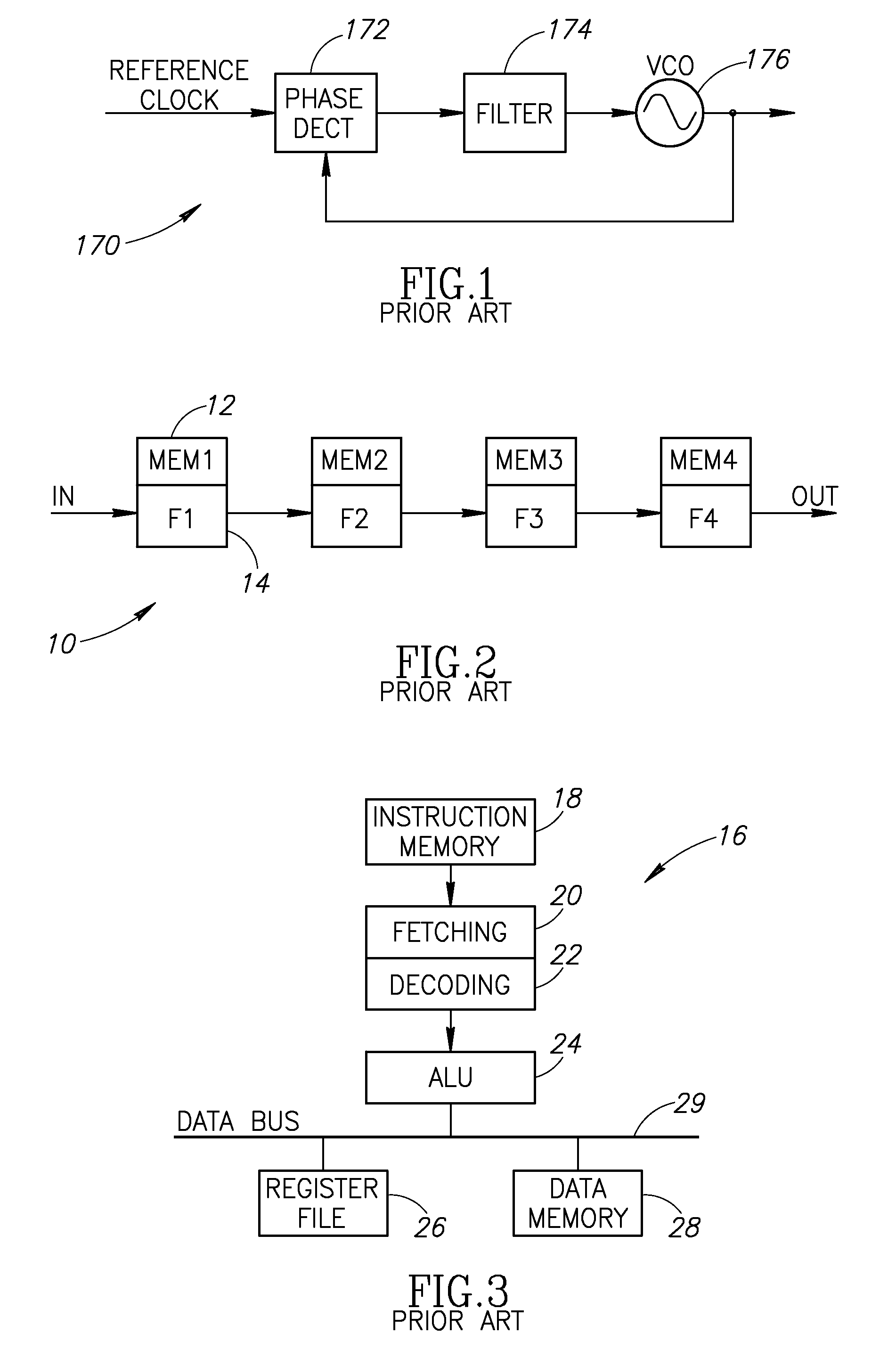

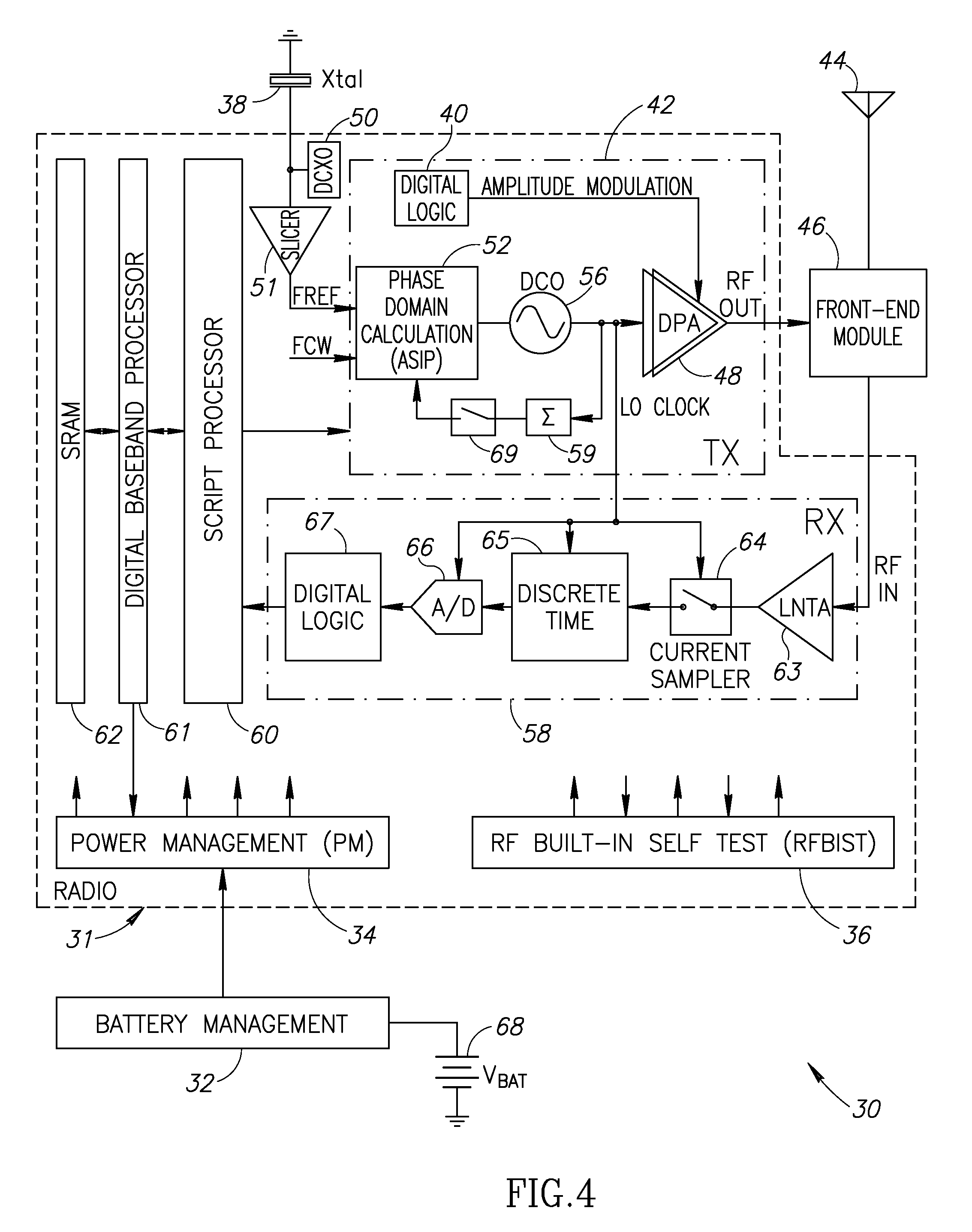

Computation spreading for spur reduction in a digital phase lock loop

ActiveUS20080069286A1Easy to reconfigureReduce generationPulse automatic controlDigital computer detailsClock rateTime-sharing

A novel and useful apparatus for and method of spur reduction using computation spreading in a digital phase locked loop (DPLL) architecture. A software based PLL incorporates a reconfigurable calculation unit (RCU) that is optimized and programmed to sequentially perform all the atomic operations of a PLL or any other desired task in a time sharing manner. An application specific instruction-set processor (ASIP) incorporating the RCU is adapted to spread the computation of the atomic operations out over and completed within an entire PLL reference clock period. Each computation being performed at a much higher processor clock frequency than the PLL reference clock rate. This functions to significantly reduce the per cycle current transient generated by the computations. Further, the frequency content of the current transients is at the higher processor clock frequency. This results in a significant reduction in spurs within sensitive portions of the output spectrum.

Owner:TEXAS INSTR INC

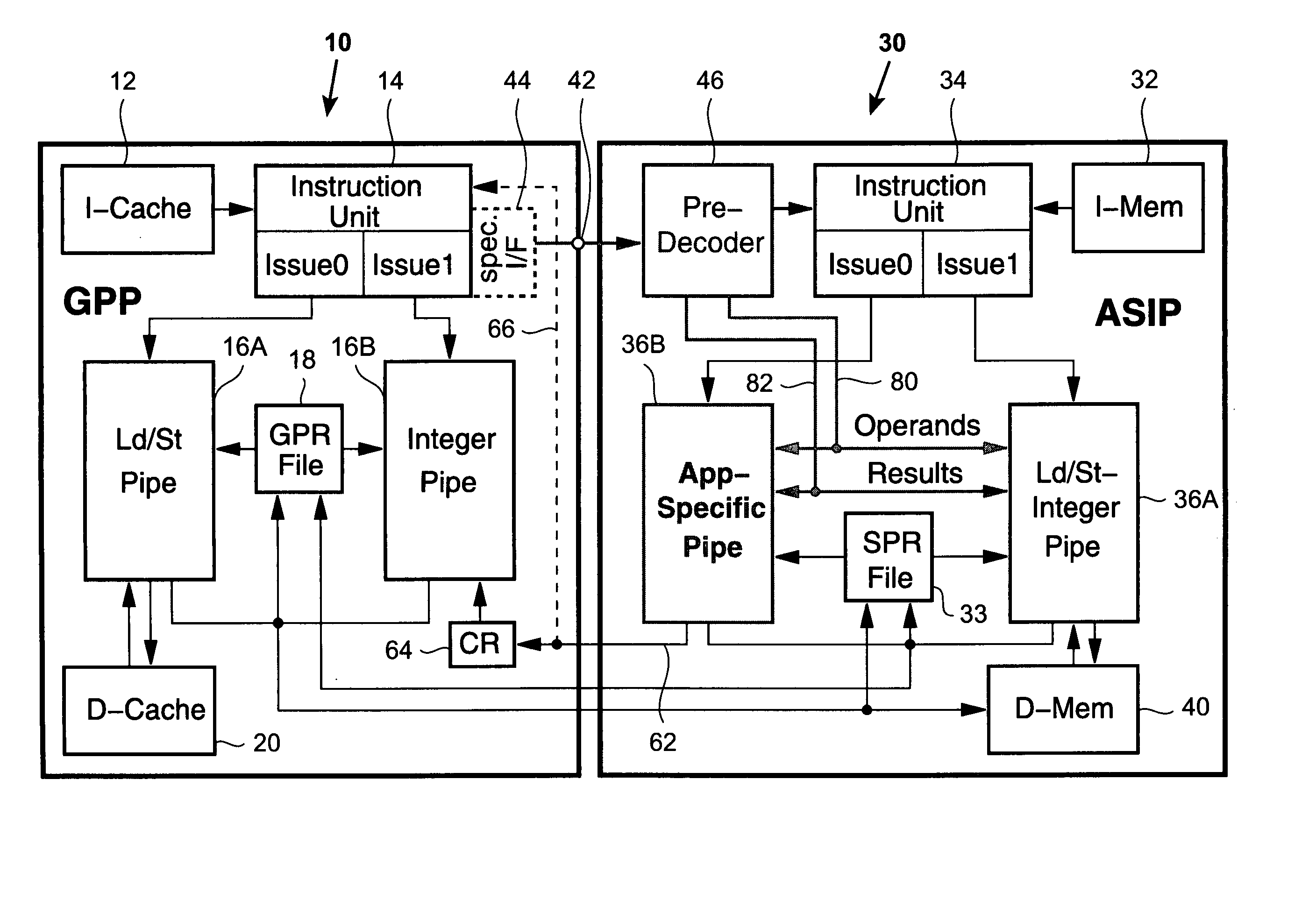

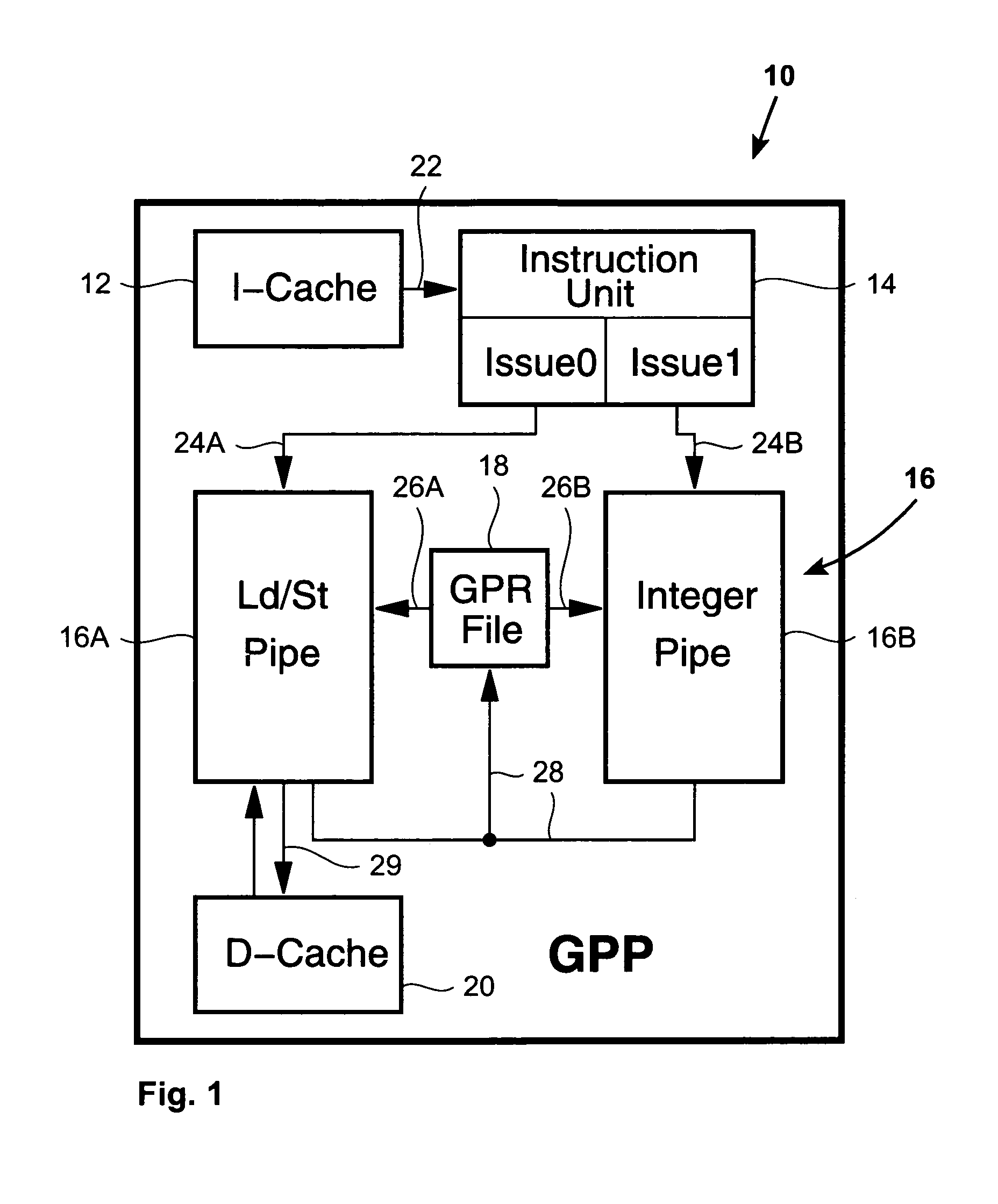

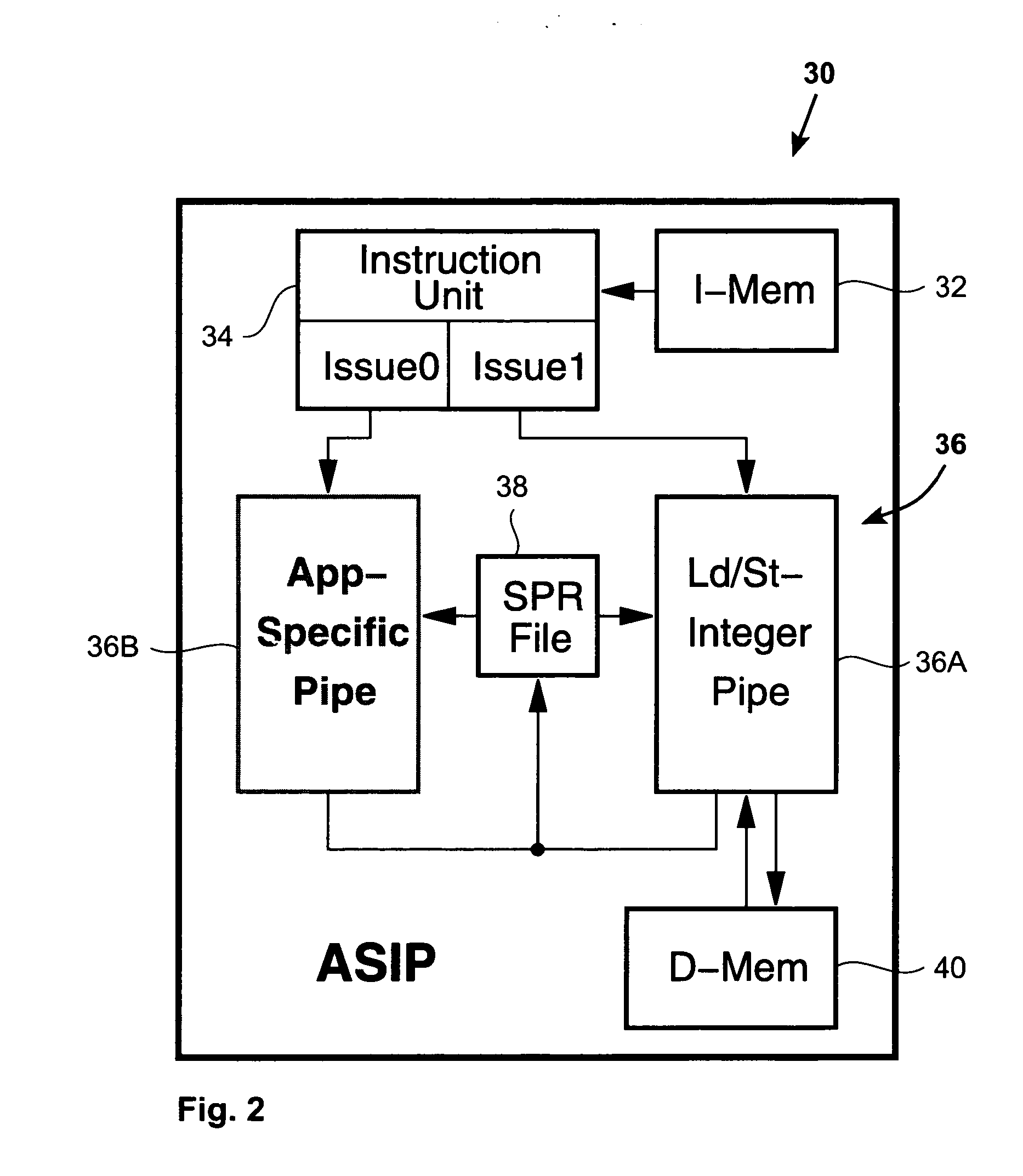

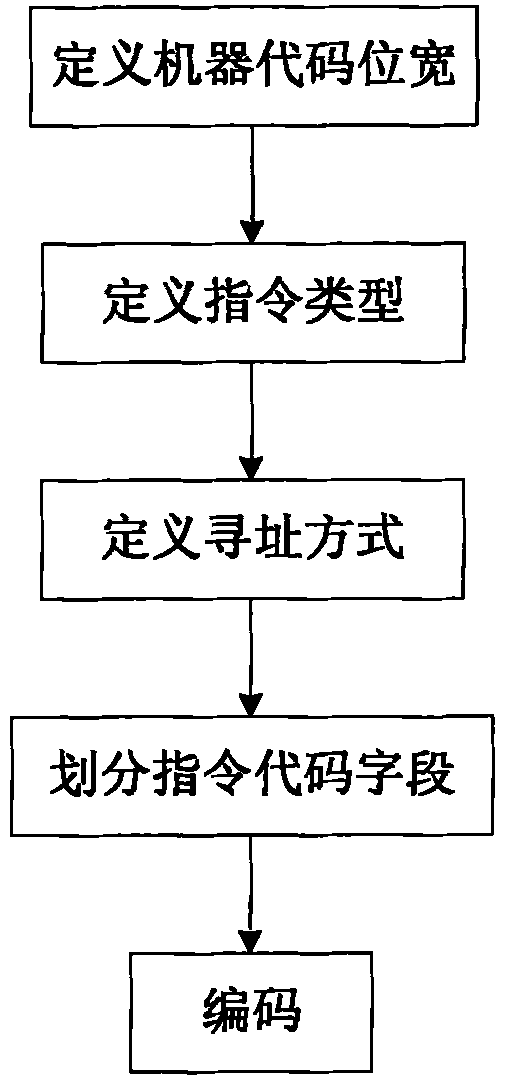

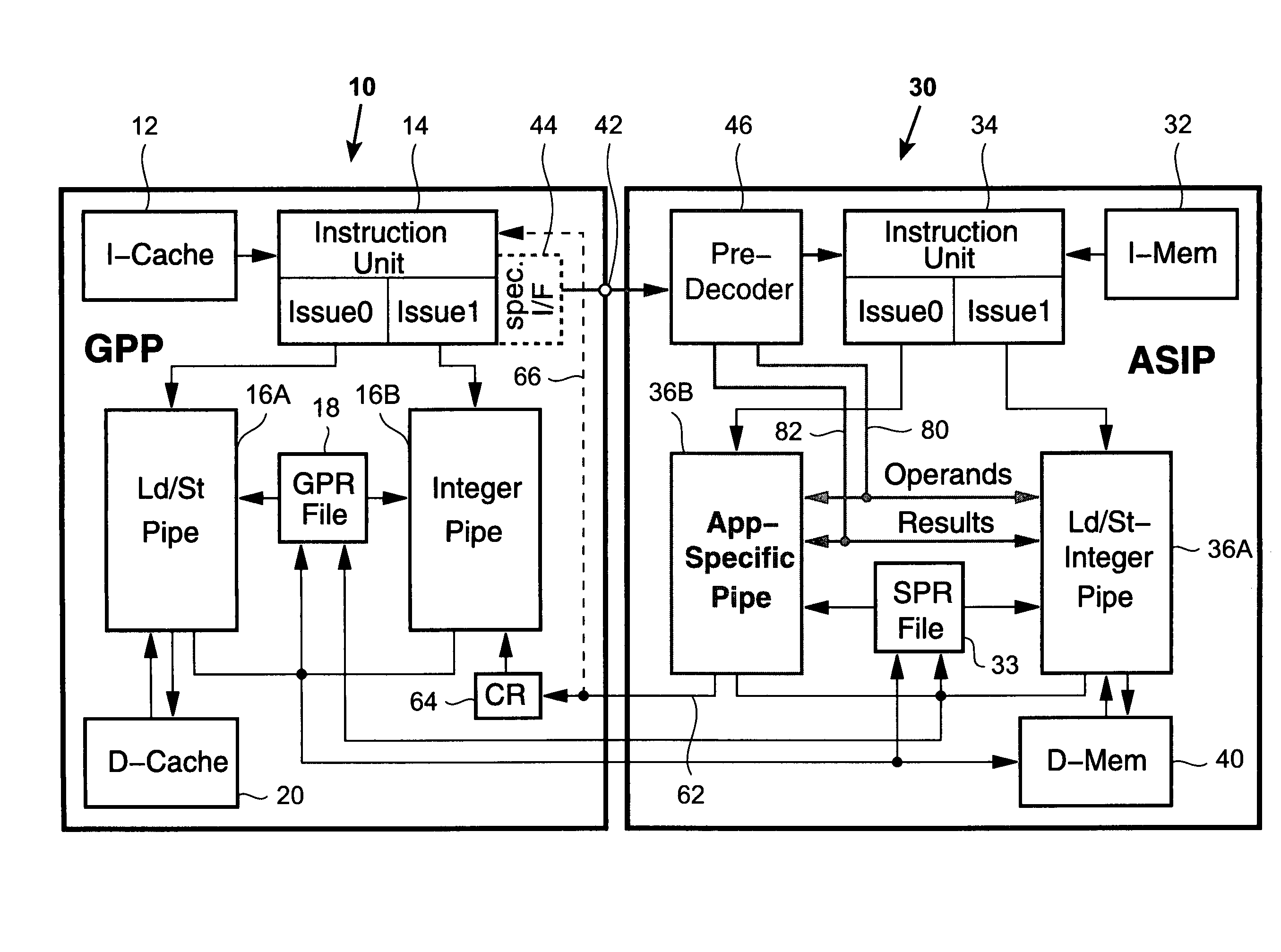

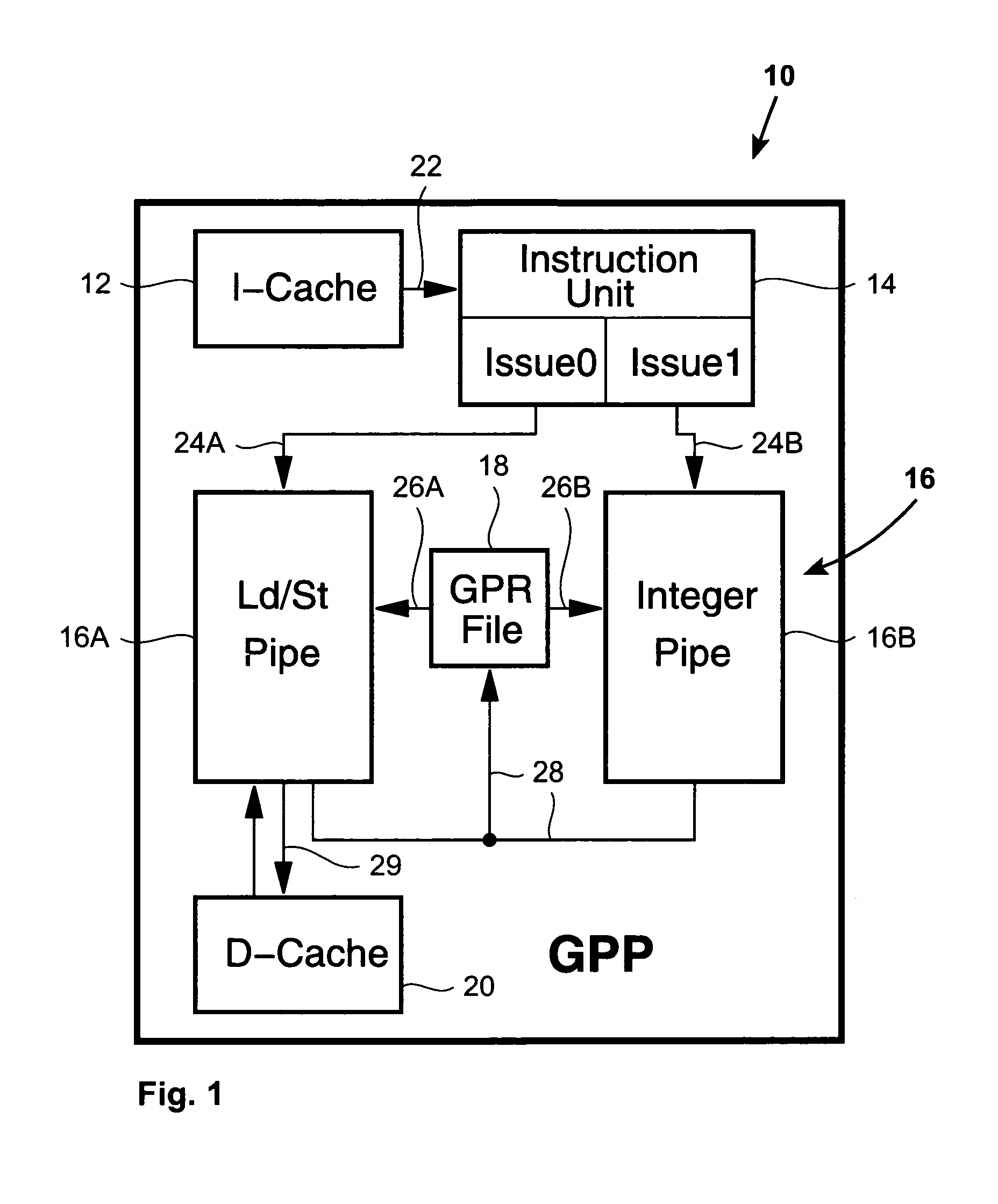

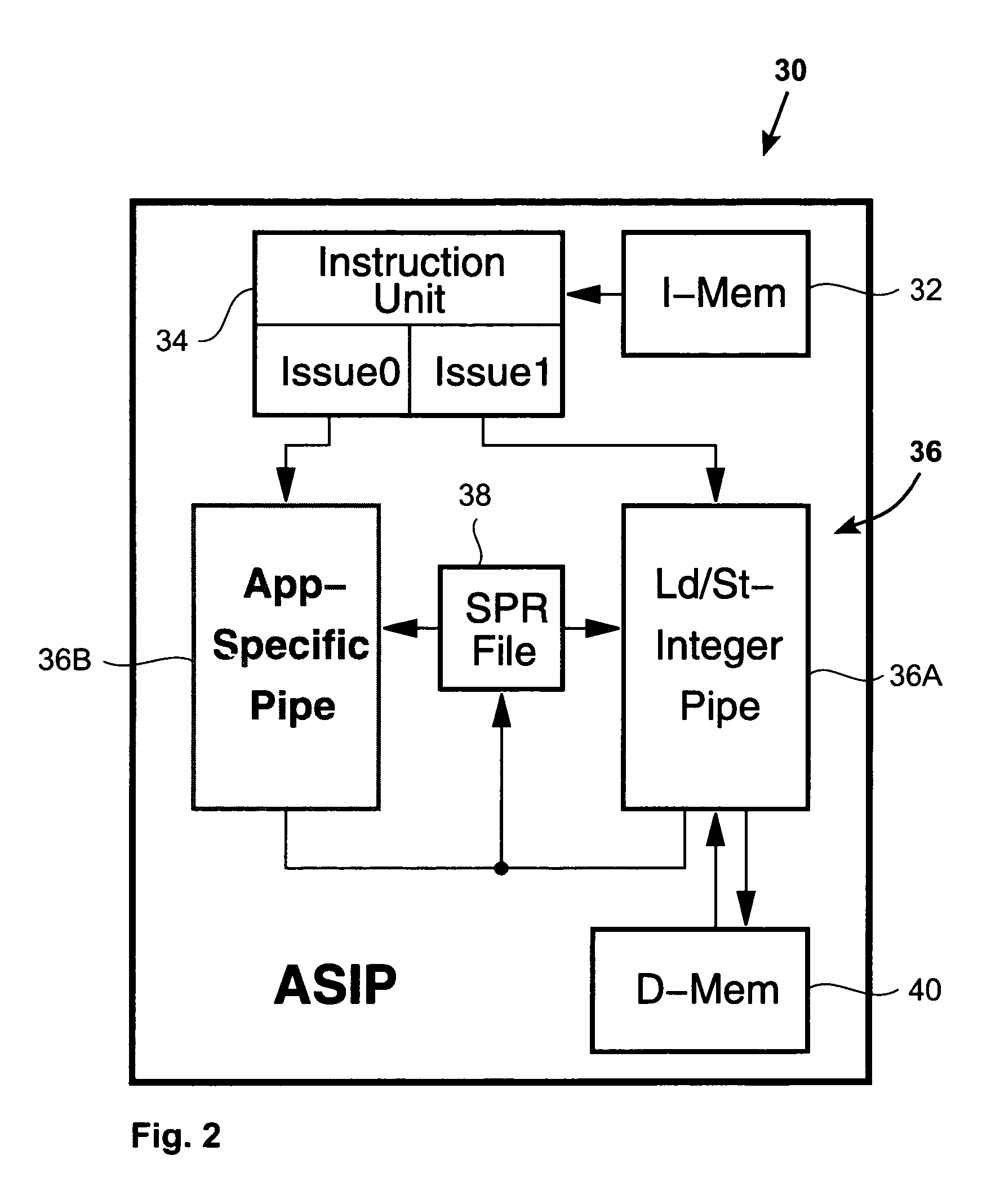

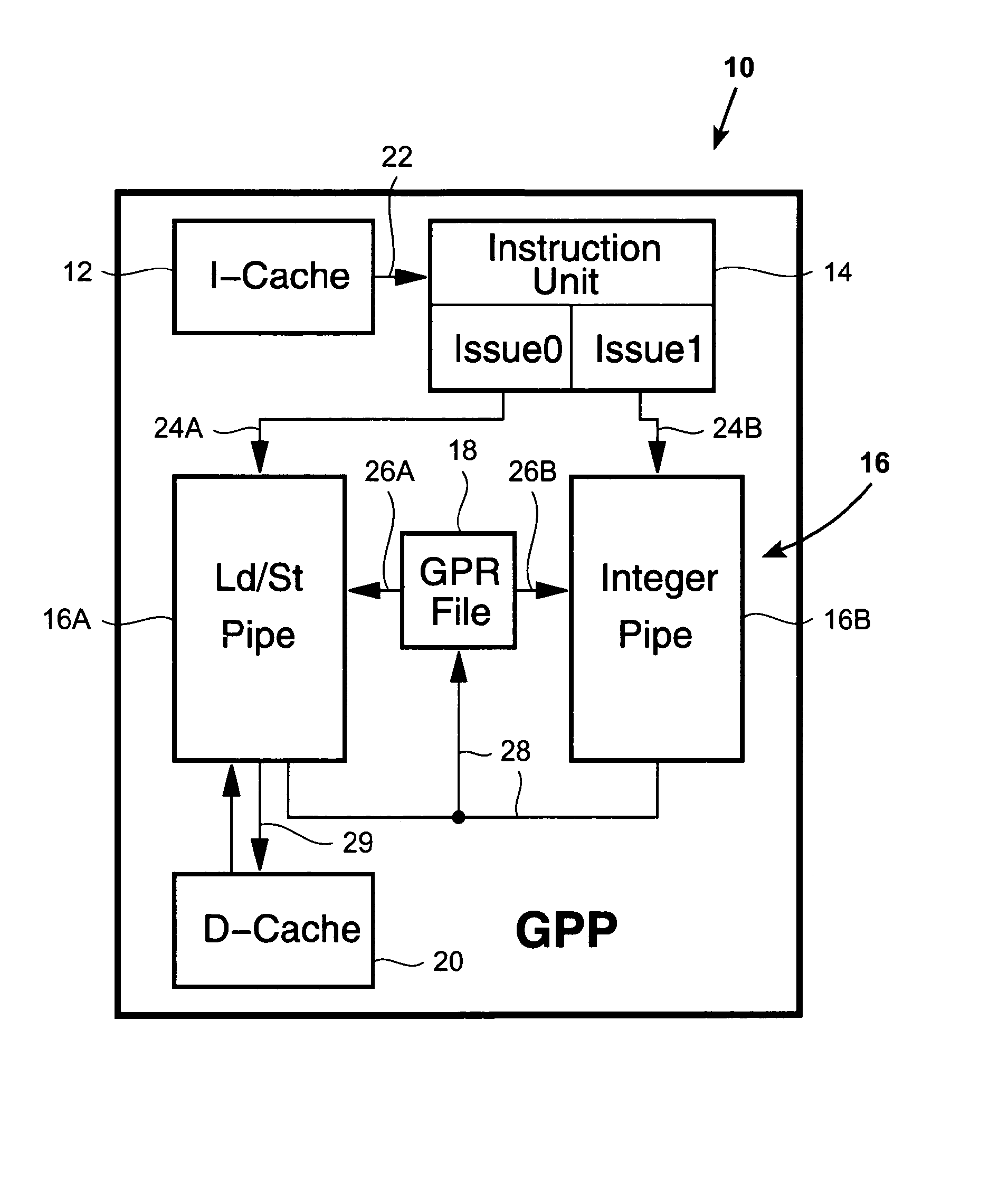

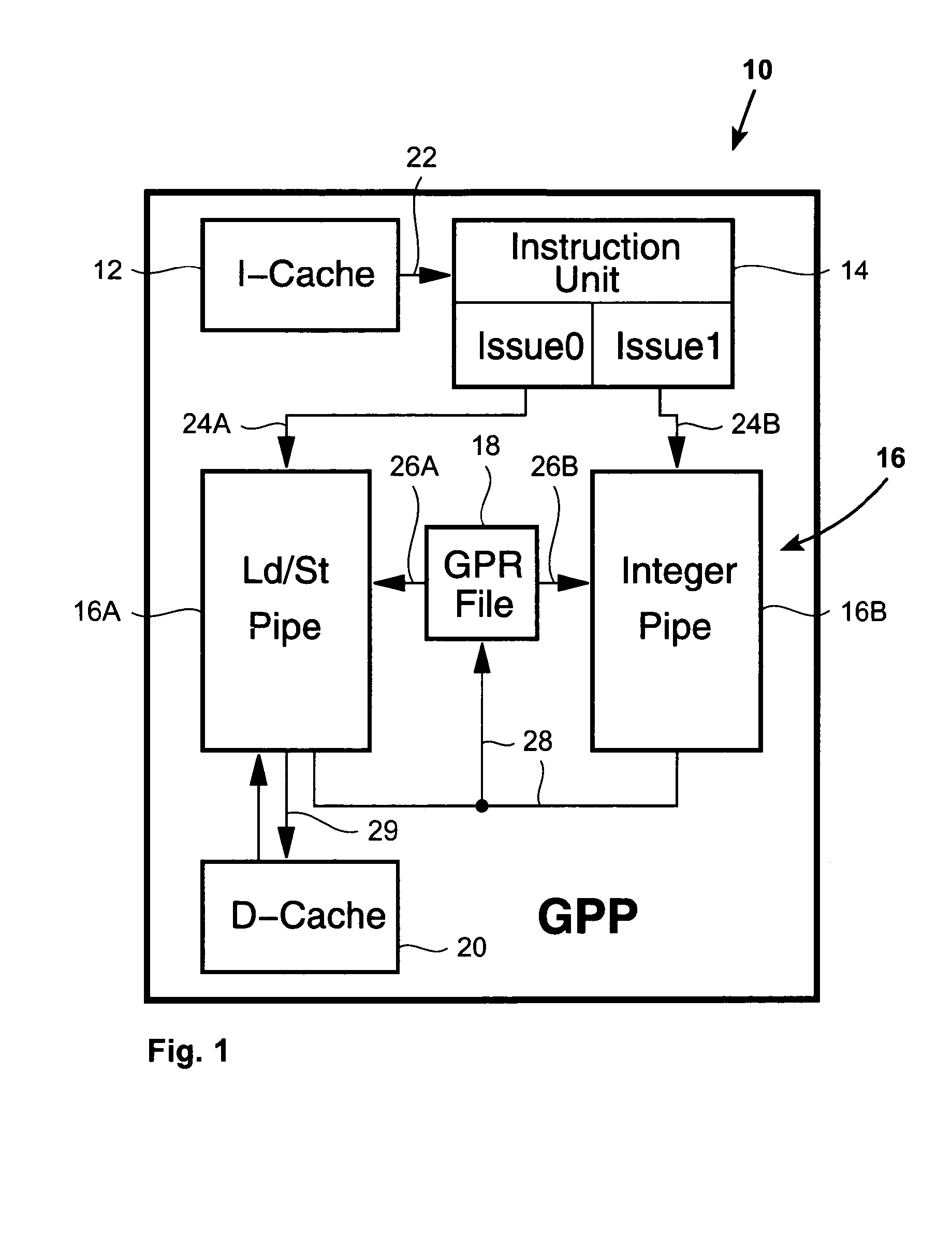

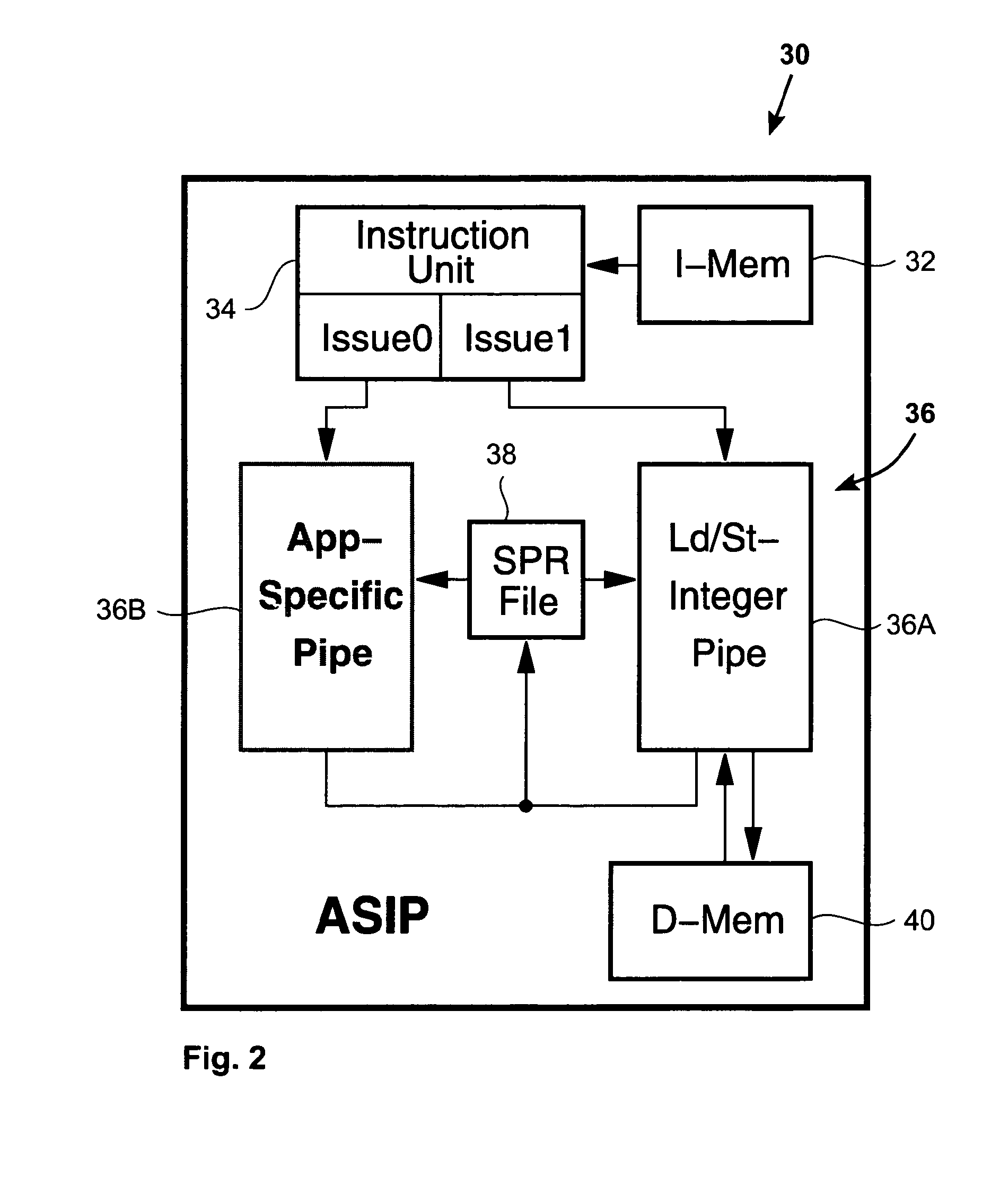

Coupling a general purpose processor to an application specific instruction set processor

InactiveUS20050172105A1Improve efficiencyRuntime instruction translationGeneral purpose stored program computerGeneral purposeInstruction memory

Provides methods, systems and apparatus for coupling a general purpose processor (GPP) to an application specific instruction set processor (ASIP) in such a manner that the GPP can include execute instructions that do not normally comprise part of its instruction set architecture (ISA). The GPP is coupled to the ASIP via a coprocessor port such that instructions issued by the GPP to the port are conveyed to a novel pre-decoder module of the ASIP. The pre-decoder module translates the GPP instruction into operation codes for ASIP instructions to be executed in the ASIP or to an address in the ASIP instruction memory that identifies a start address for a plurality of ASIP instructions defining a complex application specific function. Once the ASIP has executed the instructions it shares the result of the execution with the GPP. In this way, the GPP takes advantage of the ASIP in its ability to more quickly execute an application specific program / procedure.

Owner:IBM CORP

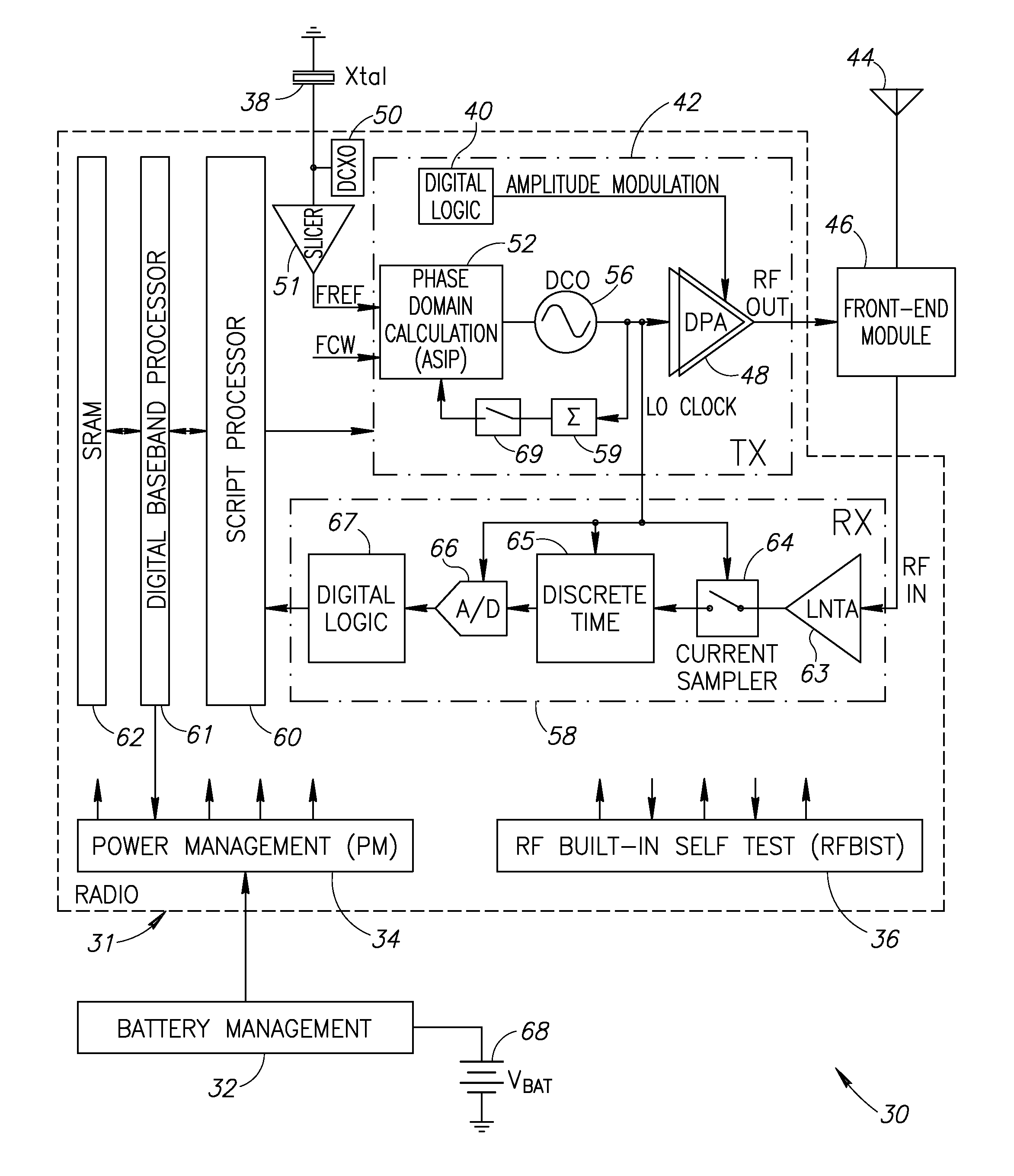

Software reconfigurable digital phase lock loop architecture

ActiveUS8321489B2Easy to reconfigureLow spuriousSynchronisation arrangementPulse automatic controlClock rateTime-sharing

A novel and useful apparatus for and method of software based phase locked loop (PLL). The software based PLL incorporates a reconfigurable calculation unit (RCU) that is optimized and programmed to sequentially perform all the atomic operations of a PLL or any other desired task in a time sharing manner. An application specific instruction-set processor (ASIP) incorporating the RCU includes an instruction set whose instructions are optimized to perform the atomic operations of a PLL. The RCU is clocked at a fast enough processor clock rate to insure that all PLL atomic operations are performed within a single PLL reference clock cycle.

Owner:TEXAS INSTR INC

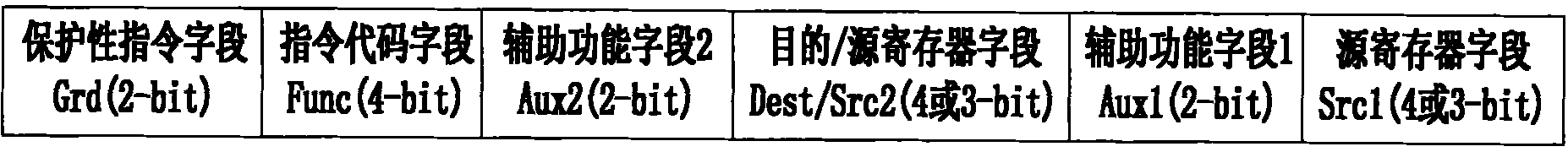

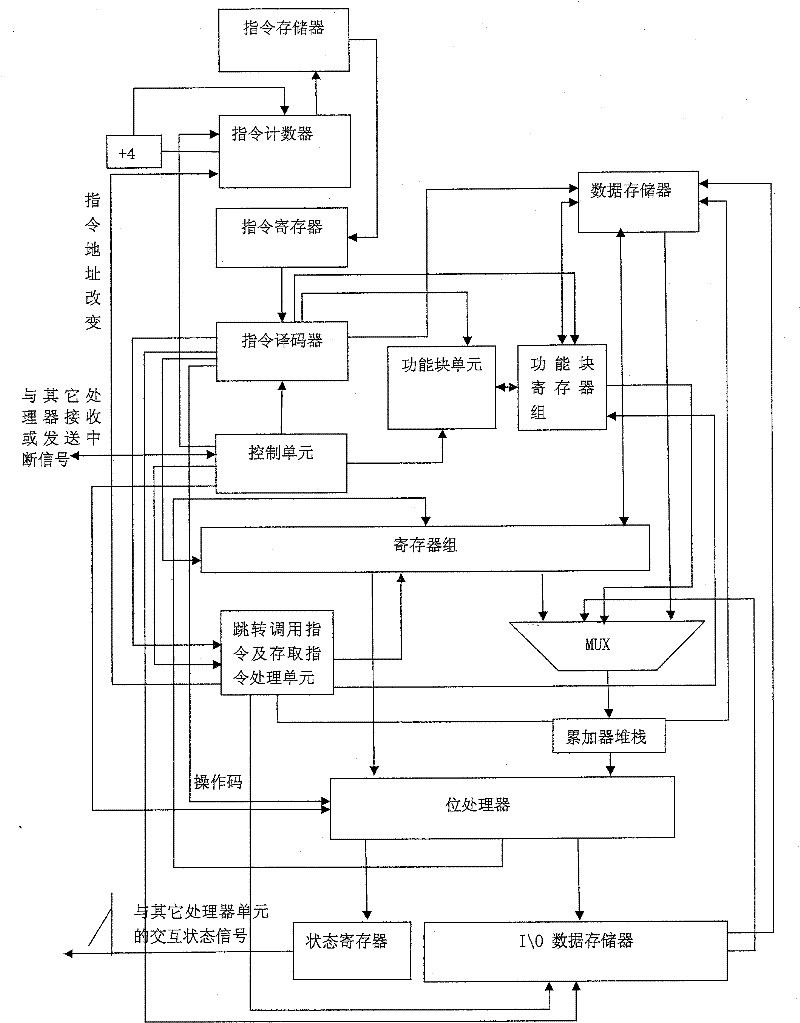

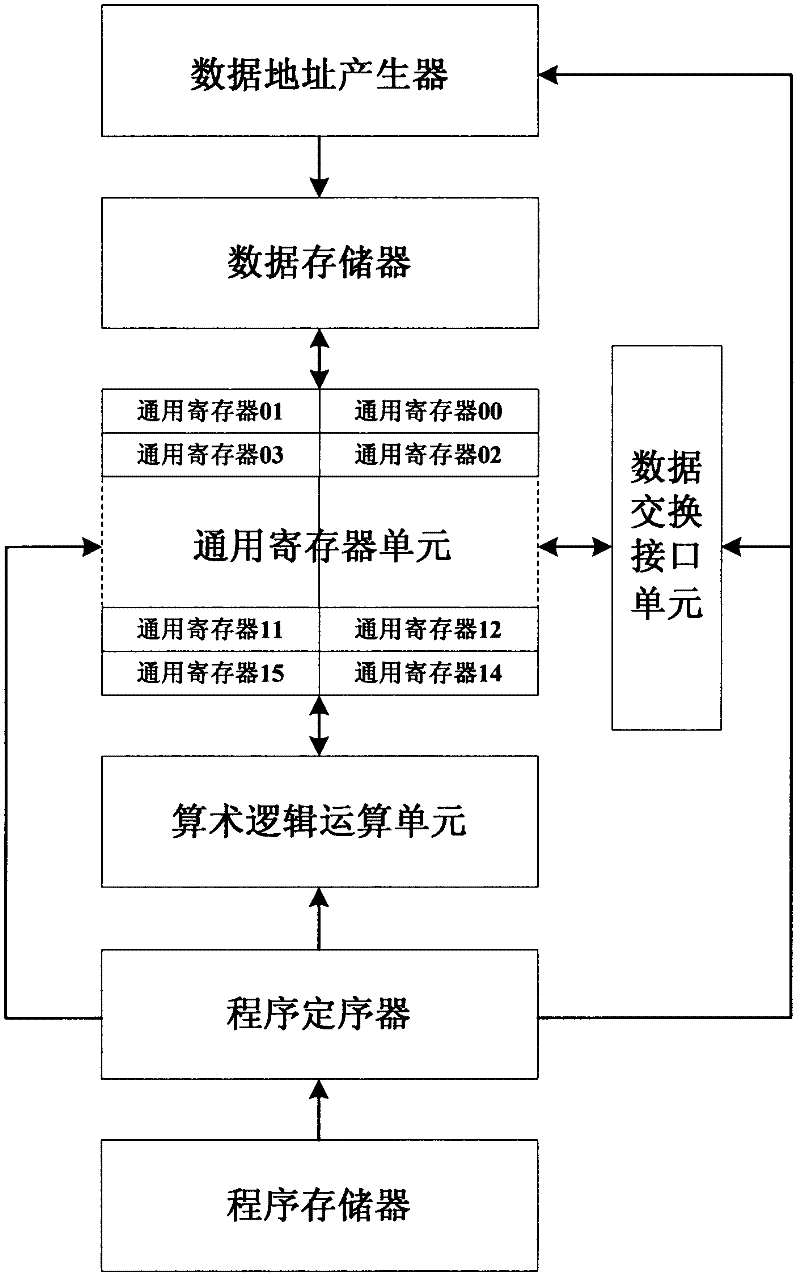

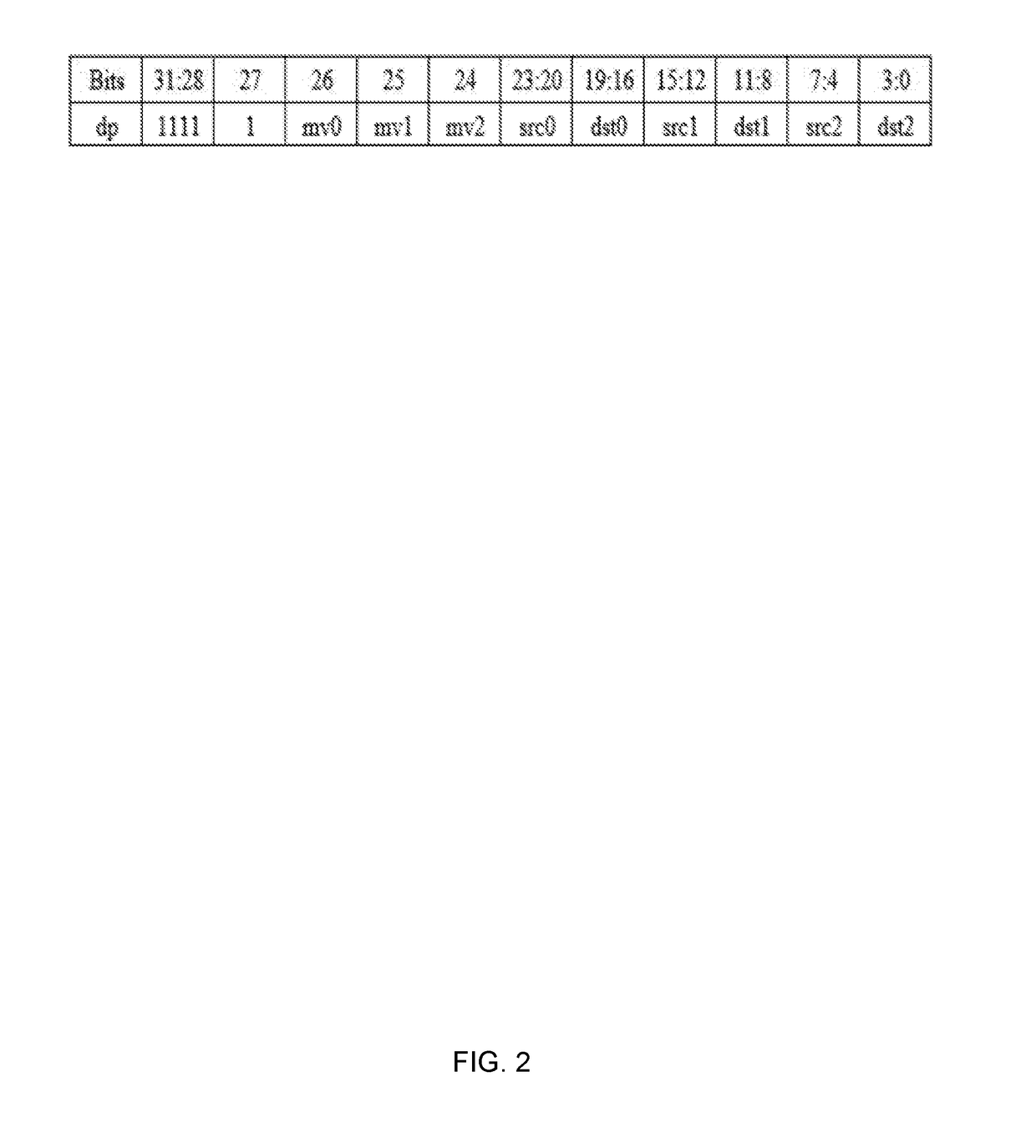

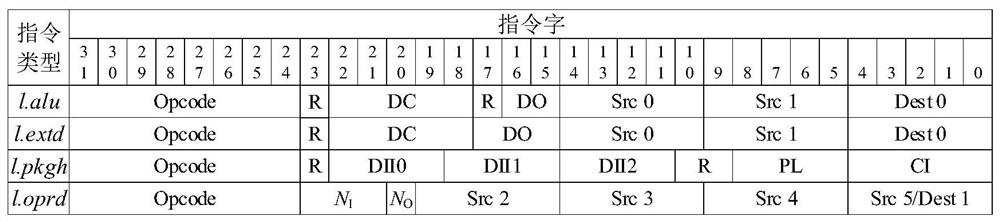

Instruction set encoding method based on embedded special instruction set processor

ActiveCN102221987AImprove utilization efficiencyGuaranteed uptimeConcurrent instruction execution18-bitInternal memory

The invention provides an instruction set encoding method based on an embedded special instruction set processor, comprising five steps of: defining machine code bit wide, defining instruction type, a defining addressing mode, a dividing instruction code filed and encoding. The instruction set is optimized according to the characteristic that both an internal memory and a data bus resource of a Field Programmable Gate Array (FPGA) take 18 bits as basic bit wide. The instruction set comprises 16 pieces of multifunctional instructions in the types of arithmetic and logic operation, data interchange and program sequencing, wherein the instructions comprise protective instruction fields required for constructing a single instruction stream-multiple data stream concurrent processing system with instruction independency capability. The instruction set disclosed by the invention has integral and simplified application models; under the two application models, the code length of an instruction machine can be respectively shortened to 16-bit and 14-bit so that the utilization efficiency of an internal circuit resource of the FPGA and the instruction execution speed of a processor are greatly improved.

Owner:XIDIAN UNIV

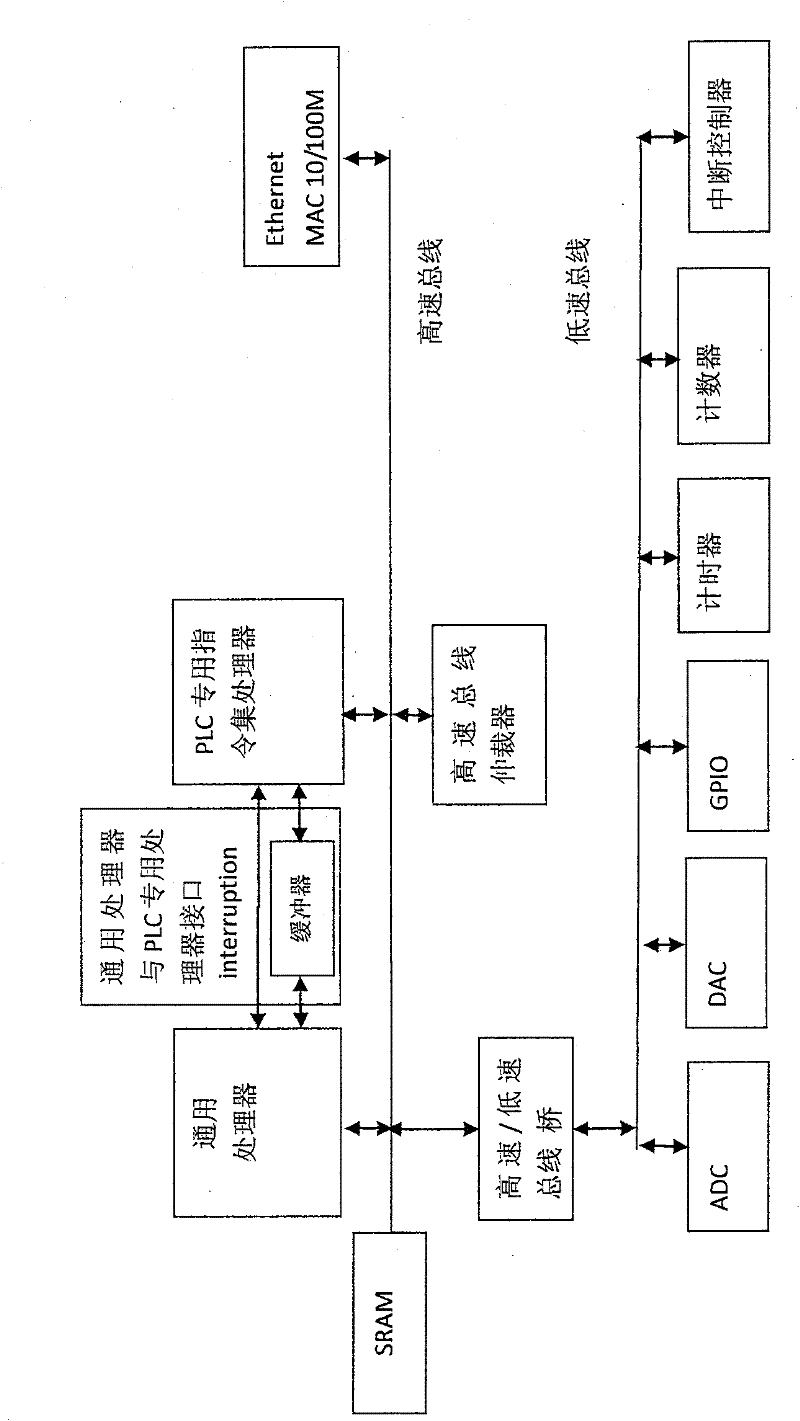

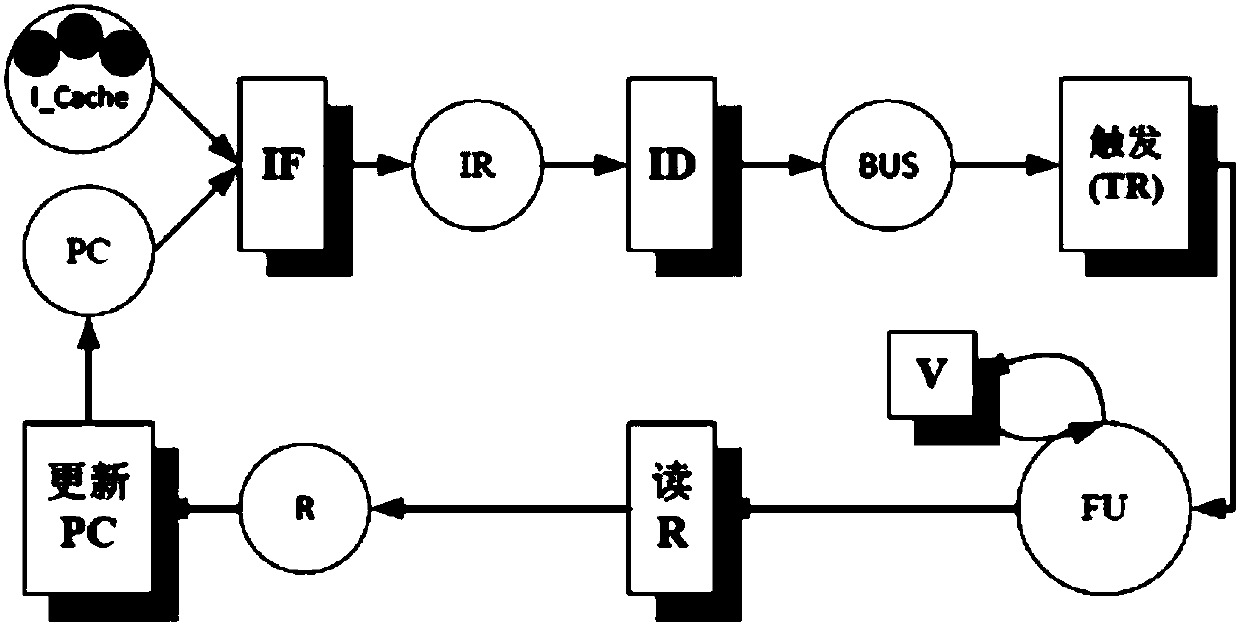

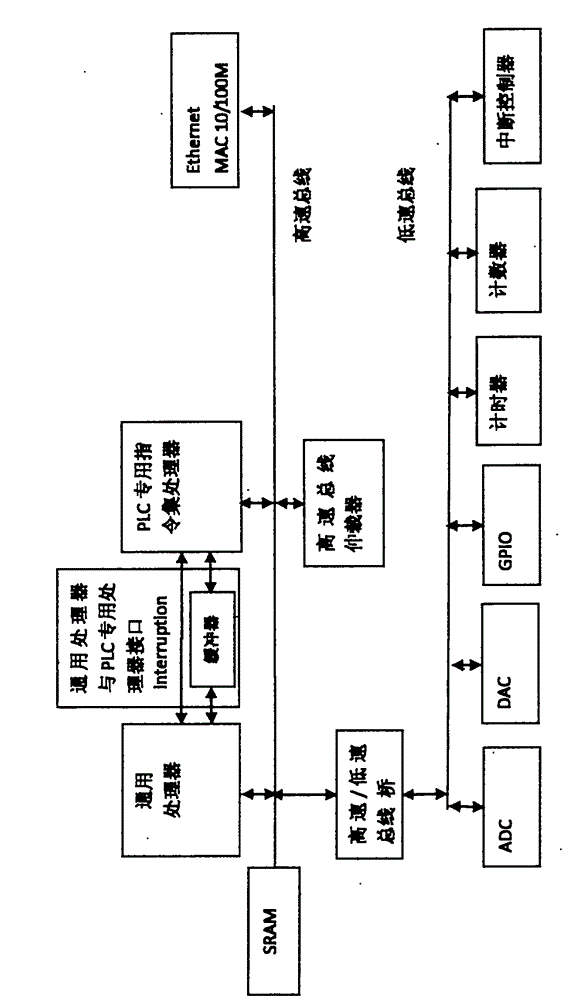

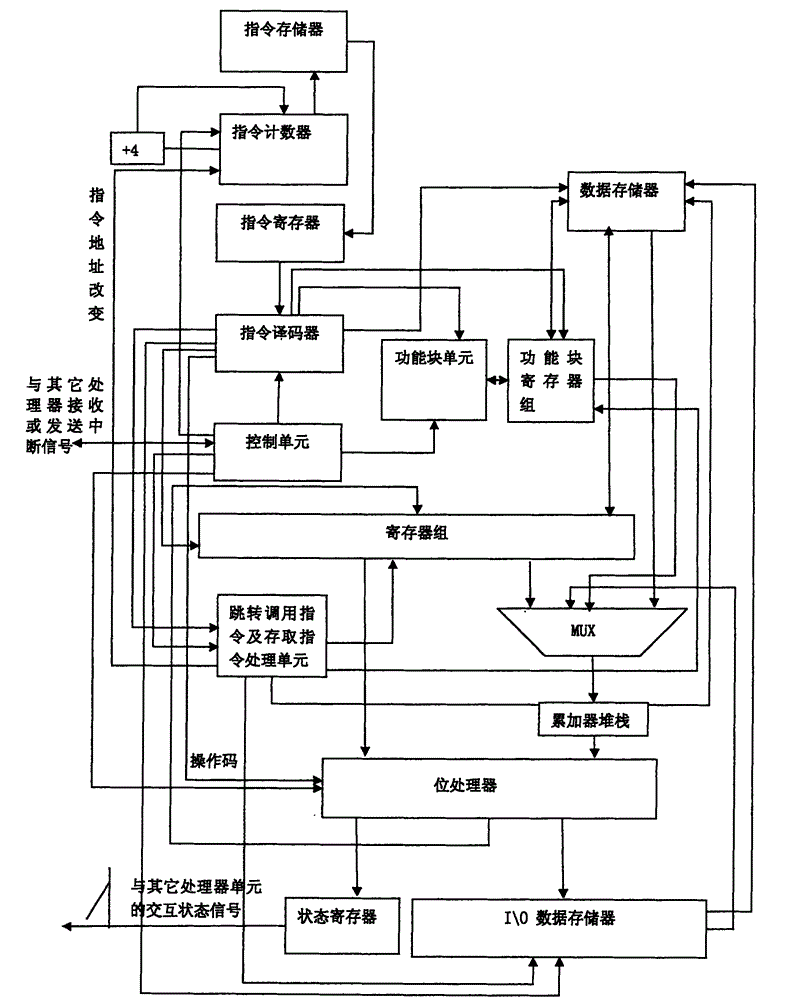

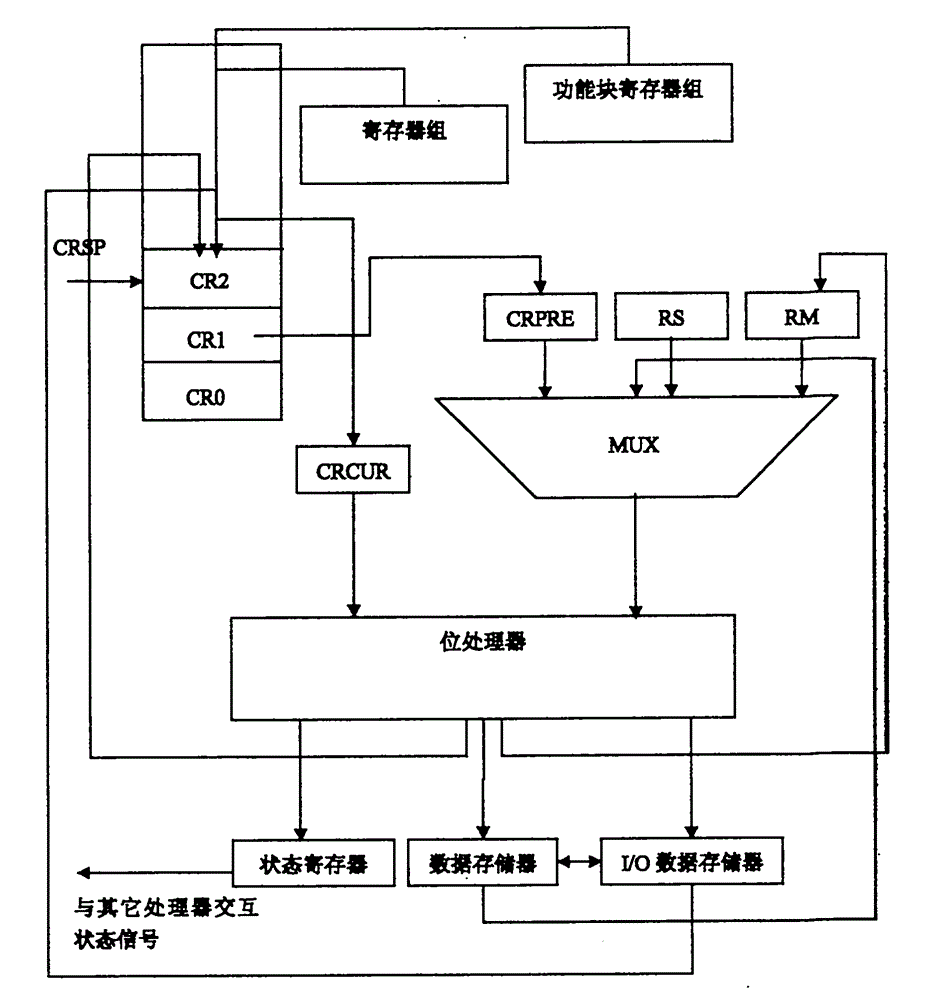

High-performance Programmable Controller Special Processor Architecture and Its Realization Method

ActiveCN102298352AReduce the number of instructionsFast executionProgramme control in sequence/logic controllersComputer architectureProgrammable logic controller

The invention relates to a specific processor system structure for a high-performance programmable controller and an implementation method of the dedicated processor system structure. The specific processor system structure comprises a PLC (Programmable Logic Controller) specific instrument set processor and a general processor, wherein the PLC specific instrument set processor is connected with a general processor through the PLC specific instrument set processor and an interface of the general processor. The implementation method comprises a four-level flow line consisting of a fetch stage,a decoding stage, an executing stage and a writing-back stage, according to the PLC specific instrument set processor. By designing the PLC specific instrument set which accords with the PLC instrument characteristics, the number of instruments for executing a PLC processor is reduced, the execution speed of a PLC program is accelerated, and the processing performance of the PLC processor to a functional block is improved.

Owner:SHENYANG INST OF AUTOMATION - CHINESE ACAD OF SCI

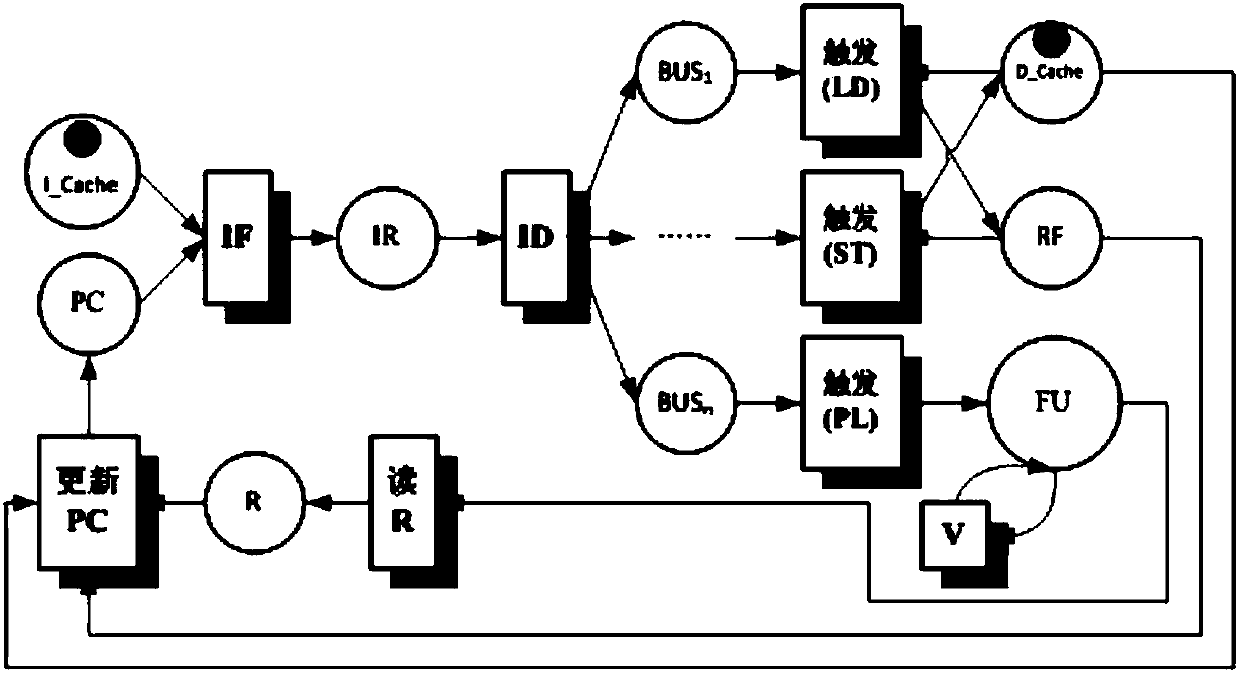

Assembler designing method based on specific instruction set processor for very long instruction words

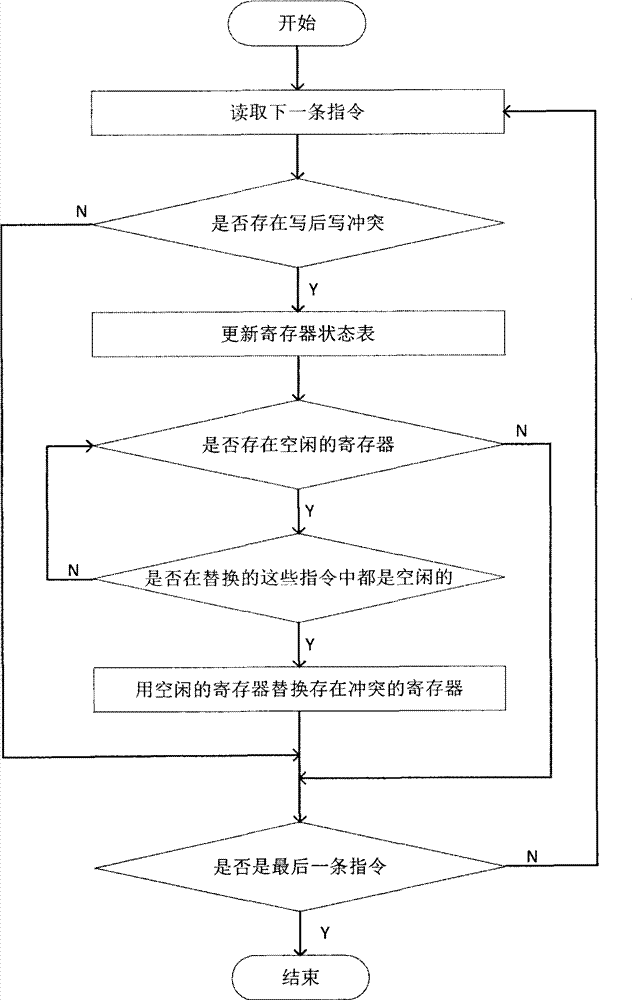

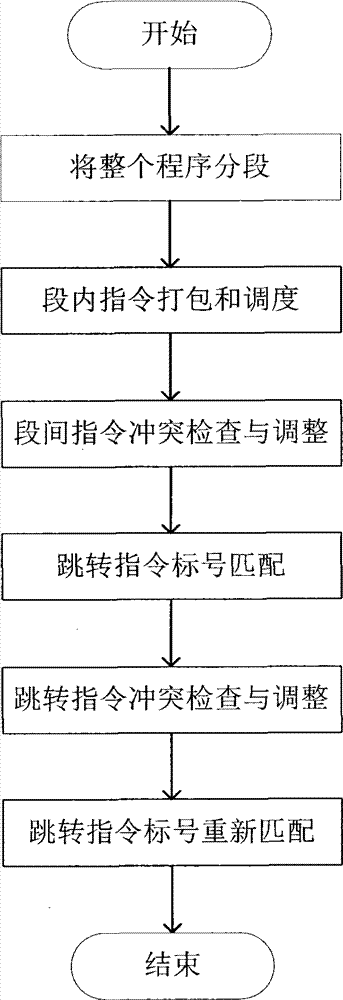

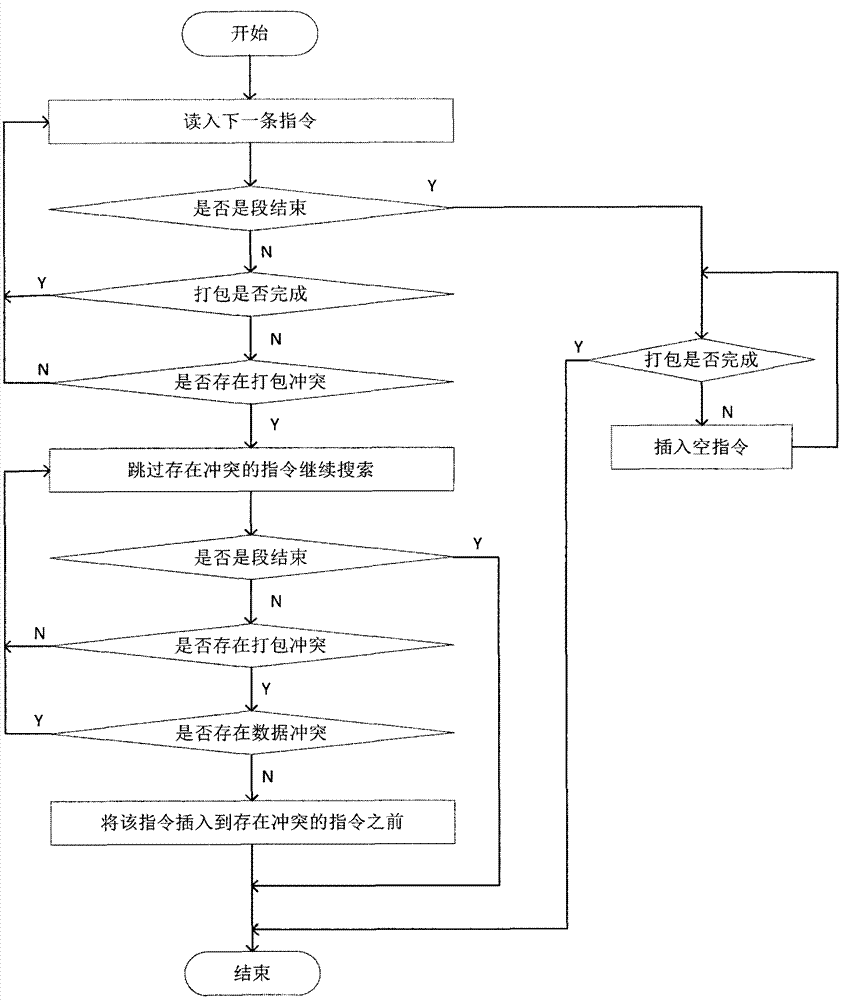

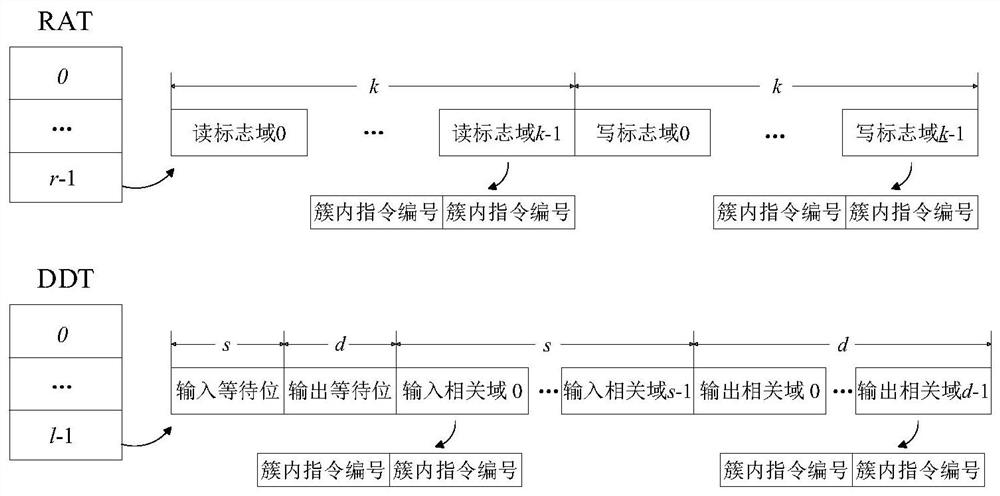

InactiveCN103116485AEliminate write-after-write conflictsImprove parallelismConcurrent instruction executionScheduling instructionsApplication specific

The invention discloses an assembler designing method based on a specific instruction set processor for very long instruction words. Improving of an assembler is realized by designing functions of register renaming and instruction packing and scheduling. The method includes that after write-after-write collisions are detected in instructions by the register renaming, a register always being idle is searched to replace a destination register in the instructions to eliminate the write-after-write collisions; the instruction packing and scheduling design are executed simultaneously, the assembler packs instructions while detects collisions among the instructions and eliminates the instruction collisions according to an executing sequence of an instruction scheduling adjusting instruction, and the instruction packing and scheduling design include steps of program segmentation, intra-segment instruction packing and scheduling, intersegment instrument collision detecting and adjusting, skip instruction label matching, skip instruction collision detecting and adjusting and skip instruction label rematching. By the assembler designing method based on the instruction set processor special for the very long instruction words, instruction-level parallelism of the assembler is improved, and application fields of the application specific instruction set process based on the very long instruction words are greatly expanded.

Owner:XIDIAN UNIV

Computation spreading utilizing dithering for spur reduction in a digital phase lock loop

ActiveUS8134411B2Easy to reconfigureReduce generationPulse automatic controlGenerator stabilizationFrequency spectrumClock rate

Owner:TEXAS INSTR INC

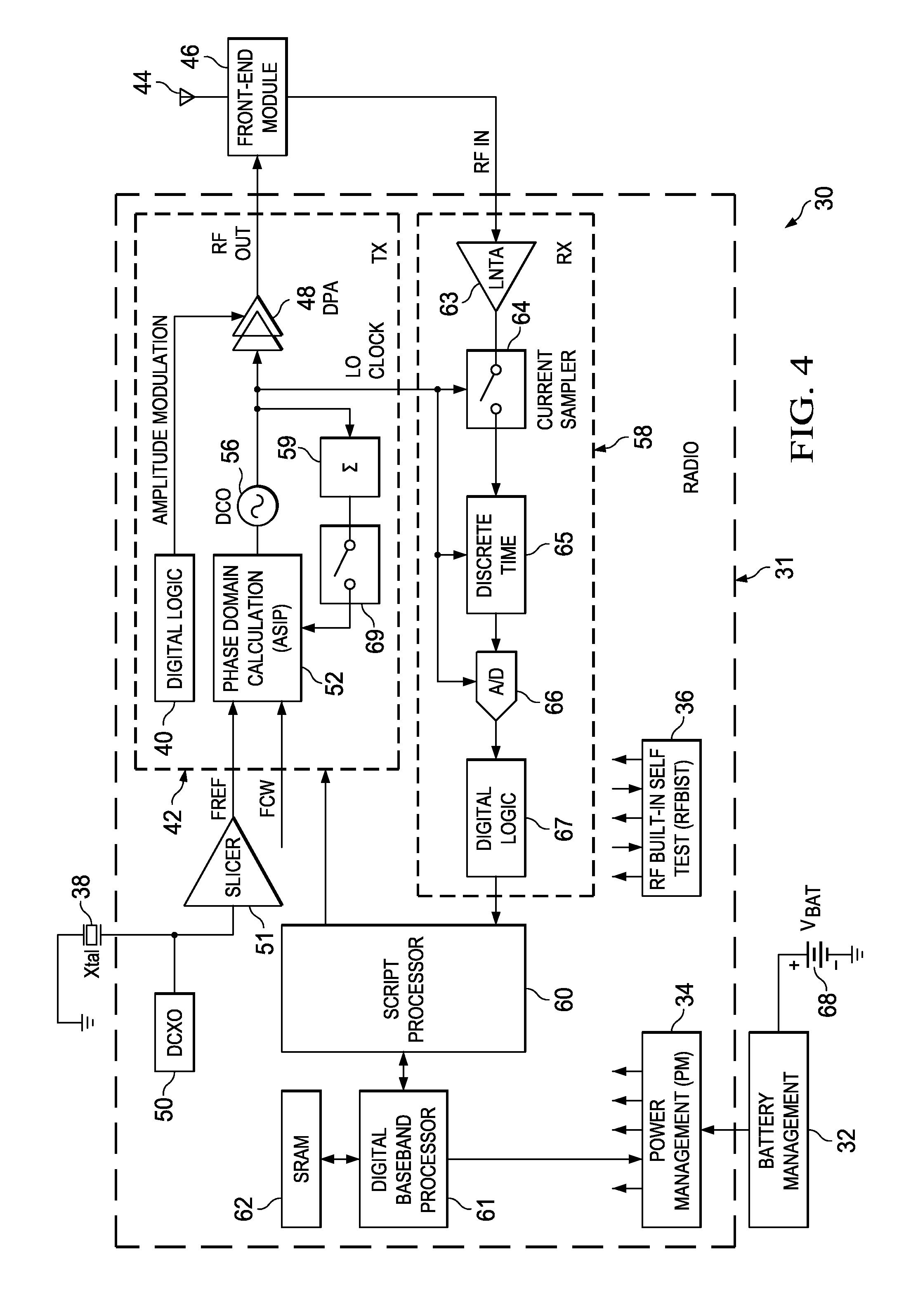

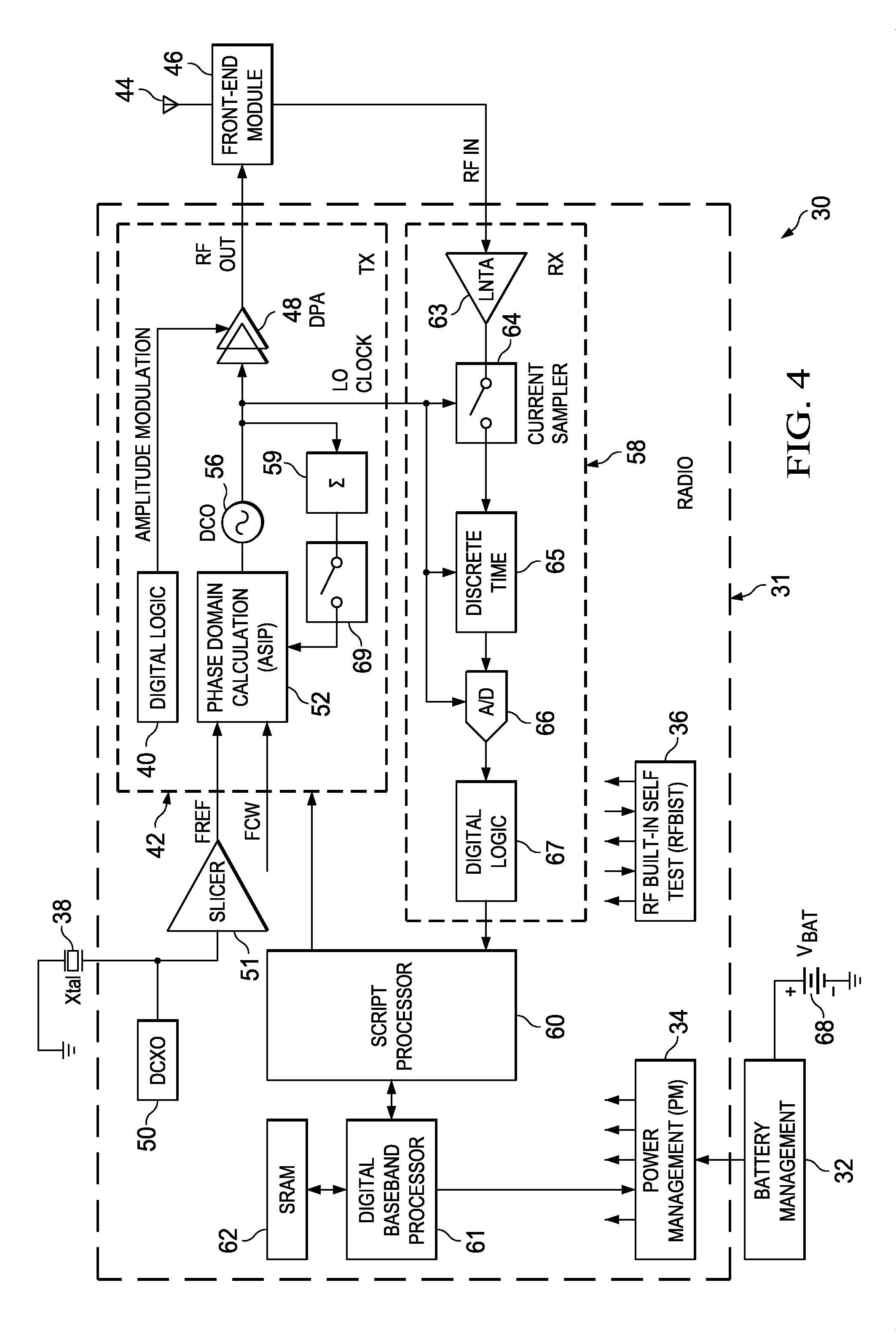

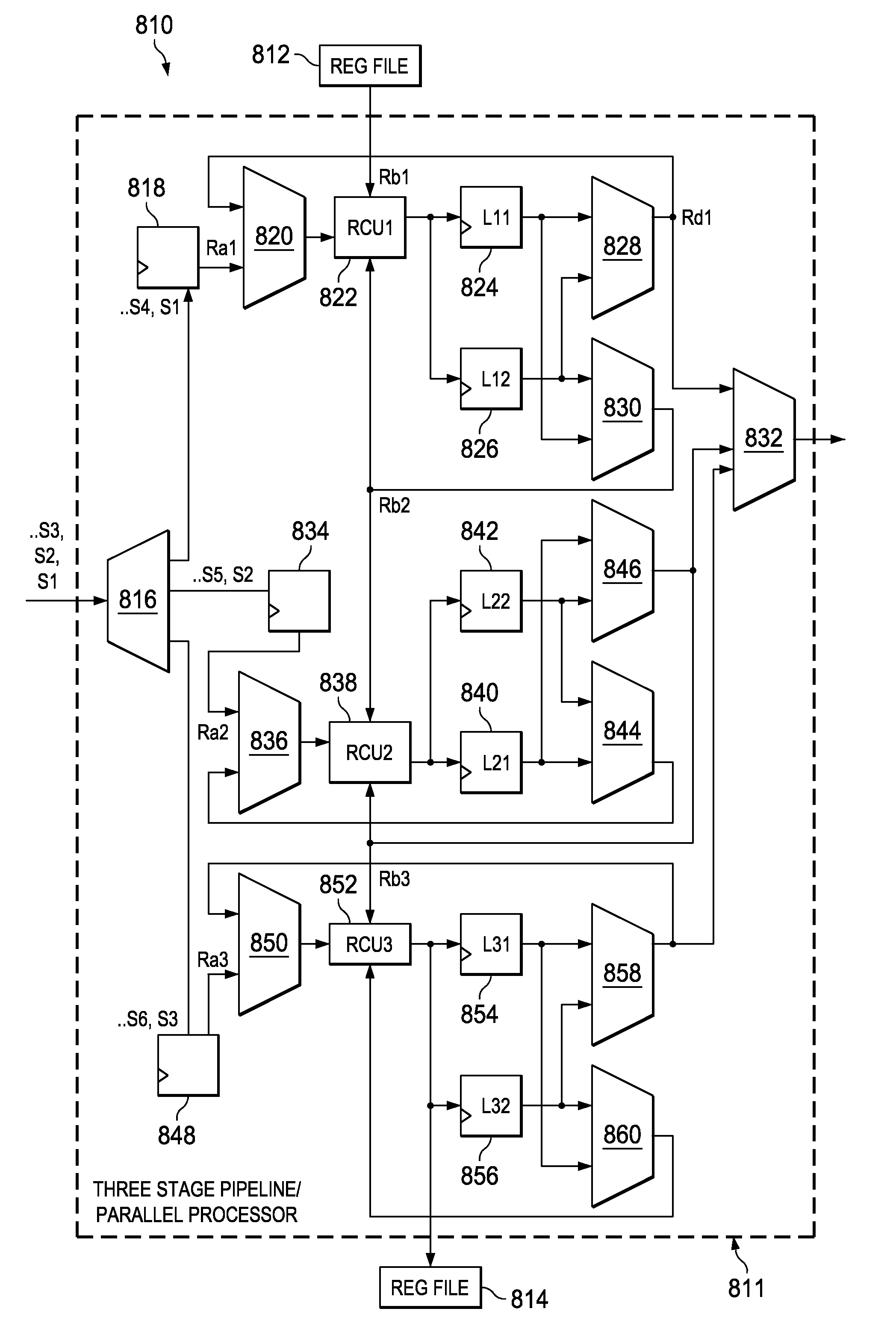

Computation parallelization in software reconfigurable all digital phase lock loop

ActiveUS7809927B2Easy to reconfigureLow spuriousPulse automatic controlGeneral purpose stored program computerData stream processingTime-sharing

A novel and useful apparatus for and method of software based phase locked loop (PLL). The software based PLL incorporates a reconfigurable calculation unit (RCU) that is optimized and programmed to sequentially perform all the atomic operations of a PLL or any other desired task in a time sharing manner. An application specific instruction-set processor (ASIP) incorporating the RCU includes an instruction set whose instructions are optimized to perform the atomic operations of a PLL. A multi-stage data stream based processor incorporates a parallel / pipelined architecture optimized to perform data stream processing efficiently. The multi-stage parallel / pipelined processor provides significantly higher processing speeds by combining multiple RCUs wherein input data samples are input in parallel to all RCUs while computation results from one RCU are used by adjacent downstream RCUs. A register file provides storage for historical values while local storage in each RCU provides storage for temporary results.

Owner:TEXAS INSTR INC

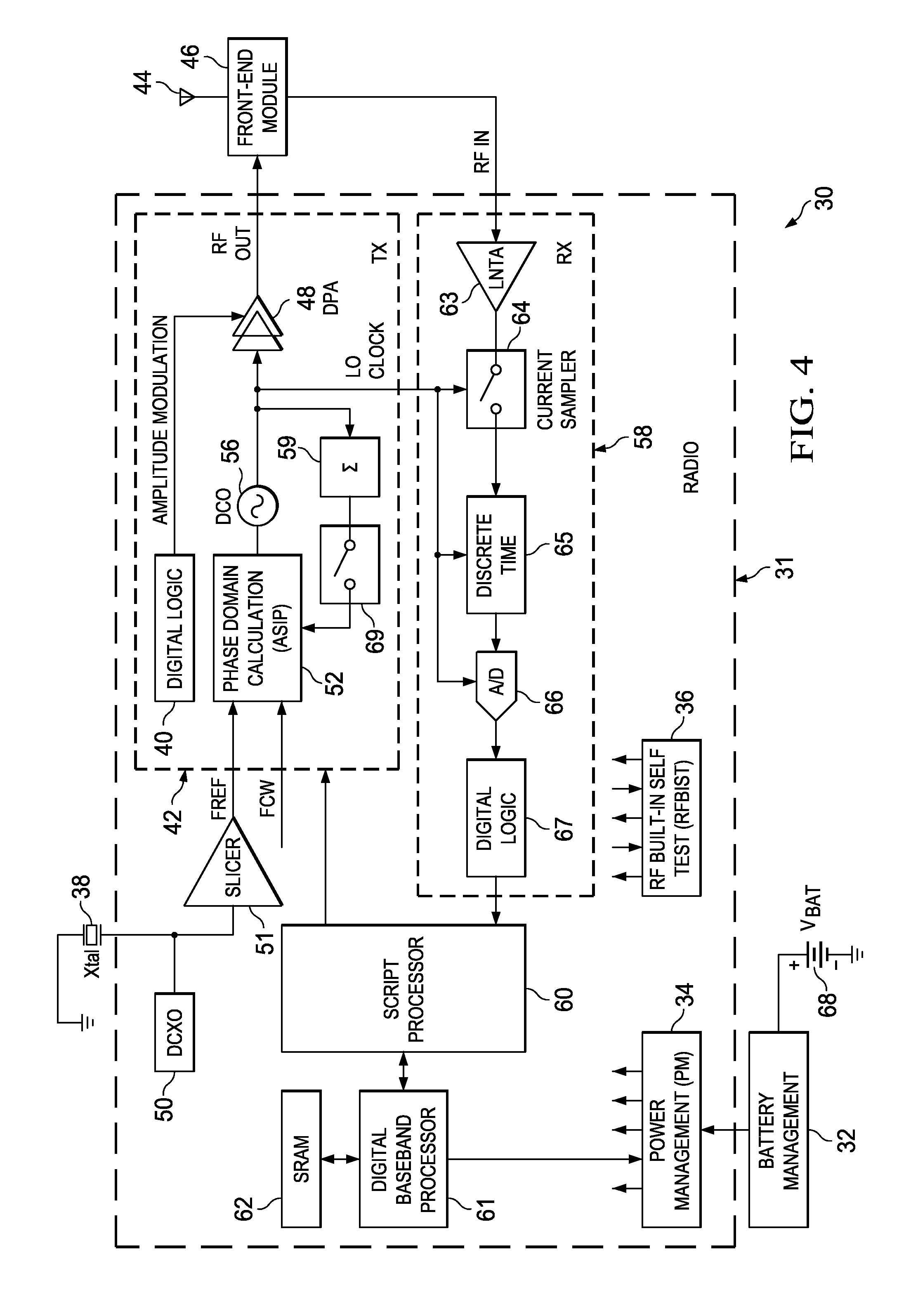

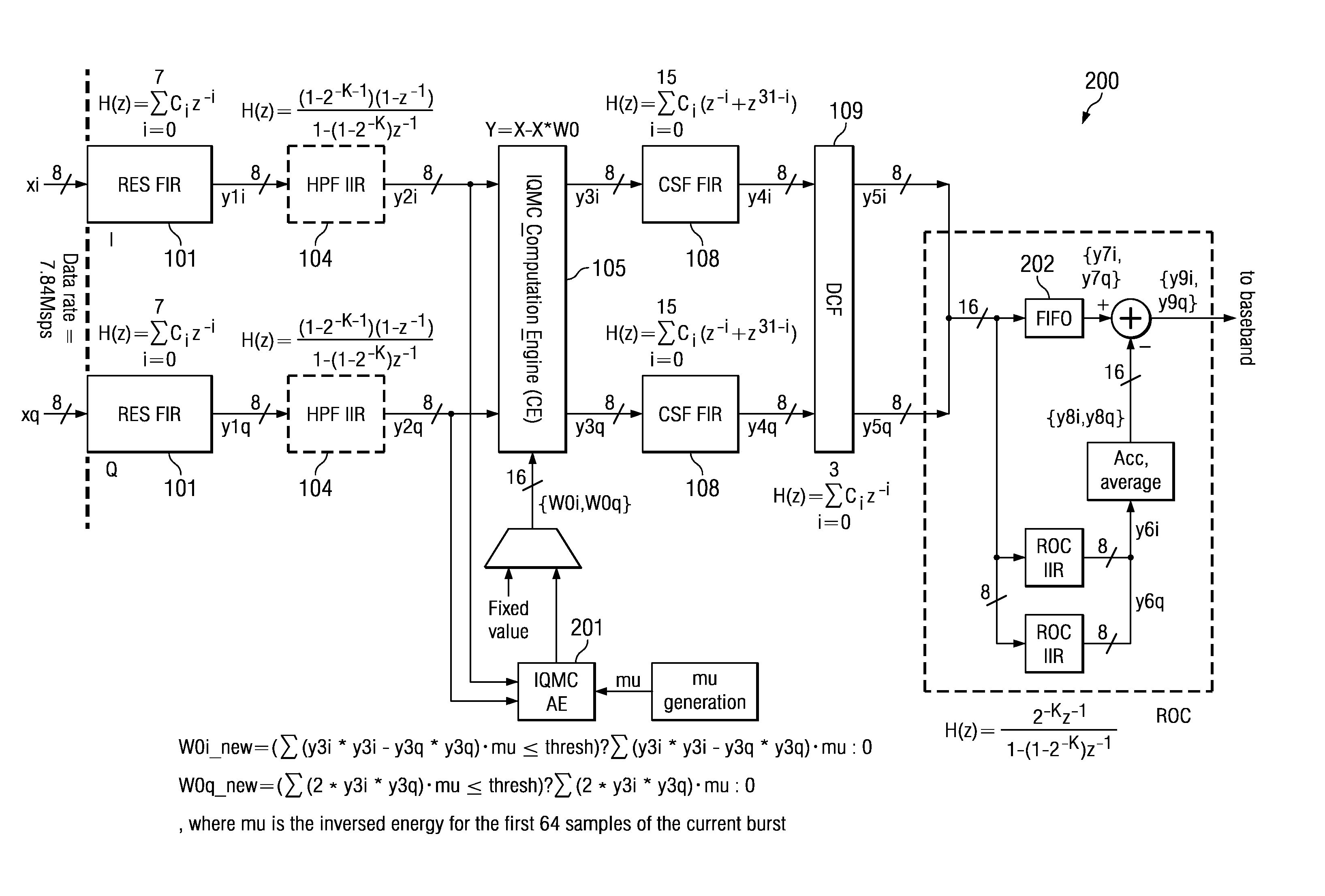

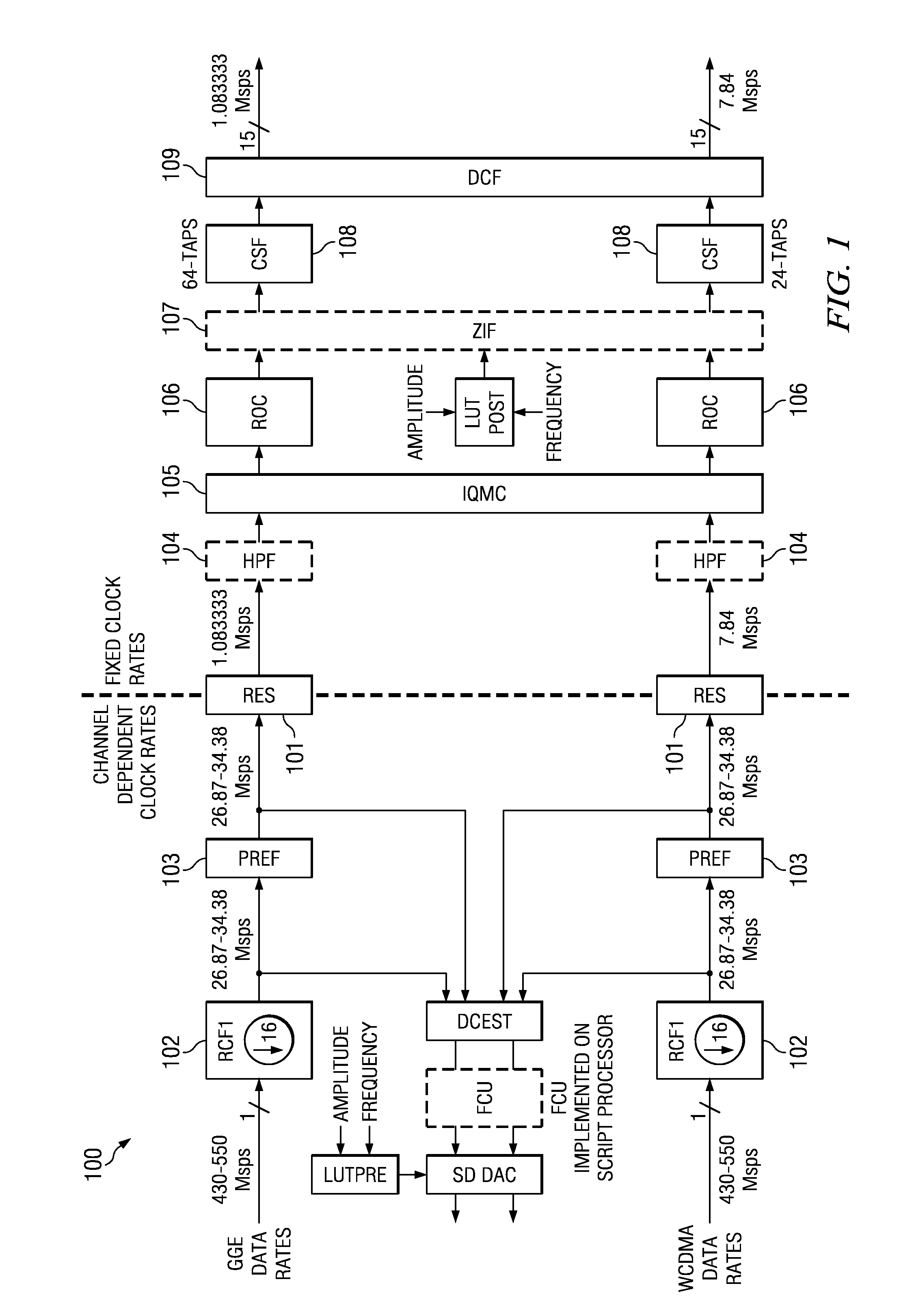

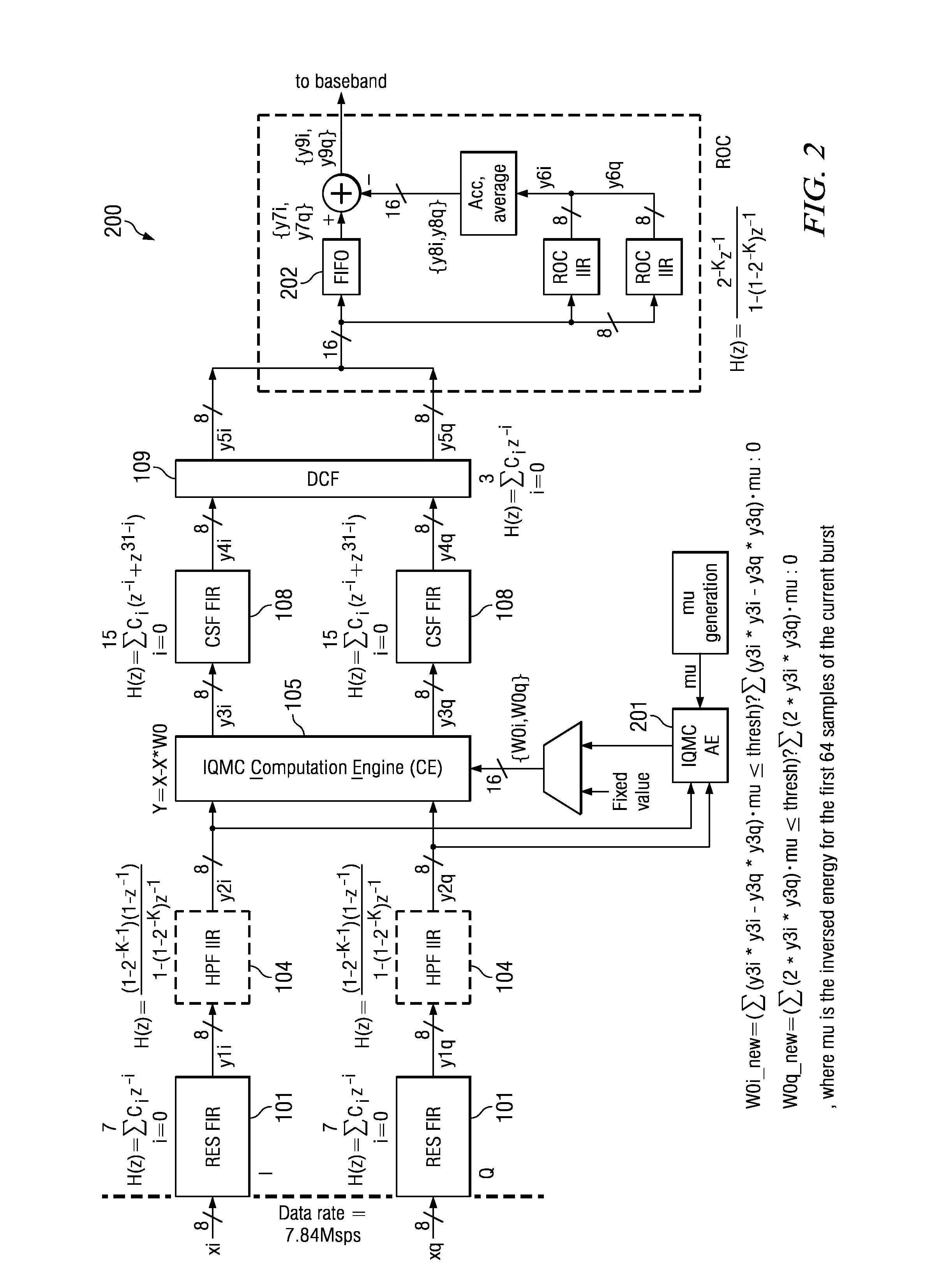

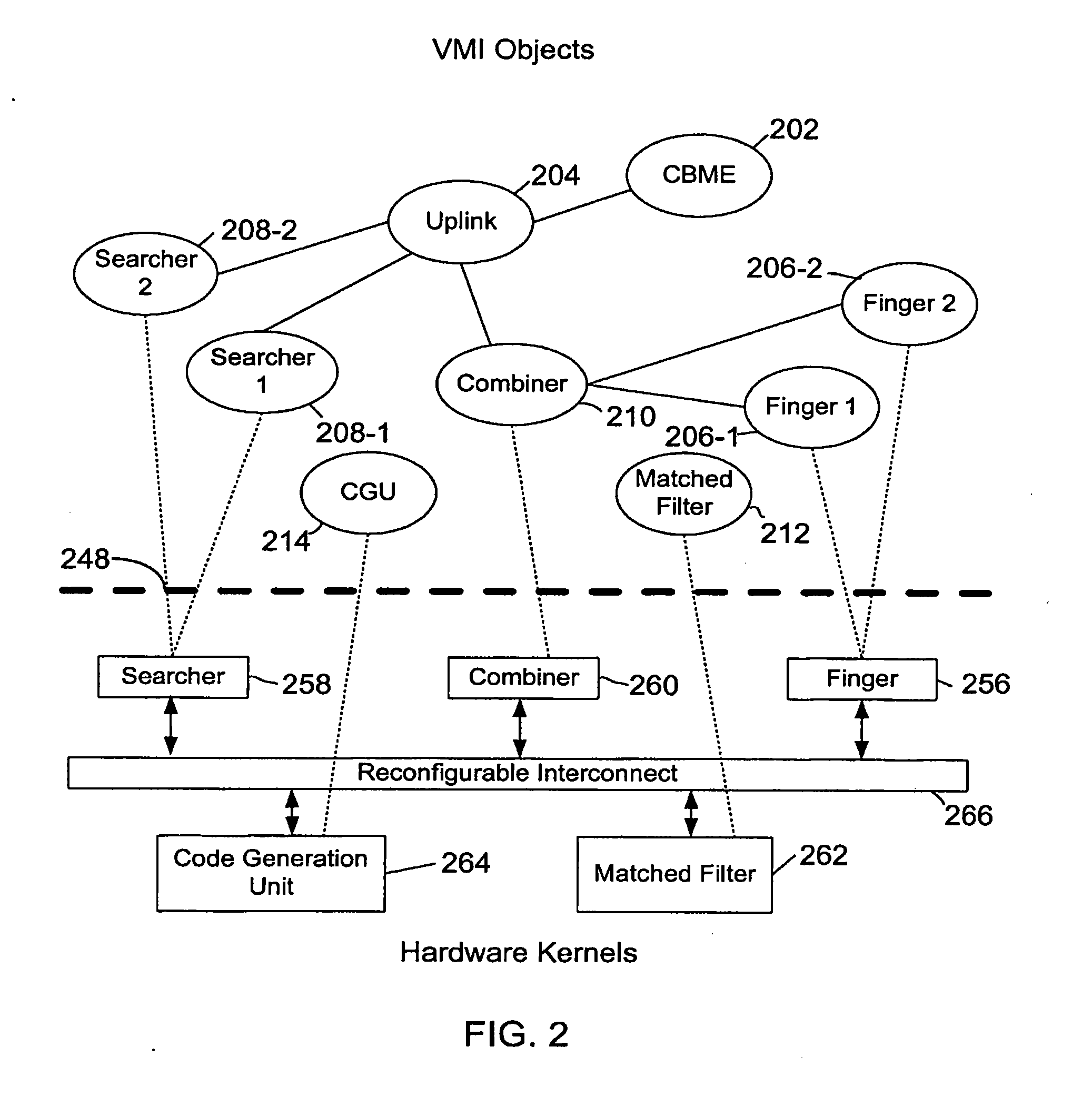

Application specific instruction set processor for digital radio processor receiving chain signal processing

ActiveUS8065506B2Increase chanceImprove customizationGeneral purpose stored program computerSpecial data processing applicationsComputer architectureDatapath

Owner:TEXAS INSTR INC

Computation spreading for spur reduction in a digital phase lock loop

ActiveUS7936221B2Easy to reconfigureReduce generationPulse automatic controlDigital computer detailsClock rateTime-sharing

A novel and useful apparatus for and method of spur reduction using computation spreading in a digital phase locked loop (DPLL) architecture. A software based PLL incorporates a reconfigurable calculation unit (RCU) that is optimized and programmed to sequentially perform all the atomic operations of a PLL or any other desired task in a time sharing manner. An application specific instruction-set processor (ASIP) incorporating the RCU is adapted to spread the computation of the atomic operations out over and completed within an entire PLL reference clock period. Each computation being performed at a much higher processor clock frequency than the PLL reference clock rate. This functions to significantly reduce the per cycle current transient generated by the computations. Further, the frequency content of the current transients is at the higher processor clock frequency. This results in a significant reduction in spurs within sensitive portions of the output spectrum.

Owner:TEXAS INSTR INC

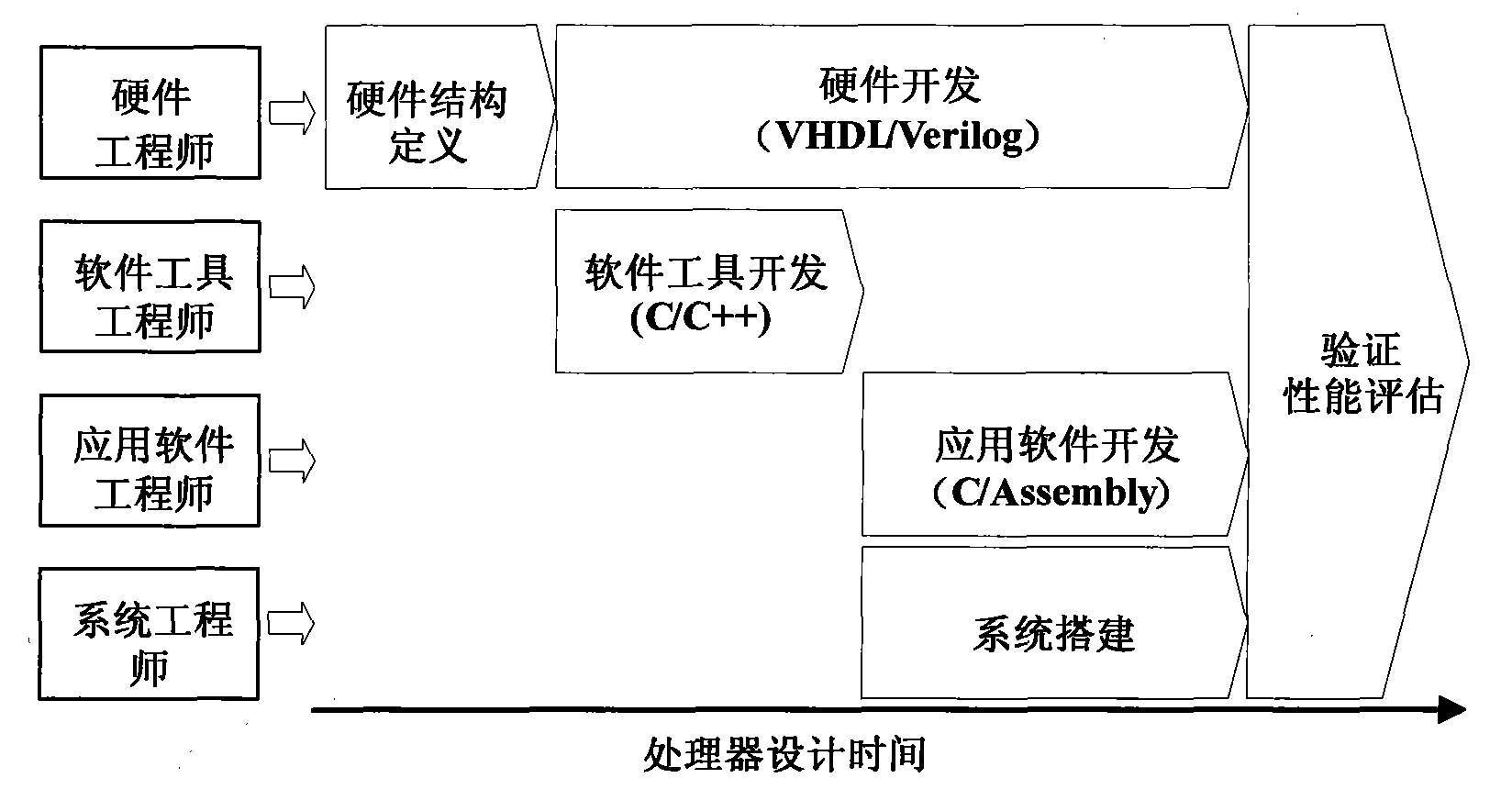

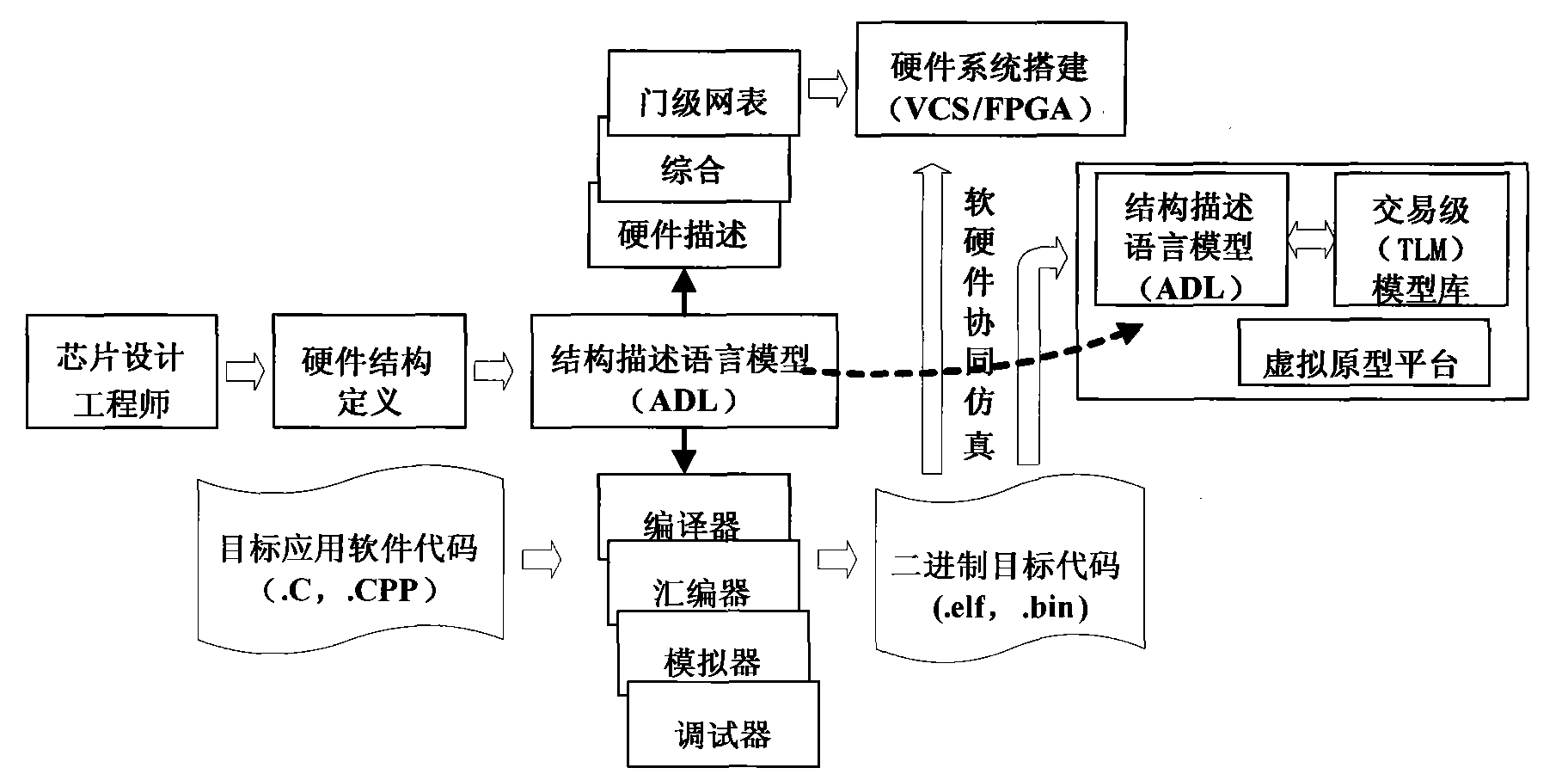

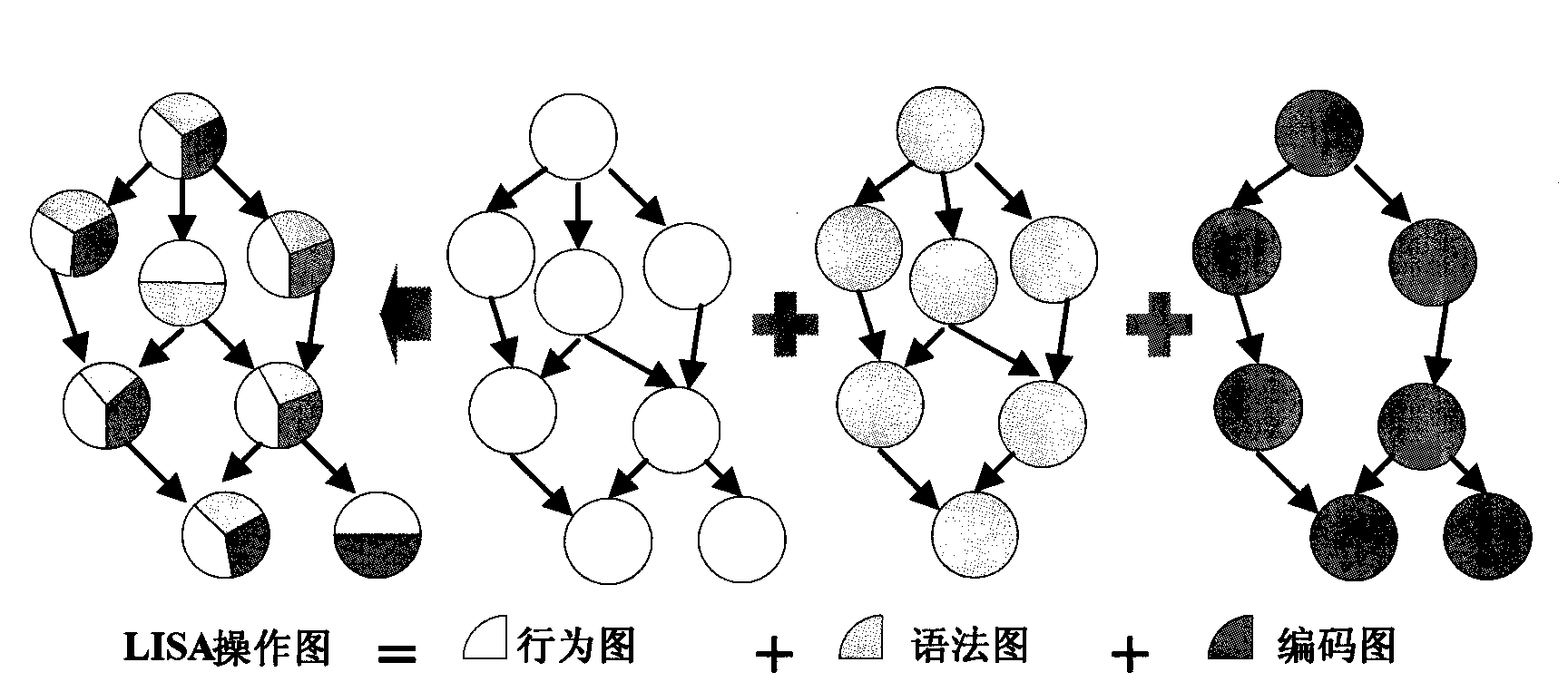

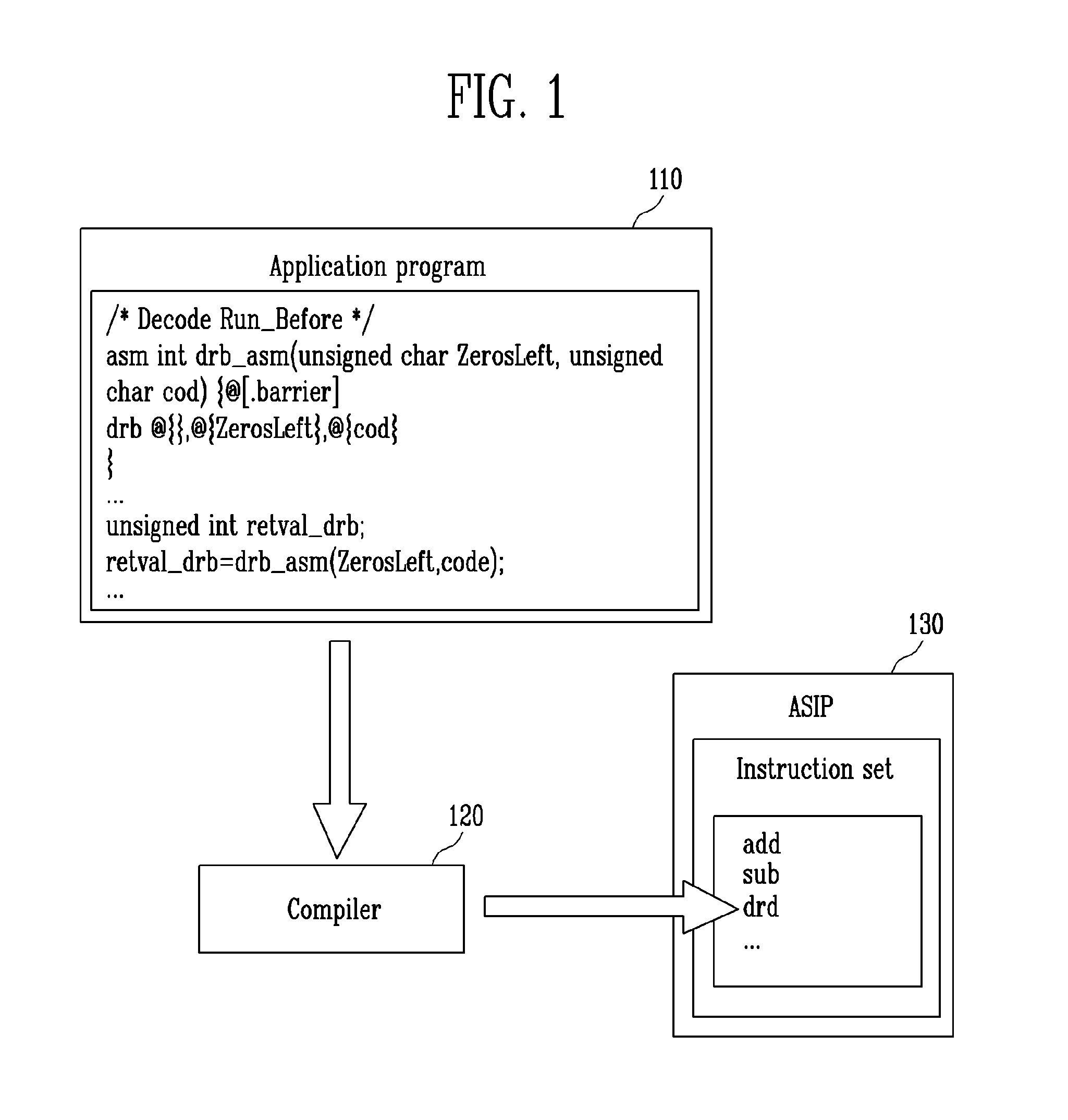

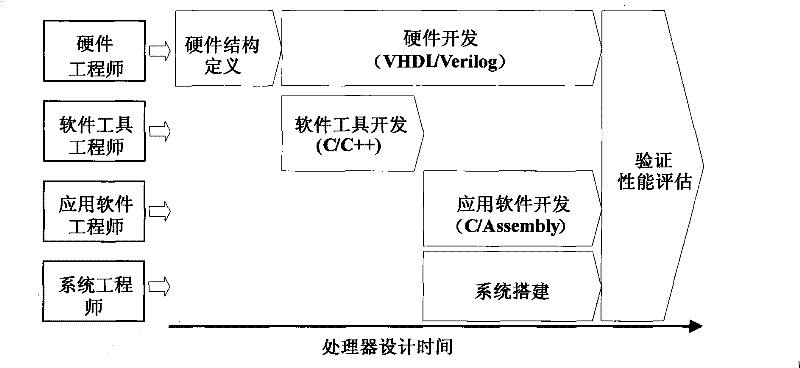

Method for designing specific instruction set processor

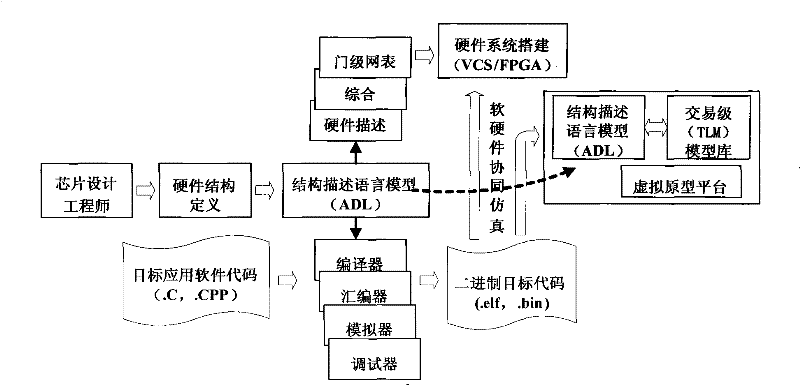

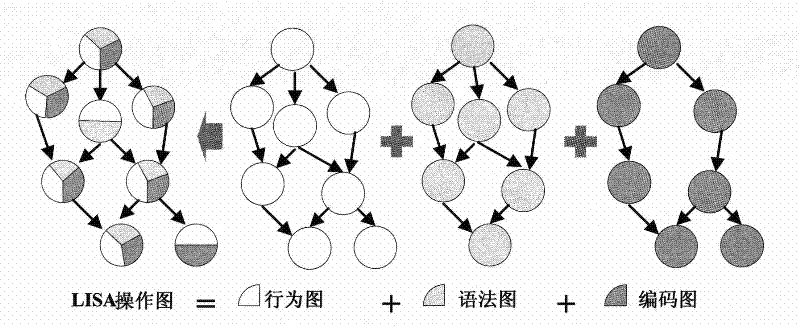

ActiveCN101561833AAccelerate Design CycleImprove performanceSpecial data processing applicationsProcessor modelComputer architecture

The invention relates to a method for designing a specific instruction set processor, and the method can make the accuracy performance evaluation at the beginning of designing a chip, advance the test of a specific application, speed up the design process and reduce the re-design possibility which is because the performances of the chip can not achieve the requirements. The method establishes an LISA processor model at the early stage of the design, generates a corresponding software tool by the LISA model, builds up a virtual prototyping platform which is similar to the performances of real hardware on an ARM ESL, including a AHB bus model with precise cycle, an EMI model and an SDRAM model which are needed for designing the platform, searches out the performances under the different situations by repairing the models of the processor, obtains an optical software / hardware dividing method, directly verifies on the models and speeds up the design cycle of the processor.

Owner:SOUTHEAST UNIV

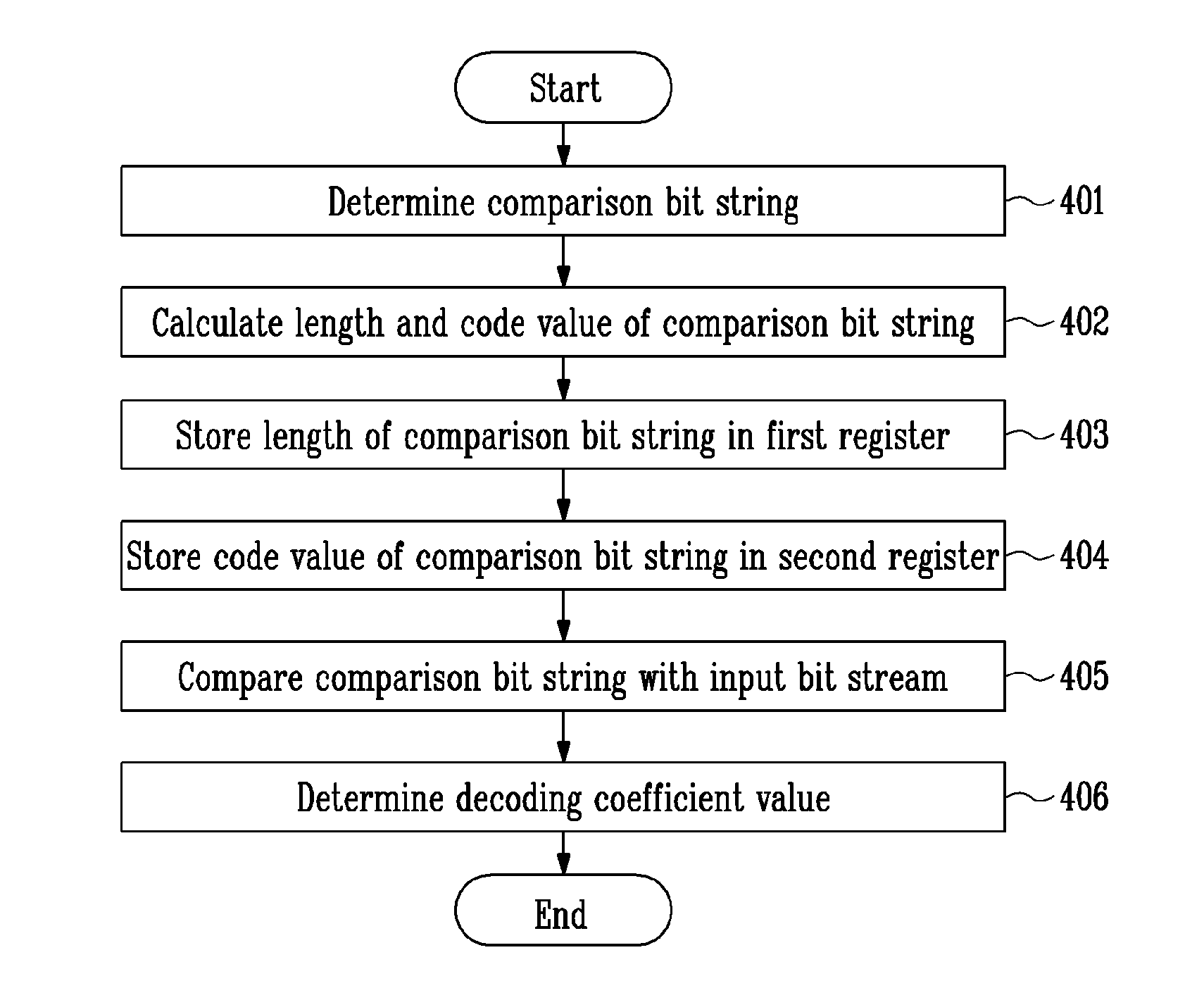

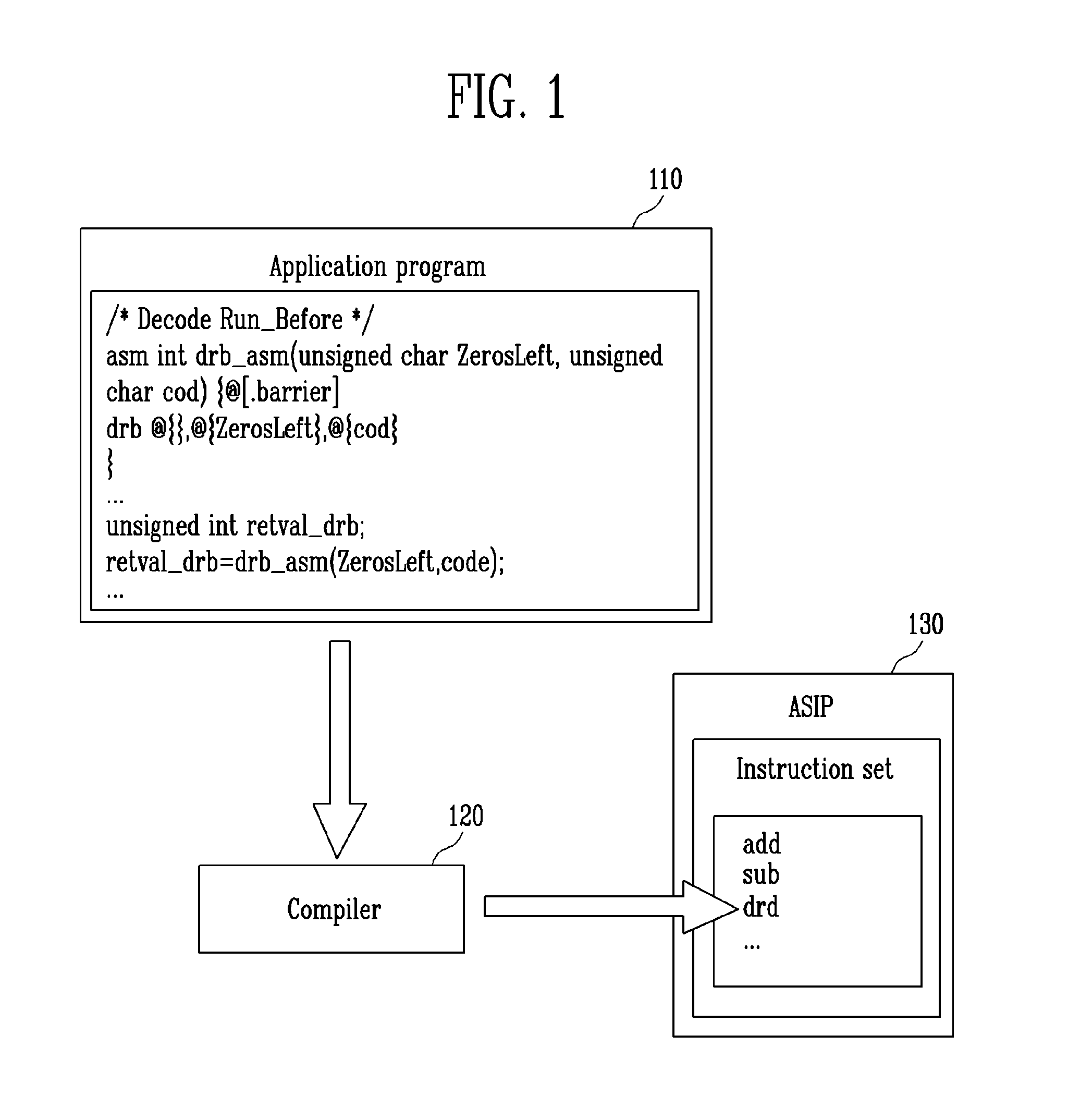

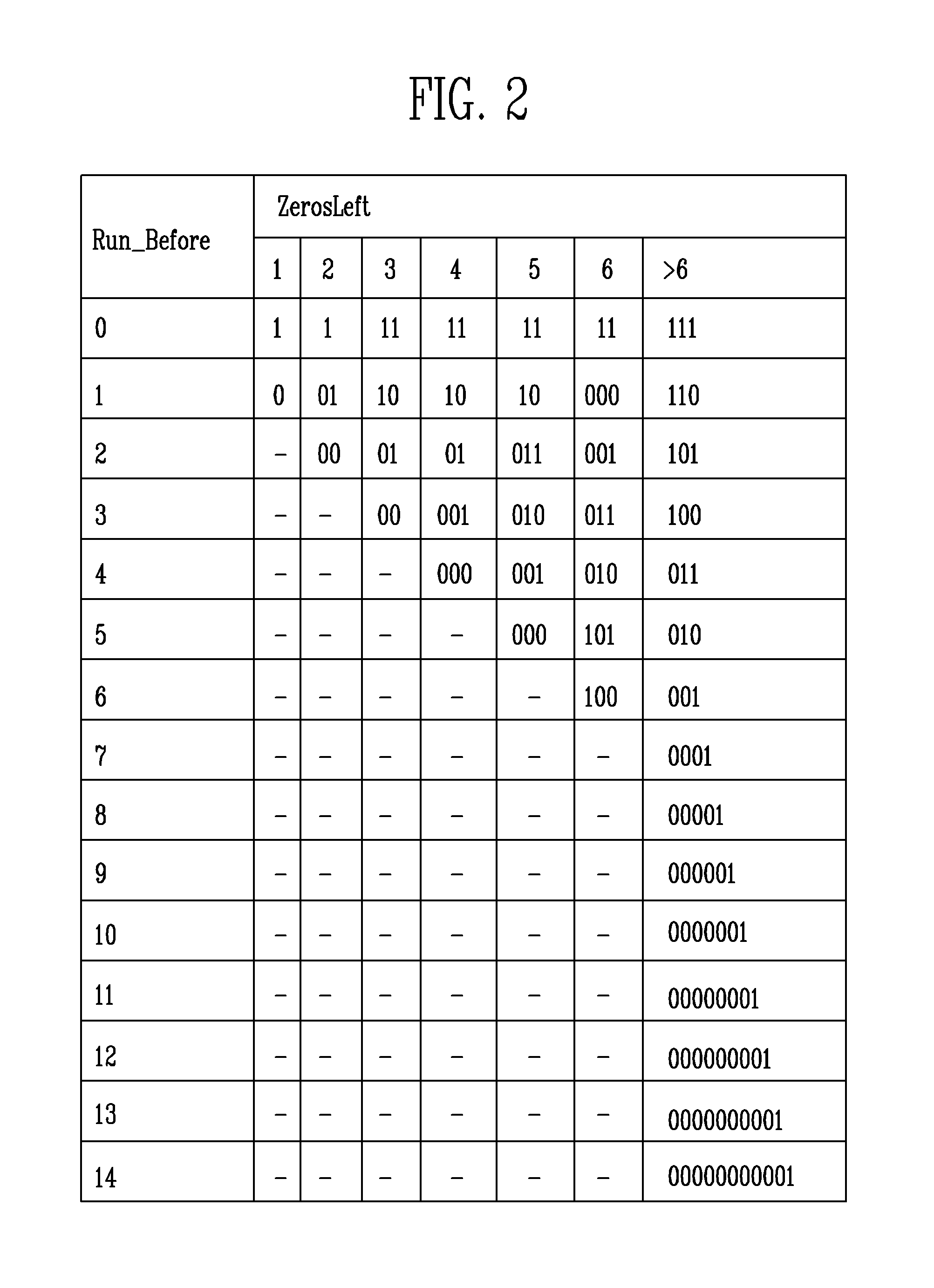

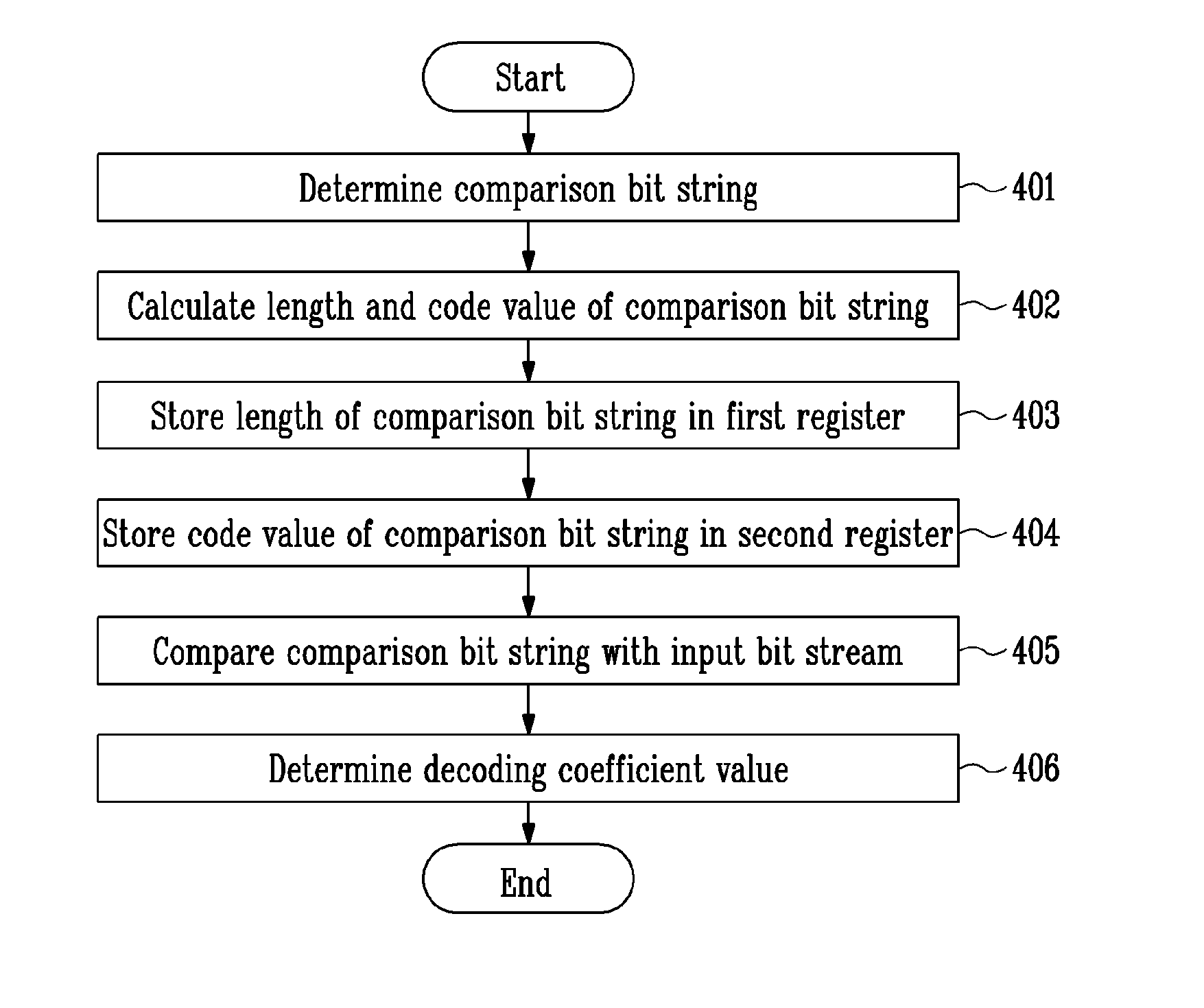

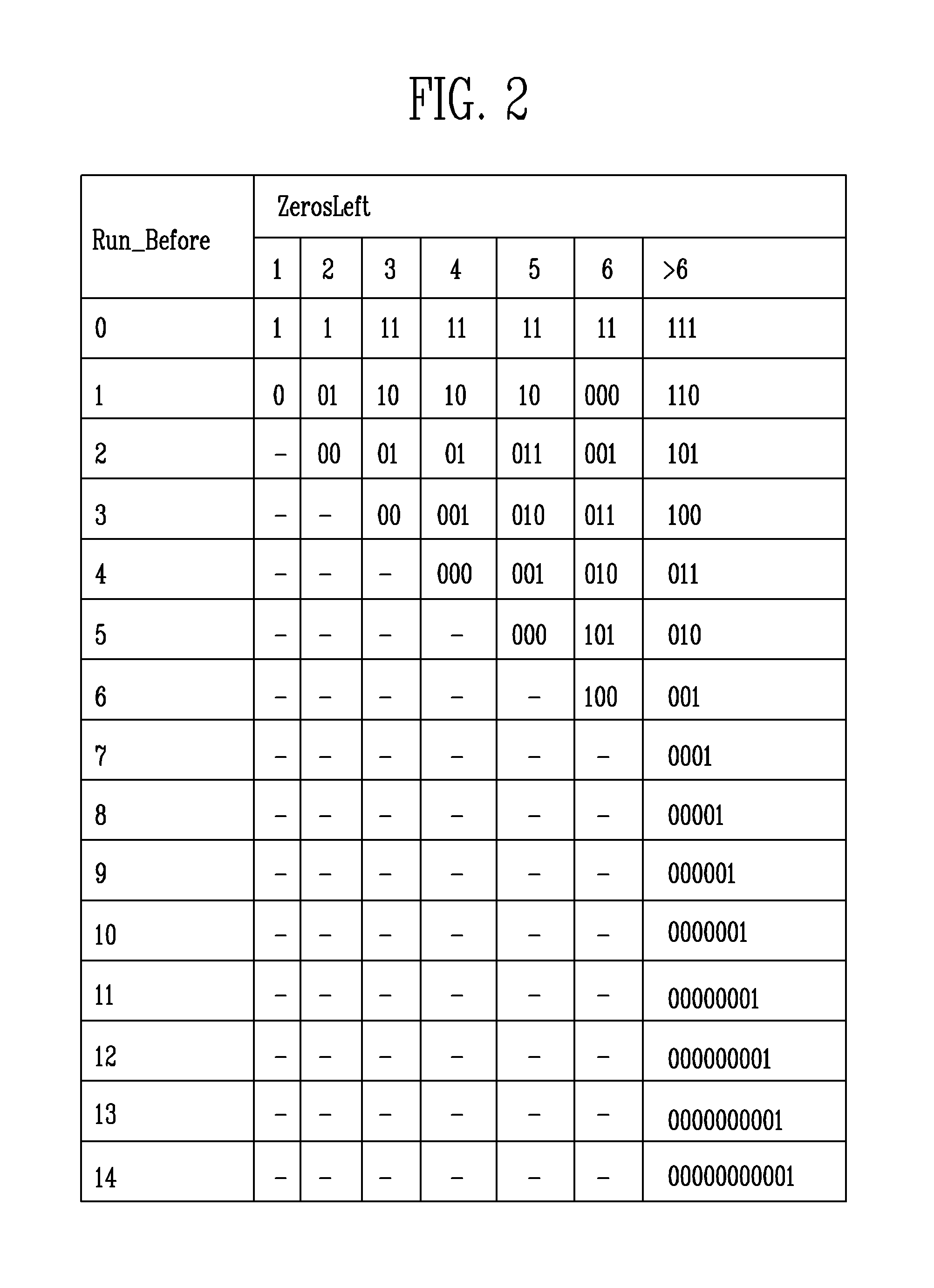

H.264 CAVLC decoding method based on application-specific instruction-set processor

Provided is an H.264 Context Adaptive Variable Length Coding (CAVLC) decoding method based on an Application-Specific Instruction-set Processor (ASIP). The H.264 CAVLC decoding method includes determining a plurality of comparison bit strings on the basis of a table of a decoding coefficient, storing lengths of the comparison bit strings in a first register, storing code values of the comparison bit strings in a second register, comparing an input bit stream with the comparison bit strings based on the lengths and code values of the comparison bit strings, and determining value of the decoding coefficient according to a result of comparison between the input bit stream and the comparison bit strings. The method extracts a decoding coefficient using a register in an ASIP without accessing a memory and prevents a reduction in speed caused by memory access, thereby increasing the decoding speed of an H.264 decoder.

Owner:ELECTRONICS & TELECOMM RES INST

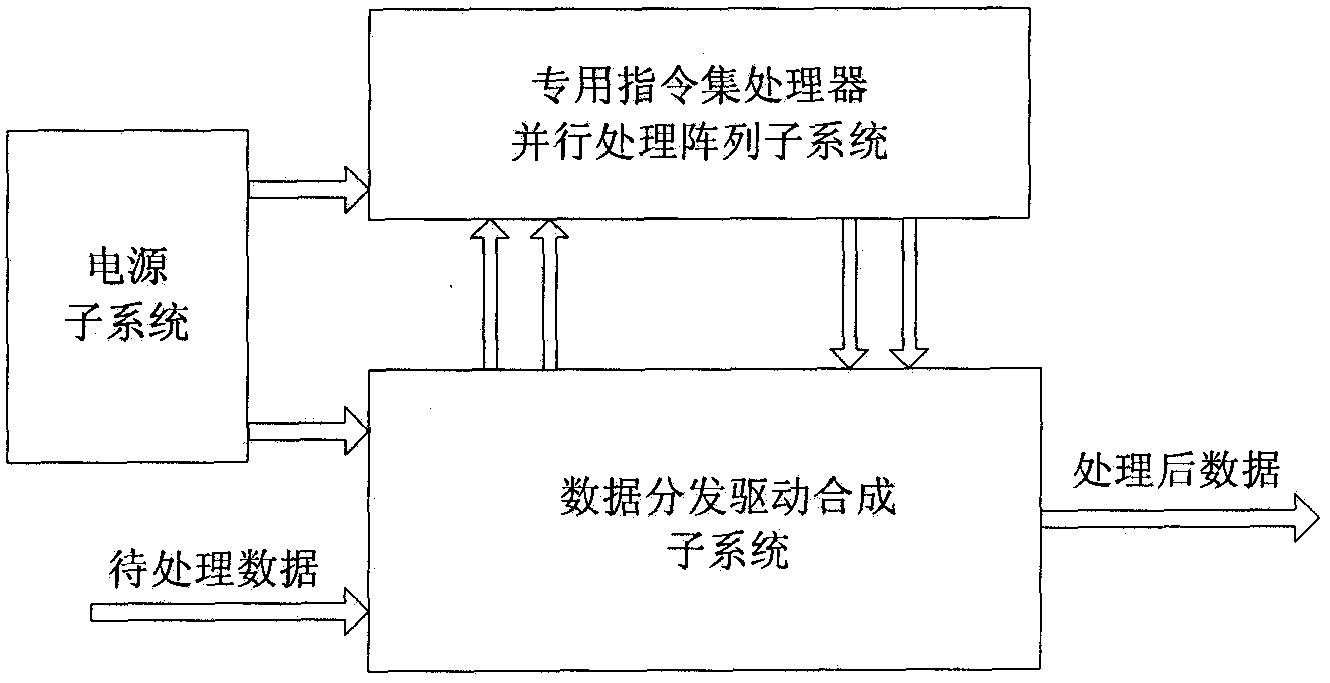

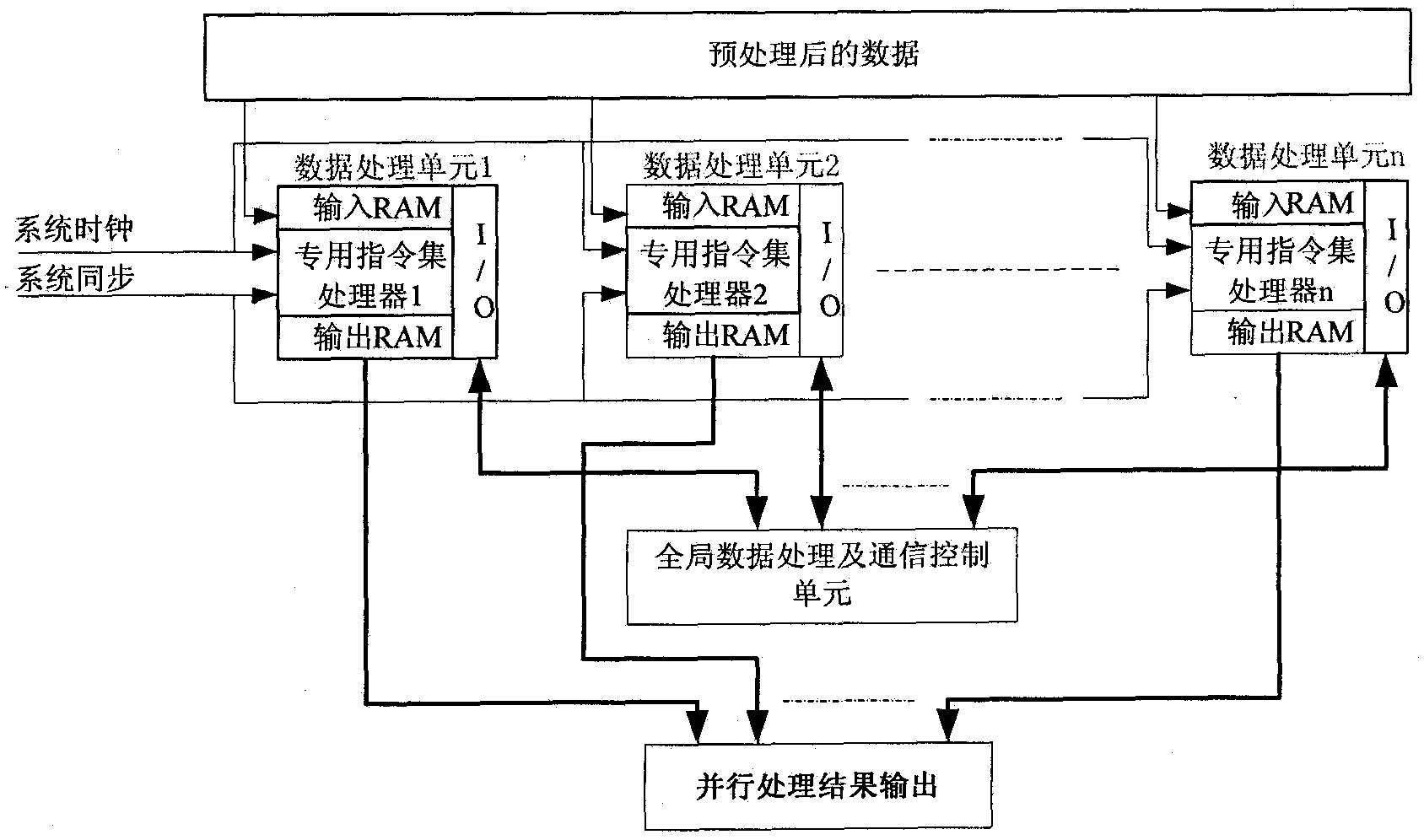

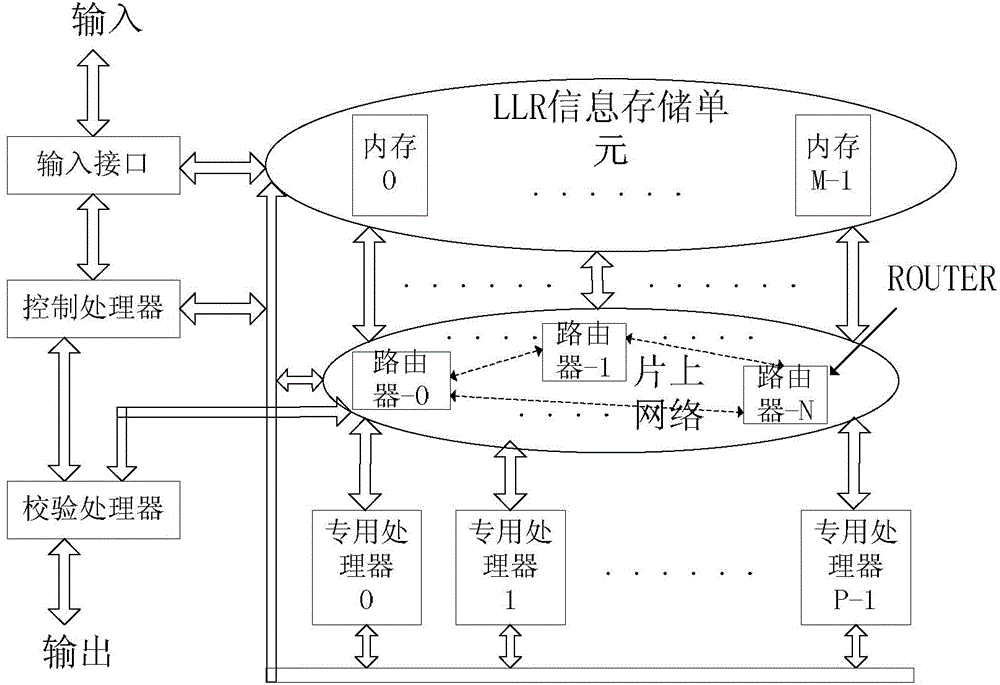

Spaceborne real-time parallel data processing system

InactiveCN106134476BReduce volumeProcessing speedSpecial data processing applicationsData processing systemOn board

The invention provides a space-borne real-time parallel data processing system aiming at the characteristics of huge data volume and high real-time processing requirements of the space-borne system. The system mainly consists of a power supply subsystem, a dedicated instruction set processor parallel processing array subsystem, and a data distribution-driven synthesis subsystem to form a three-layer processing platform structure. The data distribution-driven synthesis subsystem is used to complete the preprocessing and processing of input data The result output is located in the middle layer of the entire processing platform; the special-purpose instruction set processor parallel processing array subsystem is located on the top layer of the entire processing platform, and the special-purpose instruction set processor is used to form a parallel processing array to complete the processing of input data; the power supply subsystem The system provides power for the entire system and is located at the bottom of the entire processing platform; the three subsystems are connected through a dedicated bus layer. The invention has the advantage of being able to realize real-time parallel fast processing of massive data on the satellite, and can be used for denoising and compressing distributed images on the satellite.

Owner:XIDIAN UNIV

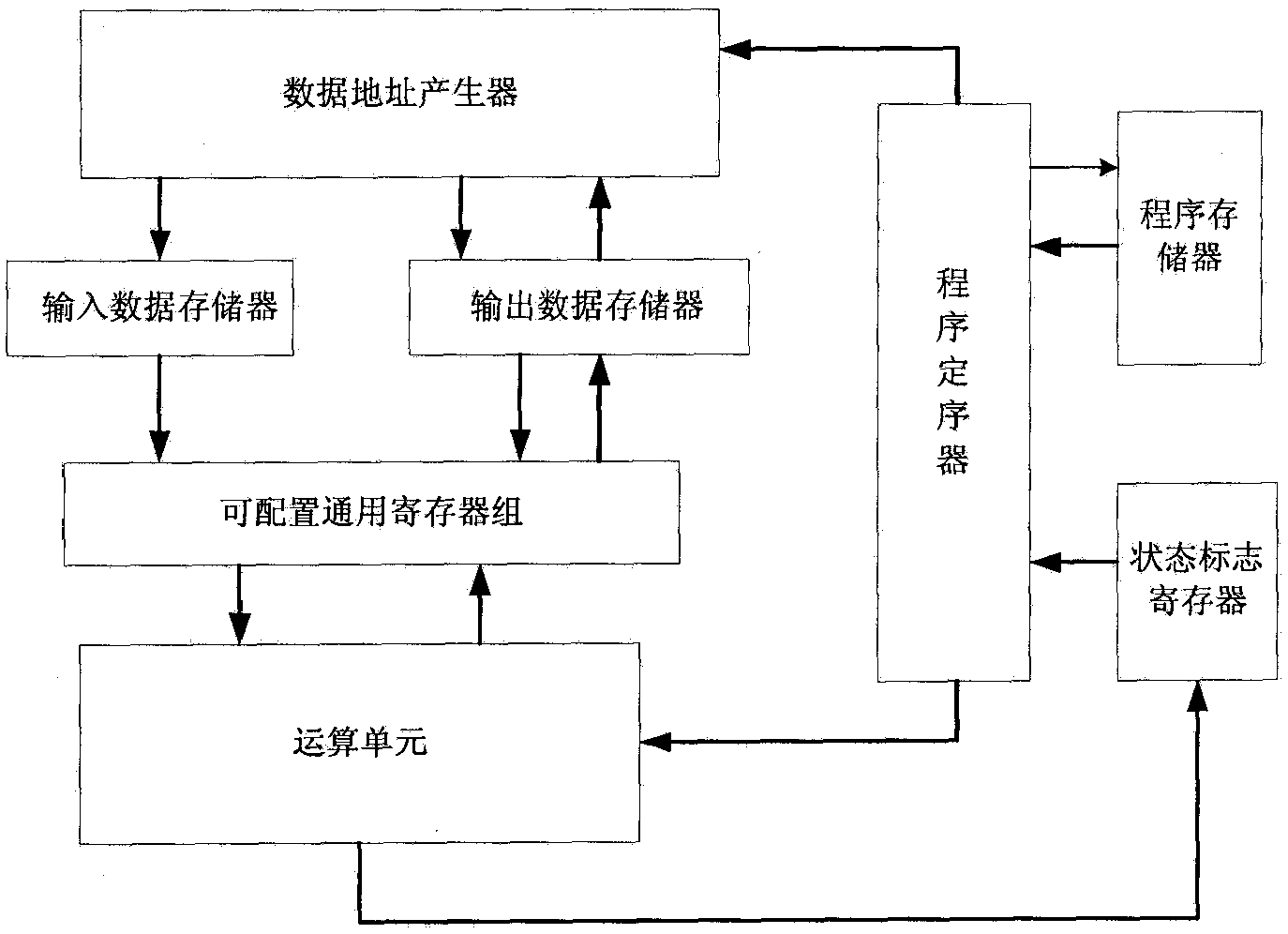

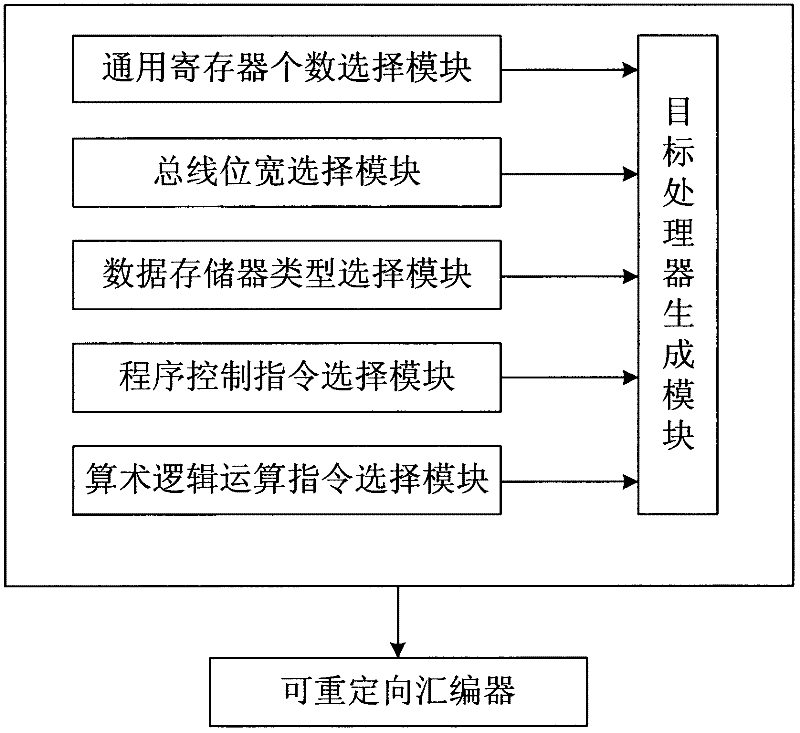

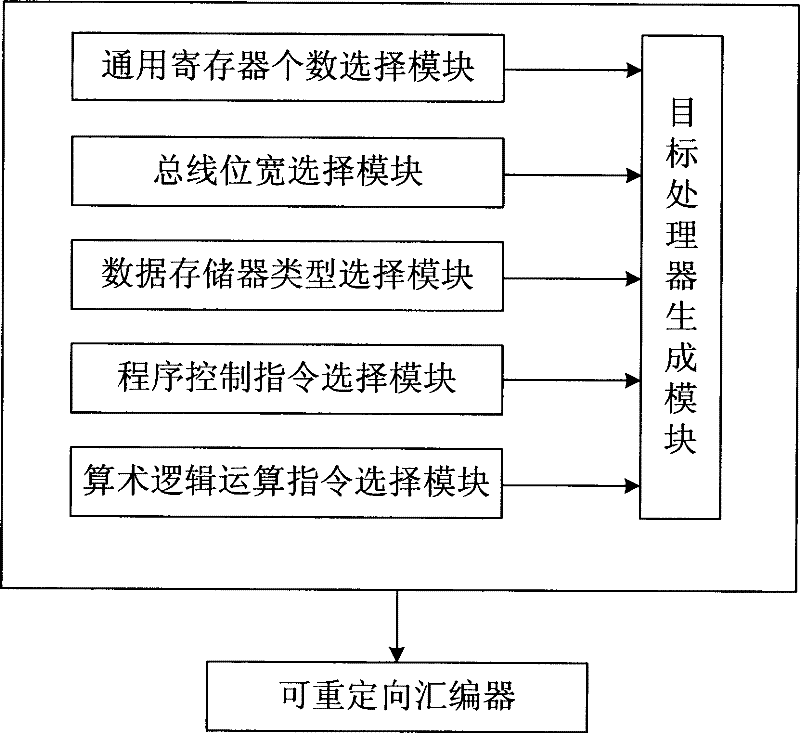

Parameterized specific instruction set processor design platform

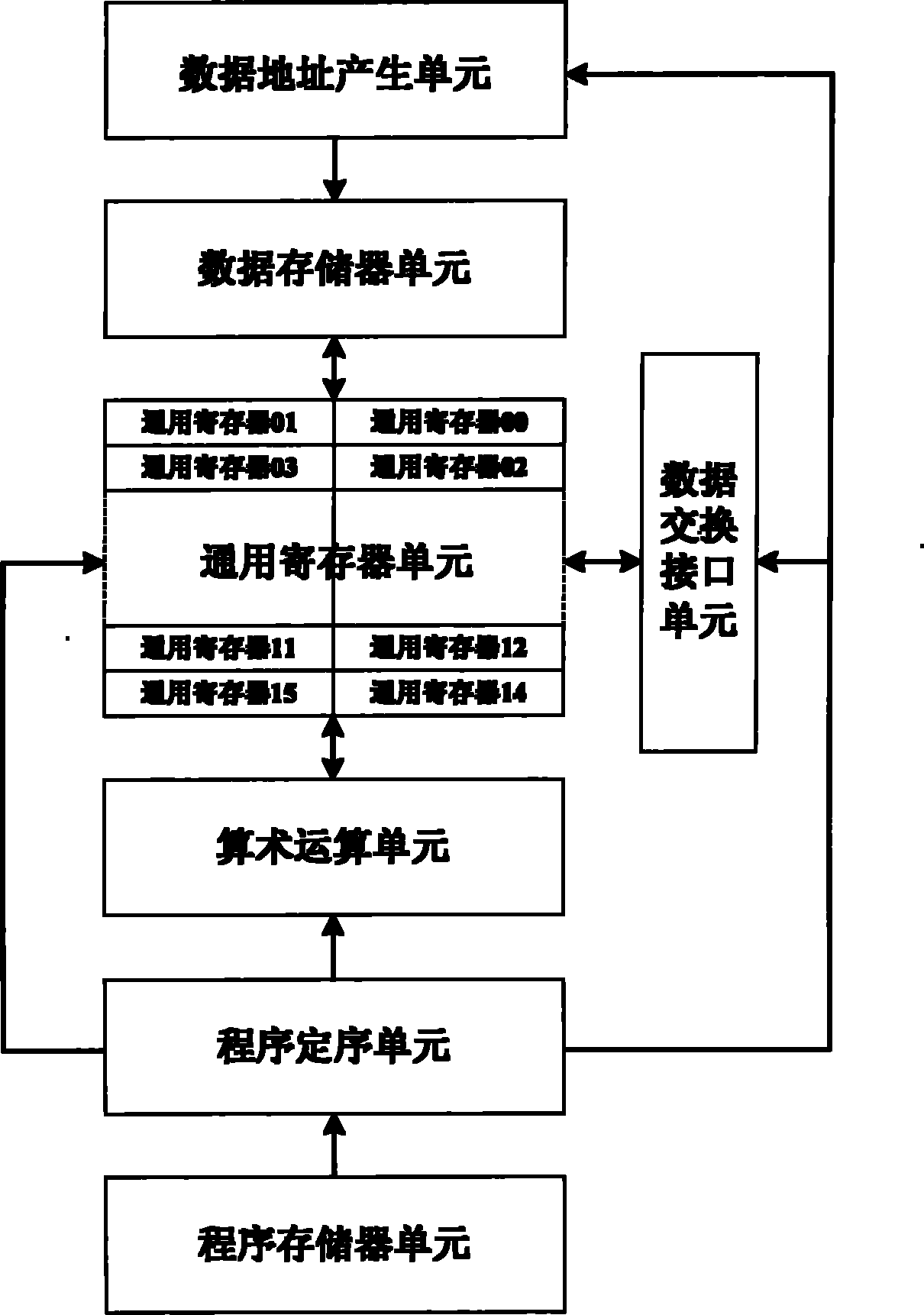

InactiveCN102446086AProcessing speedImprove utilization efficiencyMemory systemsMachine execution arrangementsLogical operationsComputer module

The invention discloses a parameterized specific instruction set processor design platform comprising a universal register number selection module, a bus bit width selection module, a data memory type selection module, a program control instruction selection module, an arithmetical logical operation instruction selection module, a target processor generation module and a retargetable assembler. The design platform generates the optimal specific instruction set processor core which saves most resources in the structure frame of the specific instruction set processor core according to related parameters selected by a user for different application fields, and also shortens the design period of the specific instruction set processor. The retargetable assembler is capable of positioning the compiler to the target processor according to the parameters selected by the user, and further capable of translating an assembler source program into the machine codes of the target processor; as a result, the work load of a programmer is reduced; therefore, the working efficiency is improved.

Owner:XIDIAN UNIV

Coupling GP processor with reserved instruction interface via coprocessor port with operation data flow to application specific ISA processor with translation pre-decoder

InactiveUS7293159B2Improve efficiencyRuntime instruction translationGeneral purpose stored program computerGeneral purposeInstruction memory

Provides methods, systems and apparatus for coupling a general purpose processor (GPP) to an application specific instruction set processor (ASIP) in such a manner that the GPP can include execute instructions that do not normally comprise part of its instruction set architecture (ISA). The GPP is coupled to the ASIP via a coprocessor port such that instructions issued by the GPP to the port are conveyed to a novel pre-decoder module of the ASIP. The pre-decoder module translates the GPP instruction into operation codes for ASIP instructions to be executed in the ASIP or to an address in the ASIP instruction memory that identifies a start address for a plurality of ASIP instructions defining a complex application specific function. Once the ASIP has executed the instructions it shares the result of the execution with the GPP. In this way, the GPP takes advantage of the ASIP in its ability to more quickly execute an application specific program / procedure.

Owner:IBM CORP

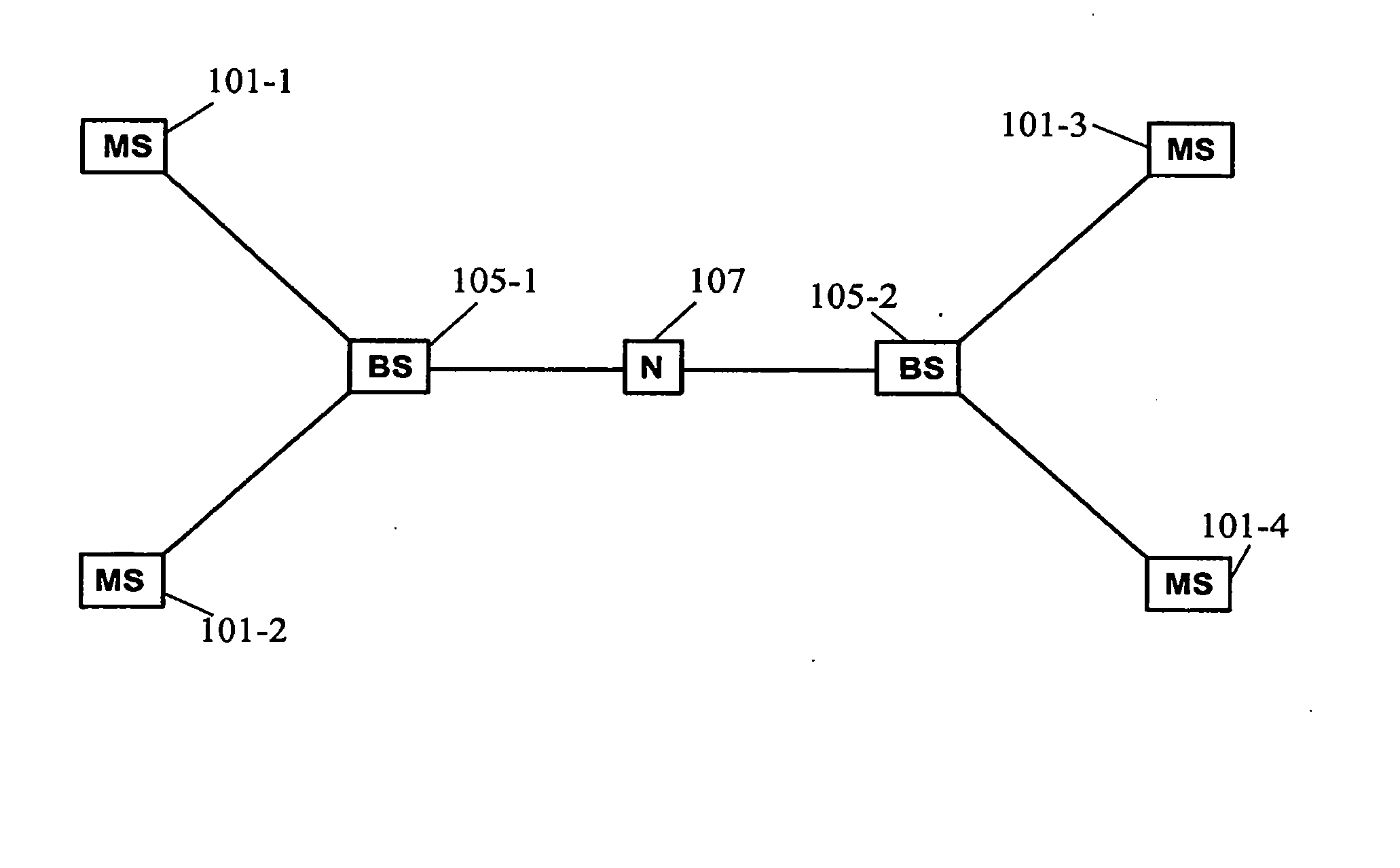

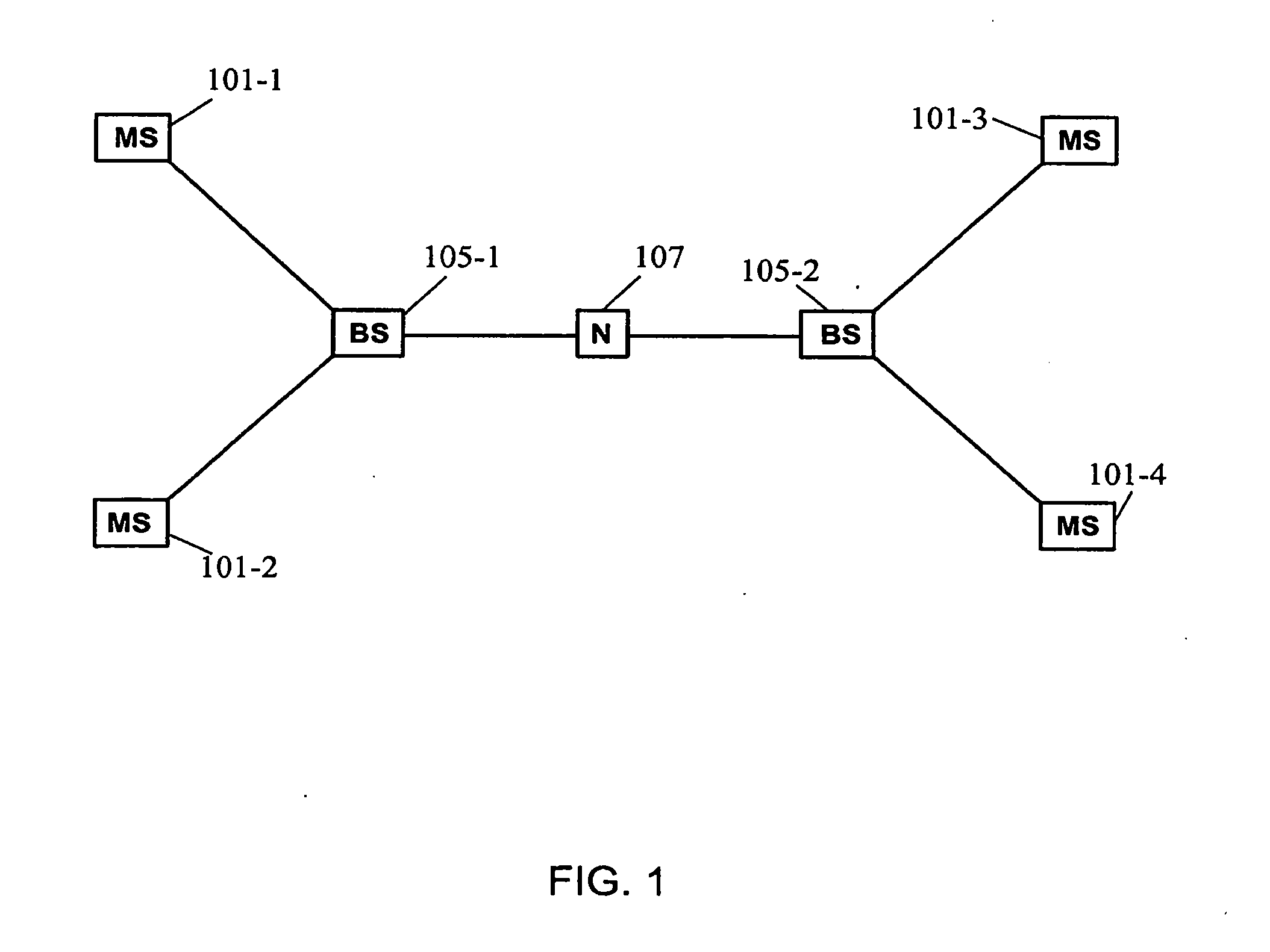

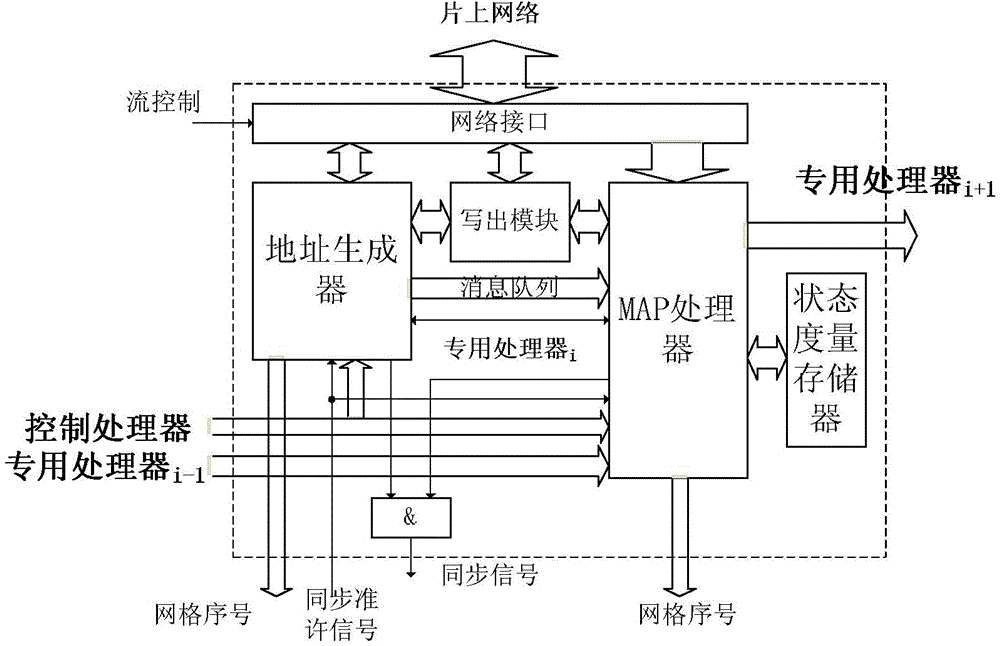

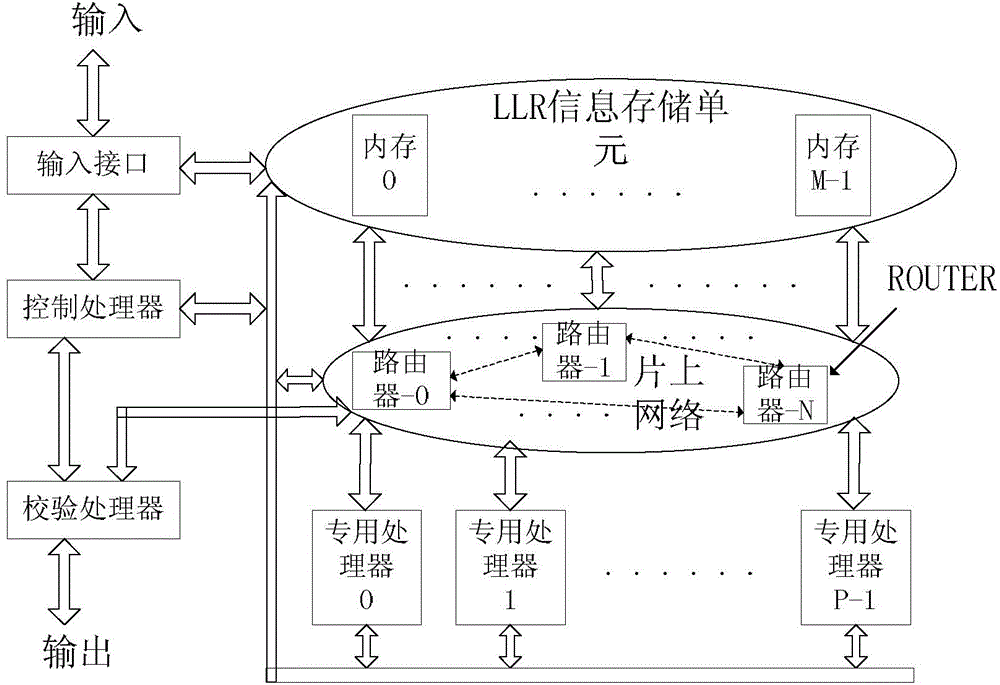

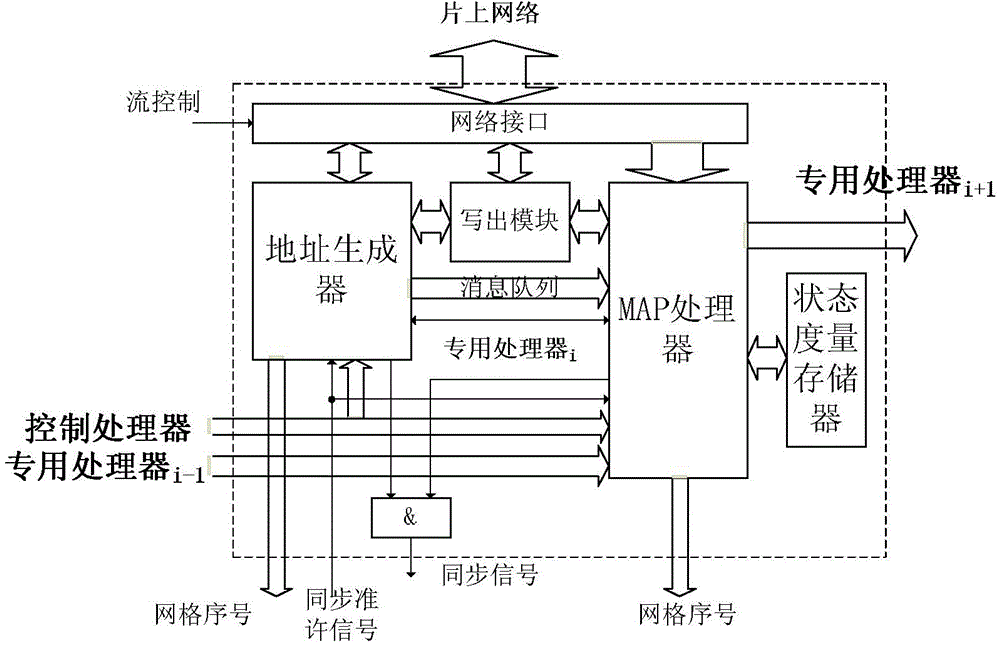

Distributed micro instruction set processor architecture for high-efficiency signal processing

ActiveUS20080084850A1Flexible computational supportEfficient process switchingEnergy efficient ICTProgram initiation/switchingProcess supportCommunications system

A wireless communication system hosts a plurality of processes in accordance with a communication protocol. The system includes application specific instruction set processors (ASISPs) that provided computation support for the process. Each ASISP is capable of executing a subset of the functions of a communication protocol. A scheduler is used to schedule the ASISPs in a time-sliced algorithm so that each ASISP supports several processes. In this architecture, the ASISP actively performs computations for one of the supported processes (active process) at any given time. The state information of each process supported by a particular ASISP is stored in a memory bank that is uniquely associated with the ASISP. When a scheduler instructs an ASISP to change which process is the active process, the state information for the inactivated process is stored in the memory bank and the state information for the newly activated process is retrieved from the memory bank.

Owner:INTEL CORP

Petri net model based ASIP (application specific instruction set processor) behavior logic synthesis method

InactiveCN107688704AReduce ambiguityImprove design efficiencyCAD circuit designSpecial data processing applicationsThird partySemantics

The invention relates to a design of a computer architecture, in particular to a design of an architecture for an application specific instruction set processor (ASIP). The method specially includes the steps of 1), establishing a Petri net based ASIP pipeline behavior model and adopting PNML (petri net markup language) to perform normative description; 2), achieving logic synthesis after the ASIPpipeline behavior model is mapped into a state machine view through organic relationship between a Petri net and a state machine; 3), downloading hard-link logic generated by an EDA tool chain to a real physical environment SoC for detection and running, and performing performance evaluation and optimizing the pipeline design. As a quite potential system level design method, the method has the advantages that normative Petri net model semantics and behaviors are acquired, correctness of the system's functionality can be verified in expectation, the method can serve as comprehensive tool inputand system technical documentation standards, and the executable description function of the method can be expanded through third-party tools.

Owner:JINLING INST OF TECH

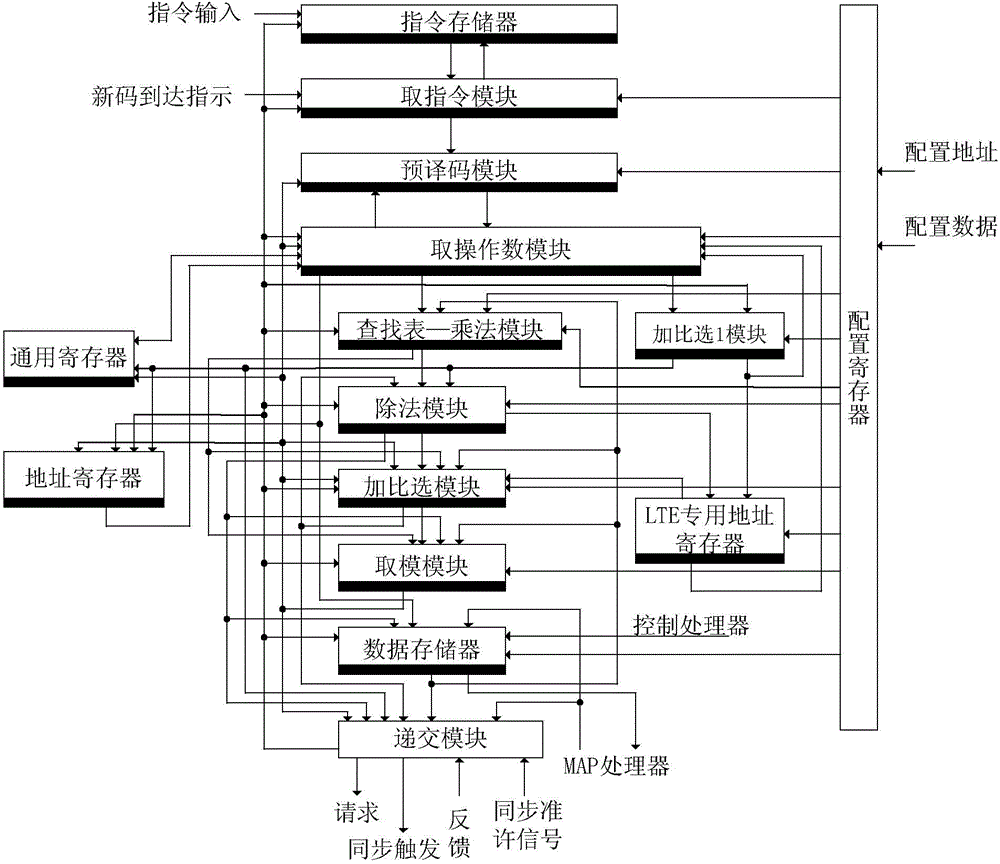

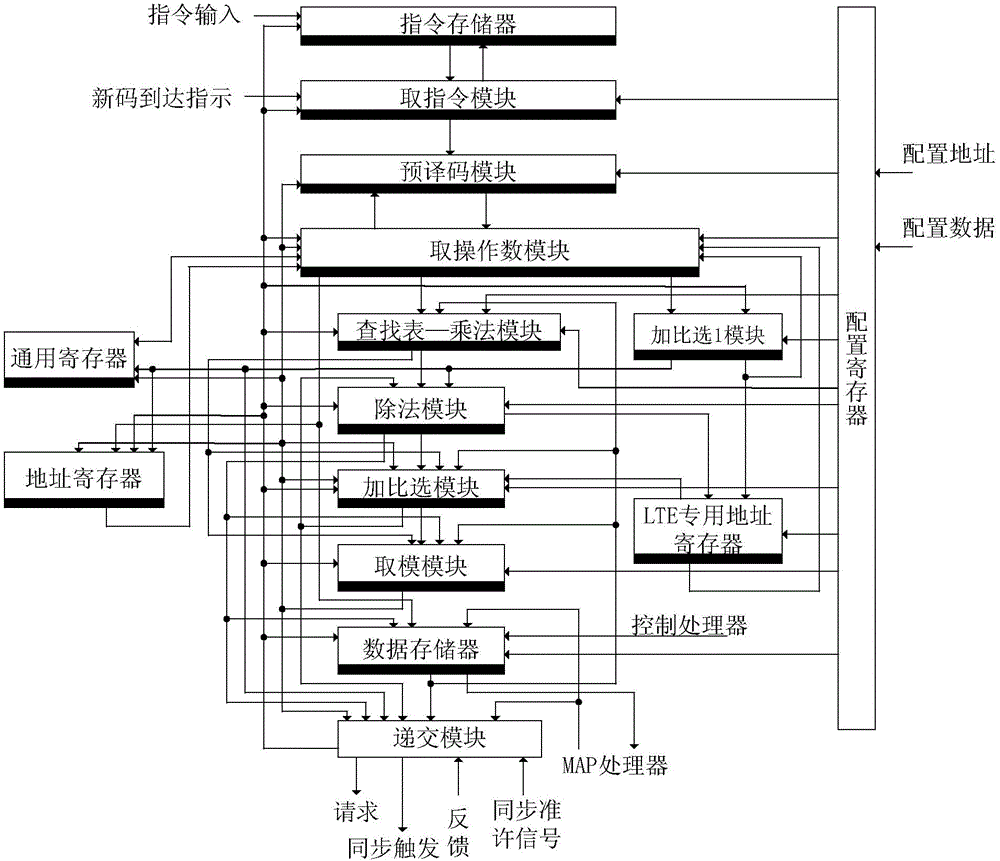

Address generator used for decoder of Turbo codes and LDPC codes

InactiveCN104539294AIncrease flexibilityError correction/detection using multiple parity bitsError correction/detection using interleaving techniquesInstruction memoryAddress generator

The invention belongs to the technical field of special instruction set processors, and particularly relates to an address generator used for a decoder of Turbo codes and LDPC codes. The address generator can generate addresses for the Turbo codes and the LDPC codes in various wireless communication standards including LTE / UMTS / WiMAX / WIFI and the like. A mixed structure is adopted for the address generator. The address generator mainly comprises an instruction memorizer, an instrument extraction module, a pre-decoding module, a multi-mode address calculation data channel, a data memorizer and the like, wherein the multi-mode address calculation data channel can be of different streamline structures according to configuration information, and address calculation is executed according to instructions. Compared with an ordinary address generator, the address generator is wider in coverage standard range and can generate addresses for the Turbo codes and the LDPC codes.

Owner:FUDAN UNIV

Coupling a general purpose processor to an application specific instruction set processor

InactiveUS20080098202A1Improve efficiencyProgram control using stored programsRuntime instruction translationGeneral purposeInstruction memory

Provides methods, systems and apparatus for coupling a general purpose processor (GPP) to an application specific instruction set processor (ASIP) in such a manner that the GPP can include execute instructions that do not normally comprise part of its instruction set architecture (ISA). The GPP is coupled to the ASIP via a coprocessor port such that instructions issued by the GPP to the port are conveyed to a novel pre-decoder module of the ASIP. The pre-decoder module translates the GPP instruction into operation codes for ASIP instructions to be executed in the ASIP or to an address in the ASIP instruction memory that identifies a start address for a plurality of ASIP instructions defining a complex application specific function. Once the ASIP has executed the instructions it shares the result of the execution with the GPP. In this way, the GPP takes advantage of the ASIP in its ability to more quickly execute an application specific program / procedure.

Owner:INTERNATIONAL BUSINESS MACHINE CORPORATION

Address generator for Turbo code and LDPC (Low Density Parity Check) code decoder

InactiveCN104579363AIncrease flexibilityError correction/detection using multiple parity bitsError correction/detection using interleaving techniquesInstruction memoryCode module

The invention belongs to the technical field of special instruction set processors and particularly relates to an address generator for a Turbo code and LDPC (Low Density Parity Check) code decoder. The address generator can generate addresses for Turbo codes and LDPC codes in various wireless communication standards, including LTE / UMTS / WiMAX / WIFI (Long Term Evolution / Universal Mobile Telecommunications System / Worldwide Interoperability for Microwave Access / Wireless Fidelity) and the like. The address generator adopts a hybrid structure and mainly comprises an instruction memory, an instruction fetch module, a pre-coding module, a multimode address computation data path, a data memory and the like, wherein the multimode address computation data path can form different pipeline structures according to configuration information and execute address computation according to an instruction. Compared with the general address generator, the address generator has wider standard coverage, and can generate the addresses for the Turbo codes and the LDPC codes.

Owner:FUDAN UNIV

Application program and special instruction set integrated processor agile design method

ActiveCN110210046ARealize integrated designRealize the designEnergy efficient computingSpecial data processing applicationsComputer architectureApplication software

The invention provides an application program and special instruction set integrated processor agile design method. The method comprises the following steps: establishing an application and test environment of an application program to be operated on a processor; formulating a processor expansion architecture and an expansion description rule, representing basic expansion units in the processor byusing a specified data type, and representing an expansion instruction in the processor by using an expansion instruction definition function; compiling an expansion instruction definition function under the formulated processor expansion architecture and the expansion description rule; and realizing the hot spot part of the application program by using the expansion instruction definition function. The processor expansion instruction is described by adopting an advanced programming language, so that a general engineer can effectively master the processor expansion instruction. The definitionof the processor extension instruction only comprises an operation definition, and details for realizing the instruction in the processor micro-architecture are not involved. Integrated research anddevelopment of processor extension instructions and application programs are achieved, and a development environment in a rapid cycle of definition, use and verification of the expansion instructionsis achieved.

Owner:芯易荟(上海)芯片科技有限公司

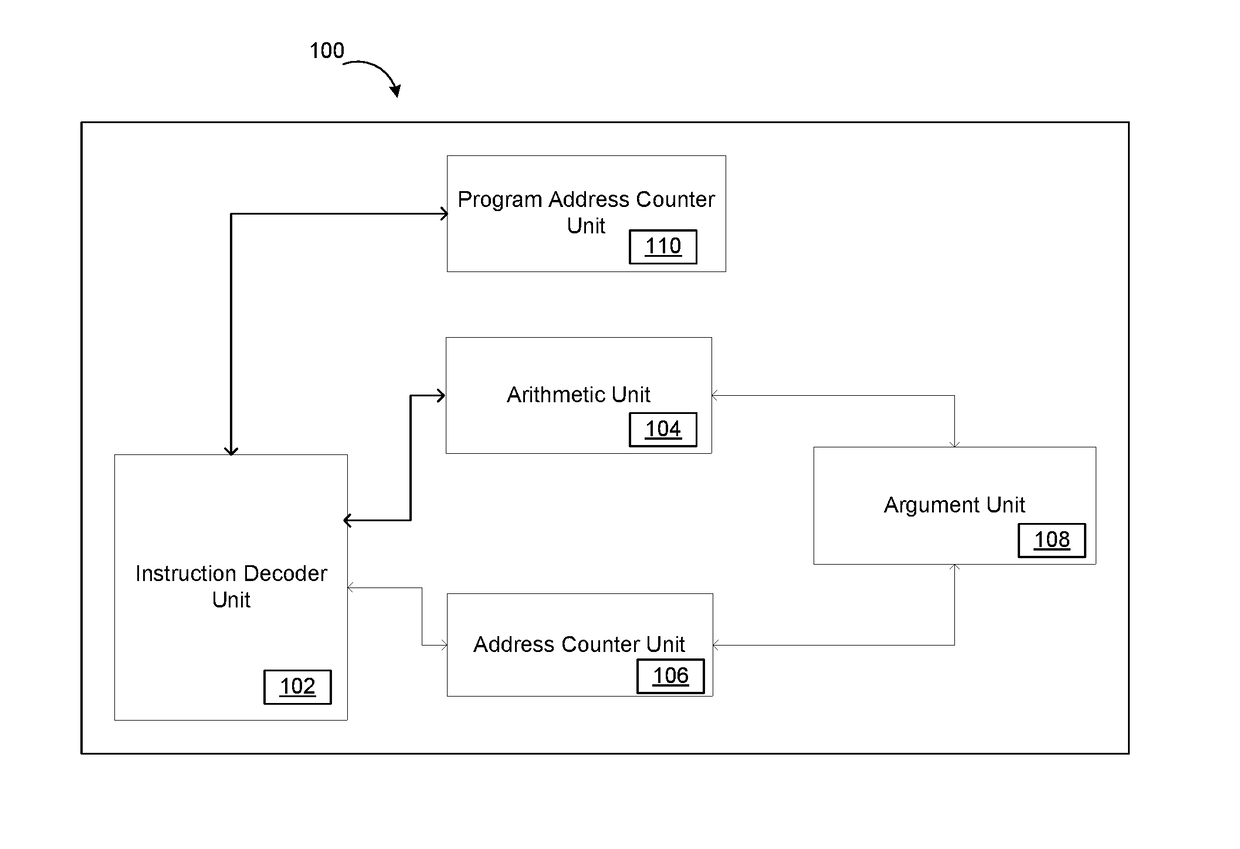

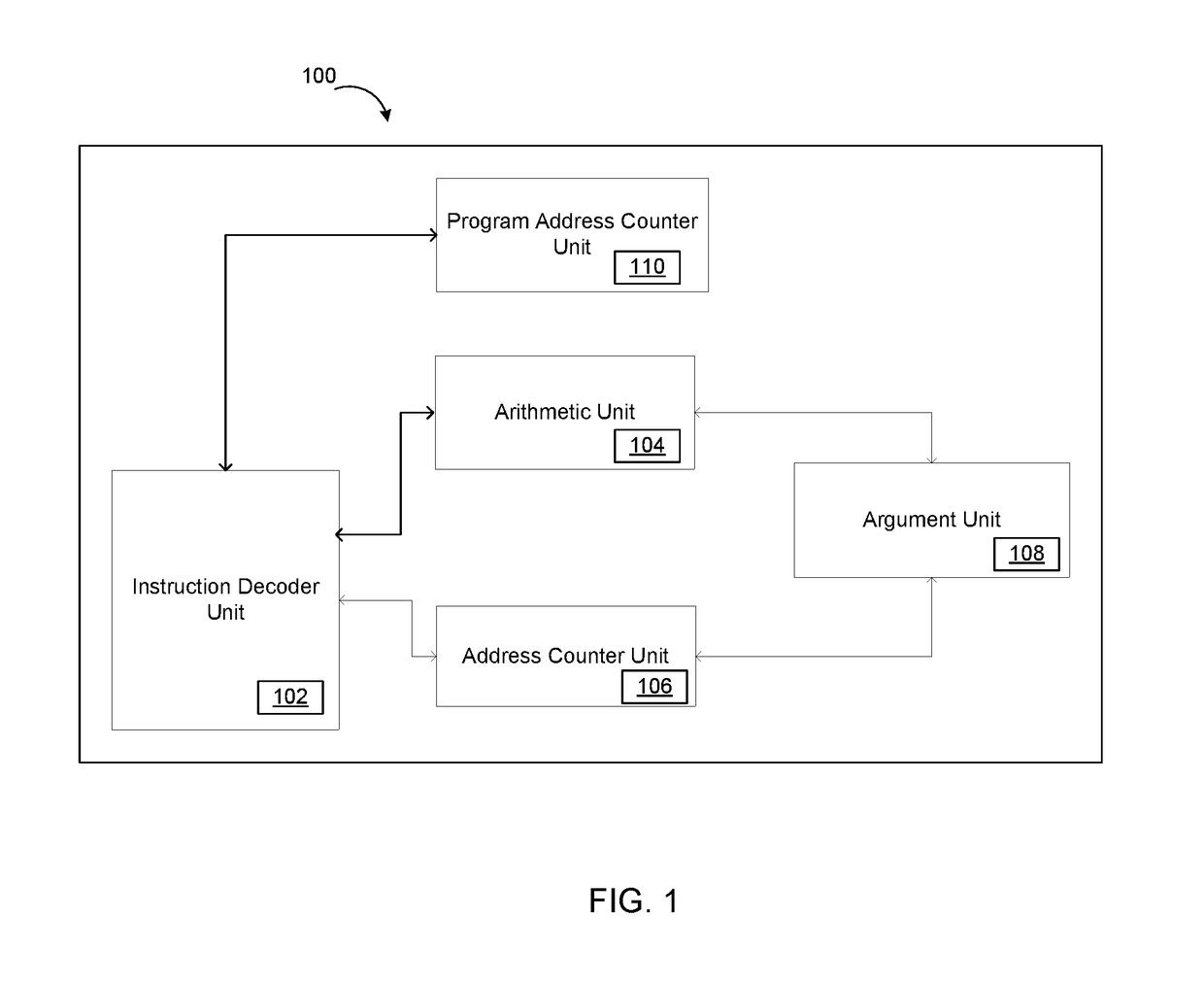

Application specific instruction-set processor (ASIP) architecture having separated input and output data ports

The invention provide an application specific instruction-set processor (ASIP) that uses a Very Long Instruction Word (VLIW) for executing atomic application specific instructions. The ASIP includes one or more units for executing a first set of atomic application specific instructions for receiving a first set of data across a plurality of input data ports in a first operation specified in an instruction word. Further, the one or more units execute a second set of atomic application specific instructions for outputting a second set of data across a plurality of output data ports in a second operation specified in the instruction word, wherein an input data port of the plurality of input data ports and a corresponding output data port of the plurality of output data ports share a same address location and are specified as operands in the instruction word. Thus, the first operation and the second operation can occur simultaneously.

Owner:KING ABDULAZIZ CITY FOR SCIENCE AND TECHNOLOGY

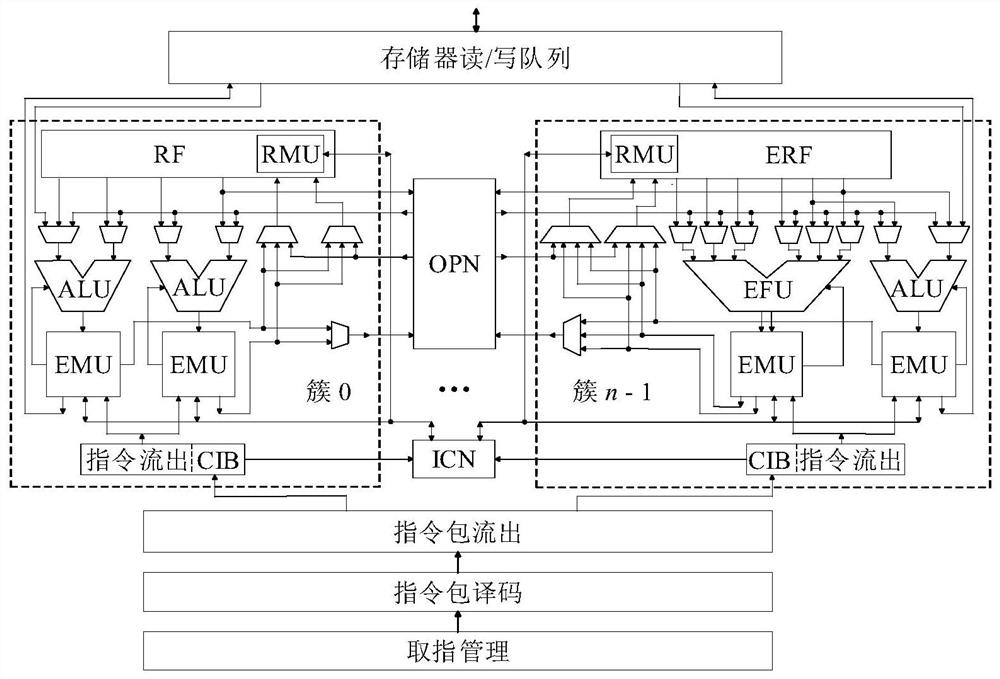

An extensible asip structure platform and instruction processing method

ActiveCN111061510BNo significant overheadThe principle is simpleDigital computer detailsMachine execution arrangementsArithmetic logic unitComputer architecture

The invention discloses an extensible ASIP structure platform and an instruction processing method. The platform is provided with an assembly line of instruction execution logic, the instruction execution logic comprises n clusters, the clusters 0-(n-2) are conventional clusters and used for achieving conventional instructions, and each cluster comprises two arithmetic logic units ALU and a 4-read-2-write distributed register file RF; the cluster n-1 is an extension cluster, is used for realizing a special extension instruction, and comprises an ERF (Extended Register Function) with 6 read ports, 2 write ports and at most 32 universal registers, an EFU (Extended Function Unit) with 6 inputs and 2 outputs, and an arithmetic logic unit ALU (Arithmetic Logic Unit); an outflow control networkunit ICN and an operand transfer network unit OPN are included between the clusters; and the execution management unit EMU coupled with each ALU or EFU and the register management unit RMU coupled with each RF or ERF form hardware of an instruction execution control mechanism. According to the method, instruction processing is completed based on the platform. The method has the advantages of beingeasy to implement, capable of improving the expansibility of the special instruction set processor and the like.

Owner:HUNAN GREAT LEO MICROELECTRONICS CO LTD

H.264 cavlc decoding method based on application-specific instruction-set processor

Provided is an H.264 Context Adaptive Variable Length Coding (CAVLC) decoding method based on an Application-Specific Instruction-set Processor (ASIP). The H.264 CAVLC decoding method includes determining a plurality of comparison bit strings on the basis of a table of a decoding coefficient, storing lengths of the comparison bit strings in a first register, storing code values of the comparison bit strings in a second register, comparing an input bit stream with the comparison bit strings based on the lengths and code values of the comparison bit strings, and determining value of the decoding coefficient according to a result of comparison between the input bit stream and the comparison bit strings. The method extracts a decoding coefficient using a register in an ASIP without accessing a memory and prevents a reduction in speed caused by memory access, thereby increasing the decoding speed of an H.264 decoder.

Owner:ELECTRONICS & TELECOMM RES INST

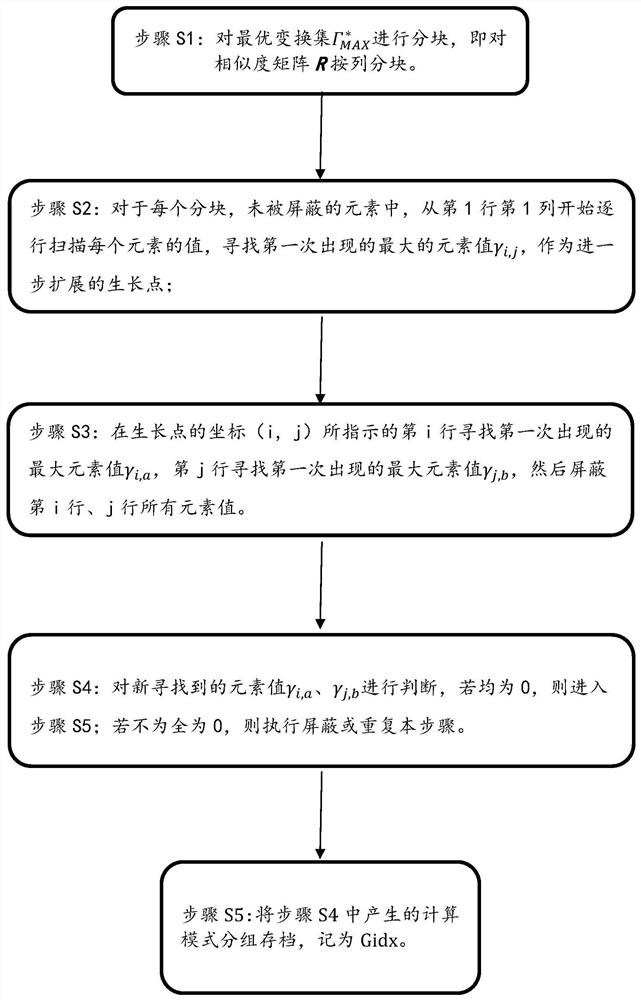

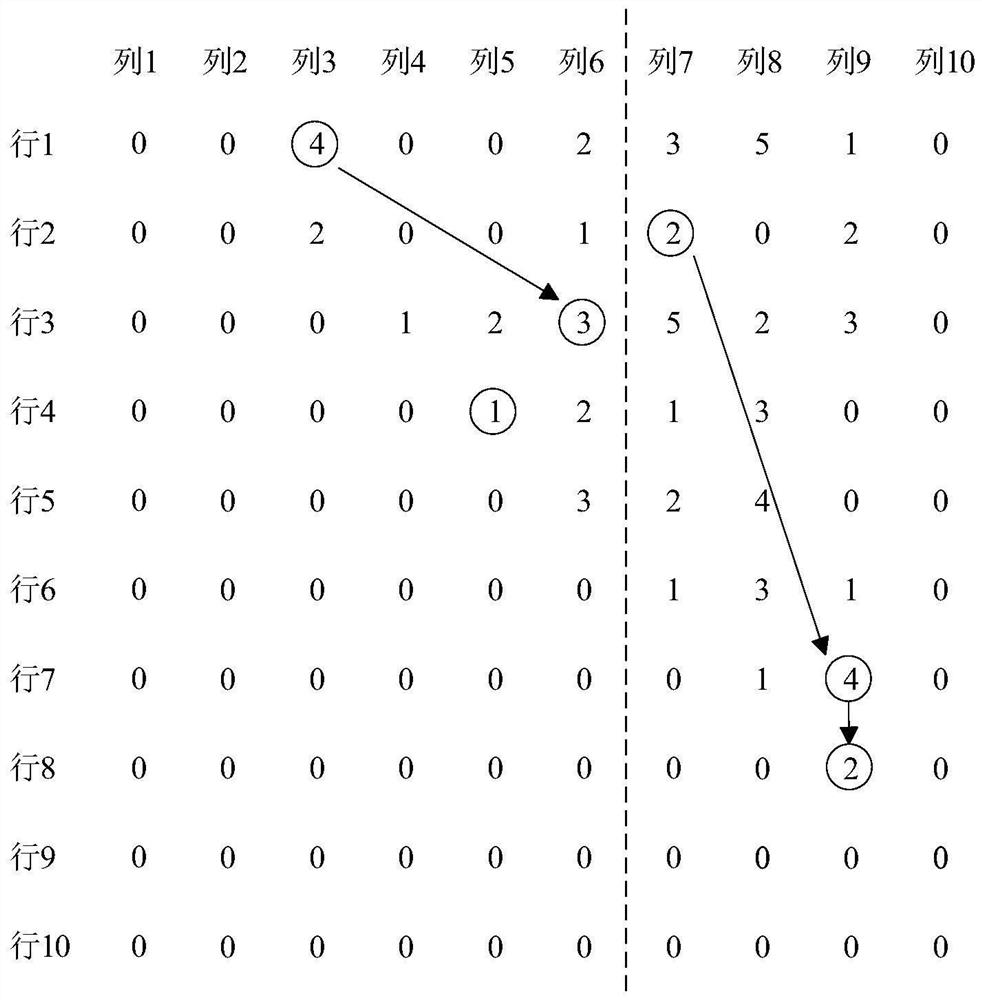

Logic resource sharing method for special instruction set processor

PendingCN113076135AThe principle is simpleEasy to implementMachine execution arrangementsTheoretical computer scienceSimilarity matrix

The invention discloses a logical resource sharing method for a special instruction set processor. The method comprises steps of S1, an optimal transformation set being partitioned, and a similarity matrix R being partitioned according to columns; S2, for unshielded elements of each block, scanning the value of each element line by line from the first row and the first column, and searching the maximum element value gamma i, j appearing for the first time as a growth point for further expansion; S3, searching a maximum element value gamma i, a appearing for the first time in the ith row indicated by the coordinates (i, j) of the growing points, searching a maximum element value gamma j, b appearing for the first time in the jth row, and then shielding all element values in the ith row and the jth row; S4, judging the newly found element values gamma i, a and gamma j, b, and if all the elements are 0, continuing; otherwise, shielding or repeating the step; and S5, grouping and archiving the calculation modes generated in the step S4. The method has advantages of being simple in principle, easy to implement, capable of improving calculation efficiency and resource utilization rate and the like.

Owner:谷芯(广州)技术有限公司

Specific processor system structure for high-performance programmable controller and implementation method of dedicated processor system structure

ActiveCN102298352BReduce the number of instructionsFast executionConcurrent instruction executionComputer architectureProgrammable logic controller

The invention relates to a specific processor system structure for a high-performance programmable controller and an implementation method of the dedicated processor system structure. The specific processor system structure comprises a PLC (Programmable Logic Controller) specific instrument set processor and a general processor, wherein the PLC specific instrument set processor is connected with a general processor through the PLC specific instrument set processor and an interface of the general processor. The implementation method comprises a four-level flow line consisting of a fetch stage,a decoding stage, an executing stage and a writing-back stage, according to the PLC specific instrument set processor. By designing the PLC specific instrument set which accords with the PLC instrument characteristics, the number of instruments for executing a PLC processor is reduced, the execution speed of a PLC program is accelerated, and the processing performance of the PLC processor to a functional block is improved.

Owner:SHENYANG INST OF AUTOMATION - CHINESE ACAD OF SCI

Method for designing specific instruction set processor

ActiveCN101561833BAccelerate Design CycleImprove performanceSpecial data processing applicationsProcessor modelComputer architecture

The invention relates to a method for designing a specific instruction set processor, and the method can make the accuracy performance evaluation at the beginning of designing a chip, advance the testof a specific application, speed up the design process and reduce the re-design possibility which is because the performances of the chip can not achieve the requirements. The method establishes an LISA processor model at the early stage of the design, generates a corresponding software tool by the LISA model, builds up a virtual prototyping platform which is similar to the performances of real hardware on an ARM ESL, including a AHB bus model with precise cycle, an EMI model and an SDRAM model which are needed for designing the platform, searches out the performances under the different situations by repairing the models of the processor, obtains an optical software / hardware dividing method, directly verifies on the models and speeds up the design cycle of the processor.

Owner:SOUTHEAST UNIV