Assembler designing method based on specific instruction set processor for very long instruction words

A technology of super-long instruction words and special instructions, applied in the direction of concurrent instruction execution, machine execution devices, etc., can solve the problems of increasing the workload of designers, increasing the design and implementation cycle, etc., to improve design efficiency, improve parallelism, and expand applications. field effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

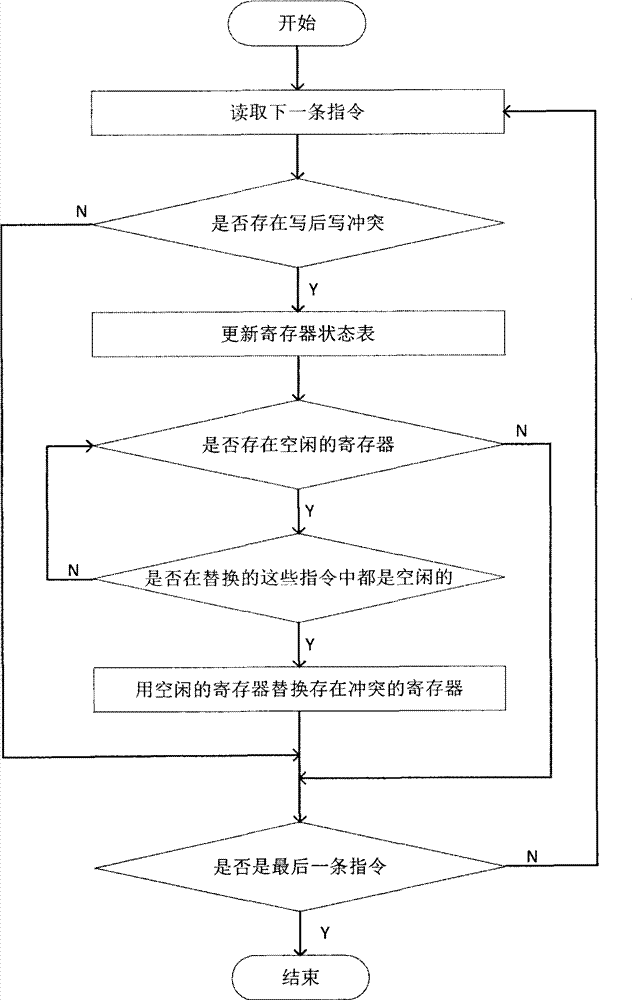

[0020] Example 1: Register renaming process

[0021] refer to figure 1 , the implementation of register renaming requires instruction write-after-write conflict detection. If a write-after-write conflict is found in the instruction, check whether there are free registers and determine whether the free registers are all free during the replacement of conflicting registers in these instructions. Yes, if there are free registers and they are always free, register renaming can be used to eliminate write-after-write conflicts. A register is free from the last time it is called until it is reassigned, and can be used for renaming. How to judge whether a register is free? For this problem, we create a register state table, and analyze the use of registers between different instructions to create a state table. When you encounter a register that needs to be renamed, that is, a register with a write-after-write conflict, you can look up the status table to determine whether there is...

Embodiment 2

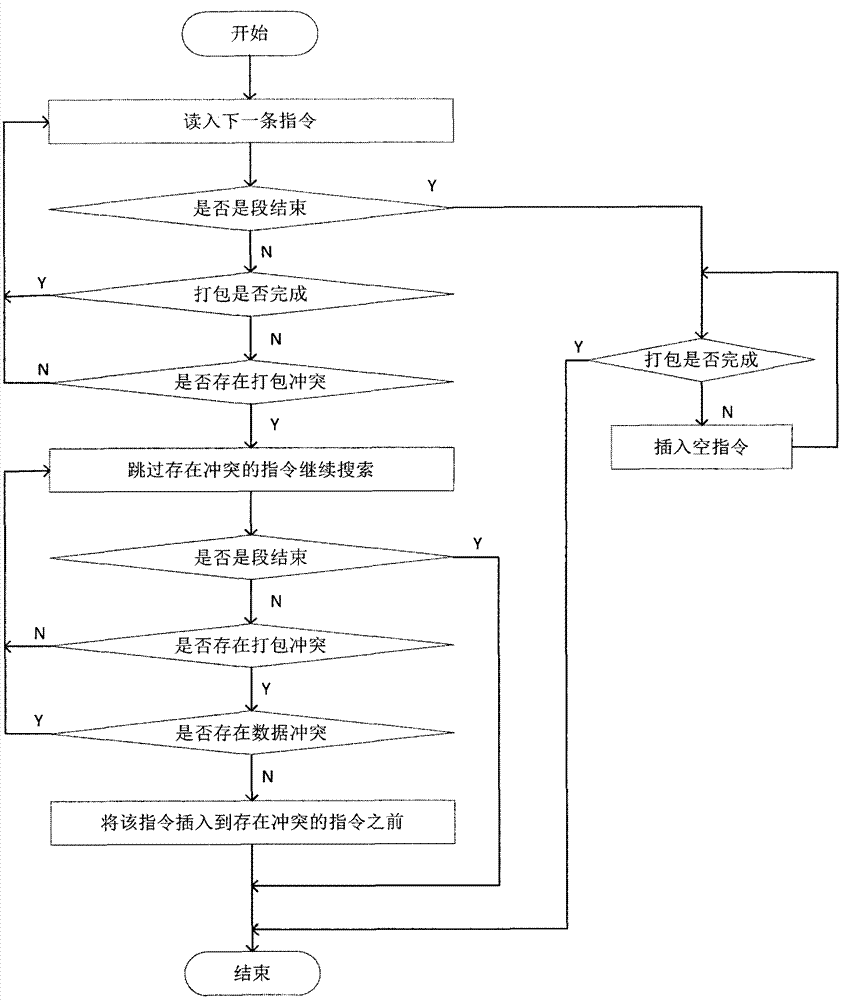

[0038] Embodiment 2: Instruction packaging and scheduling design method

[0039] In the process of instruction packaging and scheduling, the execution order of instructions before and after the jump instruction needs to be protected. This protection is mainly through the following two methods:

[0040] Instructions that appear before the jump instruction cannot be placed after the jump instruction;

[0041] Instructions that appear after a jump instruction cannot be placed before the jump instruction.

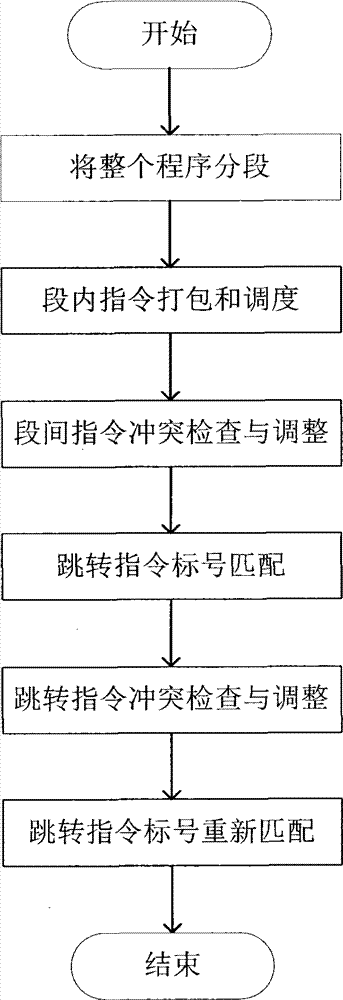

[0042] For the protection of the execution order of instructions before and after the jump instruction, the correct execution order of the instructions is mainly ensured by means of program segmentation. The instruction packaging and scheduling process of the entire program is as follows: figure 2 shown. First, the whole program is segmented according to the jump instruction and the target label. After the program is segmented, the instruction scheduling in the segment is n...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More