Patents

Literature

150 results about "Register renaming" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer architecture, register renaming is a technique that abstracts logical registers from physical registers. Every logical register has a set of physical registers associated with it. While a programmer in assembly language refers for instance to a logical register accu, the processor transposes this name to one specific physical register on the fly. The physical registers are opaque and cannot be referenced directly but only via the canonical names.

Using register rename maps to facilitate precise exception semantics

ActiveUS20100153690A1Facilitates precise exception semantics for a virtual machineEasy to implementDigital computer detailsMemory systemsSemanticsOut-of-order execution

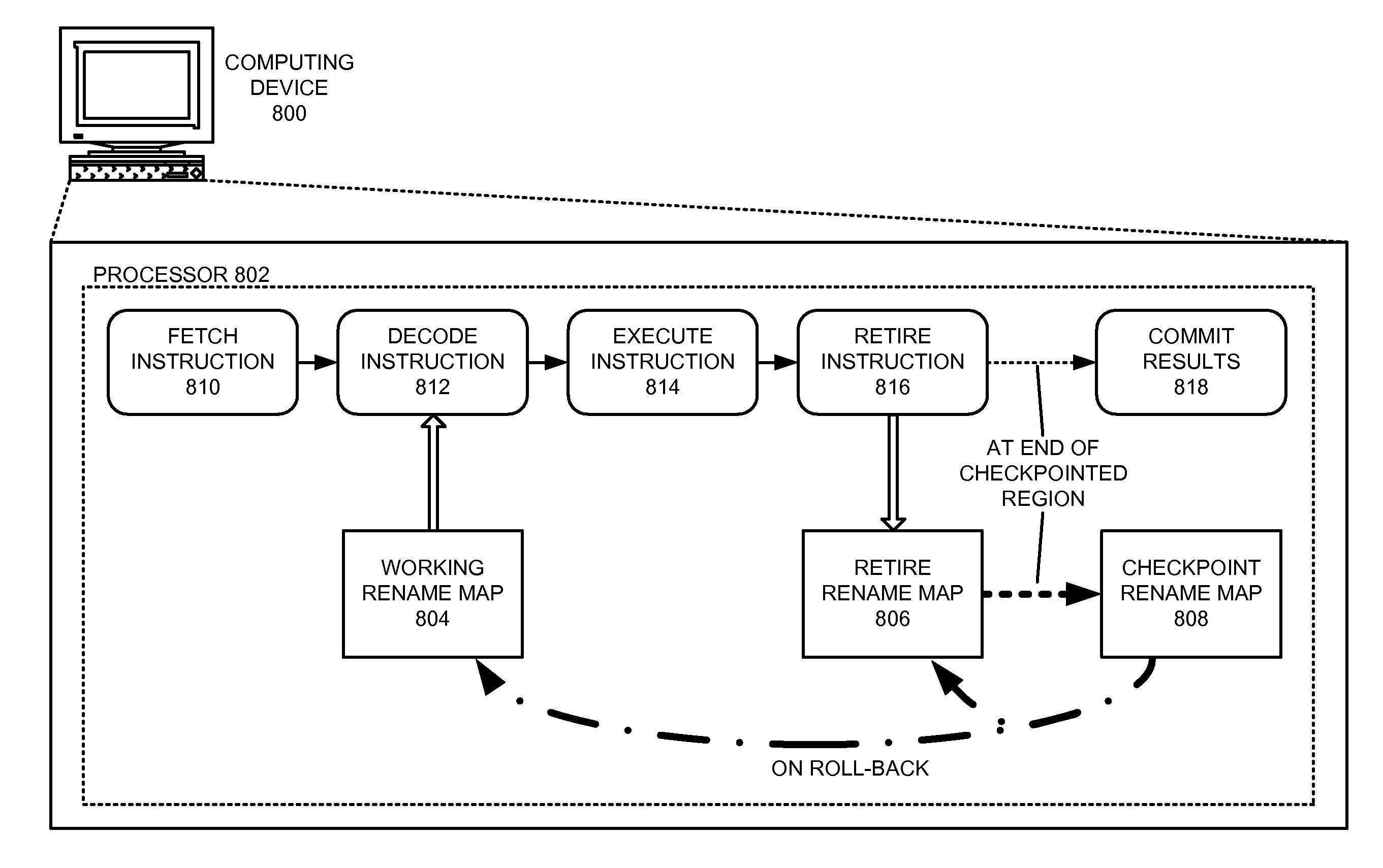

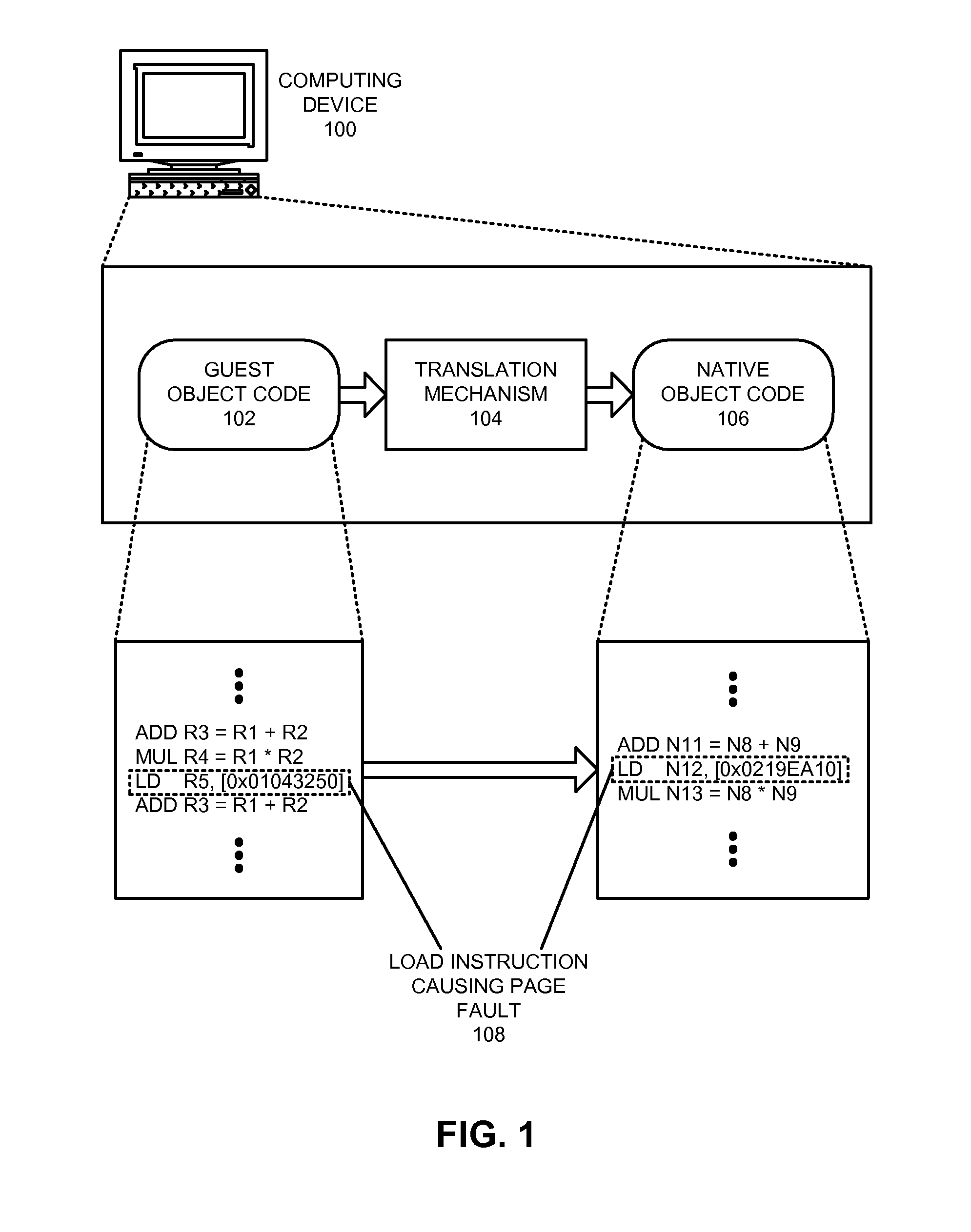

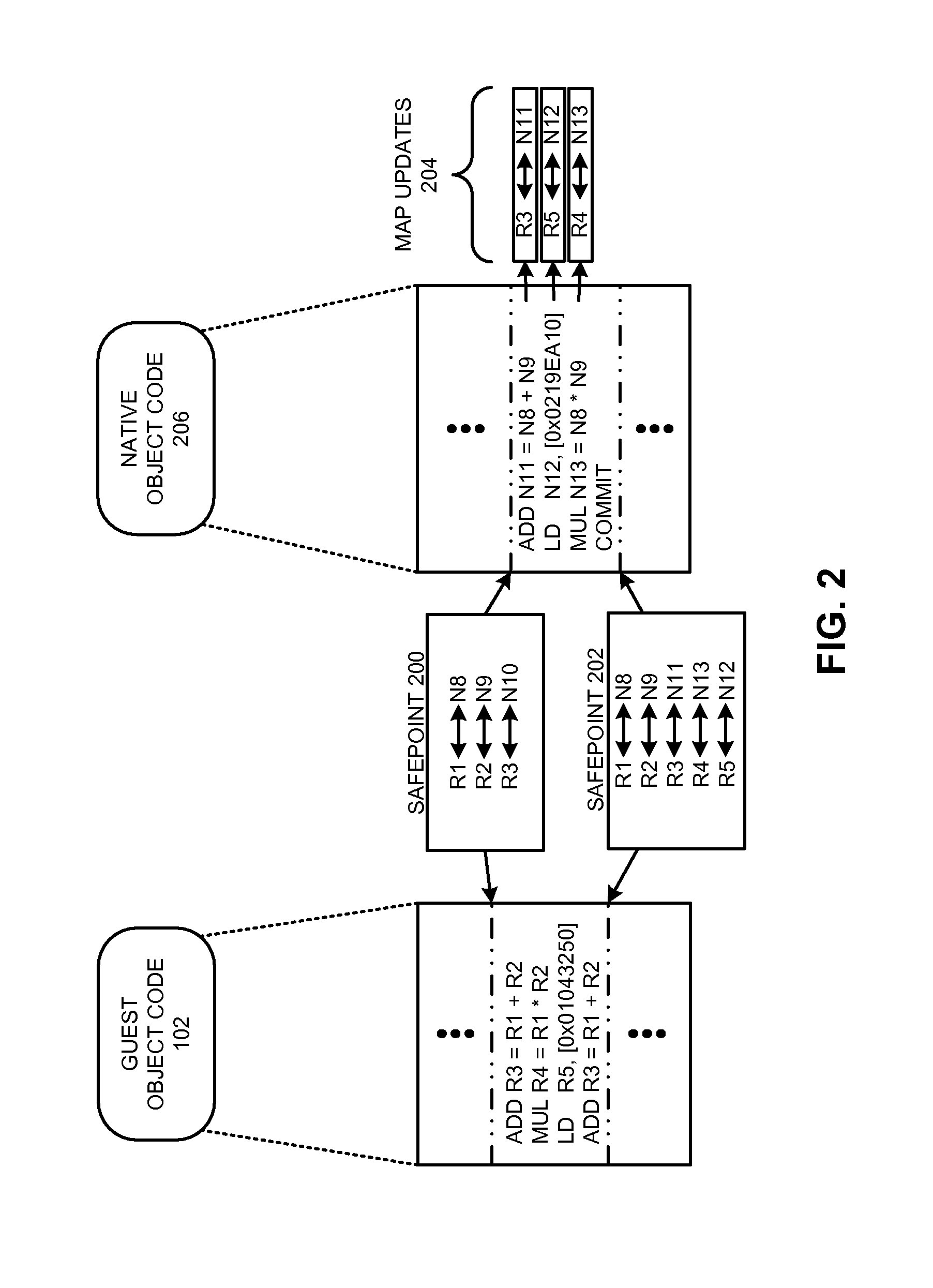

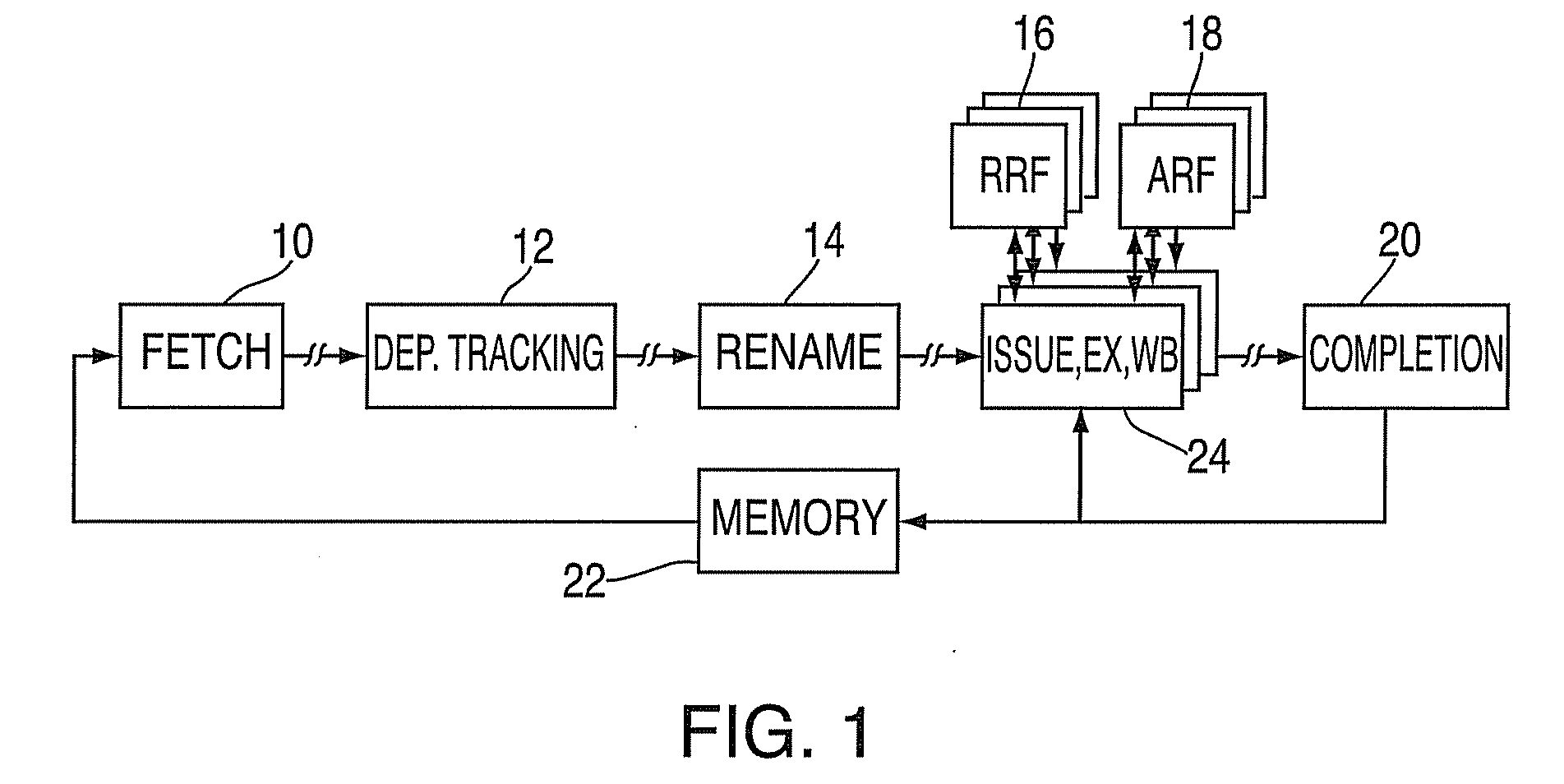

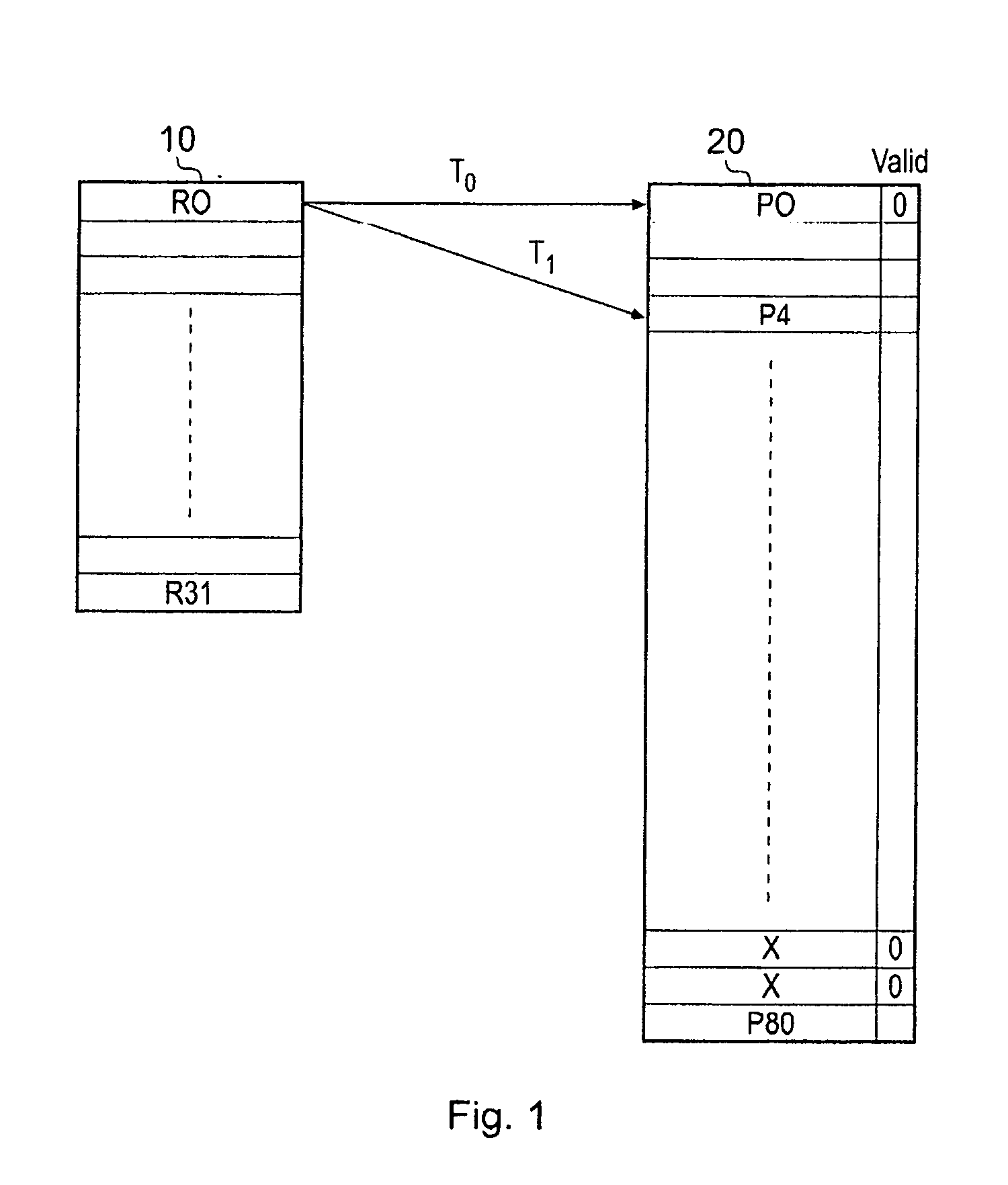

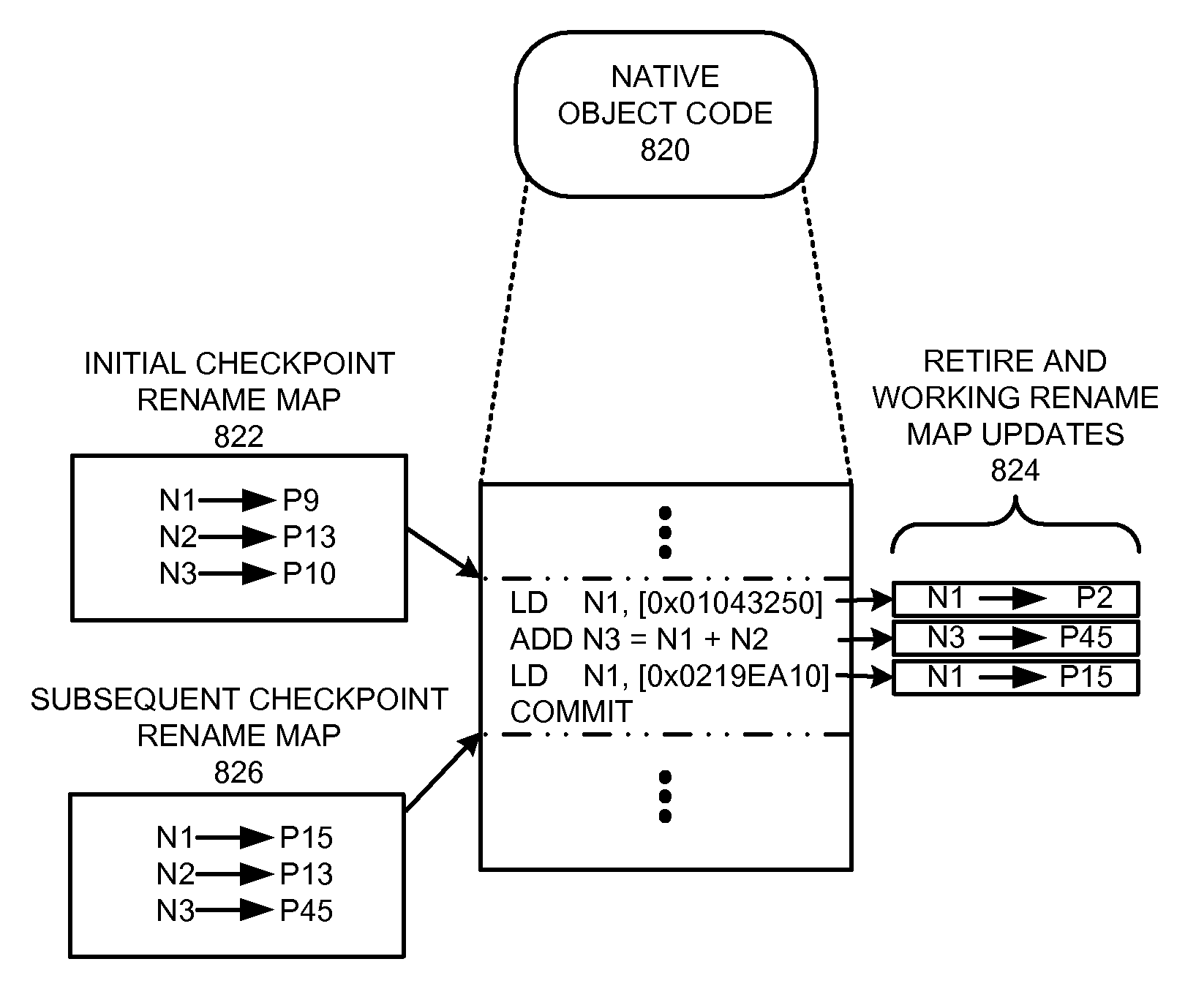

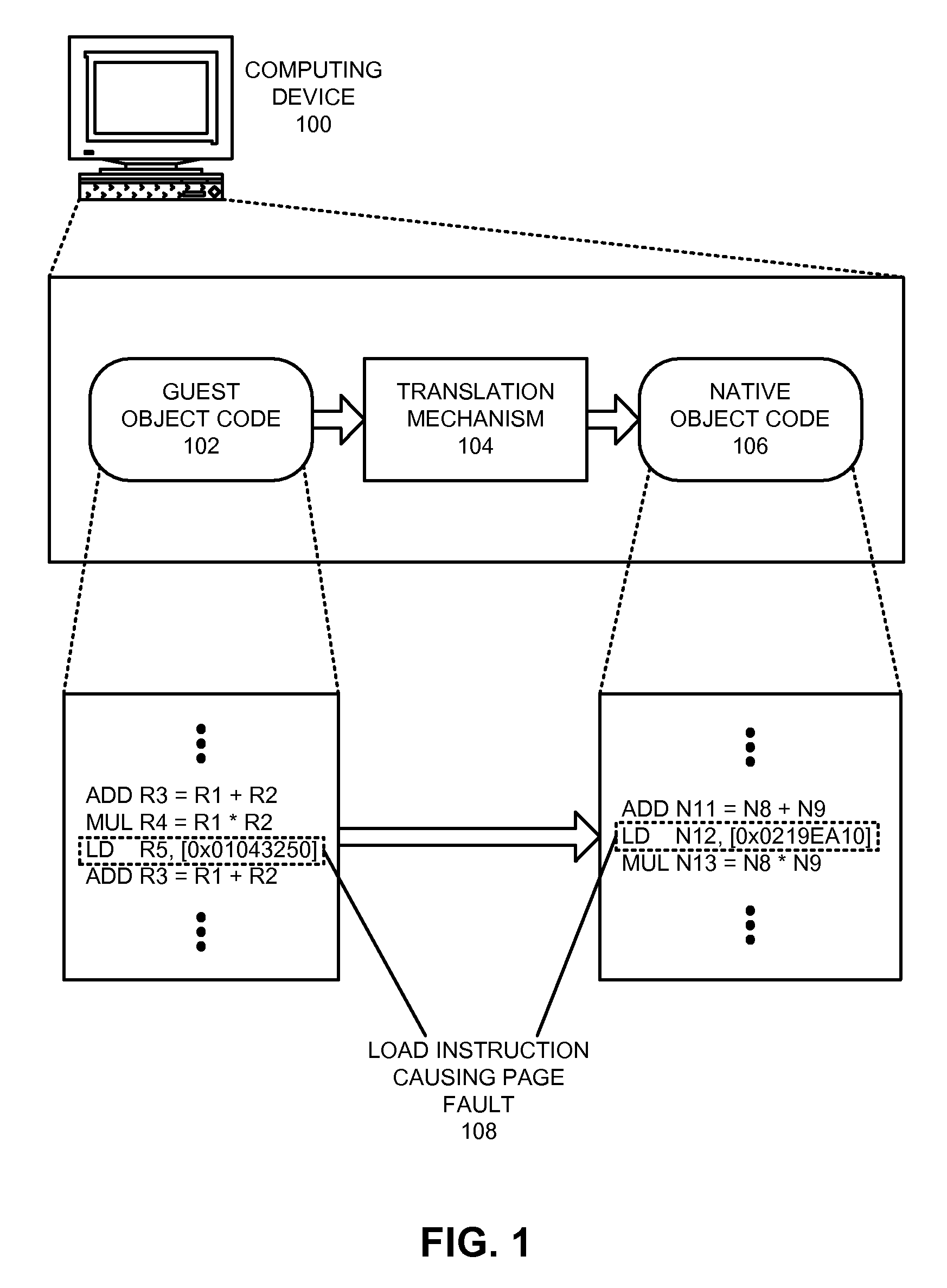

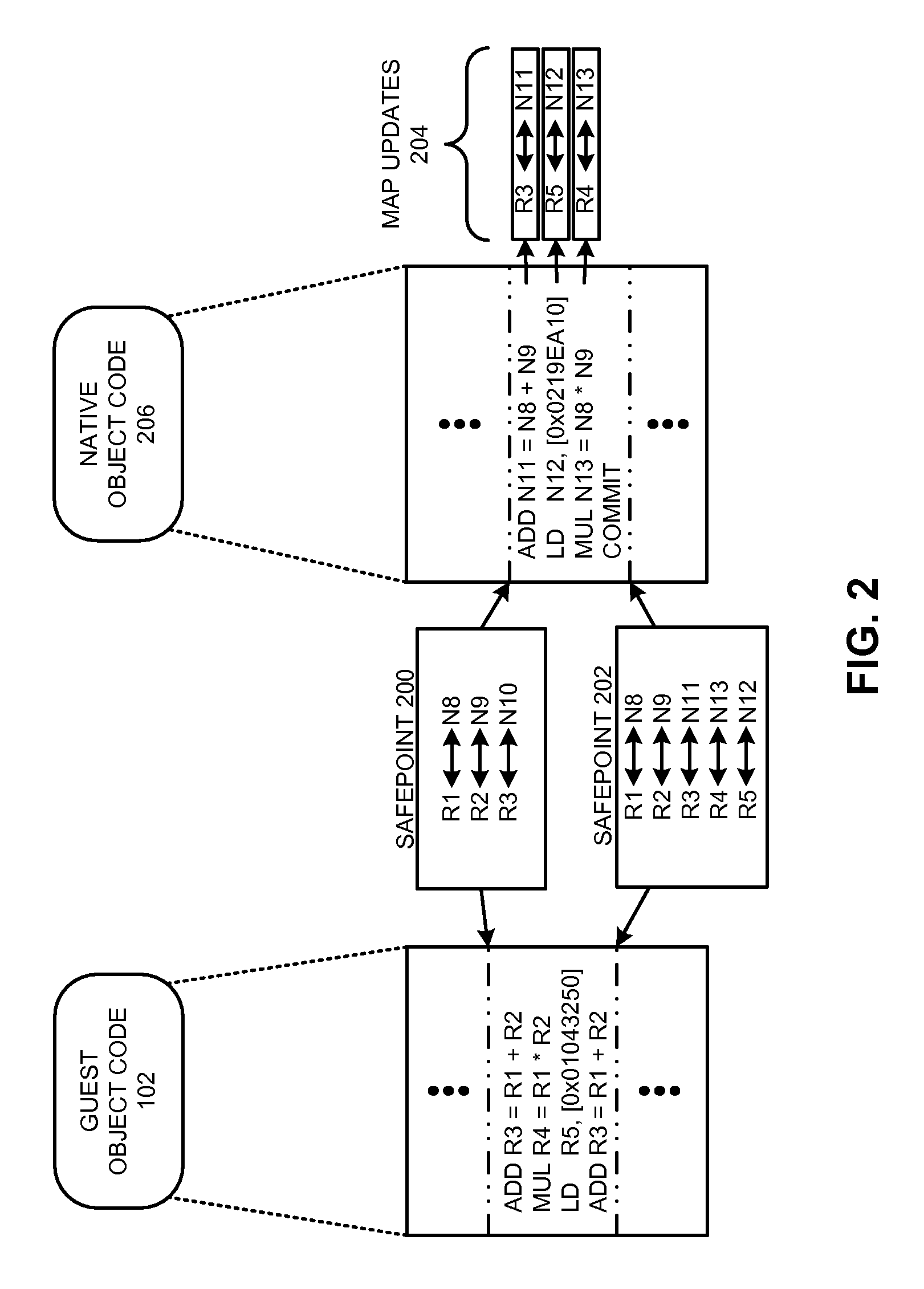

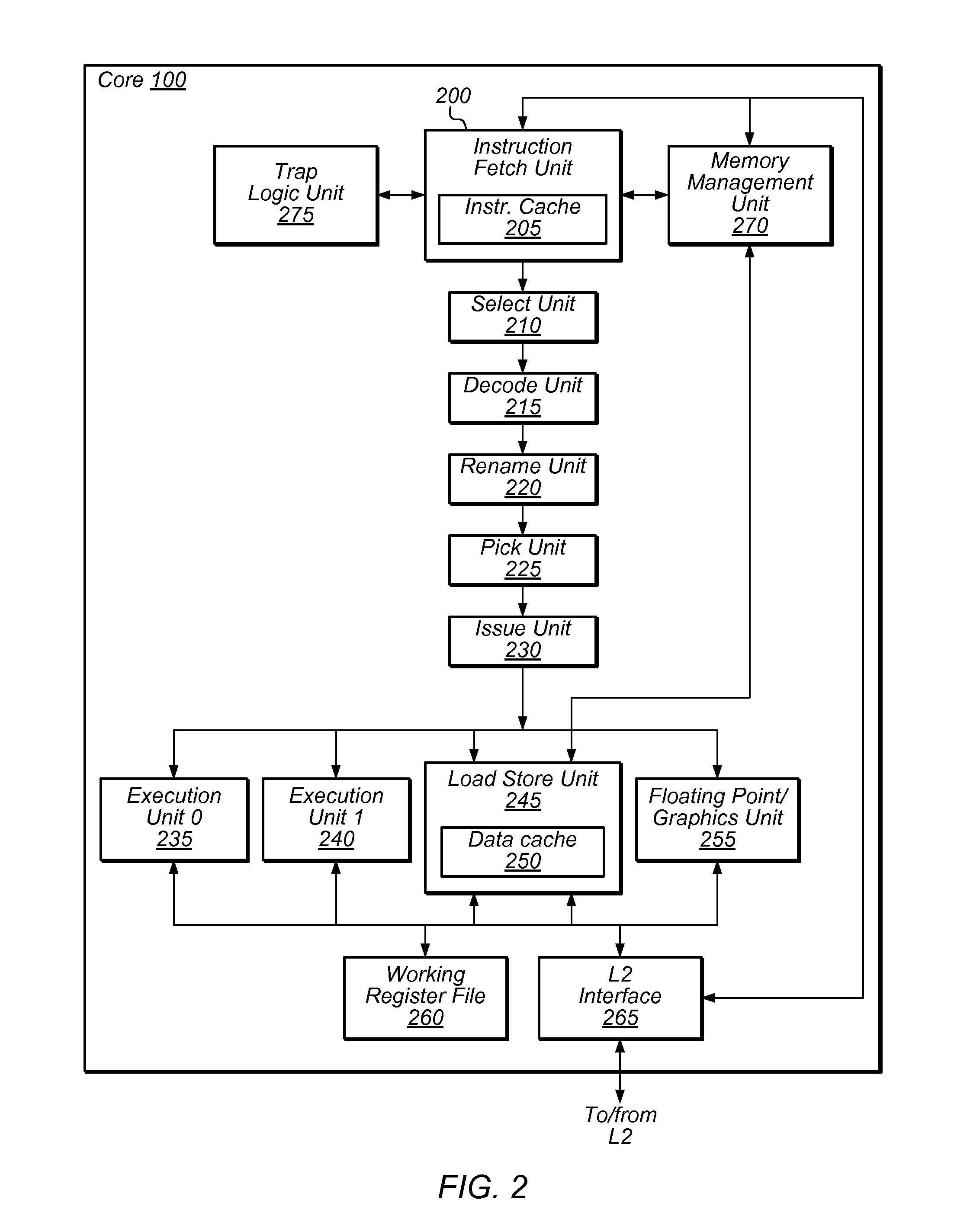

One embodiment of the present invention provides a system that facilitates precise exception semantics. The system includes a processor that uses register rename maps to support out-of-order execution, where the register rename maps track mappings between native architectural registers and physical registers for a program executing on the processor. These register rename maps include: 1) a working rename map that maps architectural registers associated with a decoded instruction to corresponding physical registers; 2) a retire rename map that tracks and preserves a set of physical registers that are associated with retired instructions; and 3) a checkpoint rename map that stores a mapping between a set of architectural registers and a set of physical registers for a preceding checkpoint in the program. When the program signals an exception, the processor uses the checkpoint rename map to roll back program execution to the preceding checkpoint.

Owner:ORACLE INT CORP

Method And Apparatus For Register Renaming Using Multiple Physical Register Files And Avoiding Associative Search

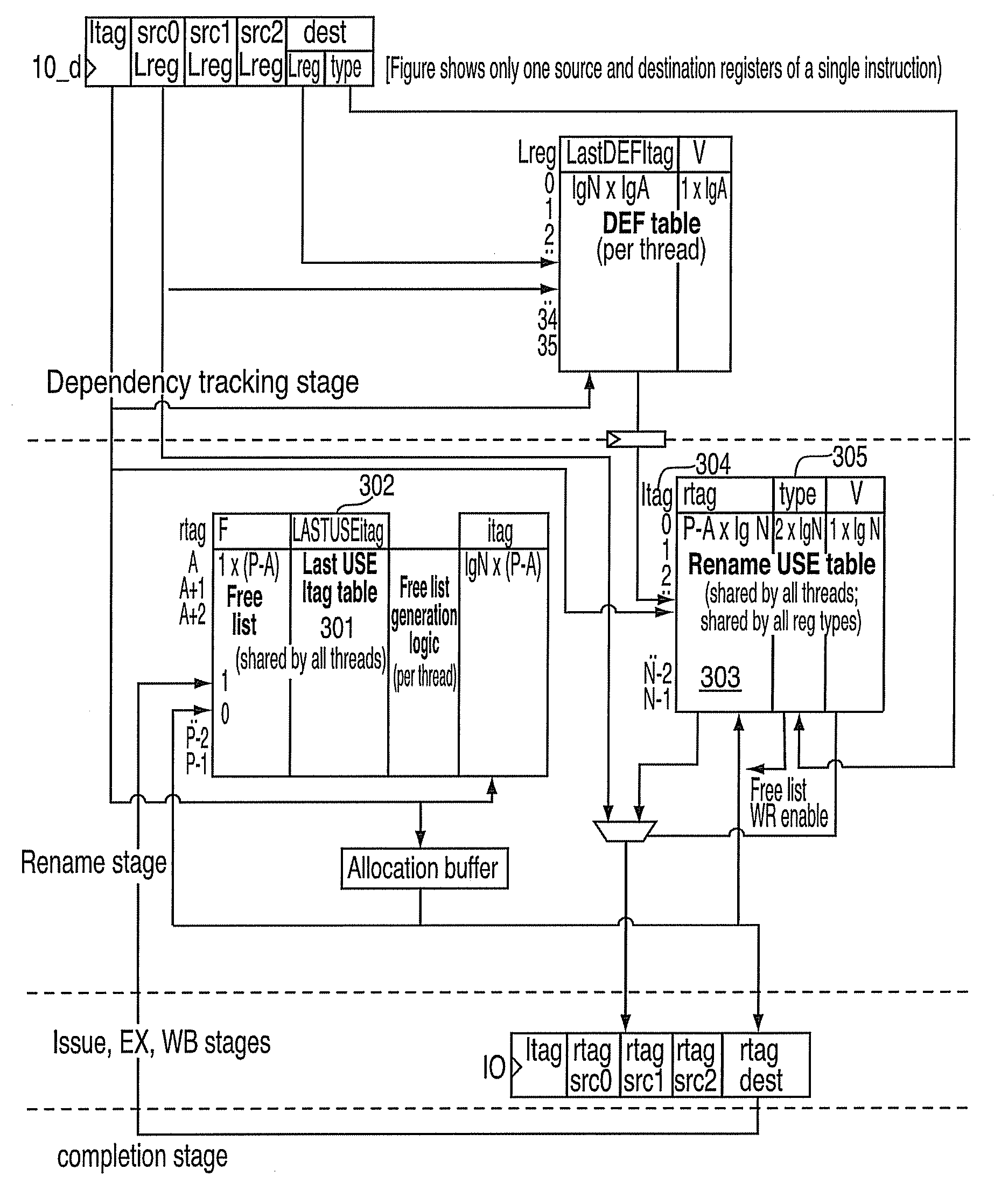

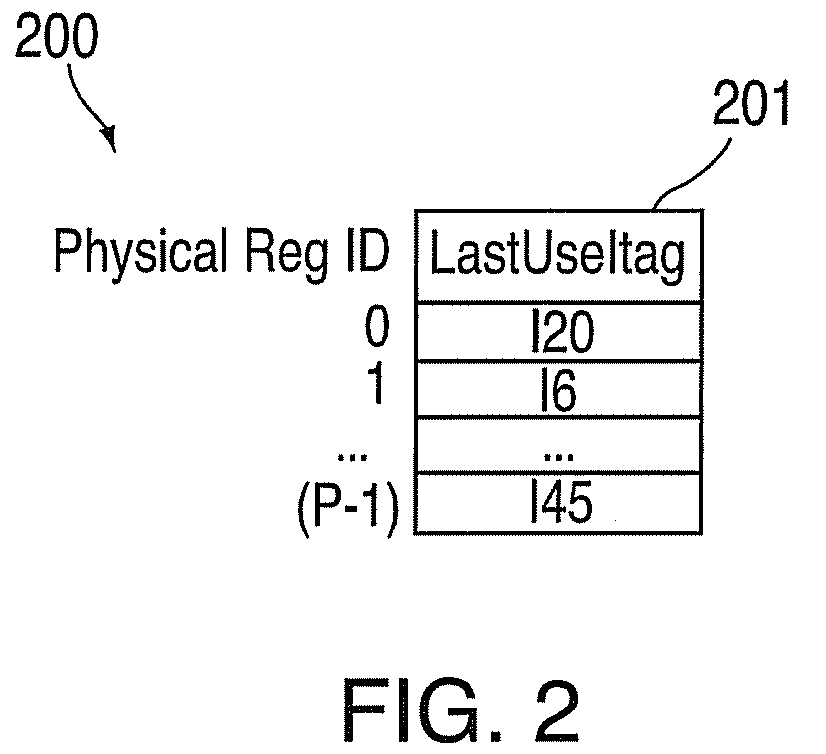

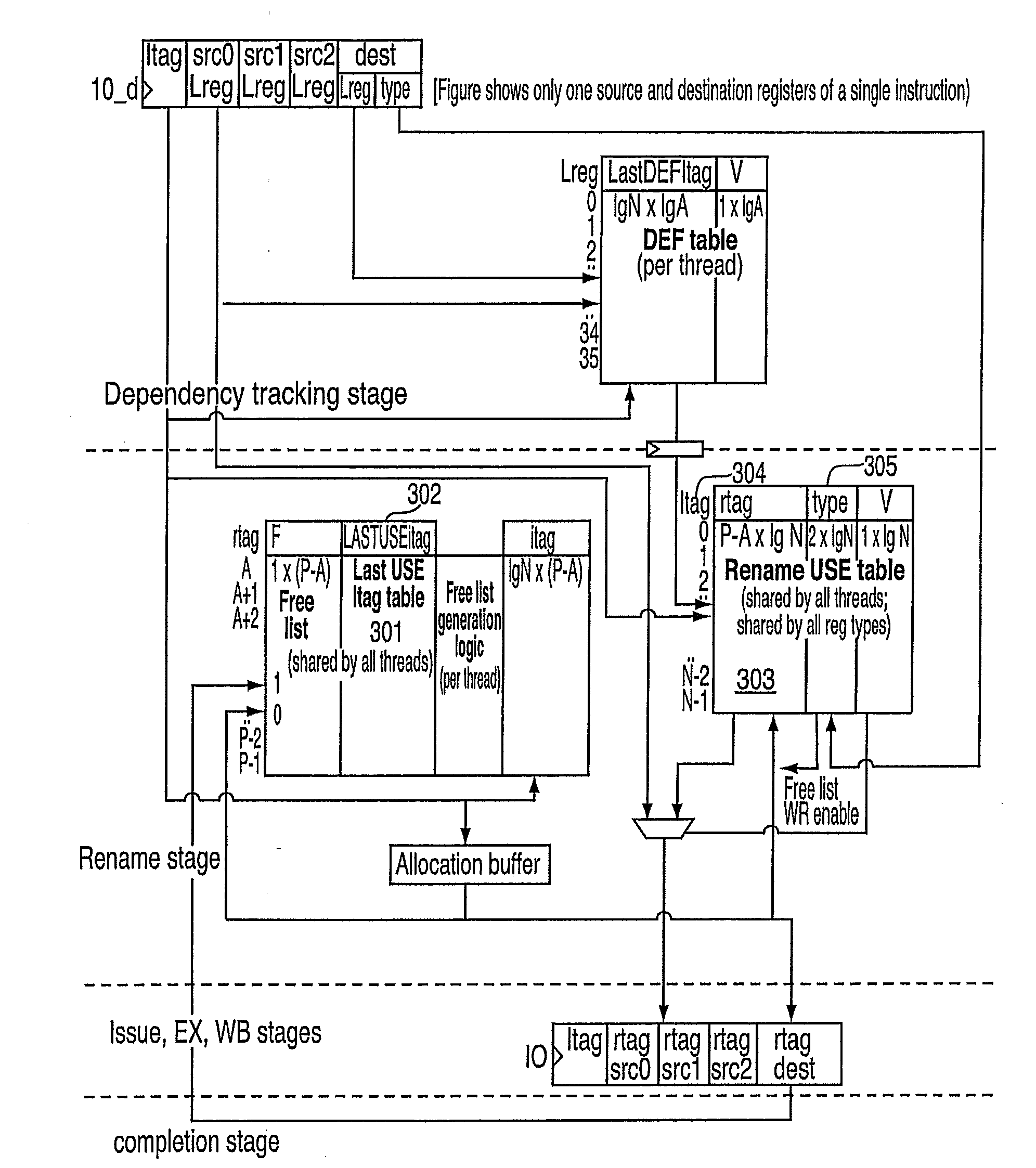

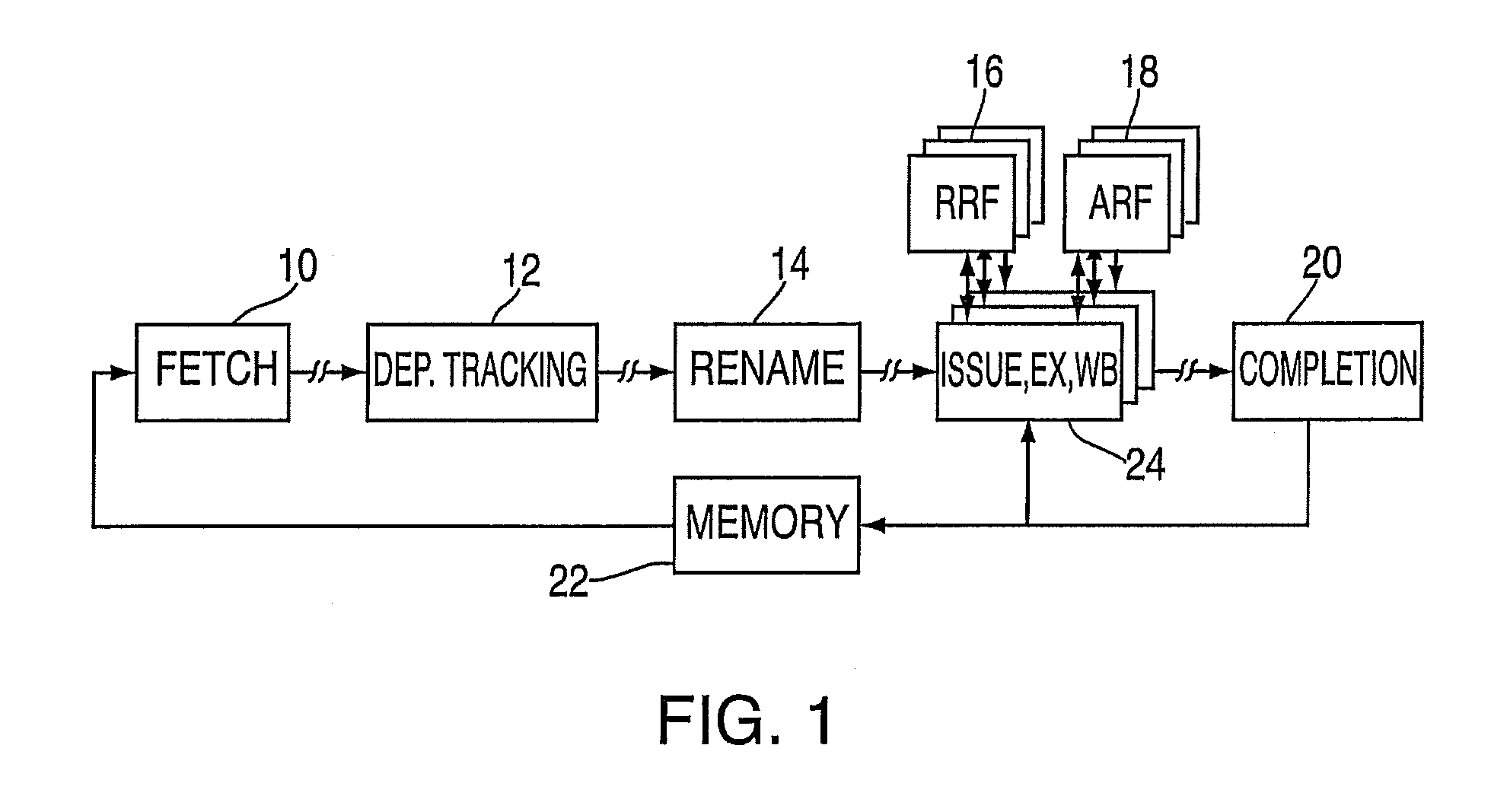

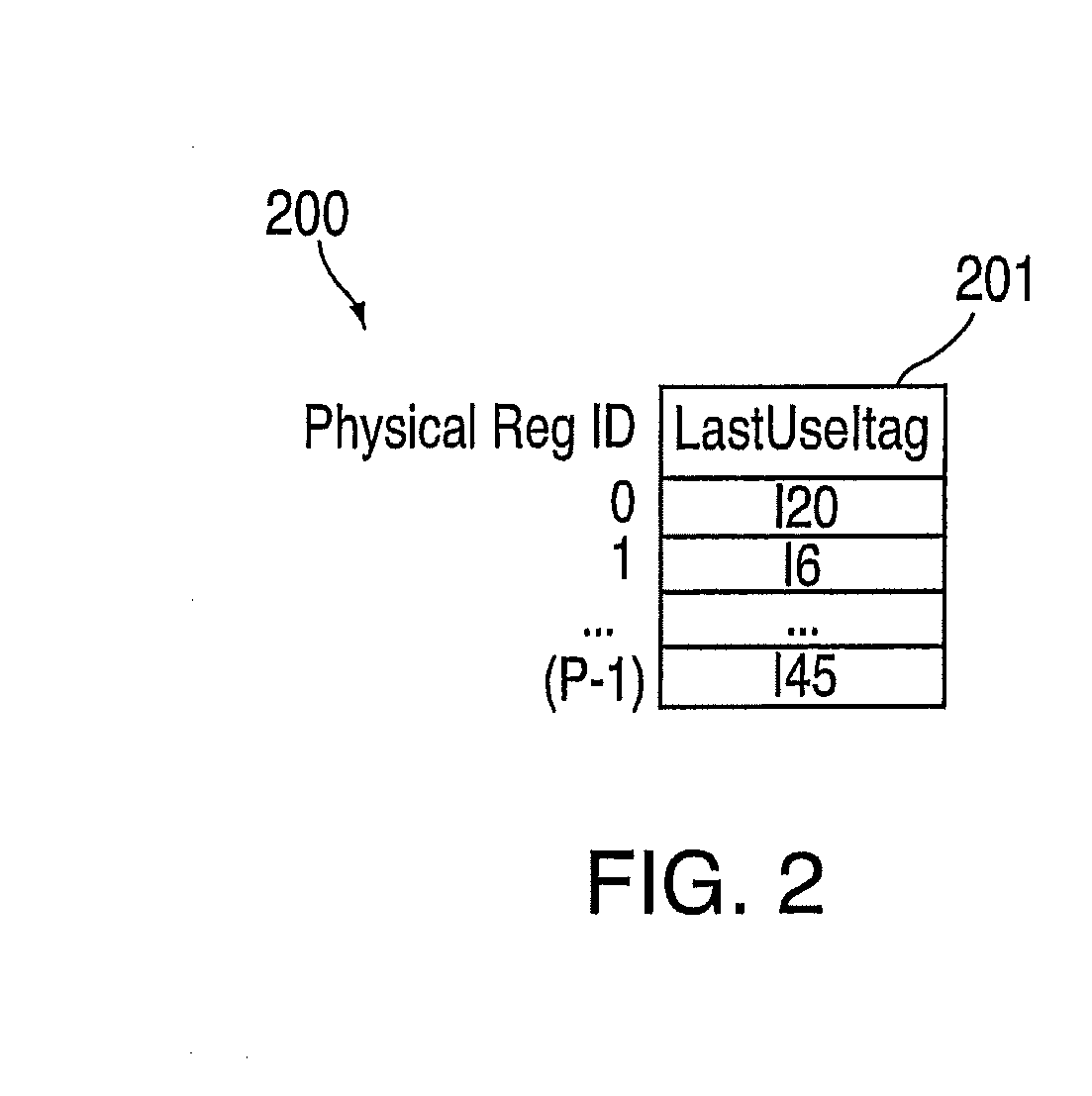

A method for implementing a register renaming scheme for a digital data processor using a plurality of physical register files for supporting out-of-order execution of a plurality of instructions from one or more threads, the method comprising: using a DEF table to store the instruction dependencies between the plurality of instructions using the instruction tags, the DEF table being indexed by a logical register name and including one entry per logical register; using a rename USE table indexed by the instruction tags to store logical-to-physical register mapping information shared by multiple sets of different types of non-architected copies of logical registers used by multiple threads; using a last USE table to transfer data of the multiple sets of different types of non-architected copies of logical registers into the first set of architected registered files, the last USE table being indexed by a physical register name in the second set of rename registered files; and performing the register renaming scheme at the instruction dispatch or wake-up / issue time.

Owner:IBM CORP

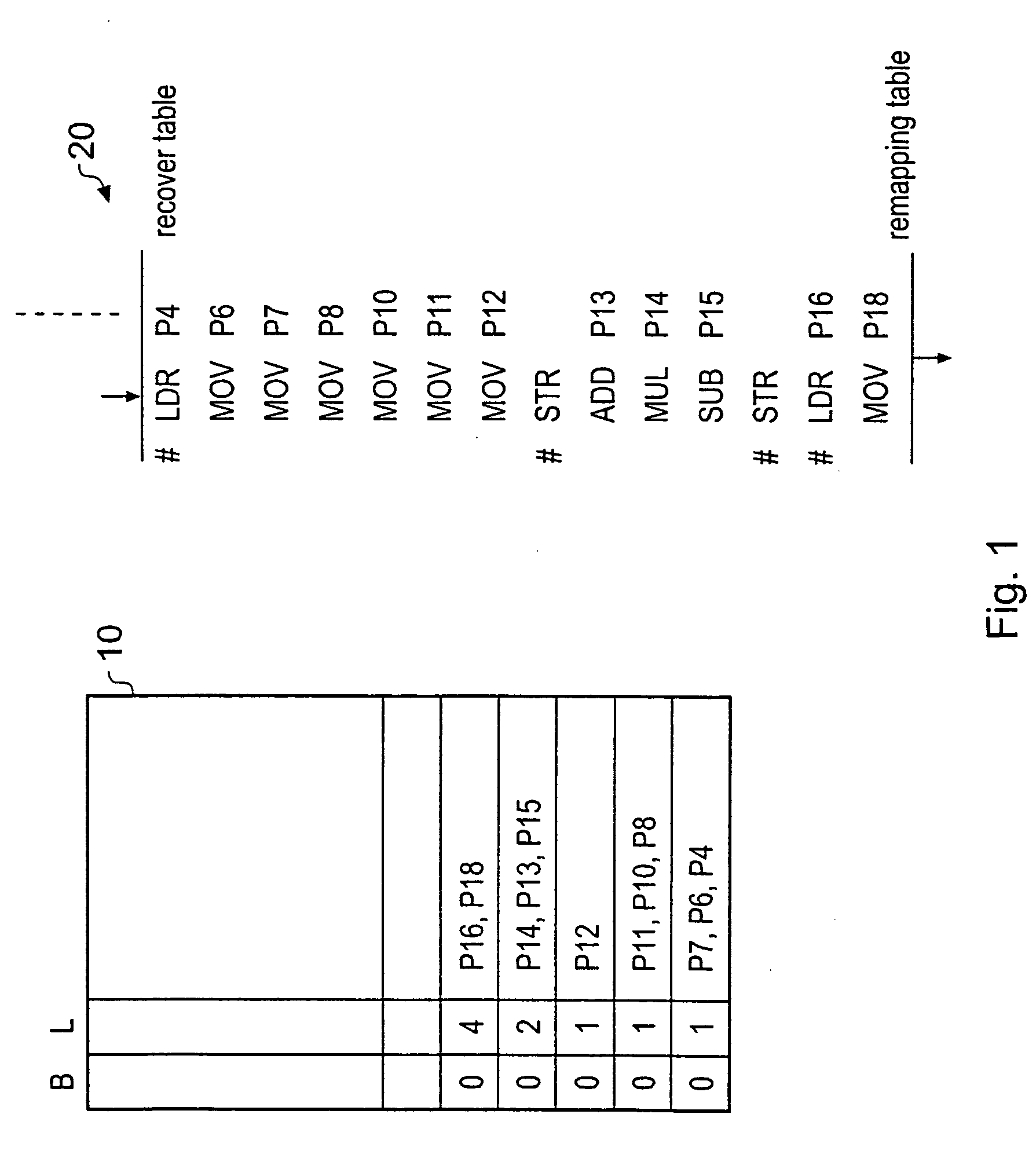

Marking registers as available for register renaming

InactiveUS20080148022A1Fast powerImprove securityDigital computer detailsMemory systemsProcessing InstructionData memory

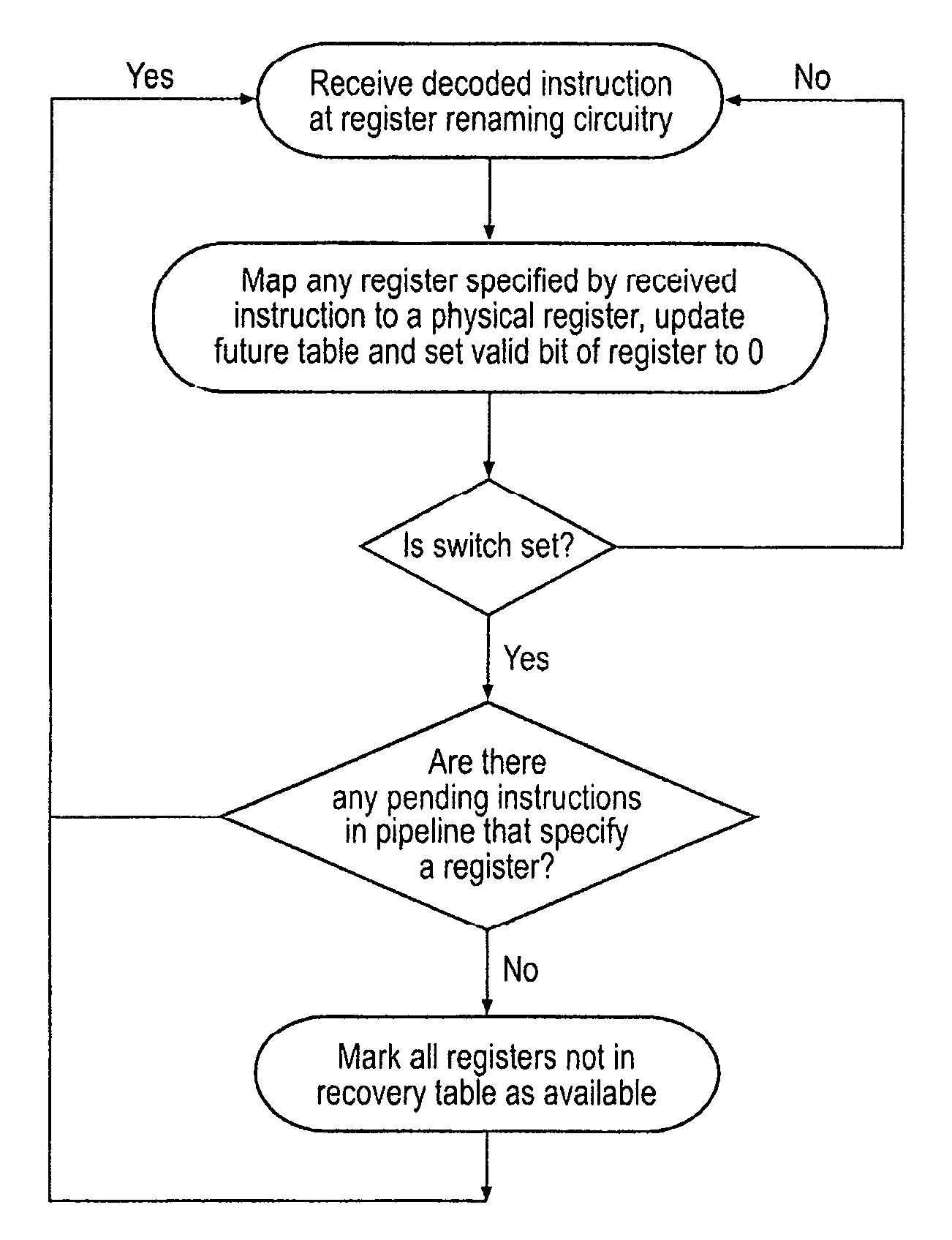

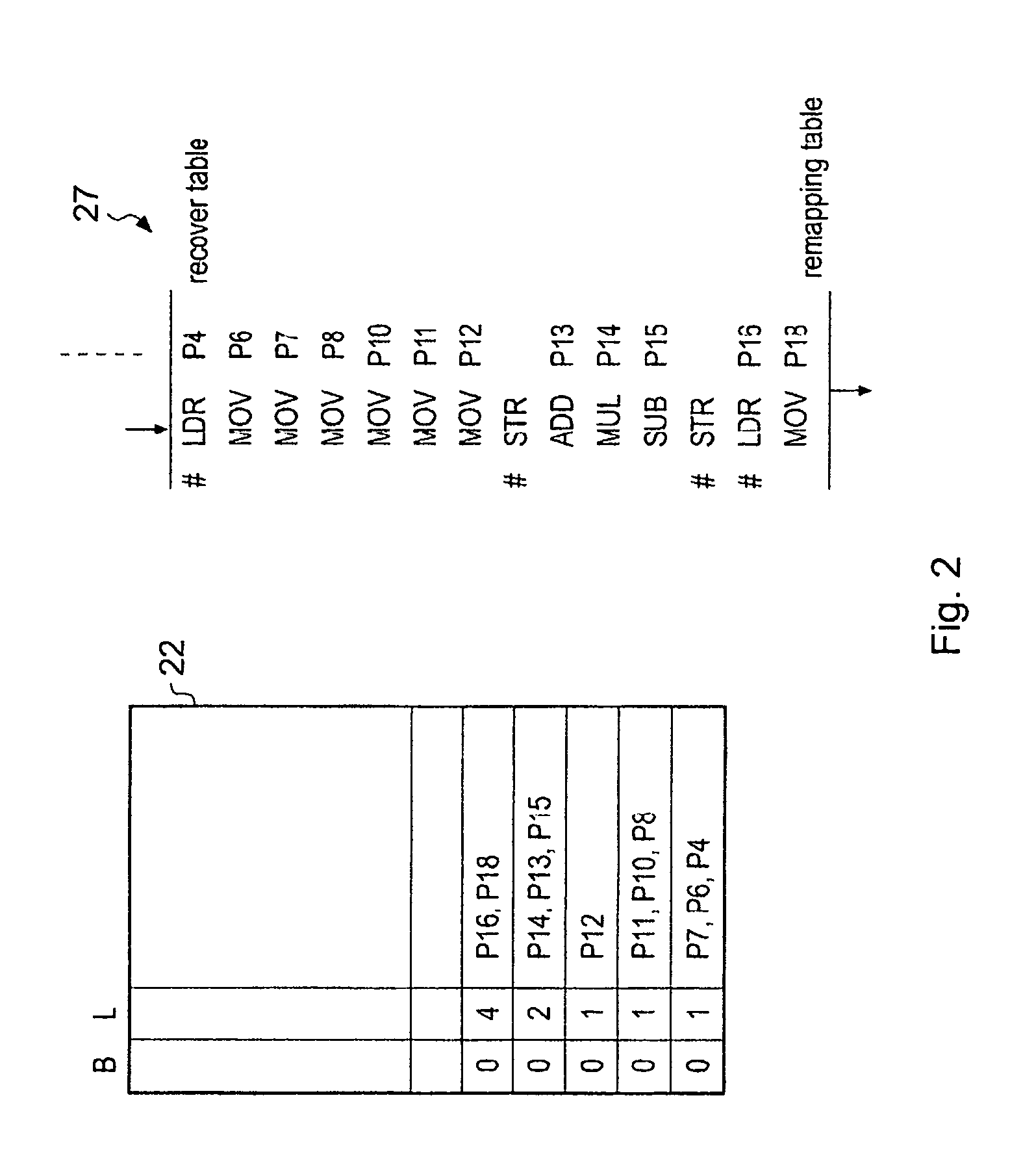

The present application discloses register renaming circuitry for mapping registers from an architectural set of registers to registers within a physical set of registers, said architectural set of registers being registers specified by instructions within an instruction set and said physical set of registers being registers within a processor for processing instructions of said instruction set, said instruction set comprising exception instructions and non-exception instructions, exception instructions being instructions that may generate an exception and non-exception instructions being instructions that execute in a statically determinable way, said register renaming circuitry comprising: a first data store for storing a future renaming table, said future renaming table comprising renaming values for mapping registers from said architectural set of registers to registers in said physical set of registers for instructions that are to be executed or are currently being executed by said processor; a second data store for storing a recovery renaming table, said recovery renaming table comprising a most recently committed mapping of said processor; wherein said register renaming circuitry is responsive to detection of a predetermined condition to mark said physical registers not mapped in said recovery renaming table as available for renaming.

Owner:ARM LTD

Register rename array with individual thread bits set upon allocation and cleared upon instruction completion

InactiveUS7093106B2Digital computer detailsMultiprogramming arrangementsArray data structureParallel computing

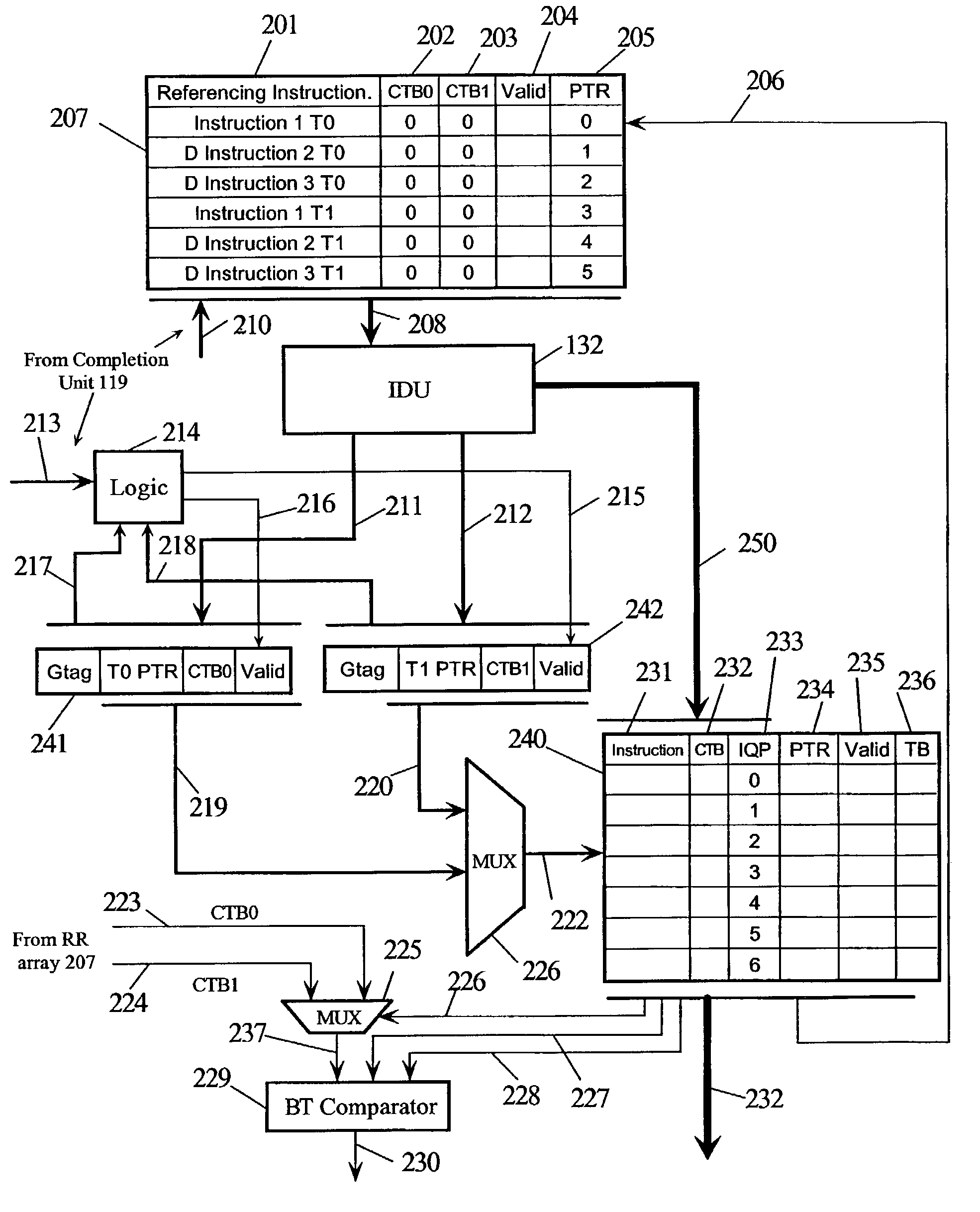

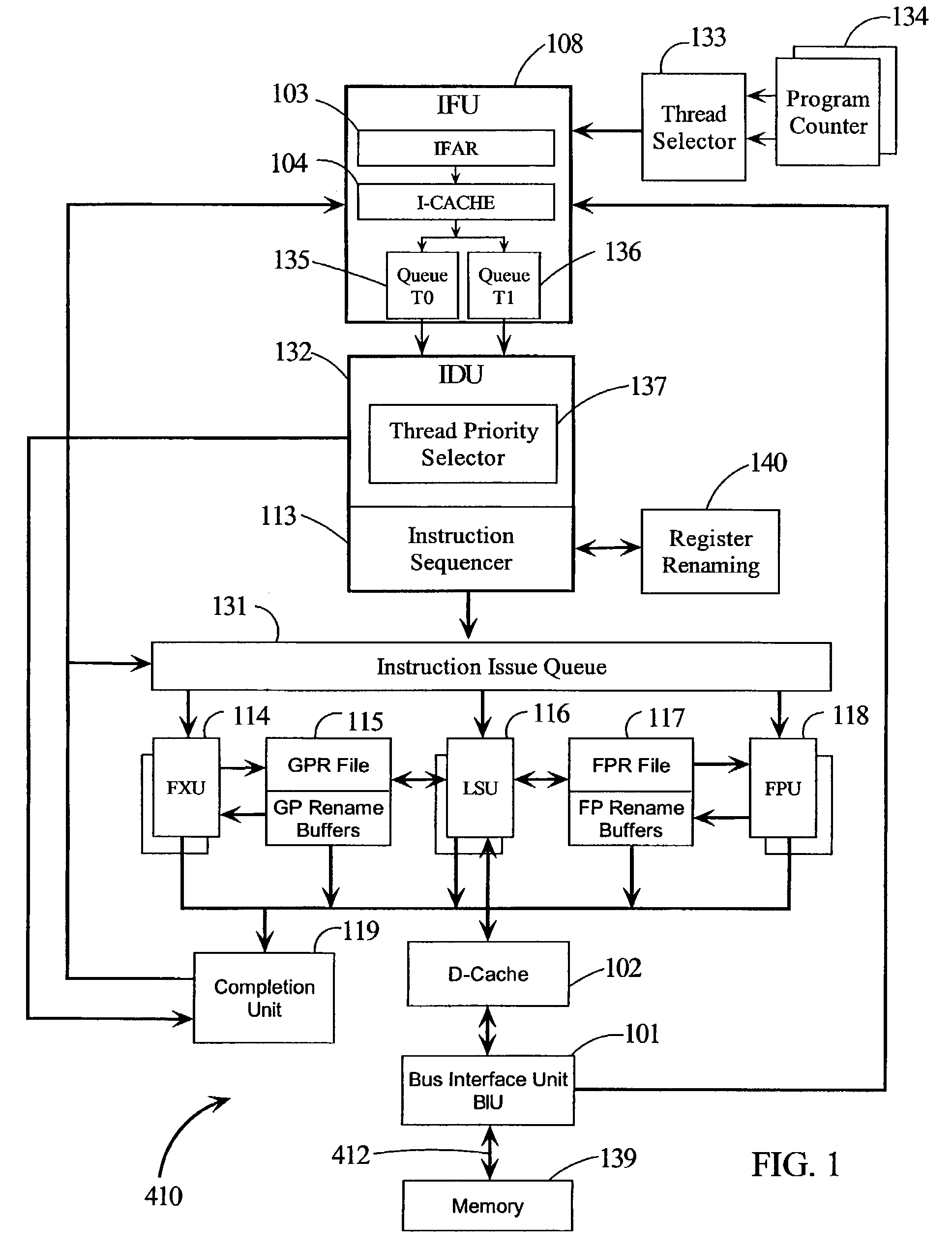

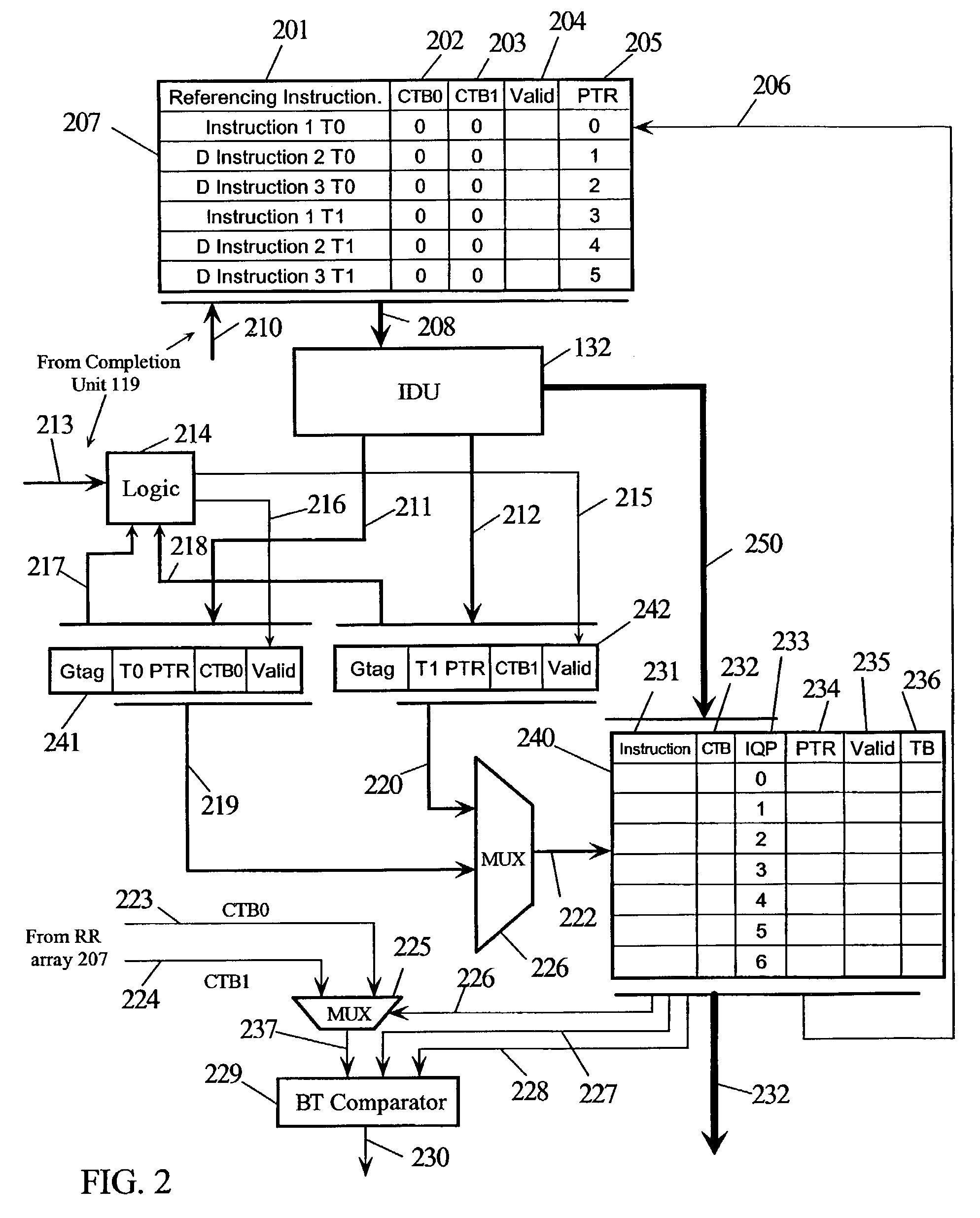

A single rename register array is used in an SMT processor. Two bits are added to each register address of the rename register array, one for bit for thread zero (CTB0) and one bit for thread one (CTB1). The CTB bits are all set to a logic value on power on or start-up. A control instruction (CI) that sets control bits used by other instructions is assigned a register in the rename register array having an address designated as pointer (PTR) address. When a control instruction with an assigned entry with PTR address M completes, then the CTB bit at the PTR address M is flipped to its opposite logic state; likewise, its Valid bit is set to a “not” Valid state. The self resetting CTB bit is used to determine whether an issued instruction sources a register in the rename register array or a corresponding architected register.

Owner:IBM CORP

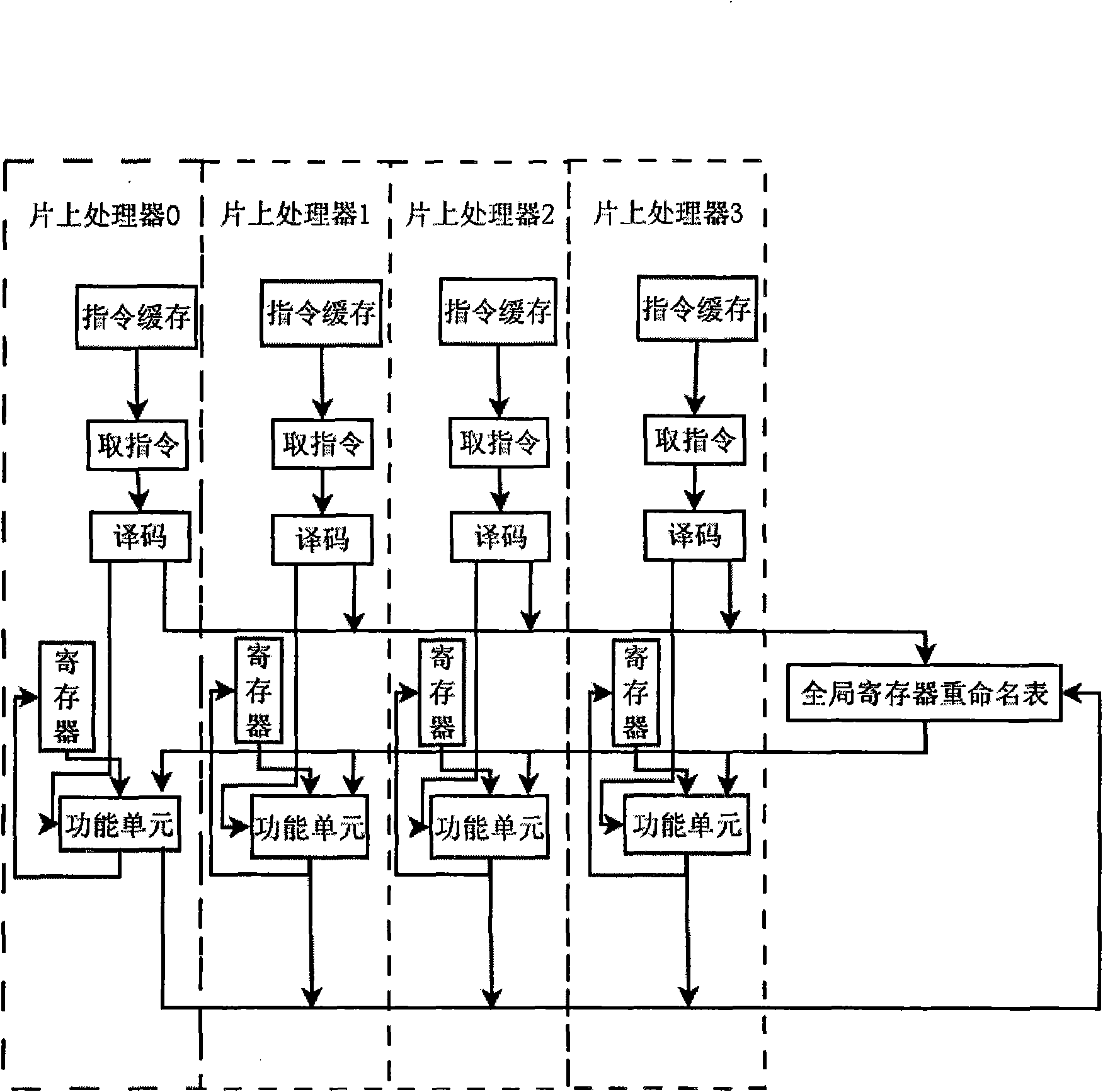

Implementation method of rename table of global register under on-chip multi-processor system framework

InactiveCN101582025AResolve dependenciesReduce trafficConcurrent instruction executionHardware structureProcessing Instruction

The invention relates to the technical field of on-chip multi-processor system structure, aiming at providing an implementation method of a rename table of a global register under on-chip multi-processor system framework. The method comprises the steps: designing the rename table of the global register; processing the dependency relationship 'writing-after-writing' of command; processing the dependency relationship 'writing-after-reading' of command; acquiring operand; writing back results; and submitting the command. As the rename table of the global register is used by the method, the dependency relationship of the commands of different processors can be recorded, and the dependency of 'writing-after-reading' and 'writing-after-writing' can be solved; the operand of the commands of the different processors can be maintained and transmitted through the rename table of the global register, so that the internuclear communication volume can be reduced; as hardware configuration used by the rename table of the global register is a logical table, the structure is simple, the complexity of hardware is low, the area of the rename table of the global register is only 1% of that of one on-chip processor, and tiny area cost is caused.

Owner:ZHEJIANG UNIV

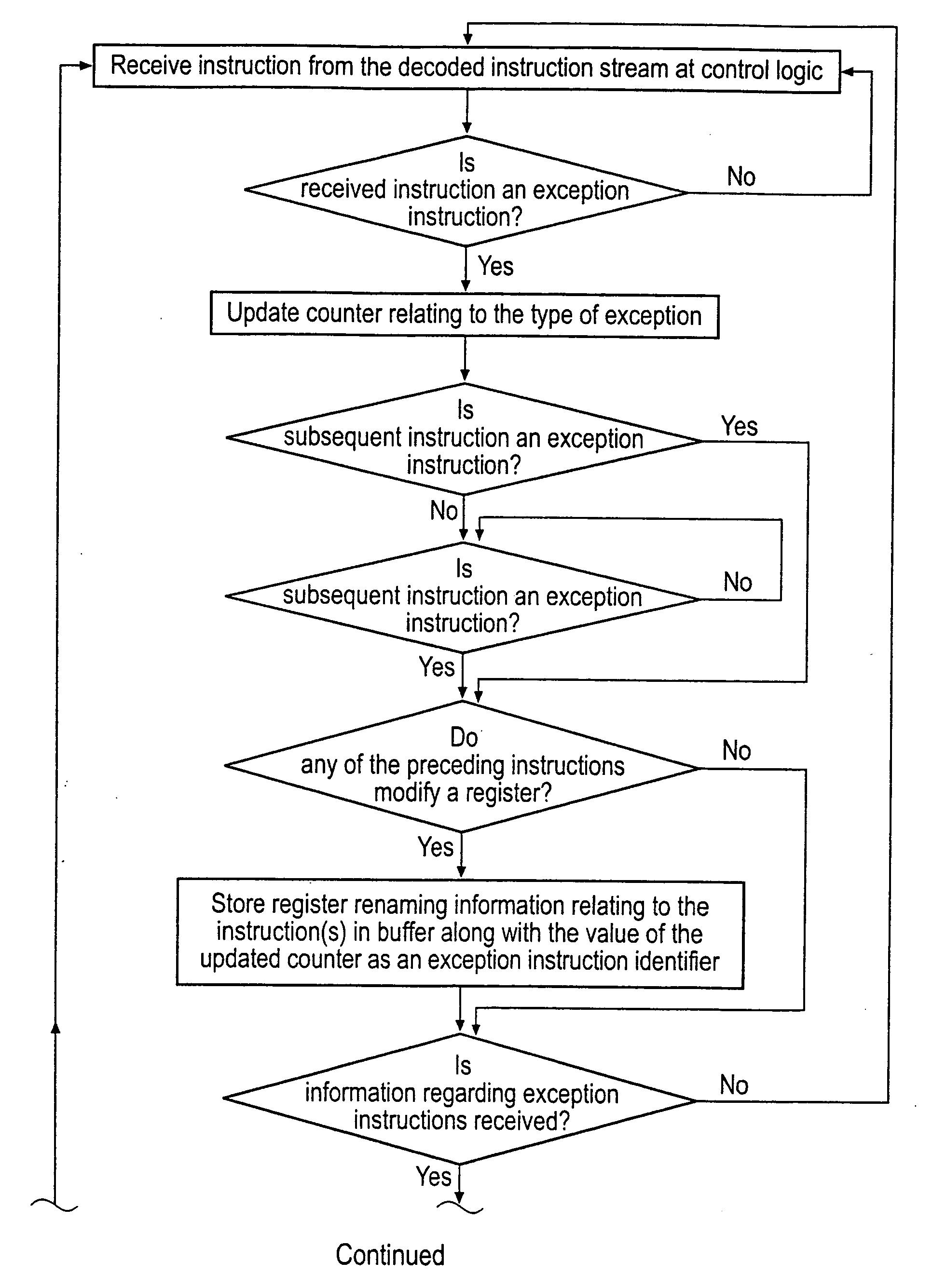

Restoring a register renaming table within a processor following an exception

InactiveUS20080077782A1Simple processEasy to controlInstruction analysisDigital computer detailsData valueControl logic

Control logic for storing values relating to unresolved exception instructions within a buffer to enable a register renaming table within a processor to be restored following an exception is disclosed. The processor is operable to process a stream of instructions from an instruction set, the instruction set comprising exception instructions and non-exception instructions, exception instructions being instructions that may generate an exception and non-exception instructions being instructions that execute in a statically determinable way. The processor comprises a physical set of registers operable to store data values being processed by the processor; and register renaming logic operable to receive a stream of decoded instructions and to map for each decoded instruction within the stream of decoded instructions, registers from an architectural set of registers associated with the instruction set to registers within the physical set of registers in dependence upon renaming values stored in the register renaming table; the control logic comprising a buffer and being operable: to identify exception and non-exception instructions within the decoded instruction stream and to group any non-exception instructions with a closest preceding exception instruction; to store in the buffer, register renaming values relating to any registers whose data values are modified by the group of instructions and which are renamed by the register renaming logic as a bundle of register renaming values associated with the exception instruction.

Owner:ARM LTD

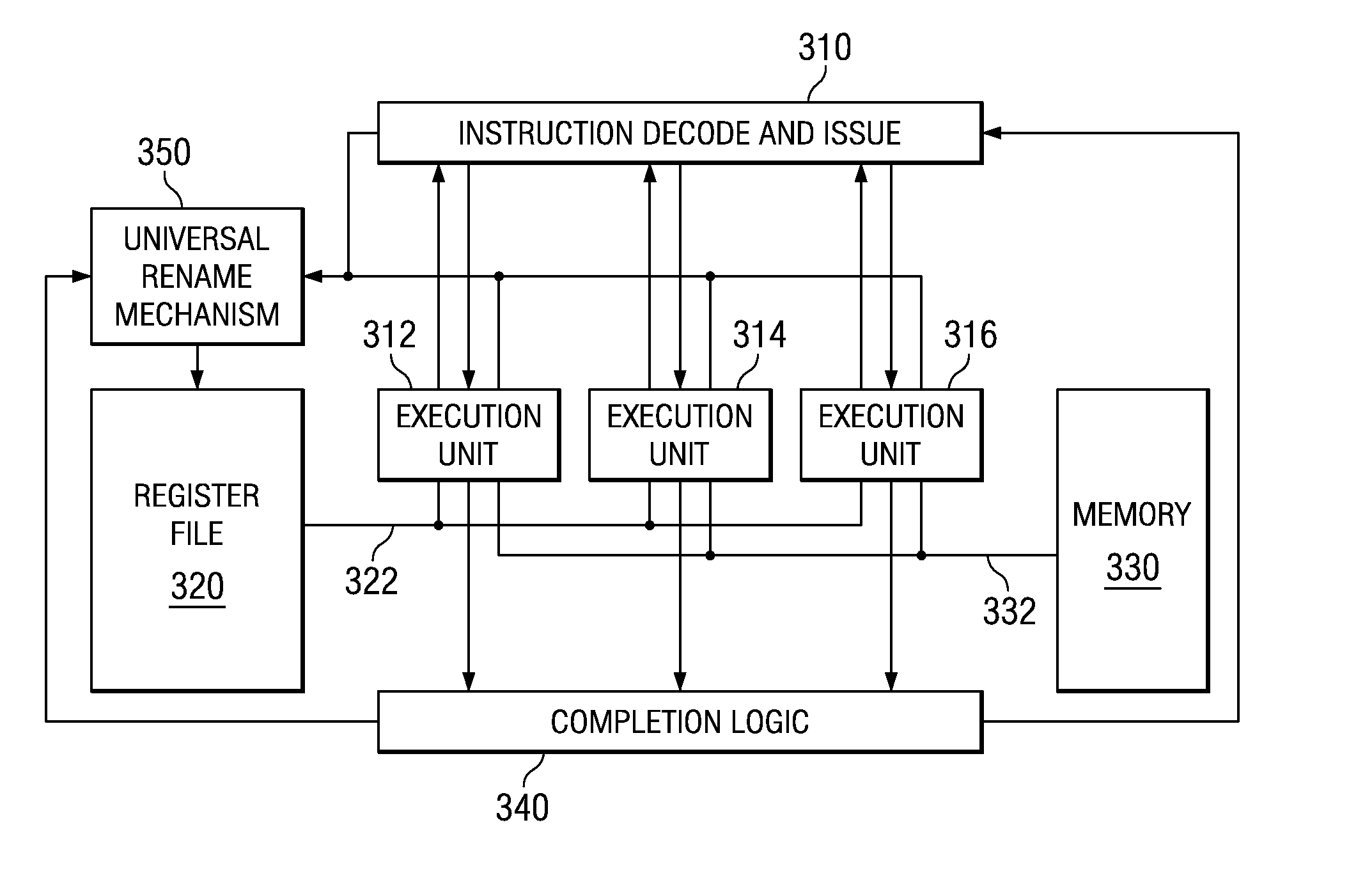

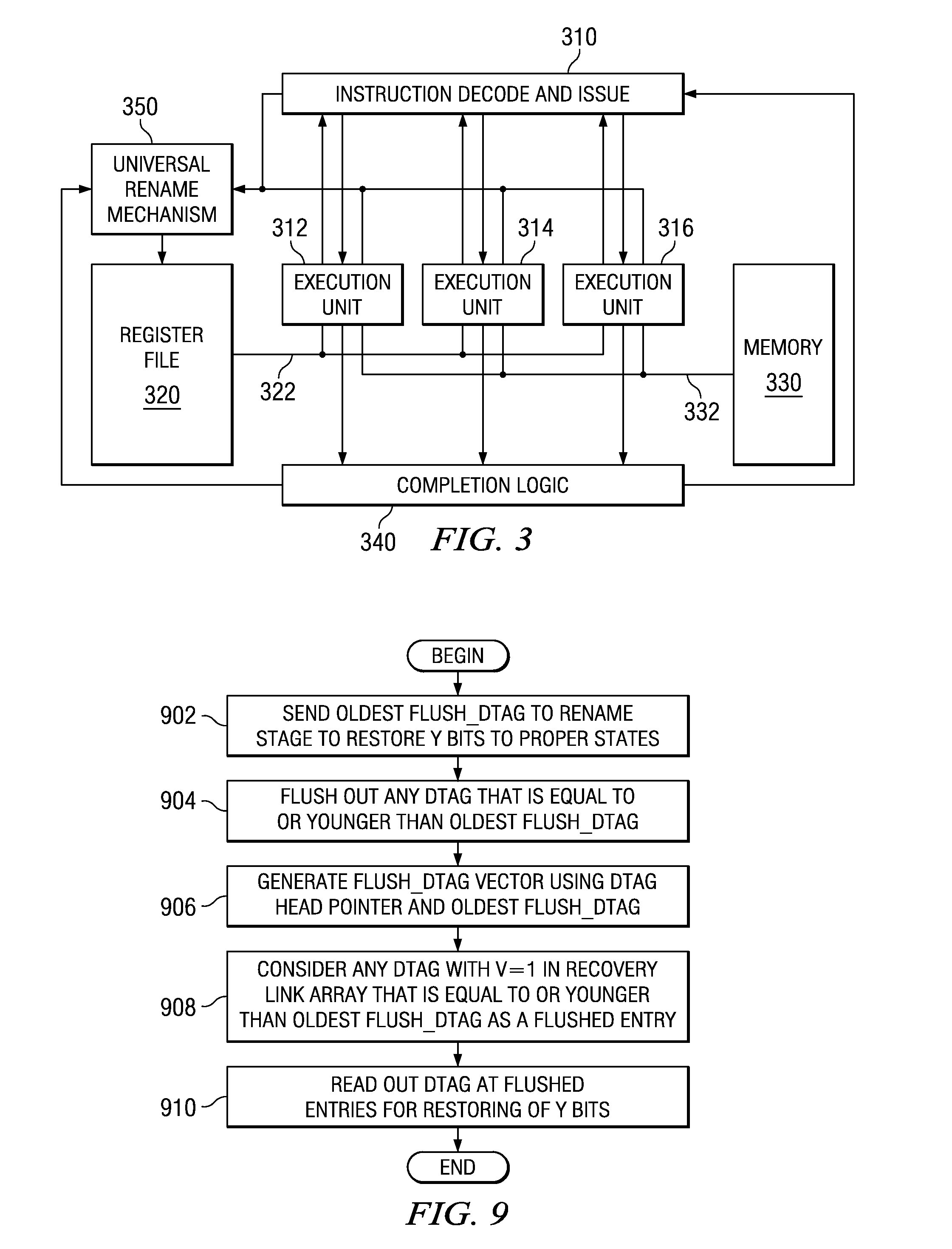

Universal Register Rename Mechanism for Targets of Different Instruction Types in a Microprocessor

InactiveUS20080263321A1Increase powerGeneral purpose stored program computerProgram controlGeneral purposeParallel computing

A unified register rename mechanism for targets of different instruction types is provided in a microprocessor. The universal rename mechanism renames destinations of different instruction types using a single rename structure. Thus, an instruction that is updating a floating point register (FPR) can be renamed along with an instruction that is updating a general purpose register (GPR) or vector multimedia extensions (VMX) instructions register (VR) using the same rename structure because the number of architected states for GPR is the same as the number of architected states for FPR and VR. Each destination tag (DTAG) is assigned to one destination. A floating point instruction may be assigned to a DTAG, and then a fixed point instruction may be assigned to the next DTAG and so forth. With a universal rename mechanism, significant silicon and power can be saved by having only one rename structure for all instruction types.

Owner:IBM CORP

Zero cycle load

ActiveUS20130339671A1Reduce loading operationsEffective latencyProgram control using stored programsDigital computer detailsLoad instructionOperand

A system and method for reducing the latency of load operations. A register rename unit within a processor determines whether a decoded load instruction is eligible for conversion to a zero-cycle load operation. If so, control logic assigns a physical register identifier associated with a source operand of an older dependent store instruction to the destination operand of the load instruction. Additionally, the register rename unit marks the load instruction to prevent it from reading data associated with the source operand of the store instruction from memory. Due to the duplicate renaming, this data may be forwarded from a physical register file to instructions that are younger and dependent on the load instruction.

Owner:APPLE INC

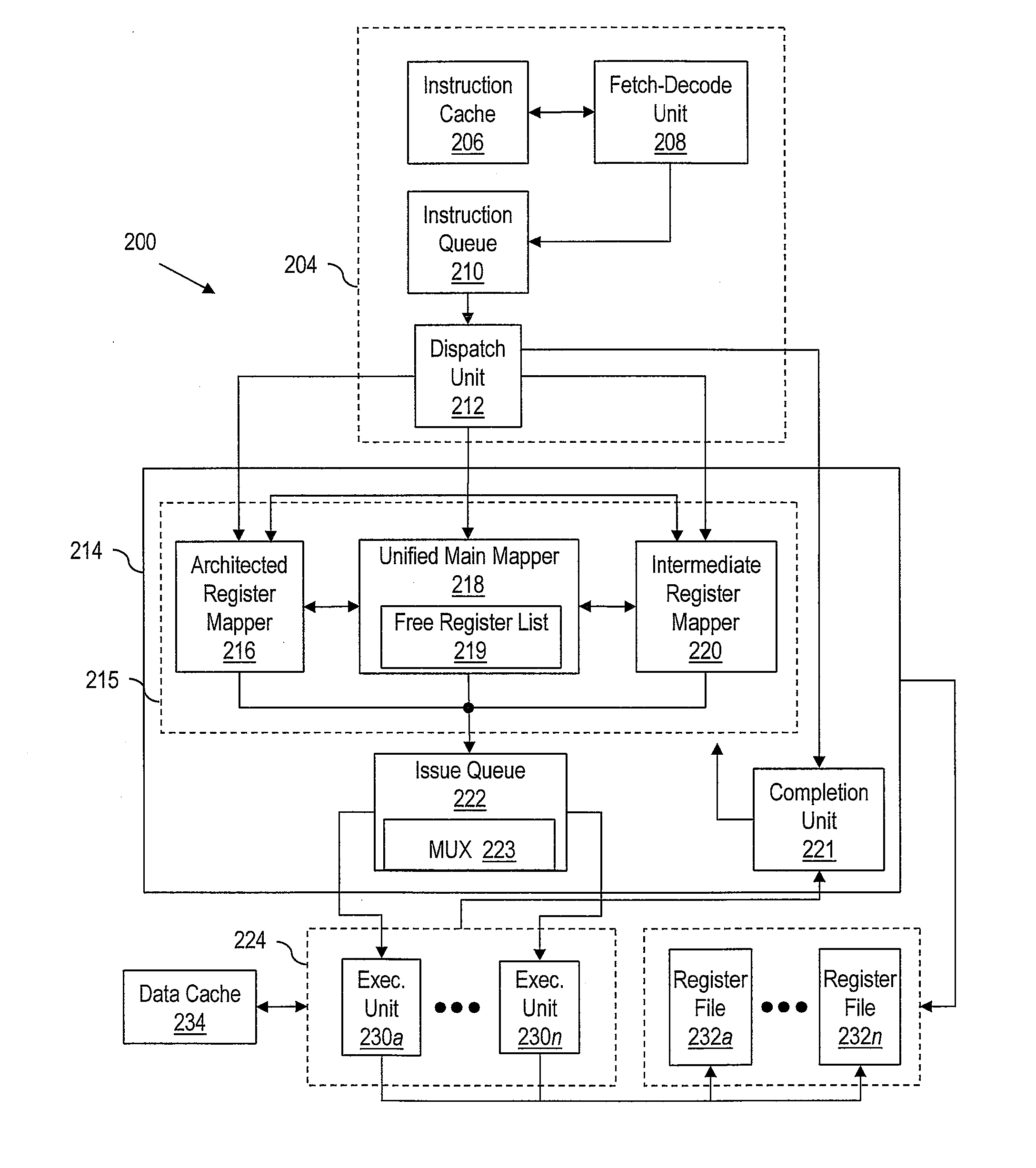

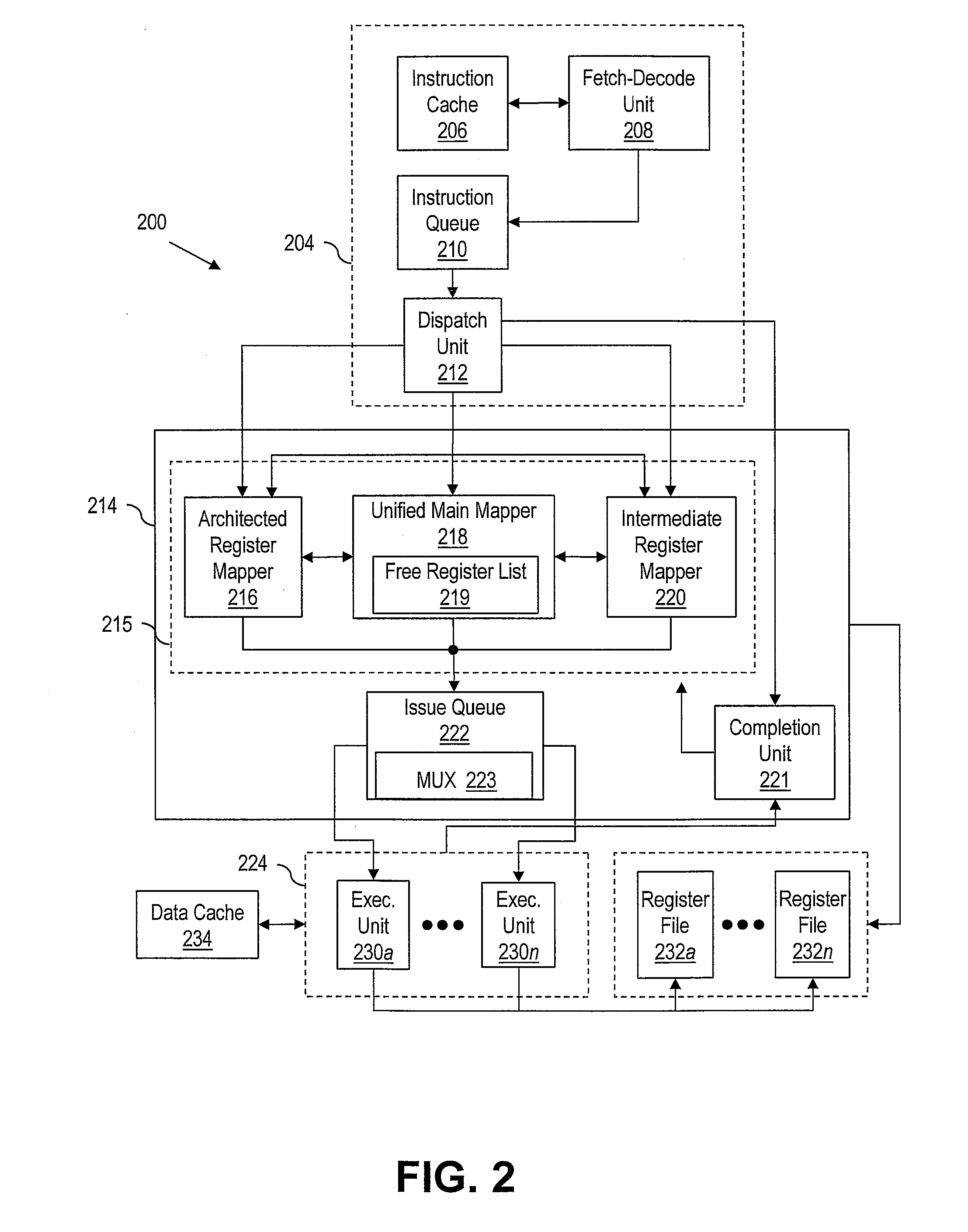

Intermediate Register Mapper

InactiveUS20110087865A1Increase the number ofDigital computer detailsSpecific program execution arrangementsParallel computingComputer program

A method, processor, and computer program product employing an intermediate register mapper within a register renaming mechanism. A logical register lookup determines whether a hit to a logical register associated with the dispatched instruction has occurred. In this regard, the logical register lookup searches within at least one register mapper from a group of register mappers, including an architected register mapper, a unified main mapper, and an intermediate register mapper. A single hit to the logical register is selected among the group of register mappers. If an instruction having a mapper entry in the unified main mapper has finished but has not completed, the mapping contents of the register mapper entry in the unified main mapper are moved to the intermediate register mapper, and the unified register mapper entry is released, thus increasing a number of unified main mapper entries available for reuse.

Owner:IBM CORP

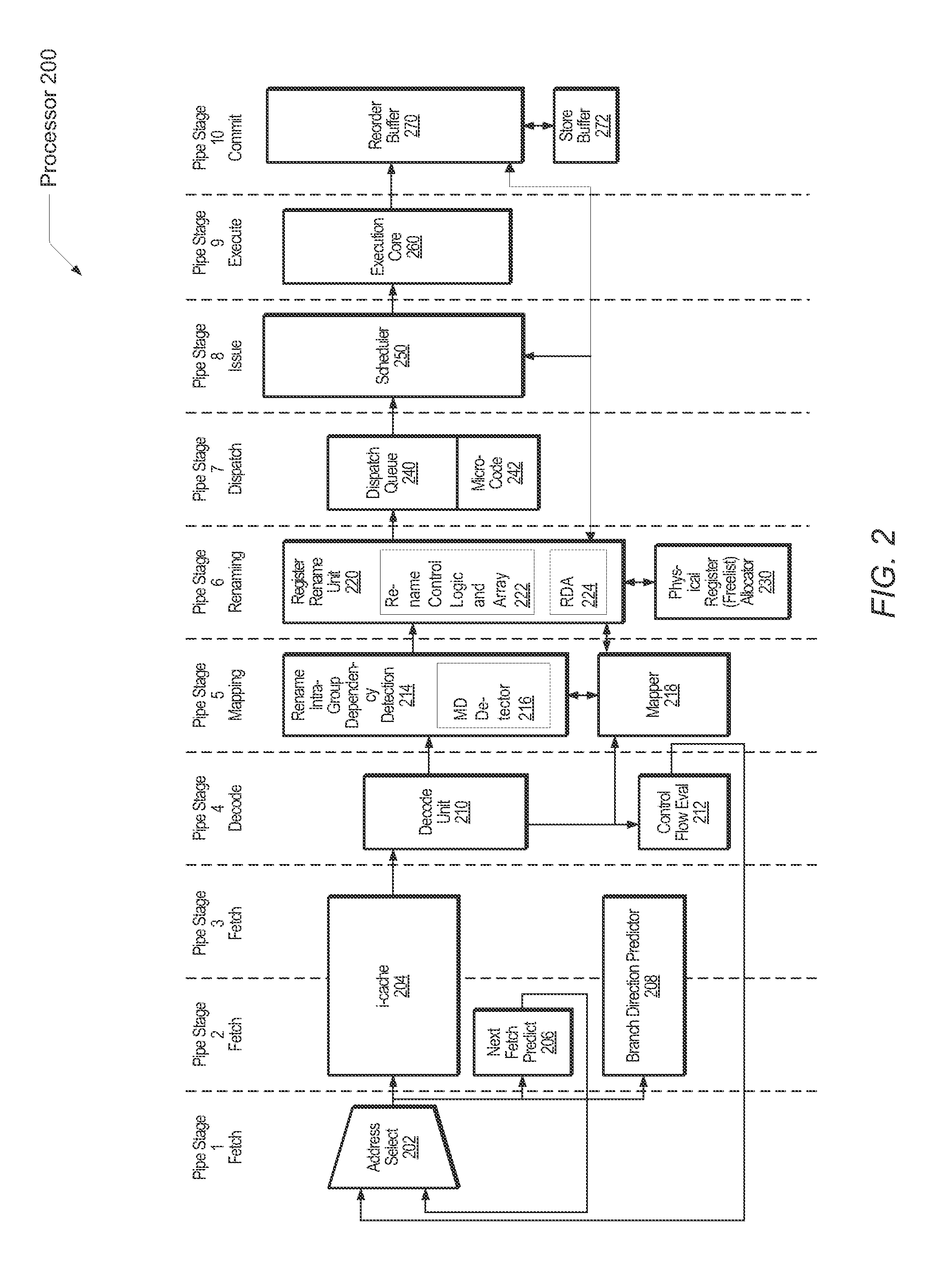

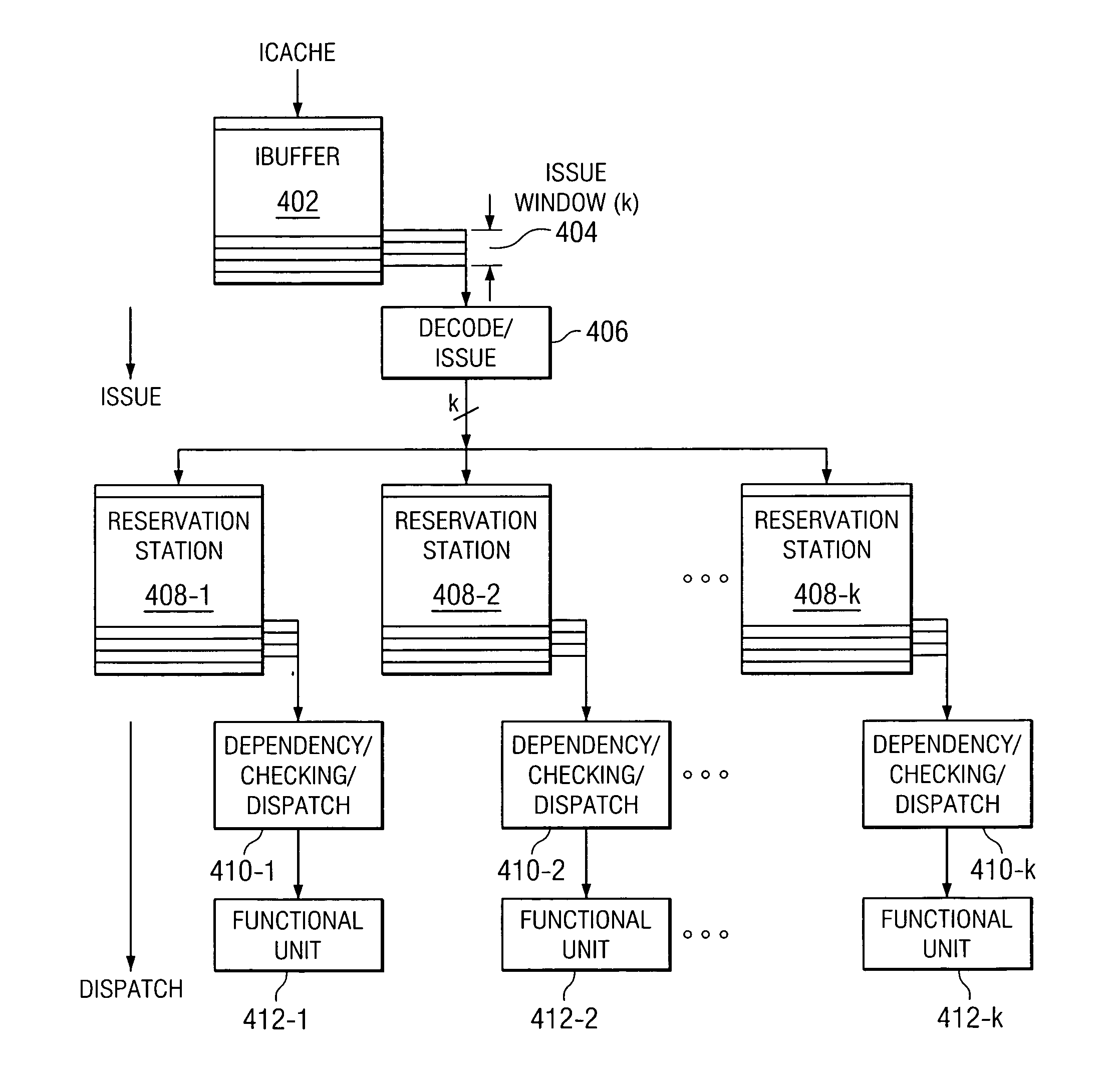

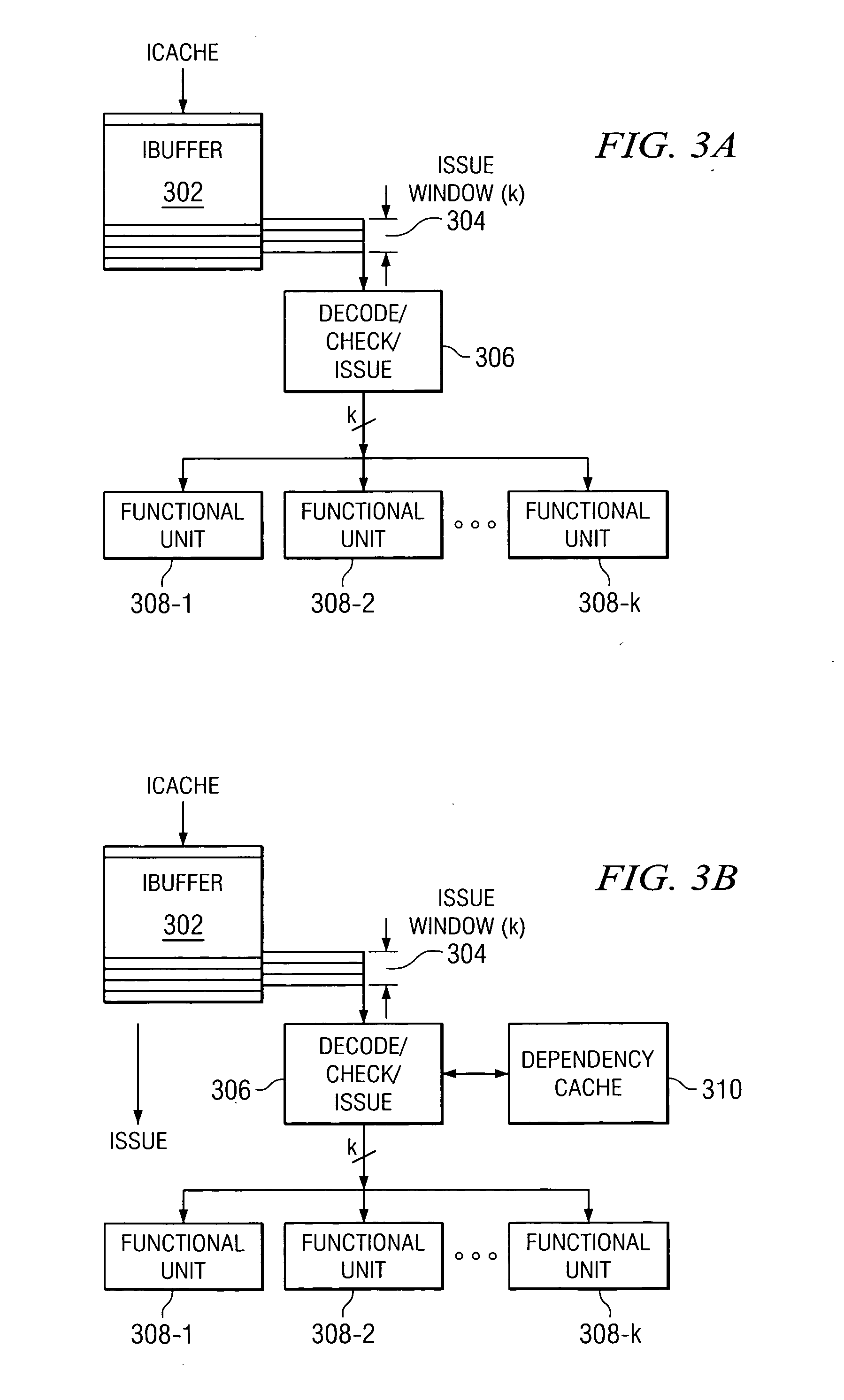

Method and apparatus for control signals memoization in a multiple instruction issue microprocessor

InactiveUS20060155965A1Save overheadDigital computer detailsMemory systemsControl vectorControl signal

A dynamic predictive and / or exact caching mechanism is provided in various stages of a microprocessor pipeline so that various control signals can be stored and memorized in the course of program execution. Exact control signal vector caching may be done. Whenever an issue group is formed following instruction decode, register renaming, and dependency checking, an encoded copy of the issue group information can be cached under the tag of the leading instruction. The resulting dependency cache or control vector cache can be accessed right at the beginning of the instruction issue logic stage of the microprocessor pipeline the next time the corresponding group of instructions come up for re-execution. Since the encoded issue group bit pattern may be accessed in a single cycle out of the cache, the resulting microprocessor pipeline with this embodiment can be seen as two parallel pipes, where the shorter pipe is followed if there is a dependency cache or control vector cache hit.

Owner:IBM CORP

Register renaming system and method for managing and renaming registers

InactiveCN102566976AEasy to determineProcessing speedConcurrent instruction executionComputer architectureTime cost

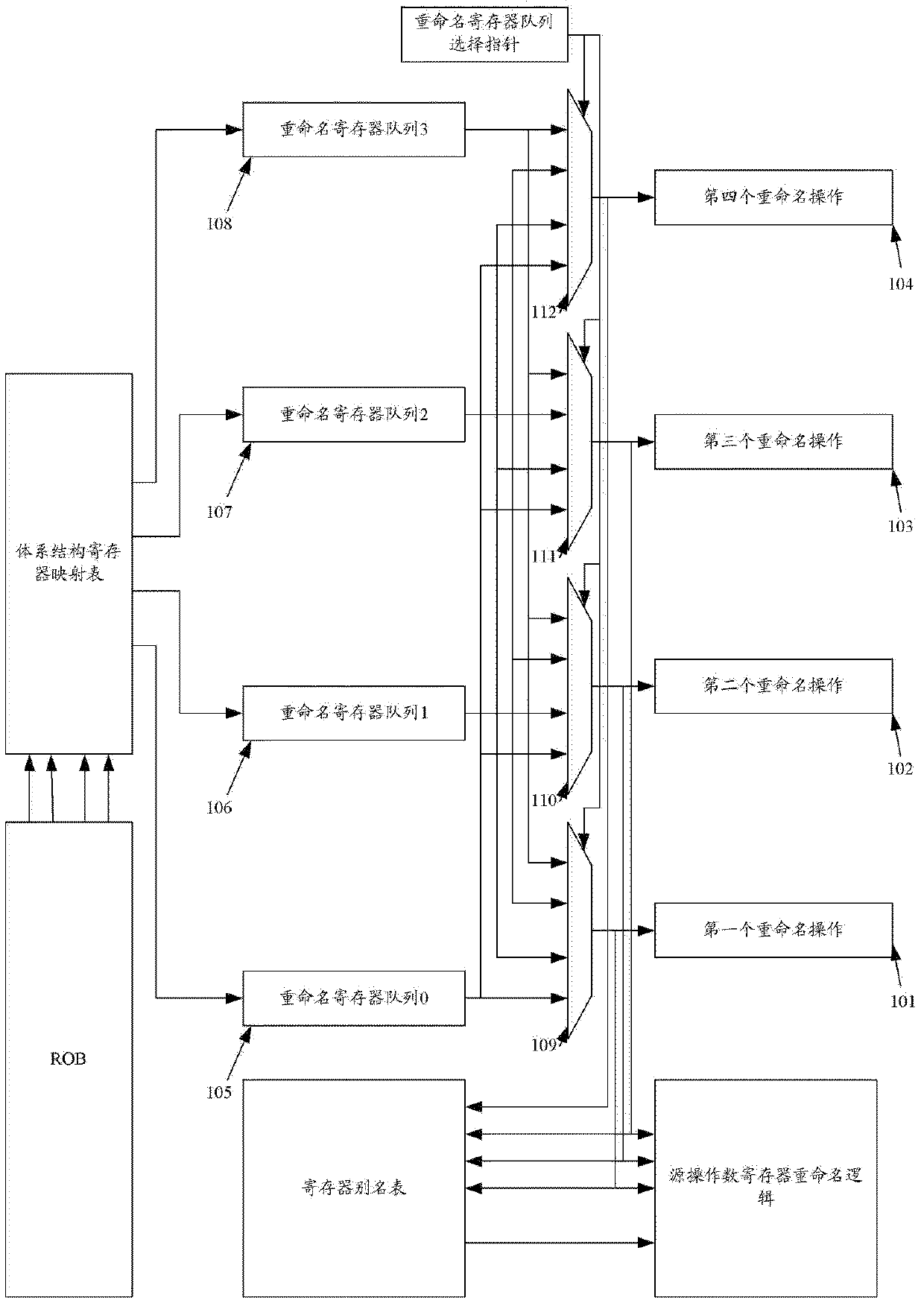

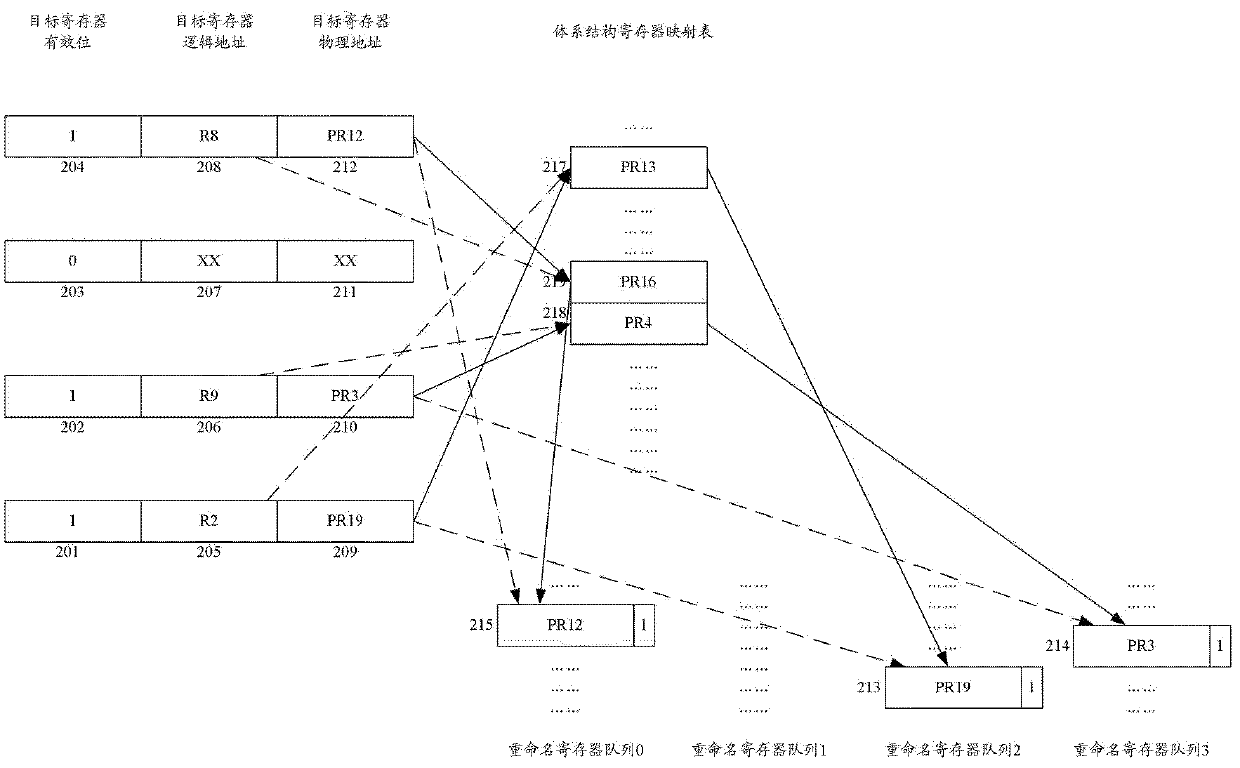

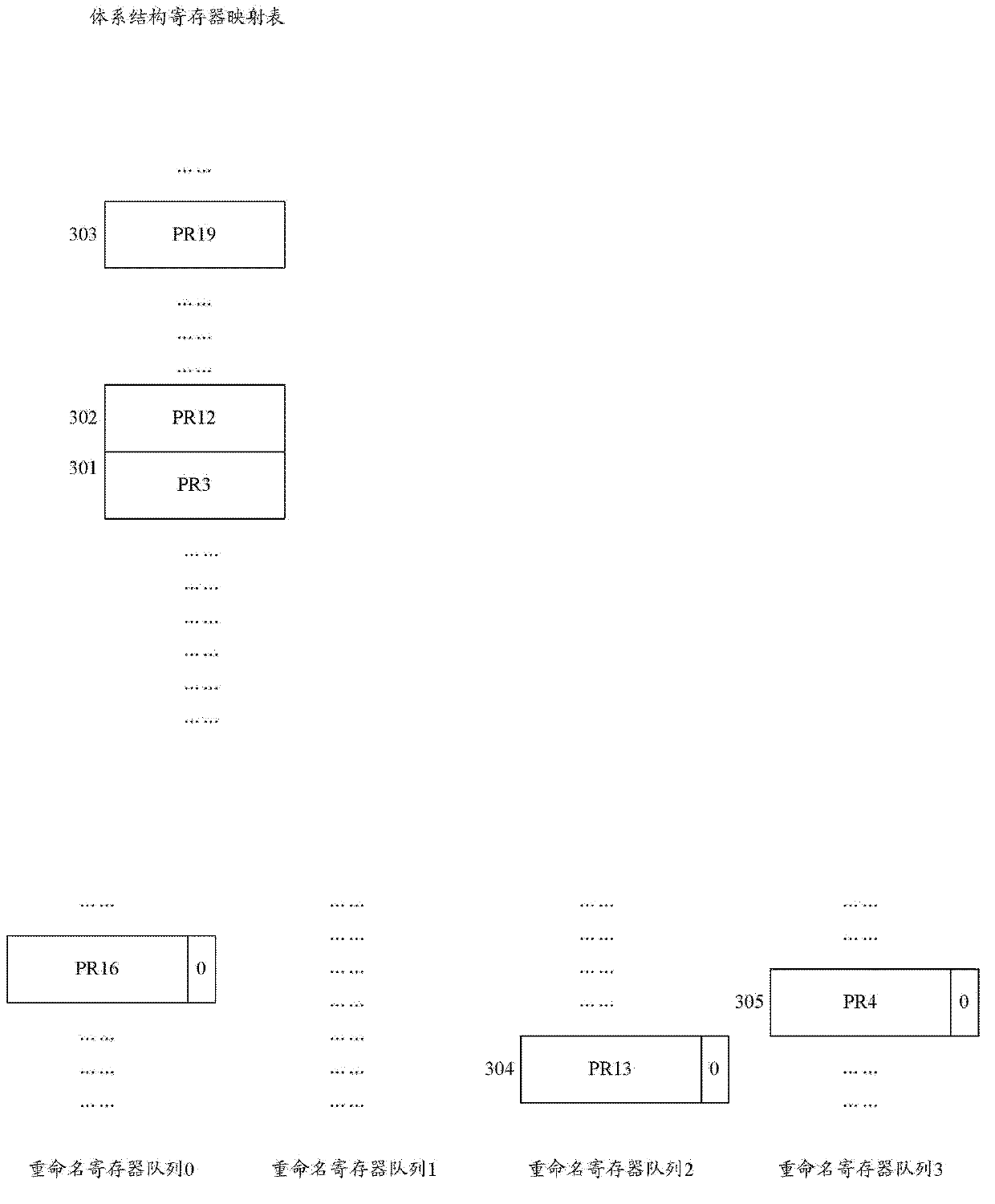

The invention relates to a register renaming system and method for managing and renaming registers. The invention specifically provides the register renaming system for managing and renaming the registers by adopting multiple renamed register queues, and the system comprises a physical register group, a register alias table (RAT), an architecture register mapping table (ARMT), a select finger of the renamed register queues, a decoder, a logic register renaming device, an RAT modifying device and an updating device of the renamed register queues. In addition, the invention further provides the method for managing and renaming the registers by adopting the multiple renamed register queues. According to the technical scheme provided by the invention, renaming operation can be simultaneously performed on the multiple registers within a same period, the implementation method is simple, the time cost is small, and the register renaming system and method are suitable for superscalar microprocessors with higher transmission width.

Owner:北京国睿中数科技股份有限公司

Zero cycle move

ActiveUS20130275720A1Reduce data latencyLower latencyDigital computer detailsMemory systemsOperandControl logic

A system and method for reducing the latency of data move operations. A register rename unit within a processor determines whether a decoded move instruction is eligible for a zero cycle move operation. If so, control logic assigns a physical register identifier associated with a source operand of the move instruction to the destination operand of the move instruction. Additionally, the register rename unit marks the given move instruction to prevent it from proceeding in the processor pipeline. Further maintenance of the particular physical register identifier may be done by the register rename unit during commit of the given move instruction.

Owner:APPLE INC

Method And Apparatus For Register Renaming Using Multiple Physical Register Files And Avoiding Associative Search

A method for implementing a register renaming scheme for a digital data processor using a plurality of physical register files for supporting out-of-order execution of a plurality of instructions from one or more threads, the method comprising: using a DEF table to store the instruction dependencies between the plurality of instructions using the instruction tags, the DEF table being indexed by a logical register name and including one entry per logical register; using a rename USE table indexed by the instruction tags to store logical-to-physical register mapping information shared by multiple sets of different types of non-architected copies of logical registers used by multiple threads; using a last USE table to transfer data of the multiple sets of different types of non-architected copies of logical registers into the first set of architected registered files, the last USE table being indexed by a physical register name in the second set of rename registered files; and performing the register renaming scheme at the instruction dispatch or wake-up / issue time.

Owner:INT BUSINESS MASCH CORP

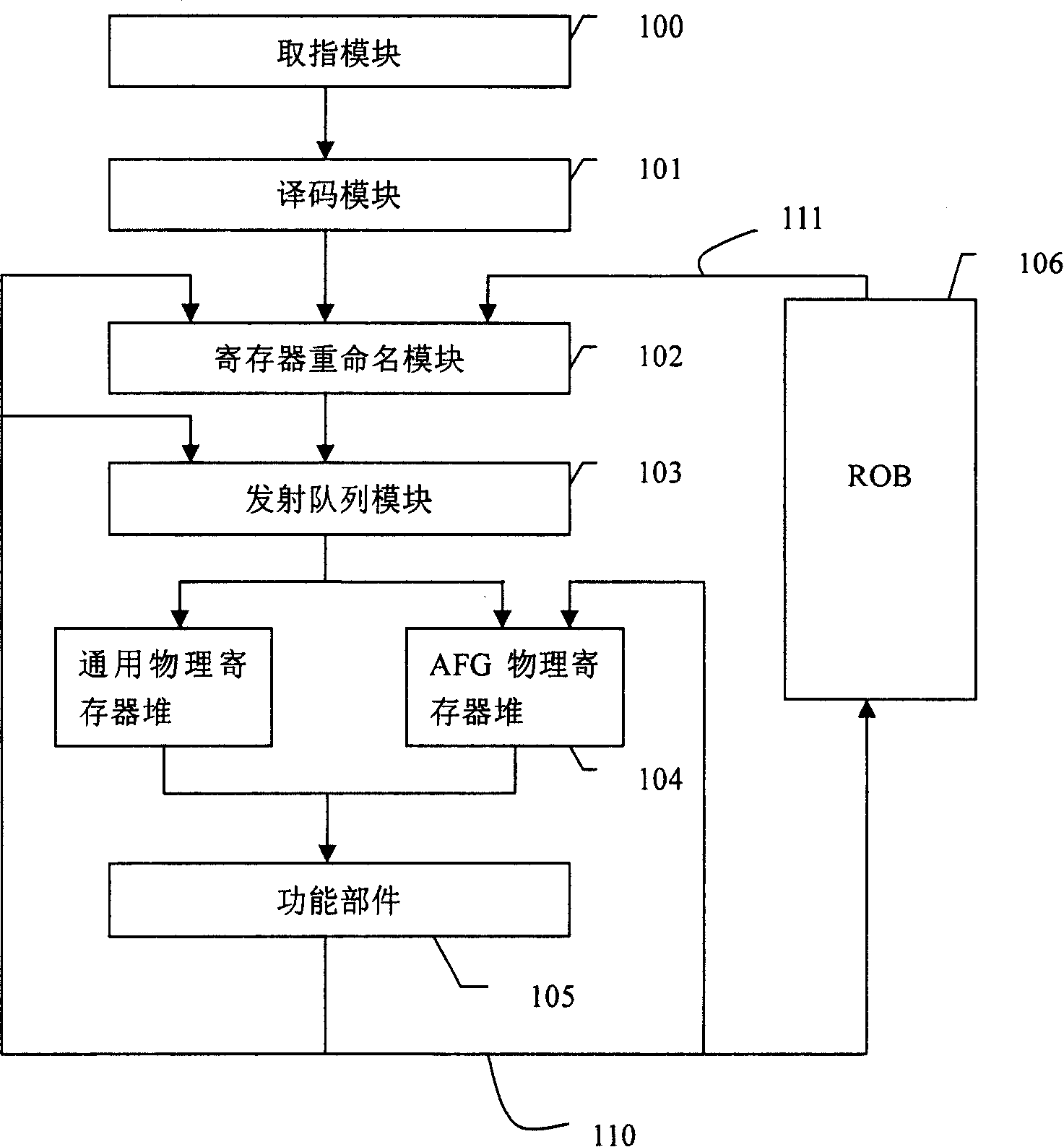

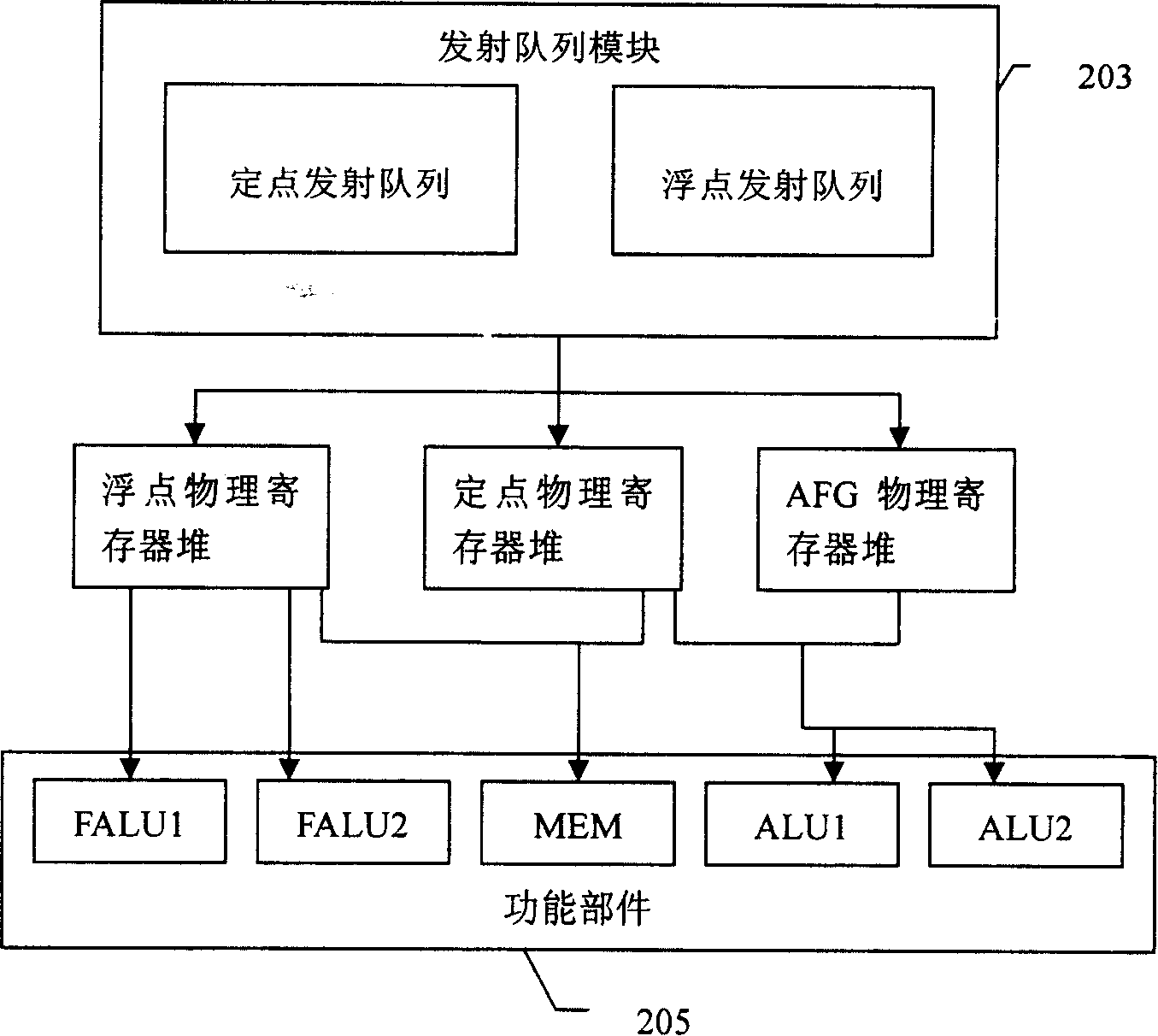

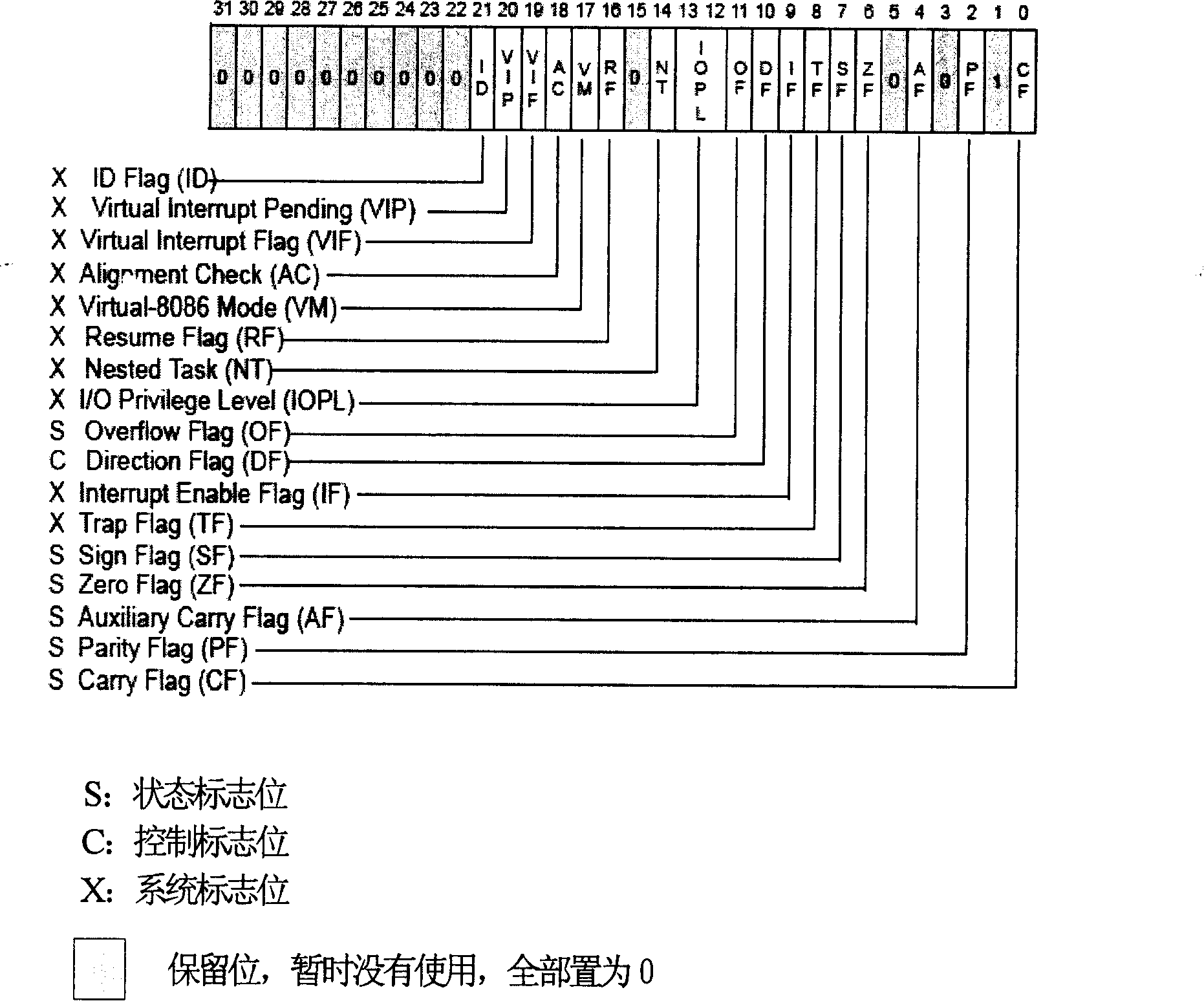

Method for renaming state register and processor using the method

ActiveCN101169710AReduce pauseReduce congestionConcurrent instruction executionComputer scienceFLAGS register

The invention provides a method for renaming a status register in a superscalar processor with a pipeline structure, wherein the status register is a register composed of a plurality of flag bits selected from all flag bits of a flag register. The method comprises determining whether a microcode will read the status register when the microcode coded by a command reaches a register renaming module of the processor; if determining that the microcode will read the status register, allocating a nearest mapping physical register for the status register; otherwise, not allocating the physical register for the status register; determining whether the microcode will be written to the status register; if determining that the microcode will be written into the status register, allocating a new physical register with empty status to the status register; and otherwise, not allocating the physical register for the status register.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

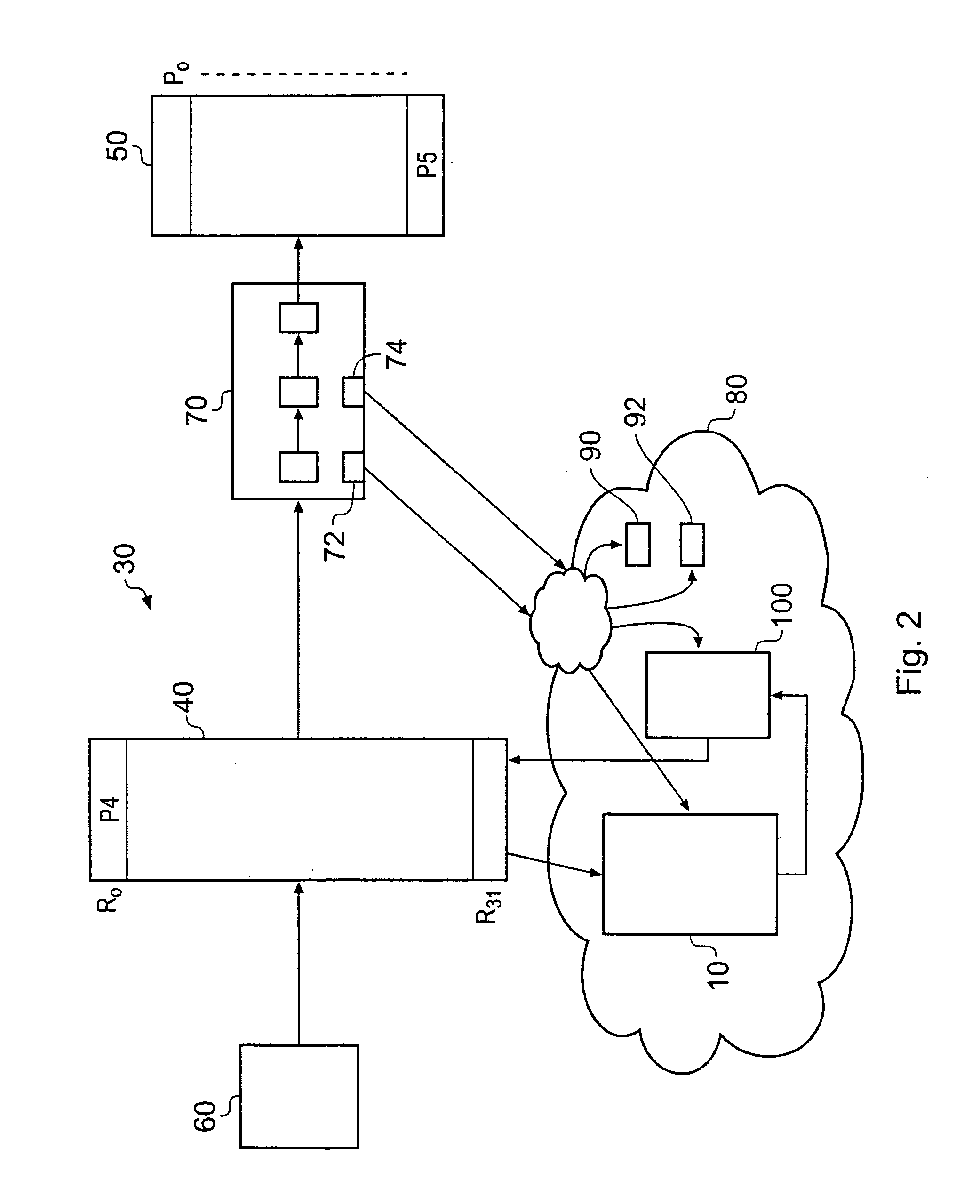

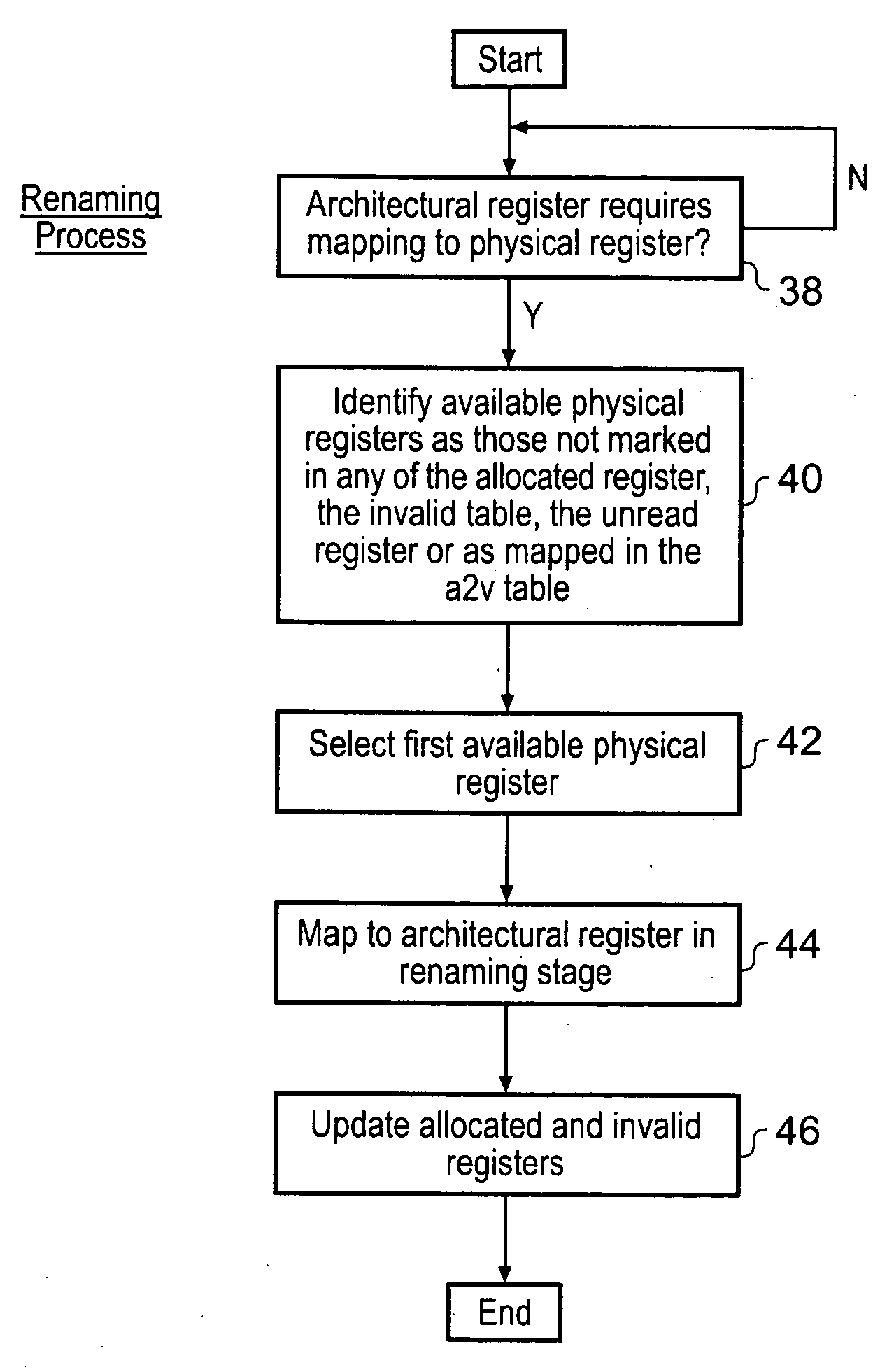

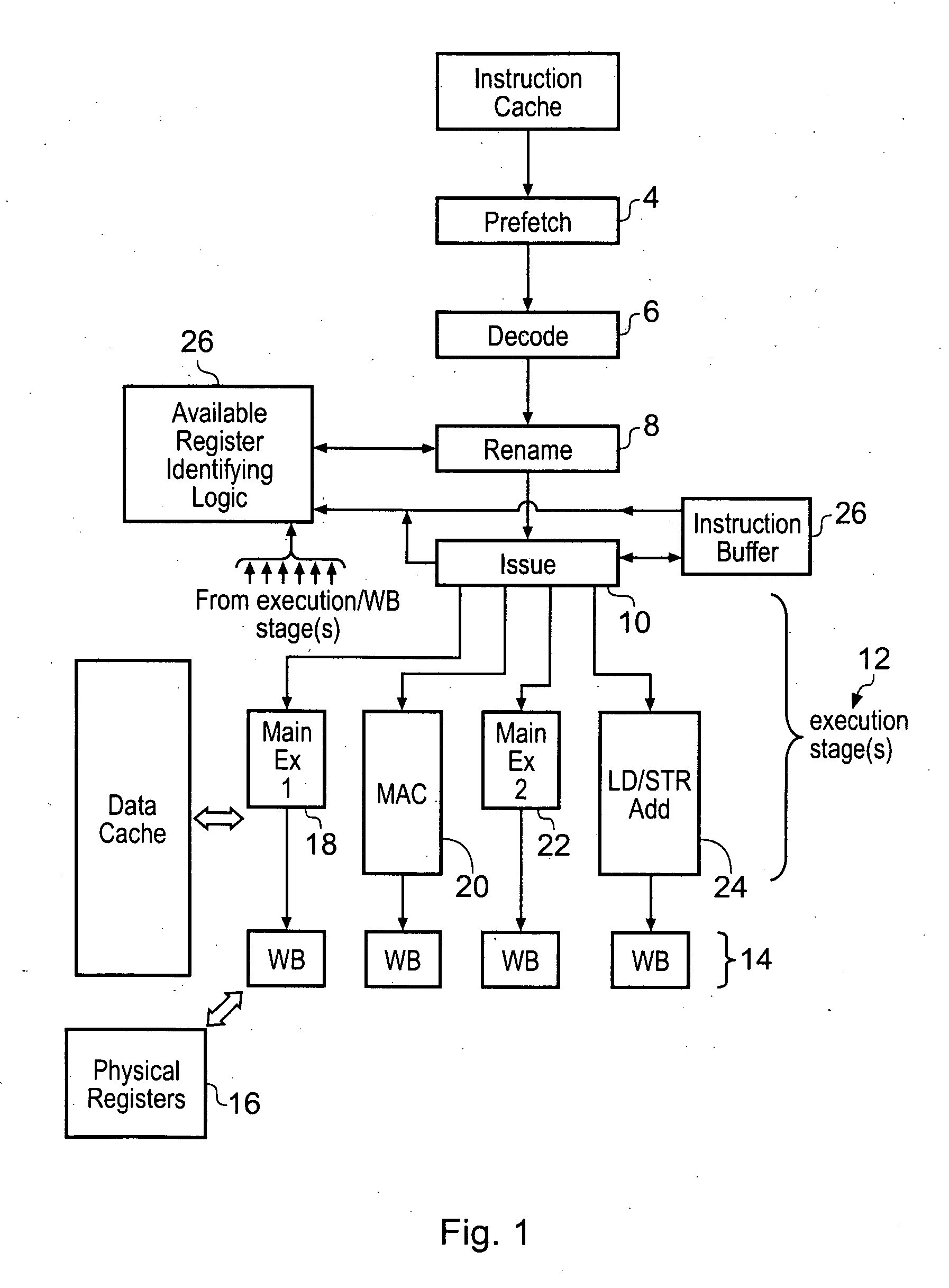

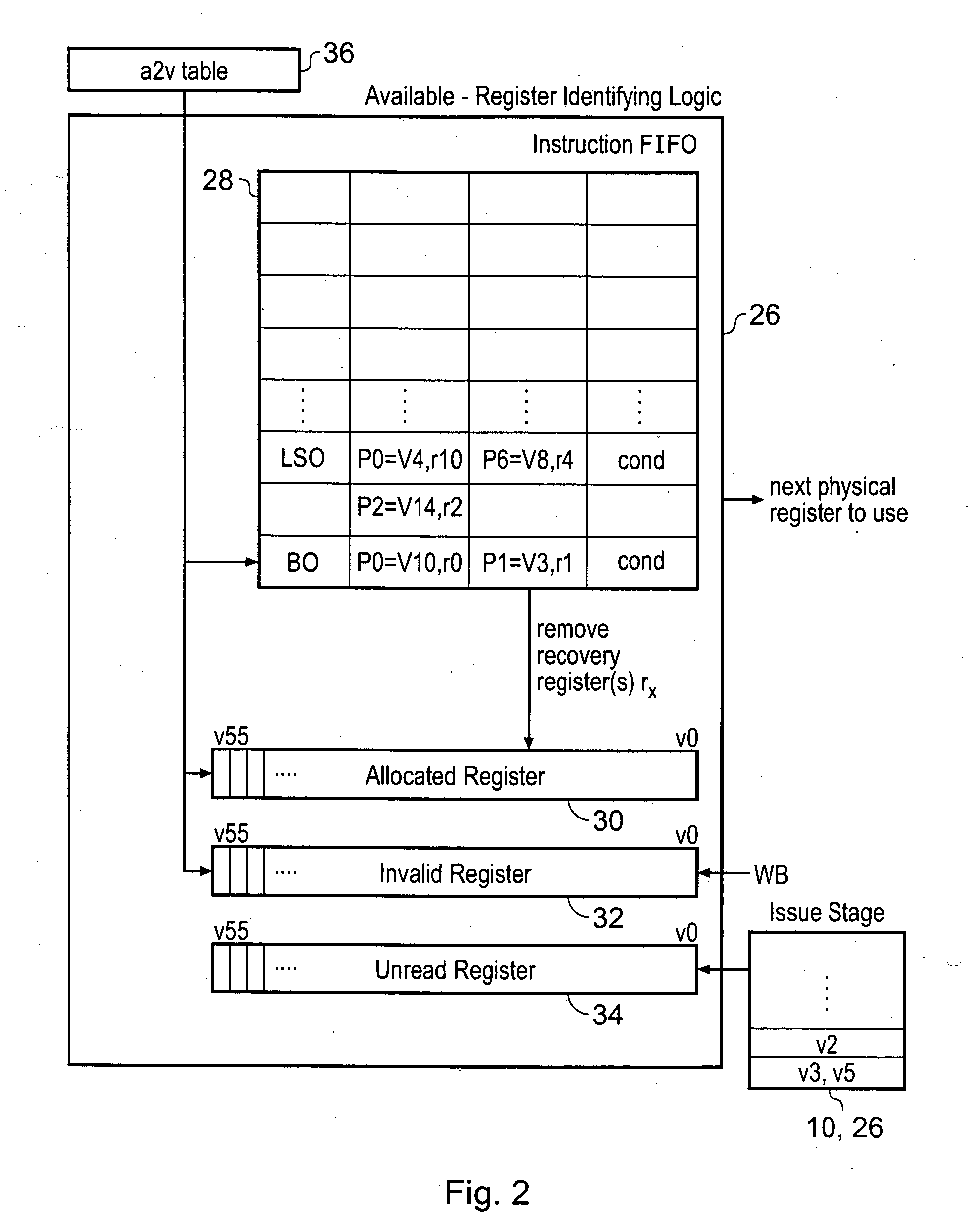

Determining register availability for register renaming

ActiveUS20080114966A1Easy to useAccurate operationDigital computer detailsMemory systemsParallel computingData treatment

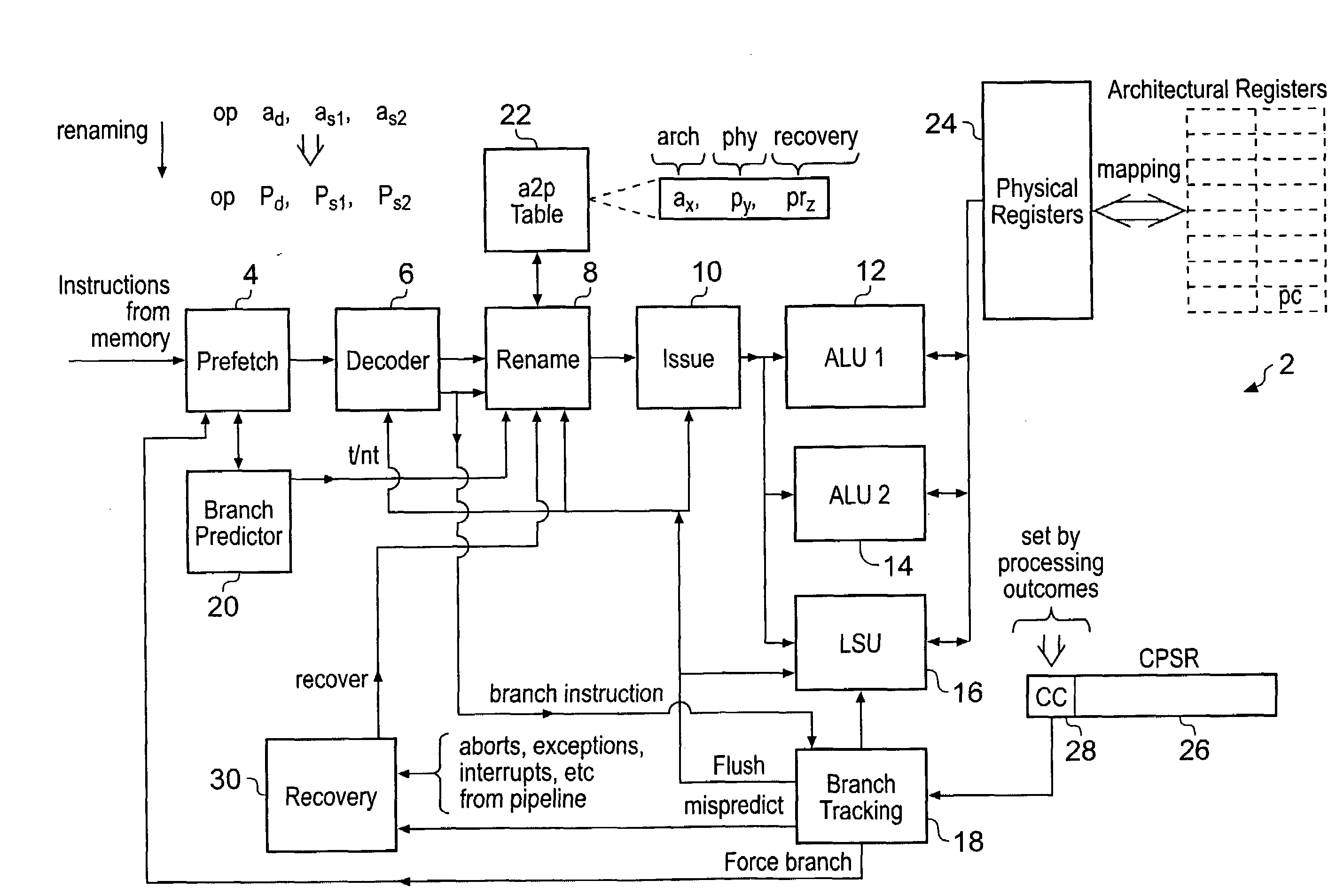

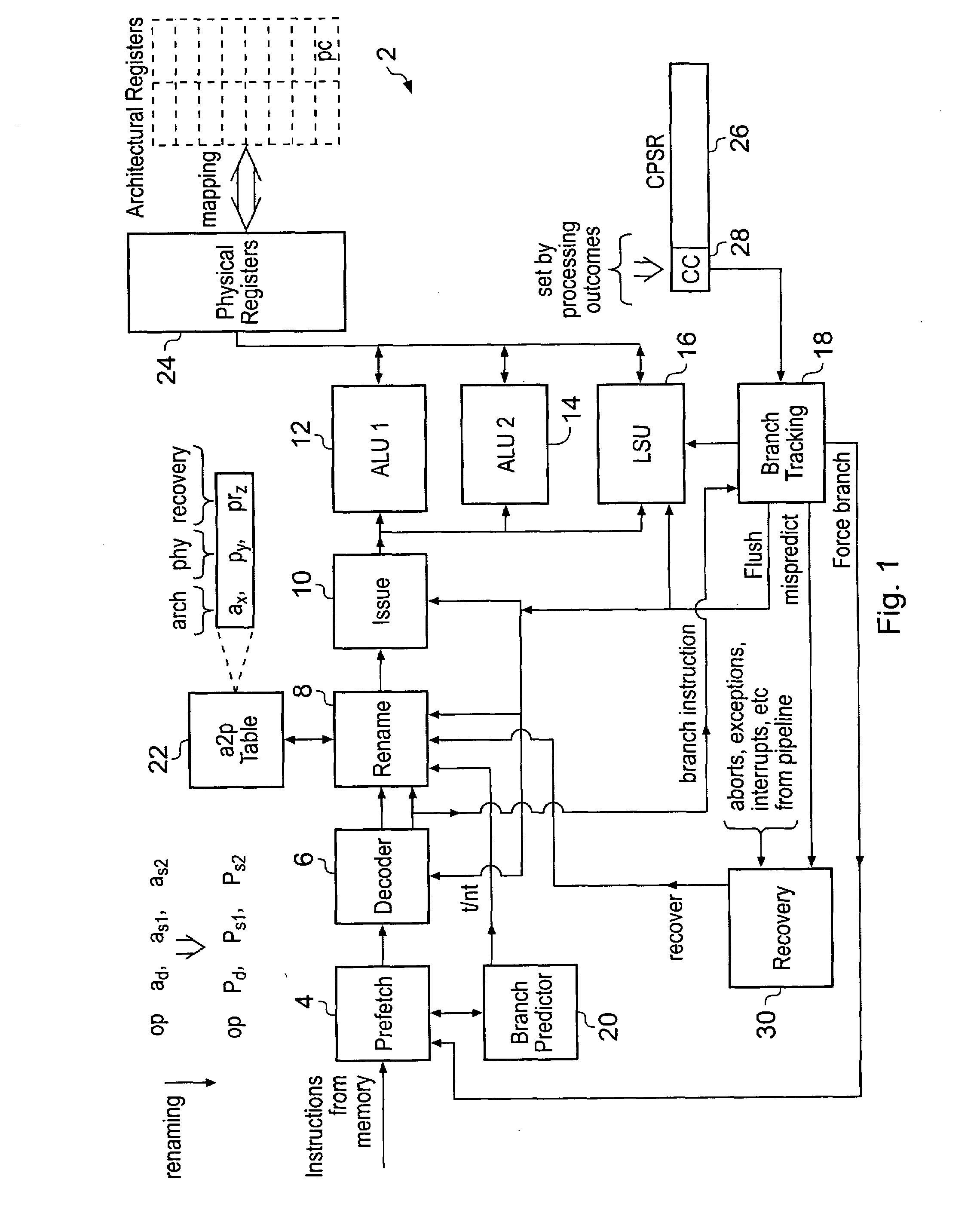

A data processing apparatus 2 supports out-of-order processing register renaming using a renaming stage 8. A set of physical registers 16 is mapped to architectural registers. Available-register identifying logic 26 is used to identify which physical registers 16 are available for use by the renaming stage 8. The available-register identifying logic 26 includes an instruction FIFO 28 storing register mapping data for unresolved instructions and indicating physical registers 16 storing data values which may be required in association with those unresolved speculative instructions. The speculative instructions may be predicted branch instructions, load / store instructions, conditional instructions or other types of instruction.

Owner:ARM LTD

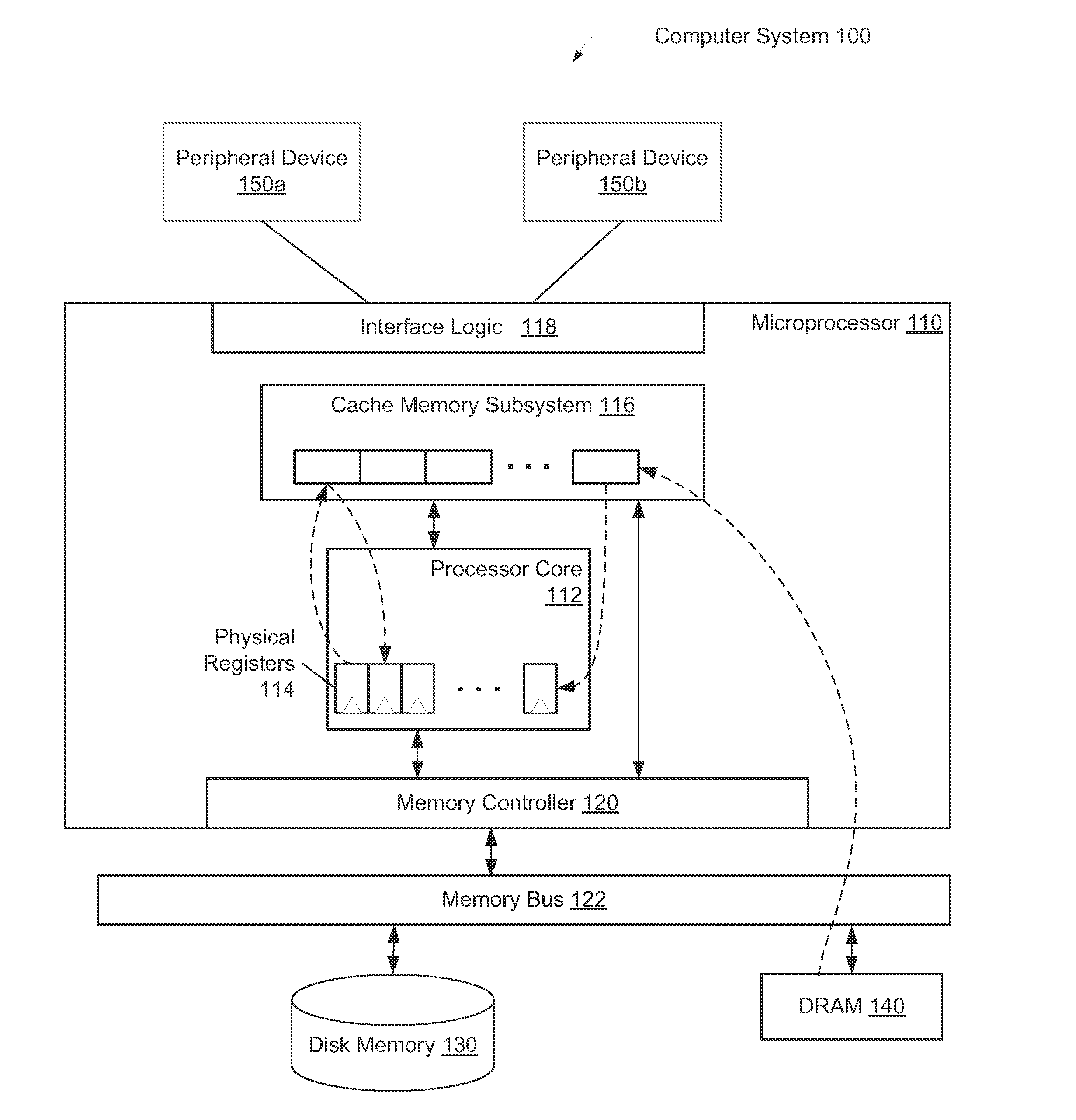

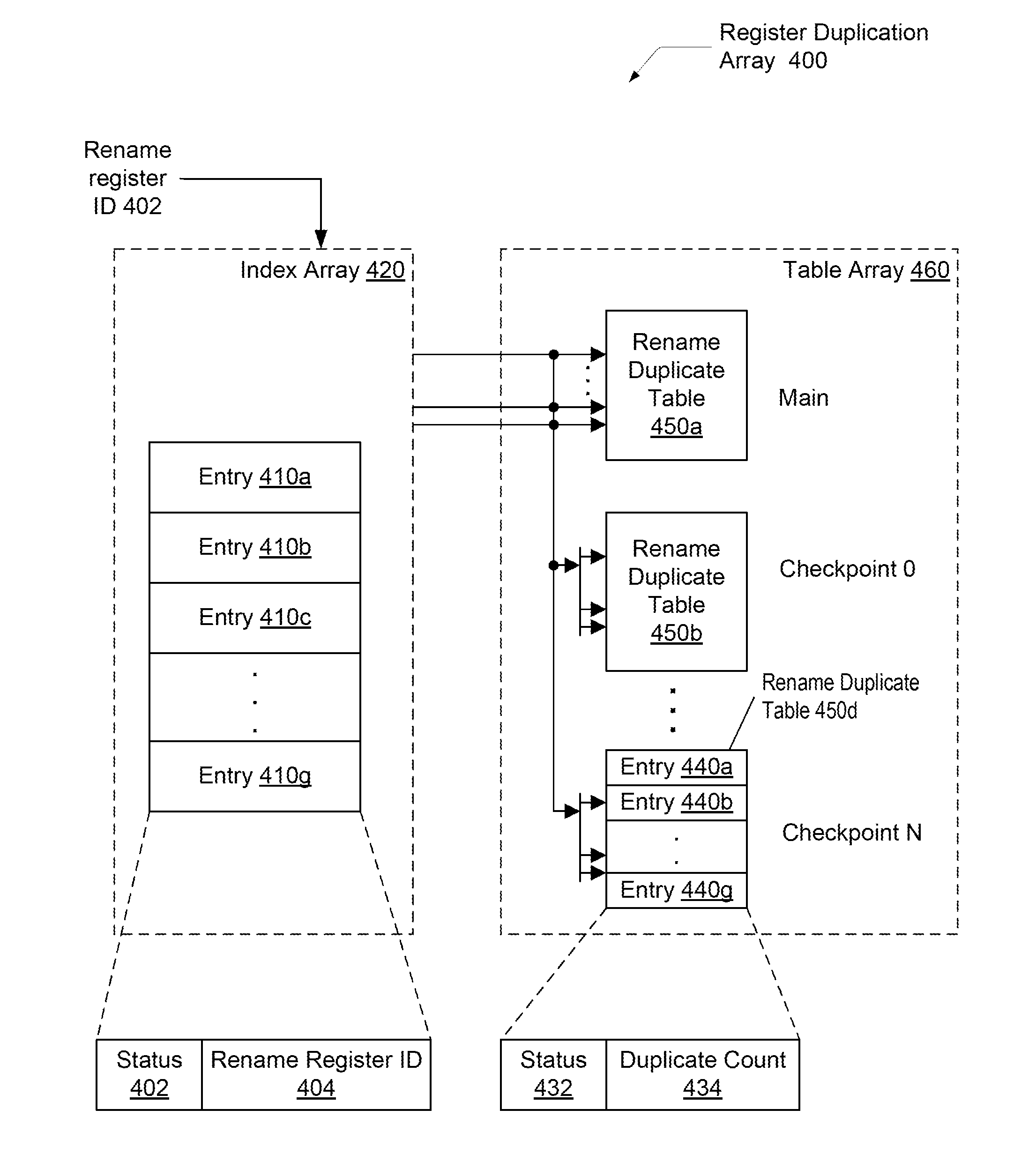

Rda checkpoint optimization

ActiveUS20150039860A1Efficient executionReduce power consumptionRegister arrangementsDigital computer detailsParallel computingContent-addressable storage

A system and method for efficiently performing microarchitectural checkpointing. A register rename unit within a processor determines whether a physical register number qualifies to have duplicate mappings. Information for maintenance of the duplicate mappings is stored in a register duplicate array (RDA). To reduce the penalty for misspeculation or exception recovery, control logic in the processor supports multiple checkpoints. The RDA is one of multiple data structures to have checkpoint copies of state. The RDA utilizes a content addressable memory (CAM) to store physical register numbers. The duplicate counts for both the current state and the checkpoint copies for a given physical register number are updated when instructions utilizing the given physical register number are retired. To reduce on-die real estate and power consumption, a single CAM entry is stores the physical register number and the other fields are stored in separate storage elements.

Owner:APPLE INC

Suppressing register renaming for conditional instructions predicted as not executed

ActiveUS20080177984A1Improve forecast accuracyAdvantageousDigital computer detailsSpecific program execution arrangementsData processing systemData treatment

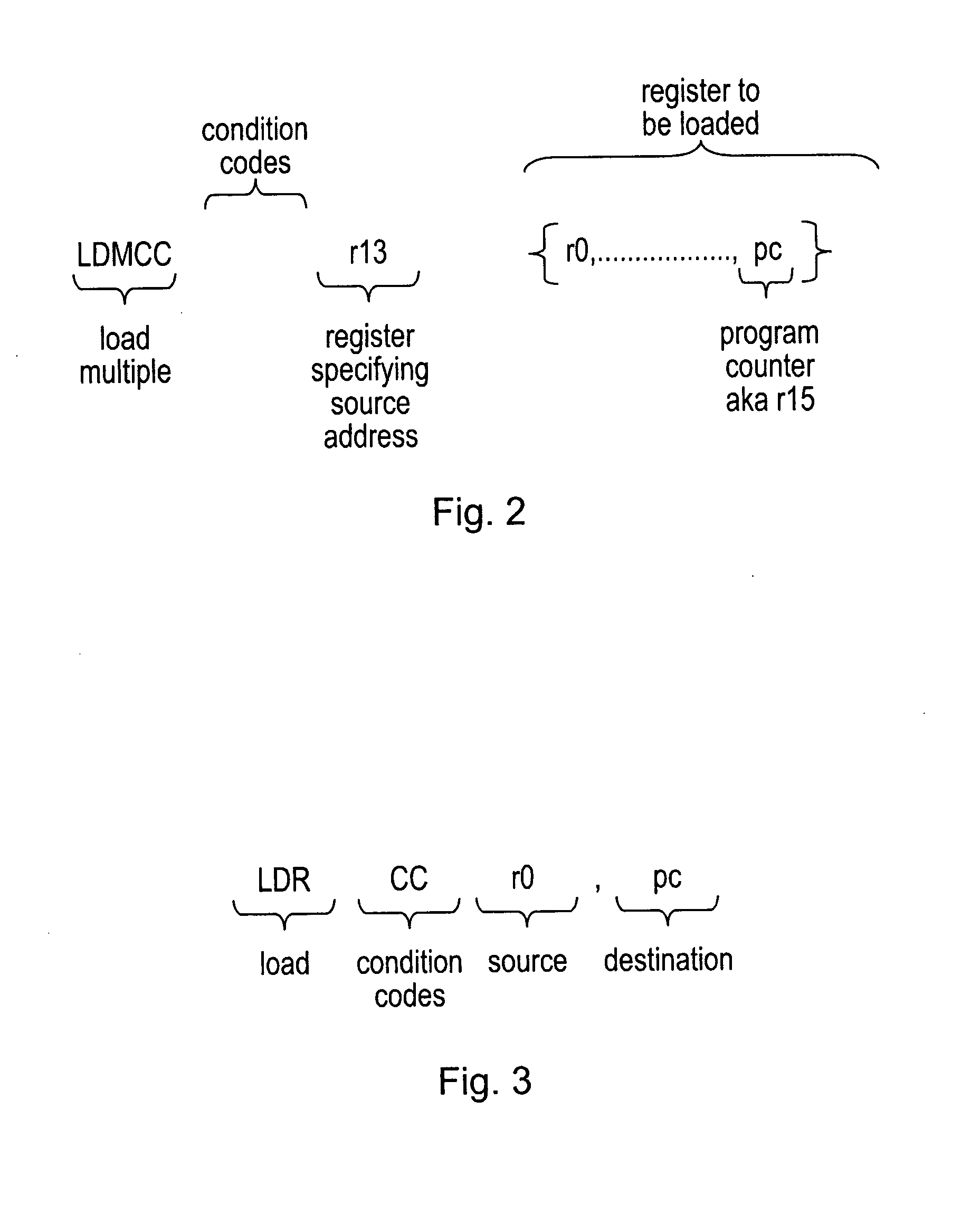

Within a data processing system 2 including a register renaming mechanism 8, 22, register renaming for some conditional instructions which are predicted as not-executed is suppressed. The conditional instructions which are subject to such suppression of renaming may not be all conditional instructions, but may be those which are known to consume a particularly large number of physical registers 24 if they are subject to renaming A conditional load multiple instruction in which multiple registers are loaded with new data values taken from memory in response to signal instruction is an example where the present technique may be used, particularly when one of the registers loaded is the program counter and accordingly the instruction is a conditional branch.

Owner:ARM LTD

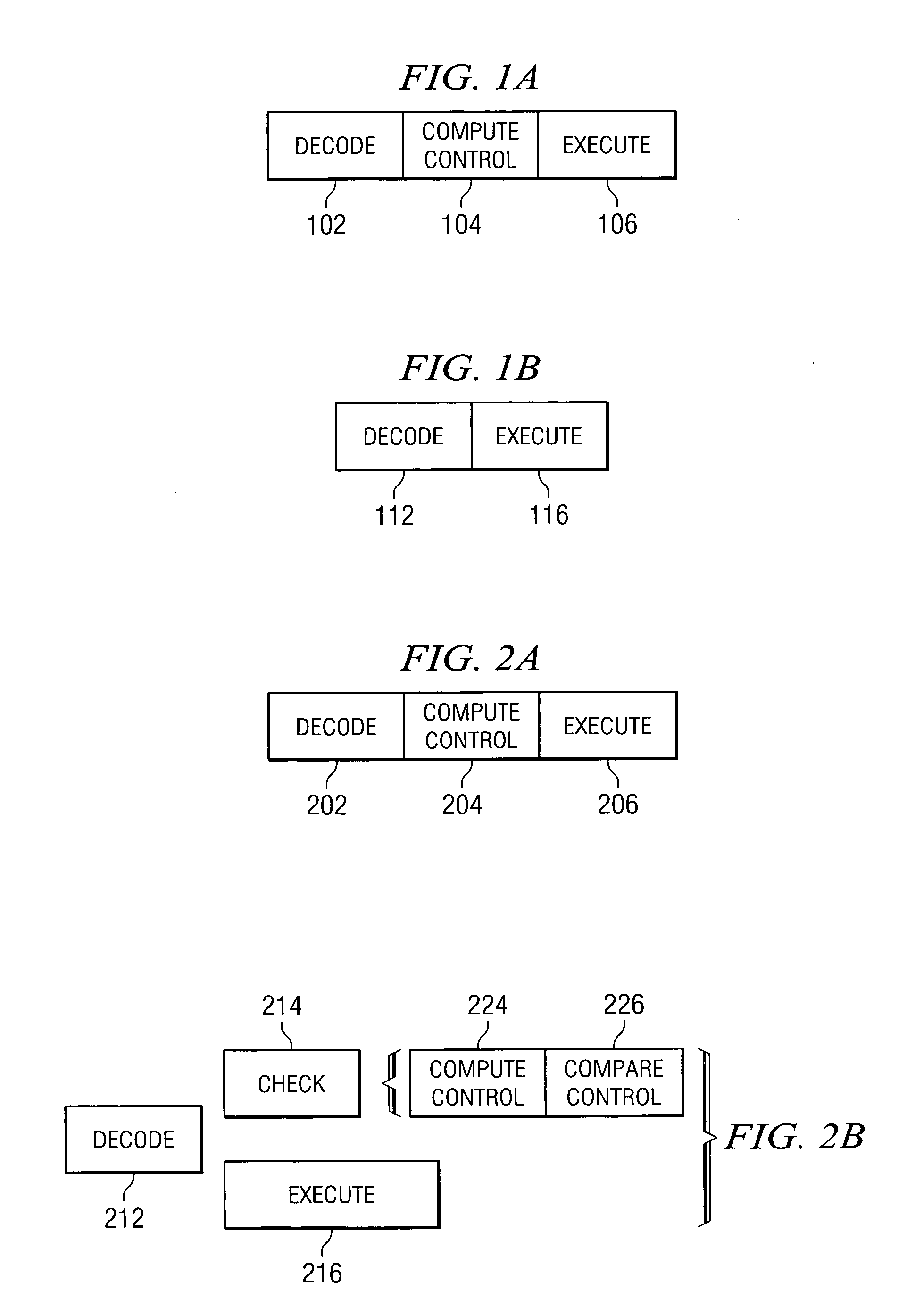

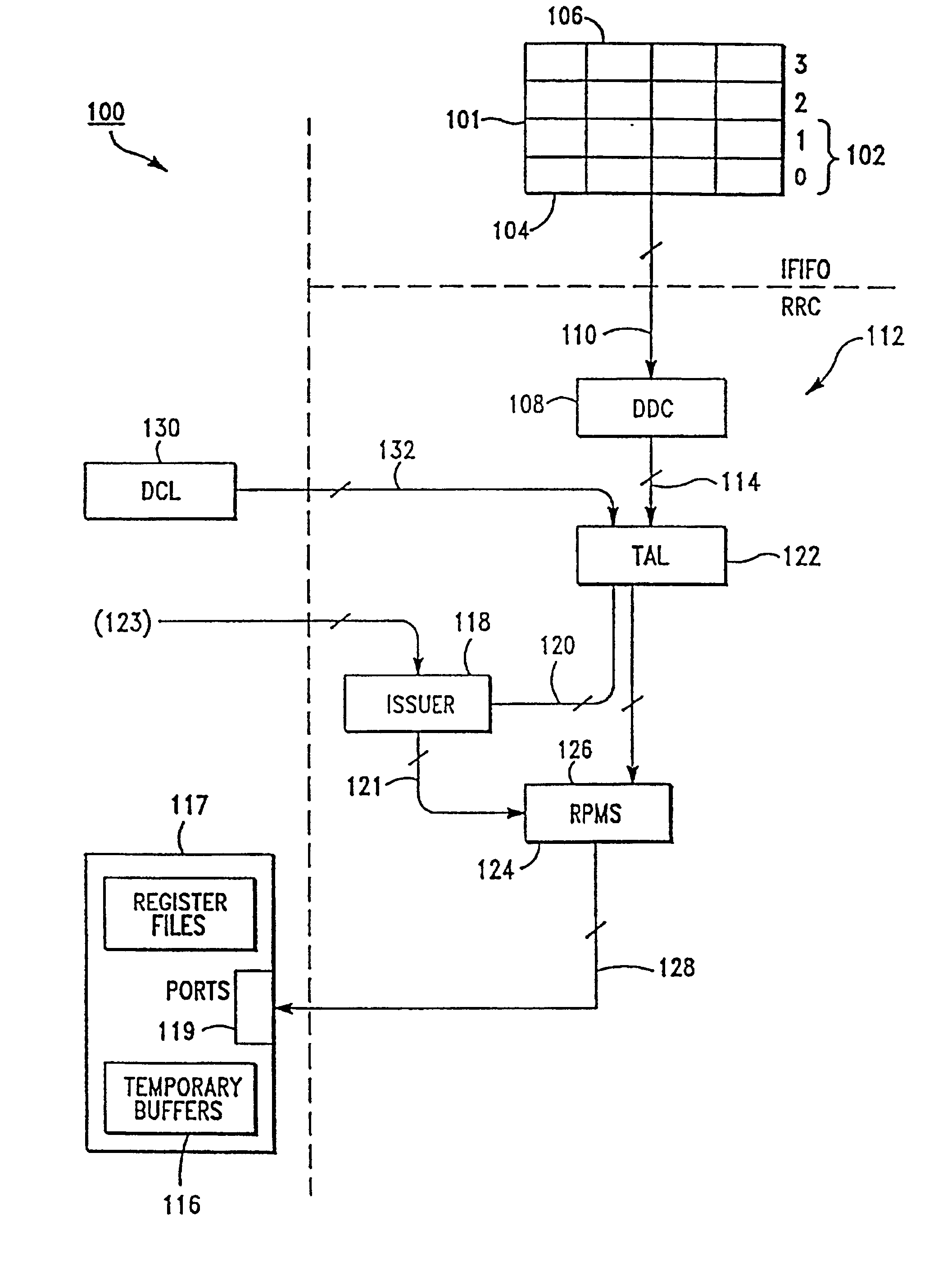

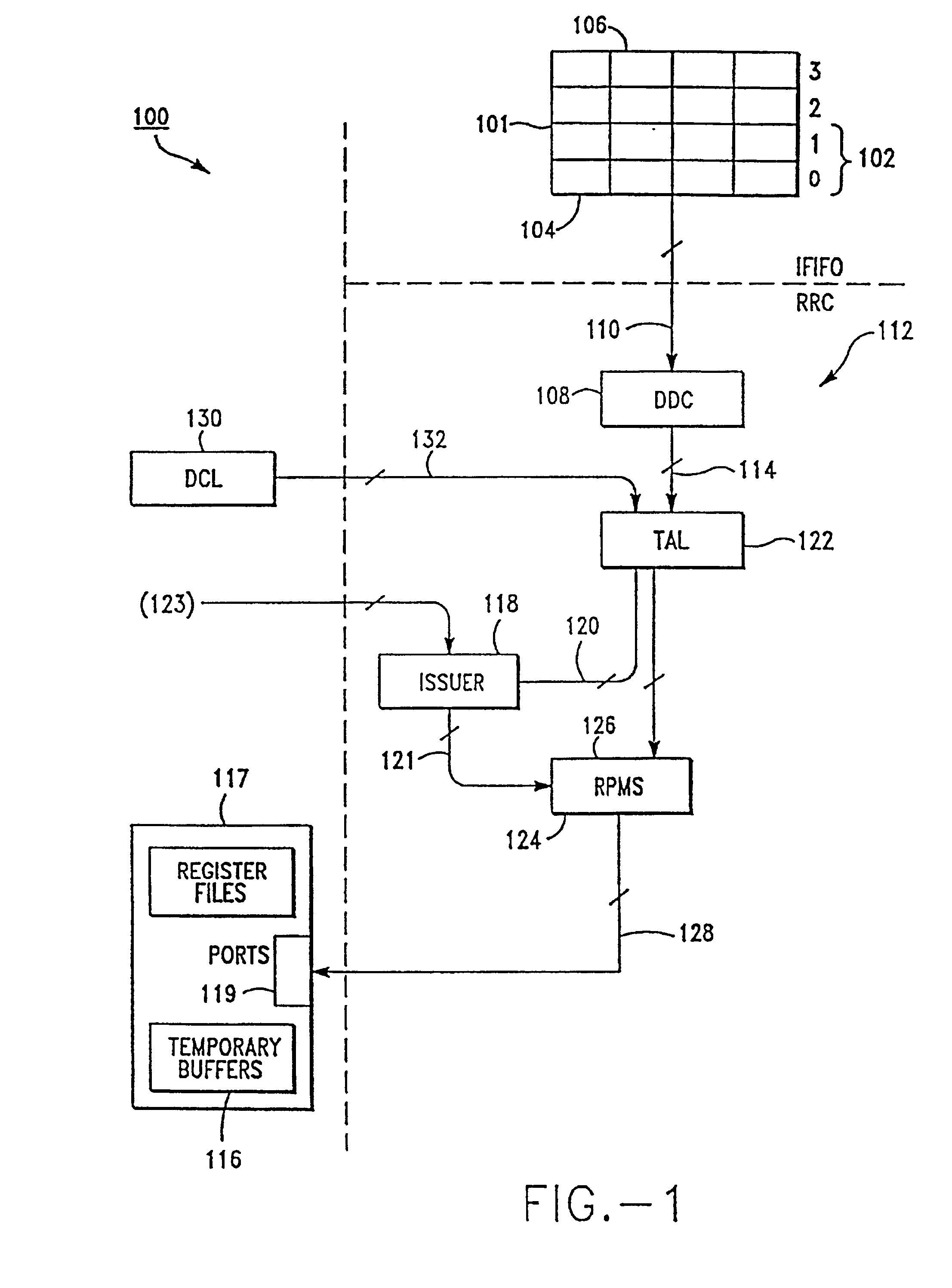

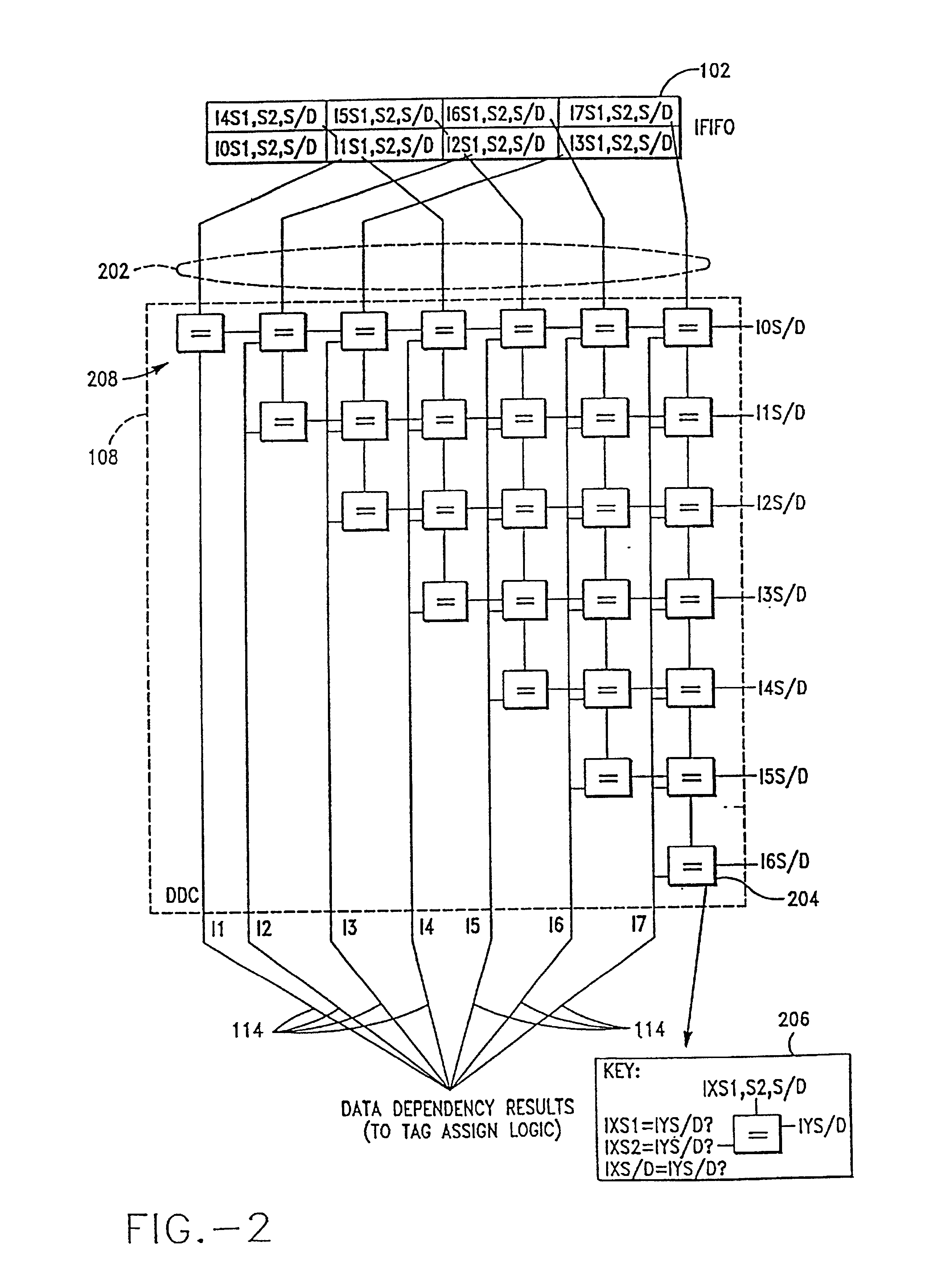

Superscalar RISC instruction scheduling

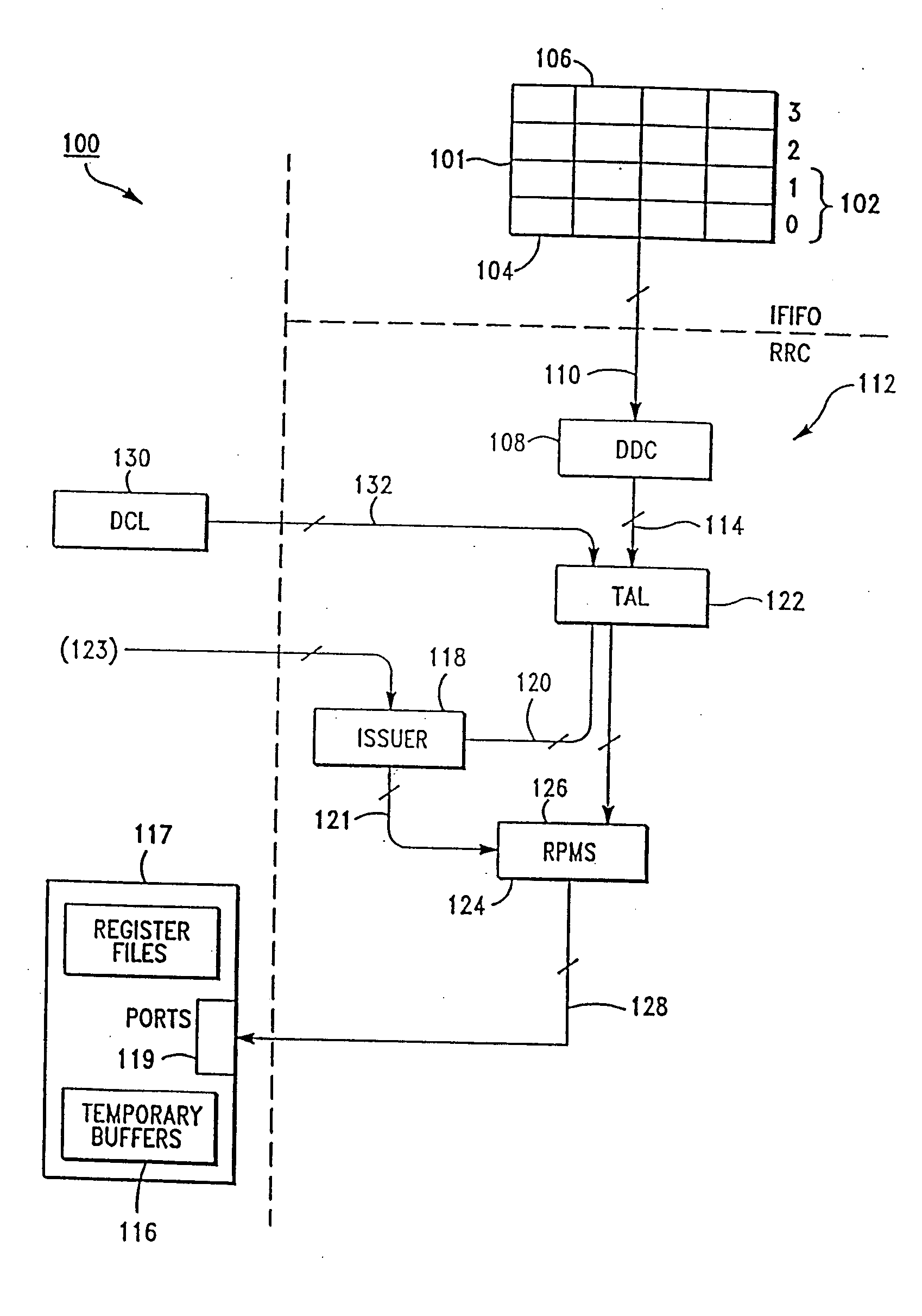

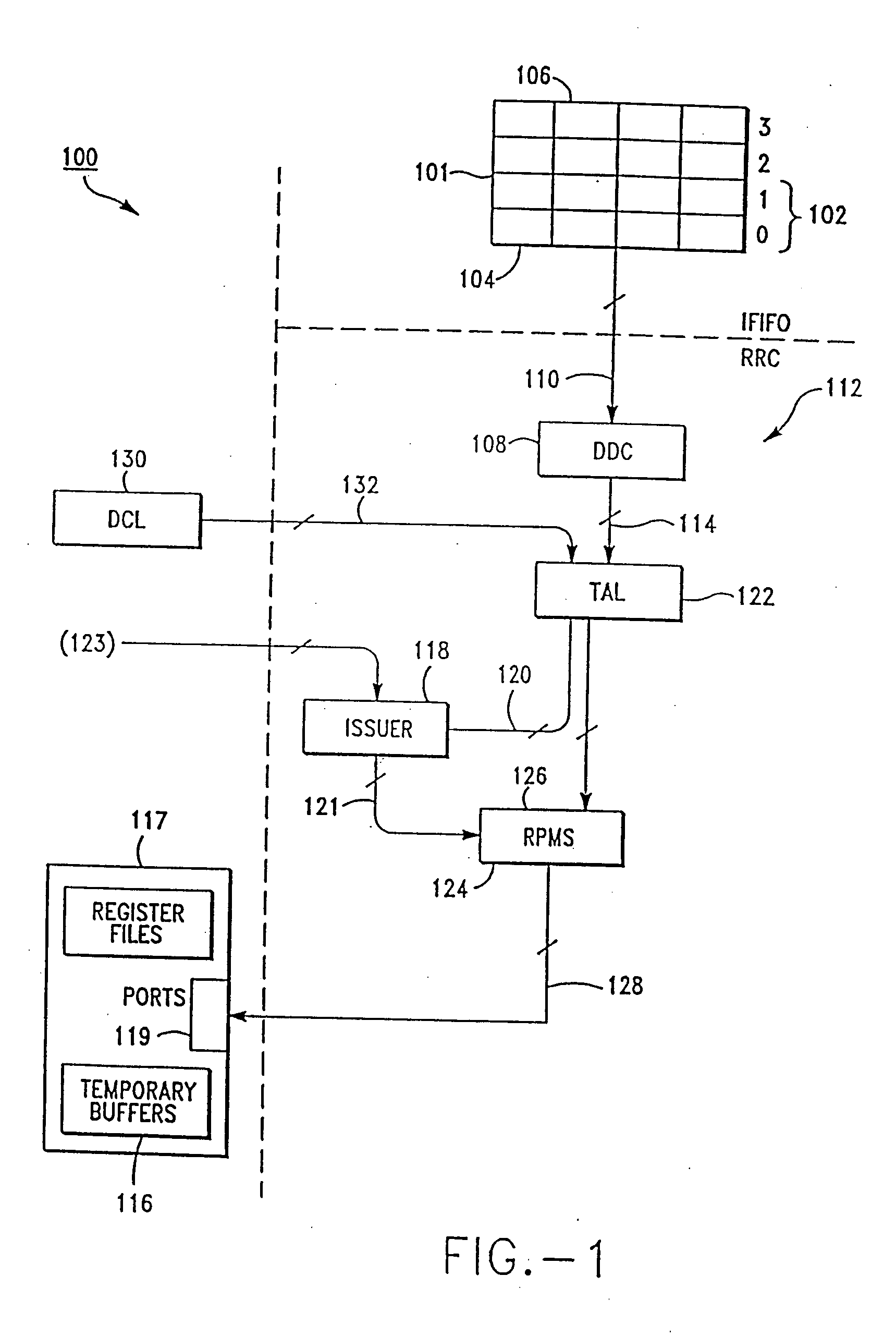

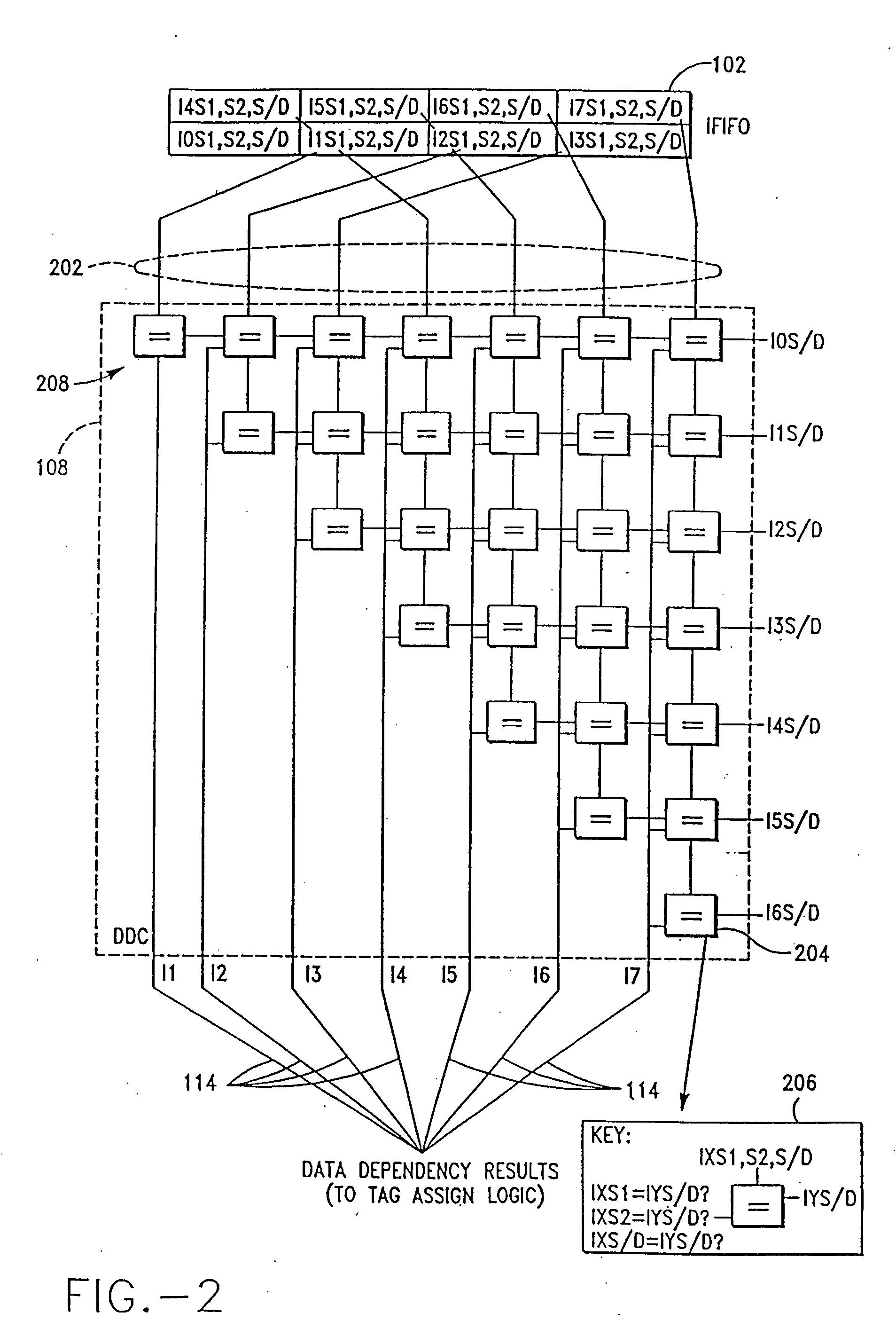

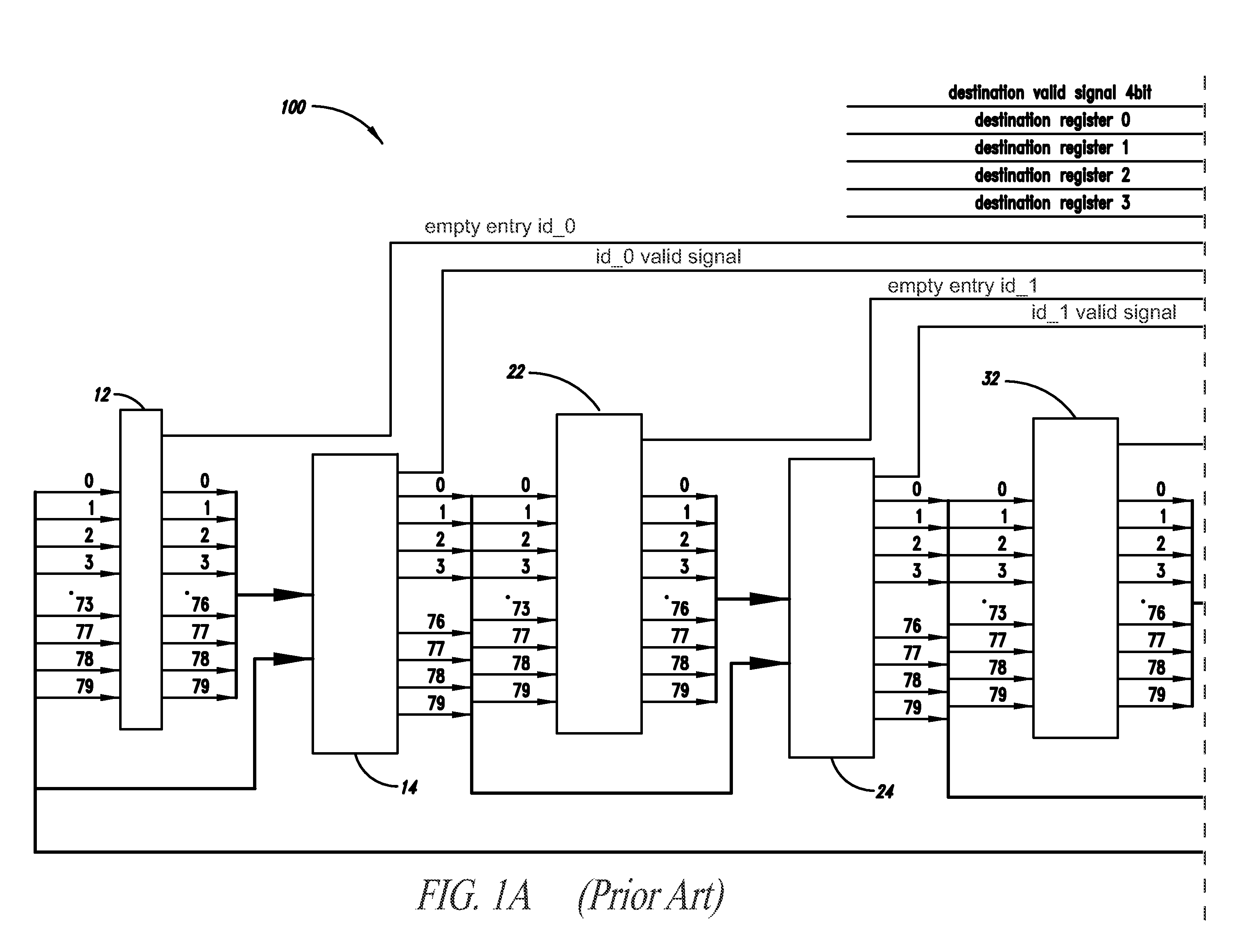

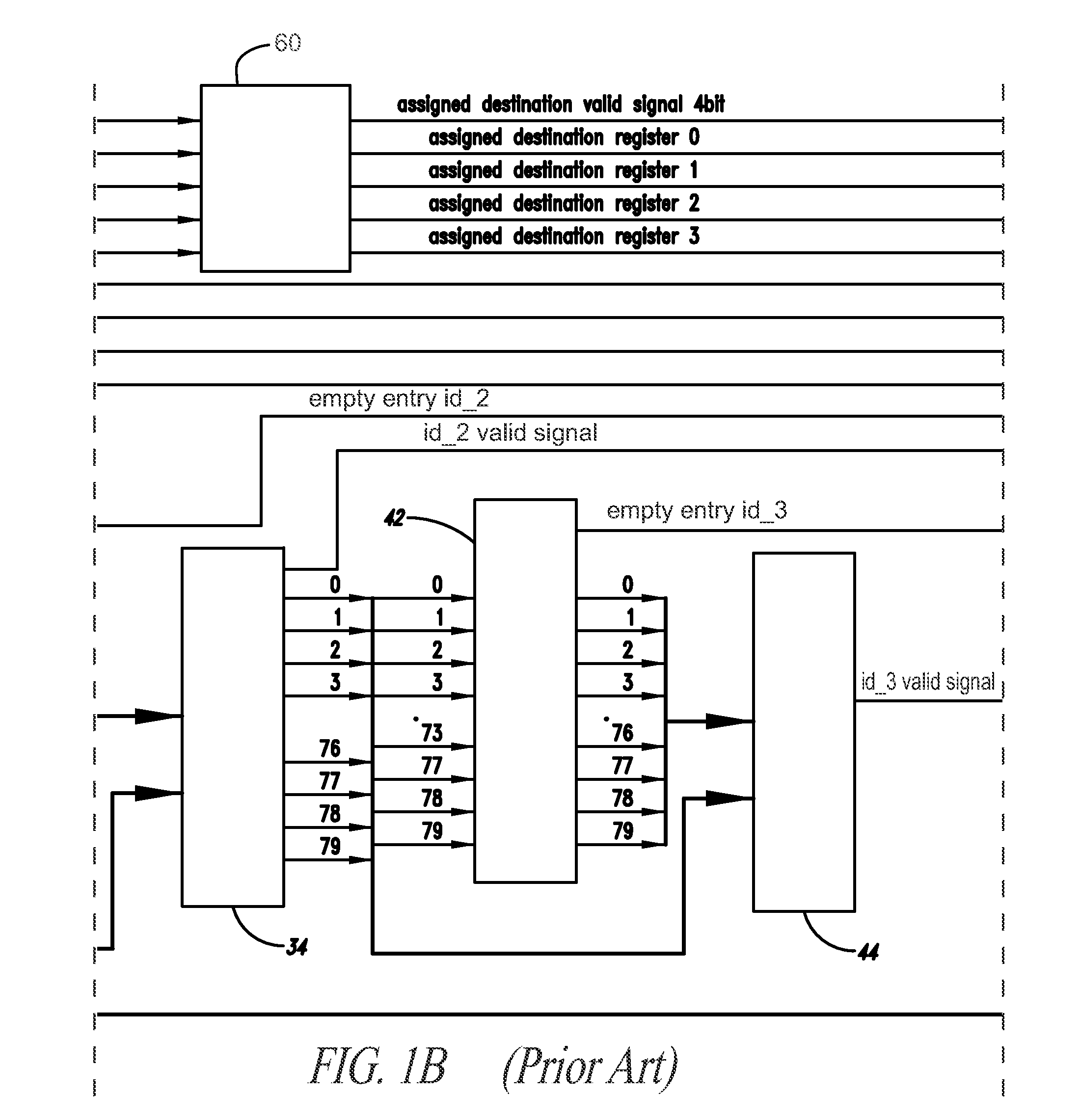

InactiveUS7051187B2Saving chip area/cost and execution speedRegister arrangementsGeneral purpose stored program computerScheduling instructionsMultiplexer

A register renaming system for out-of-order execution of a set of reduced instruction set computer instructions having addressable source and destination register fields, adapted for use in a computer having an instruction execution unit with a register file accessed by read address ports and for storing instruction operands. A data dependance check circuit is included for determining data dependencies between the instructions. A tag assignment circuit generates one or more tags to specify the location of operands, based on the data dependencies determined by the data dependance check circuit. A set of register file port multiplexers select the tags generated by the tag assignment circuit and pass the tags onto the read address ports of the register file for storing execution results.

Owner:HANGER SOLUTIONS LLC

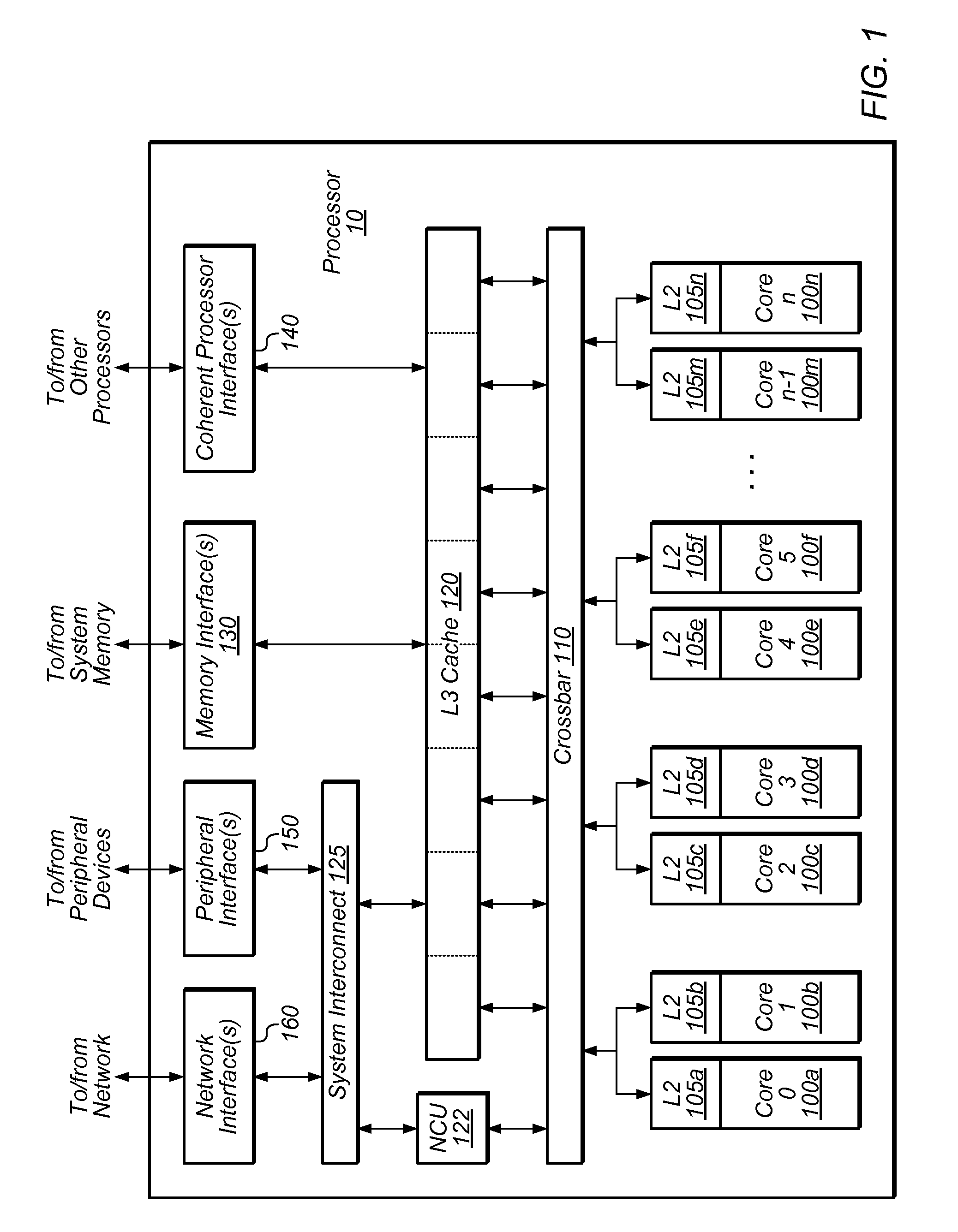

General purpose processing unit with low power digital signal processing (DSP) mode

InactiveUS20150026500A1Efficient executionReduce power consumptionPower supply for data processingEnergy efficient computingDigital signal processingGeneral purpose

A method and circuit arrangement utilize a general purpose processing unit having a low power DSP mode for reconfiguring the general purpose processing unit to efficiently execute DSP workloads with reduced power consumption. When in a DSP mode, one or more of a data cache, an execution unit, and simultaneous multithreading may be disabled to reduce power consumption and improve performance for DSP workloads. Furthermore, partitioning of a register file to support multithreading, and register renaming functionality, may be disabled to provide an expanded set of registers for use with DSP workloads. As a result, a general purpose processing unit may be provided with enhanced performance for DSP workloads with reduced power consumption, while also not sacrificing performance for other non-DSP / general purpose workloads.

Owner:GLOBALFOUNDRIES INC

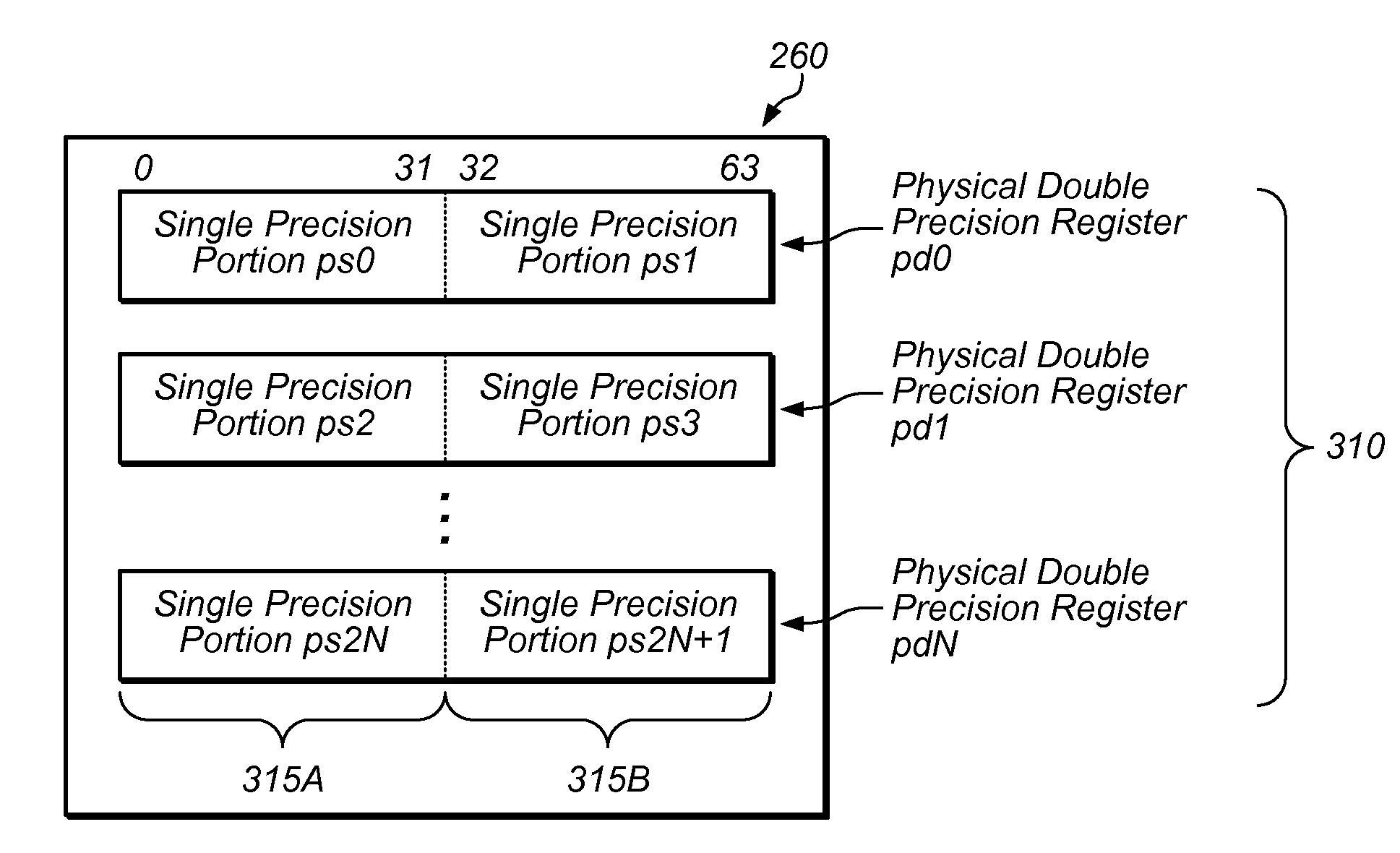

Apparatus and method for handling dependency conditions

ActiveUS20100274992A1Reduce problemsDigital computer detailsSpecific program execution arrangementsInstruction streamRegister renaming

Techniques for handling dependency conditions, including evil twin conditions, are disclosed herein. An instruction may designate a source register comprising two portions. The source register may be a double-precision register and its two portions may be single-precision portions, each specified as destinations by two other single-precision instructions. Execution of these two single-precision instructions, especially on a register renaming machine, may result in the appropriate values for the two portions of the source register being stored in different physical locations, which can complicate execution of an instruction stream. In response to detecting a potential dependency, one or more instructions may be inserted in an instruction stream to enable the appropriate values to be stored within one physical double precision register, eliminating an actual or potential evil twin dependency. Embodiments including a compiler that inserts instructions in a generated instruction stream to eliminate dependency conditions are also contemplated.

Owner:ORACLE INT CORP

Using register rename maps to facilitate precise exception semantics

ActiveUS8078854B2Facilitates precise exception semantics for a virtual machineEasy to implementDigital computer detailsSpecific program execution arrangementsSemanticsPerformed Procedure

Owner:ORACLE INT CORP

Optimized allocation of multi-pipeline executable and specific pipeline executable instructions to execution pipelines based on criteria

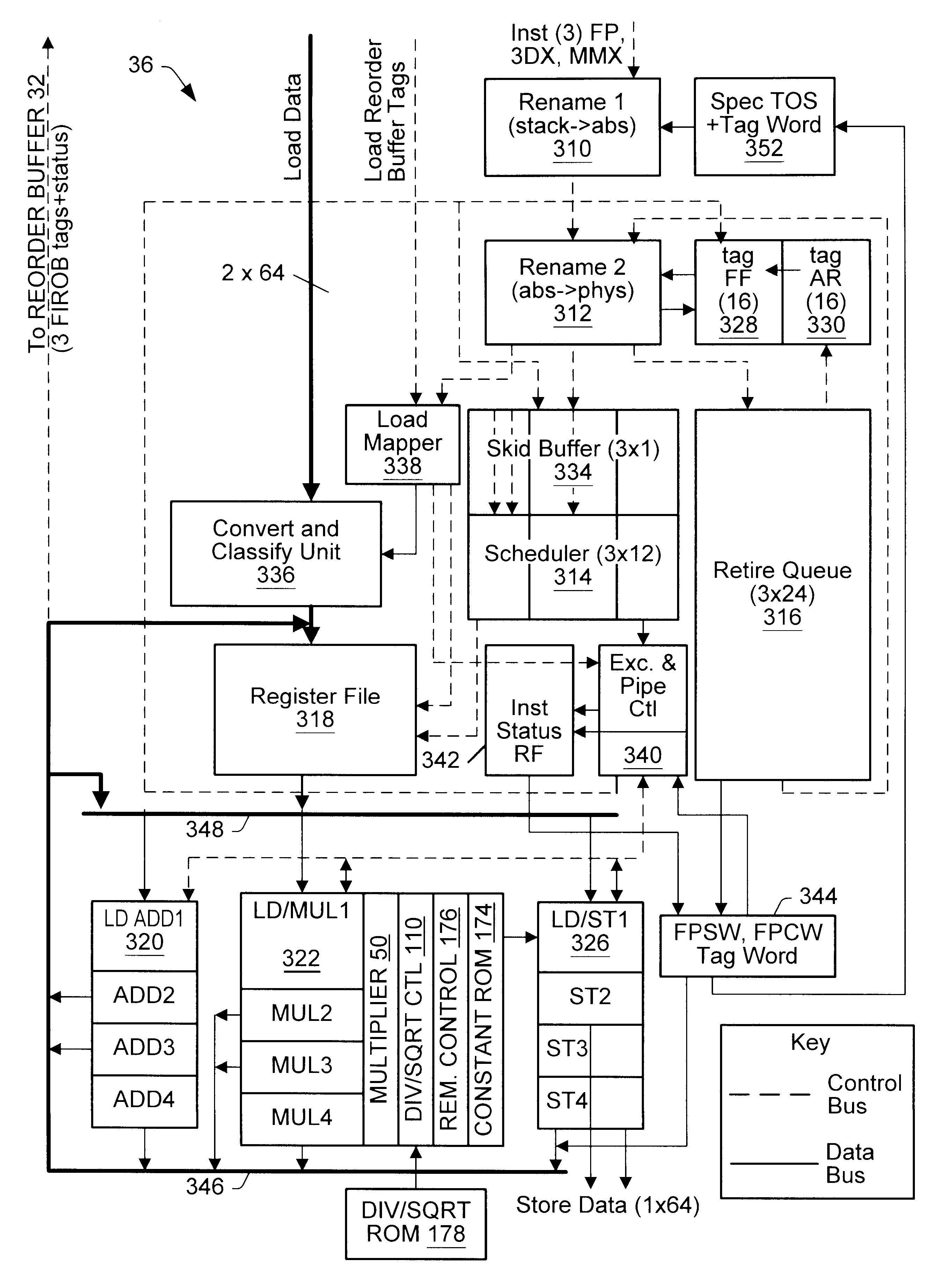

InactiveUS6370637B1Digital computer detailsMultiprogramming arrangementsFloating-point unitParallel computing

A microprocessor with a floating point unit configured to efficiently allocate multi-pipeline executable instructions is disclosed. Multi-pipeline executable instructions are instructions that are not forced to execute in a particular type of execution pipe. For example, junk ops are multi-pipeline executable. A junk op is an instruction that is executed at an early stage of the floating point unit's pipeline (e.g., during register rename), but still passes through an execution pipeline for exception checking. Junk ops are not limited to a particular execution pipeline, but instead may pass through any of the microprocessor's execution pipelines in the floating point unit. Multi-pipeline executable instructions are allocated on a per-clock cycle basis using a number of different criteria. For example, the allocation may vary depending upon the number of multi-pipeline executable instructions received by the floating point unit in a single clock cycle.

Owner:GLOBALFOUNDRIES INC

Superscalar RISC instruction scheduling

InactiveUS20060041736A1Saving chip area/costSaving execution speedRegister arrangementsGeneral purpose stored program computerScheduling instructionsMultiplexer

A register renaming system for out-of-order execution of a set of reduced instruction set computer instructions having addressable source and destination register fields, adapted for use in a computer having an instruction execution unit with a register file accessed by read address ports and for storing instruction operands. A data dependance check circuit is included for determining data dependencies between the instructions. A tag assignment circuit generates one or more tags to specify the location of operands, based on the data dependencies determined by the data dependance check circuit. A set of register file port multiplexers select the tags generated by the tag assignment circuit and pass the tags onto the read address ports of the register file for storing execution results.

Owner:HANGER SOLUTIONS LLC

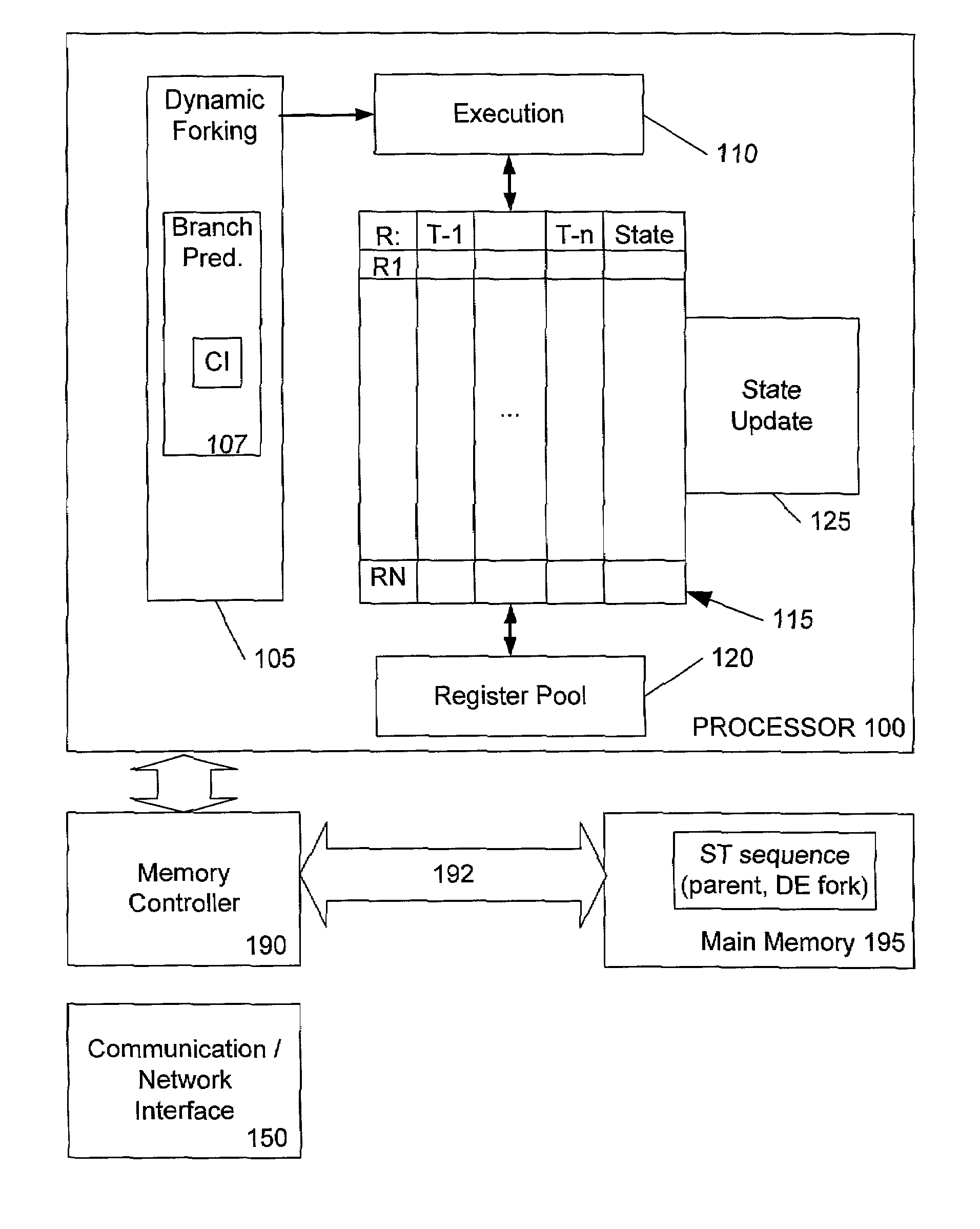

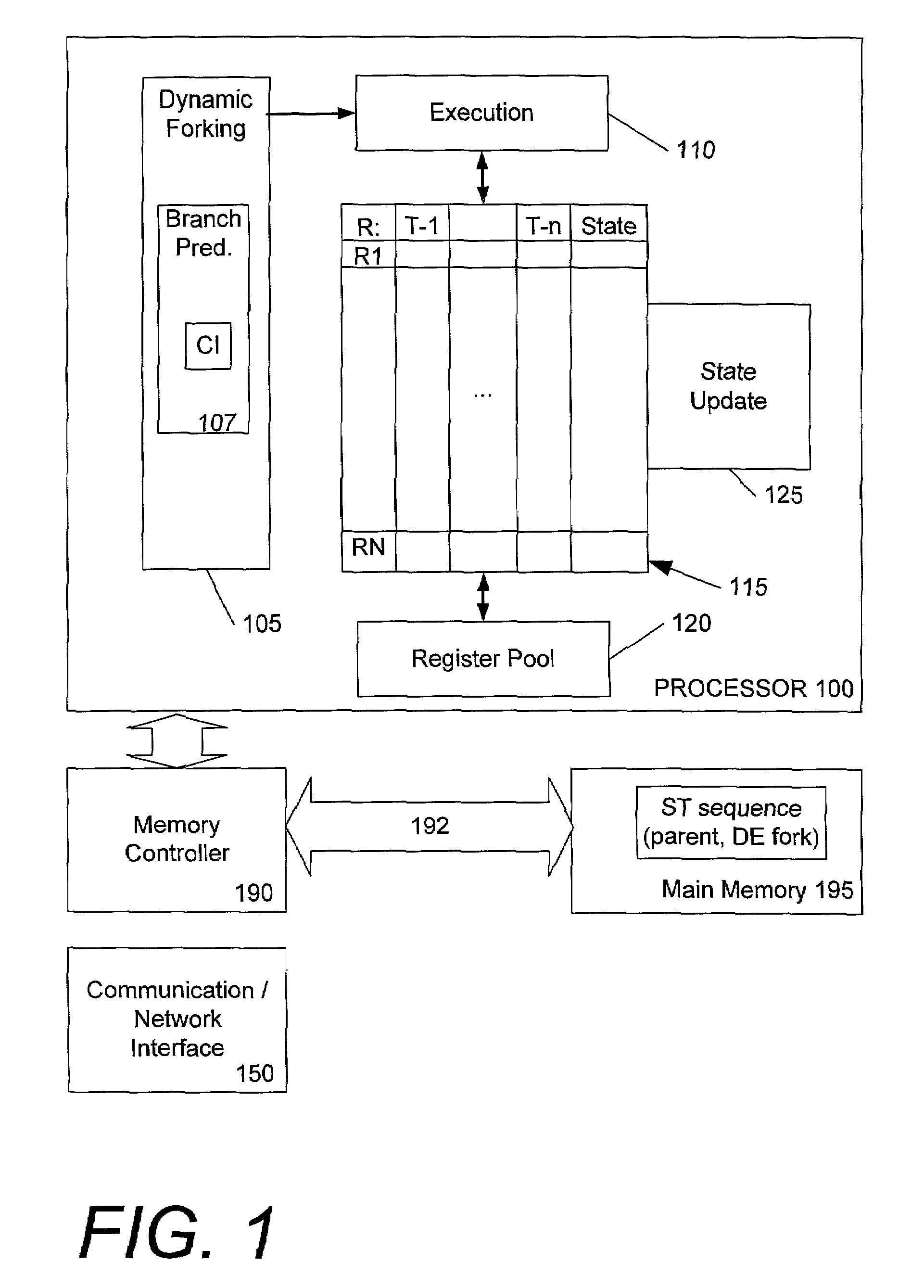

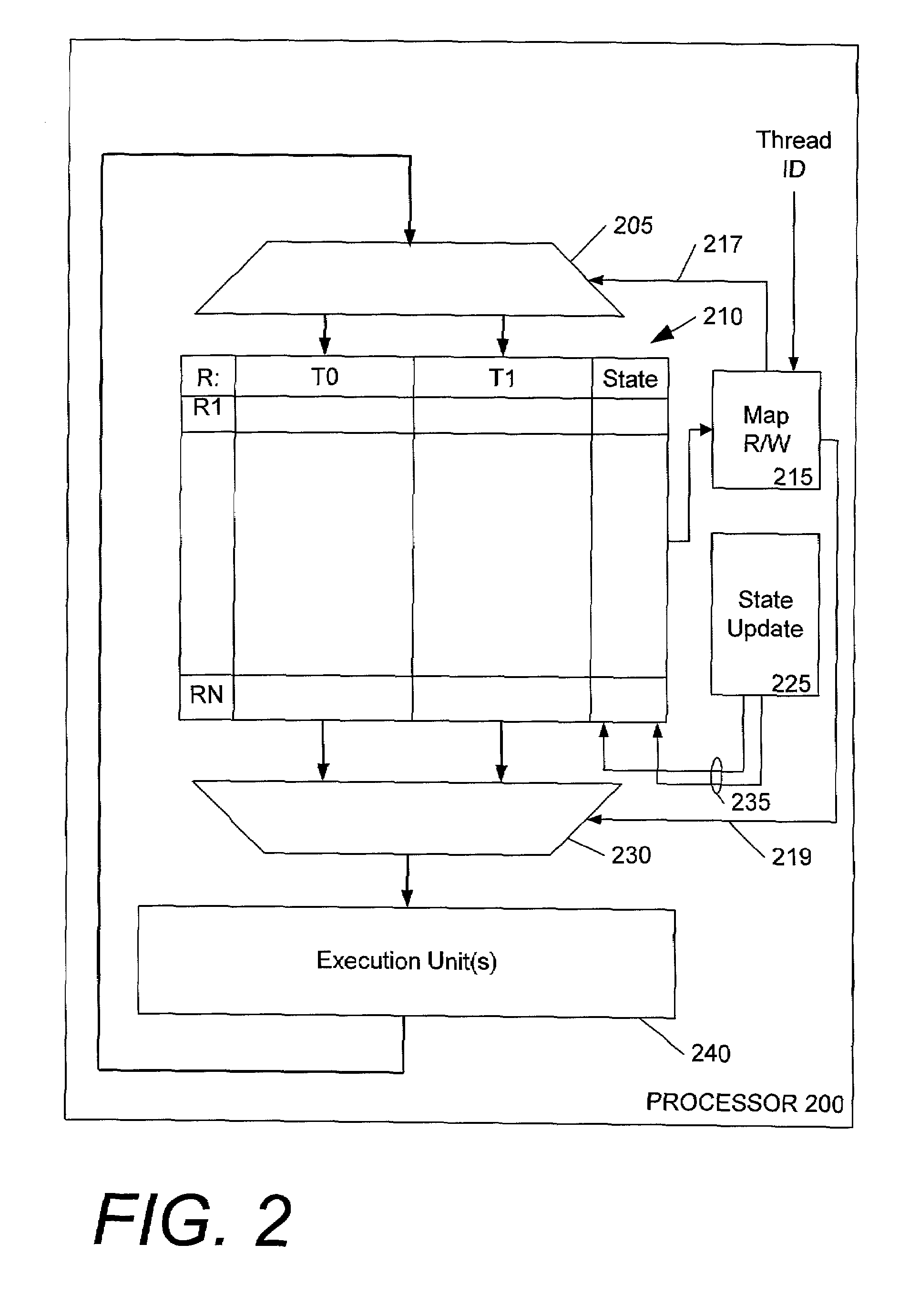

Register renaming for dynamic multi-threading

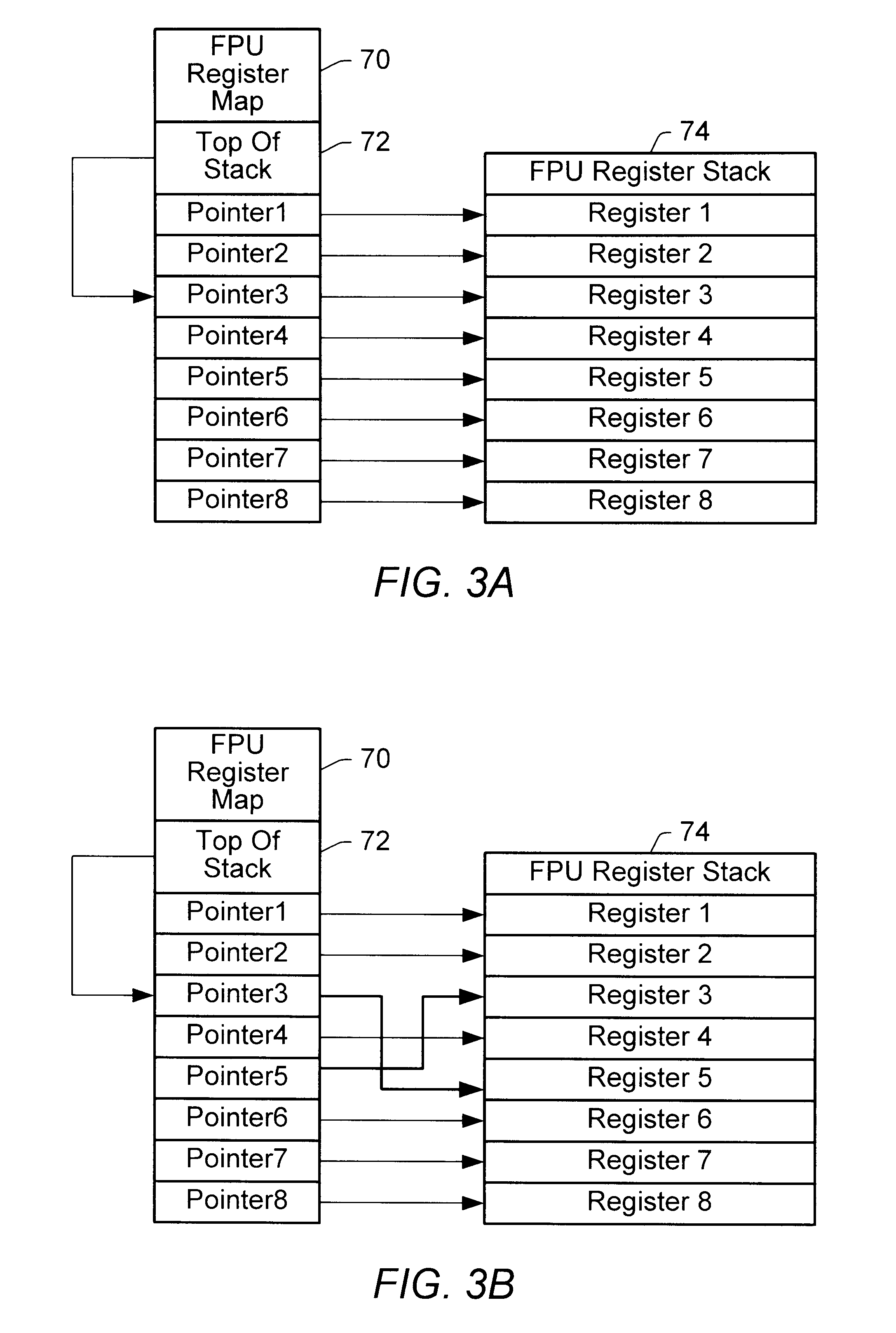

InactiveUS7313676B2Digital computer detailsConcurrent instruction executionTheoretical computer scienceRegister renaming

A register renaming technique for dynamic multithreading. One disclosed embodiment includes a register map to store up to M×N values to map M registers for N threads. A set of N values, one per thread, and a set of state bits is associated with each of the M registers. Each set of state bits indicates which of the N values per register are valid and whether ones of the N sets of values have been written by a dynamic execution thread. In response to termination of a dynamic execution thread, recovery logic may update state bits associated with ones of the M registers that were written to during dynamic execution.

Owner:INTEL CORP

Apparatus and method for handling dependency conditions

Owner:ORACLE INT CORP

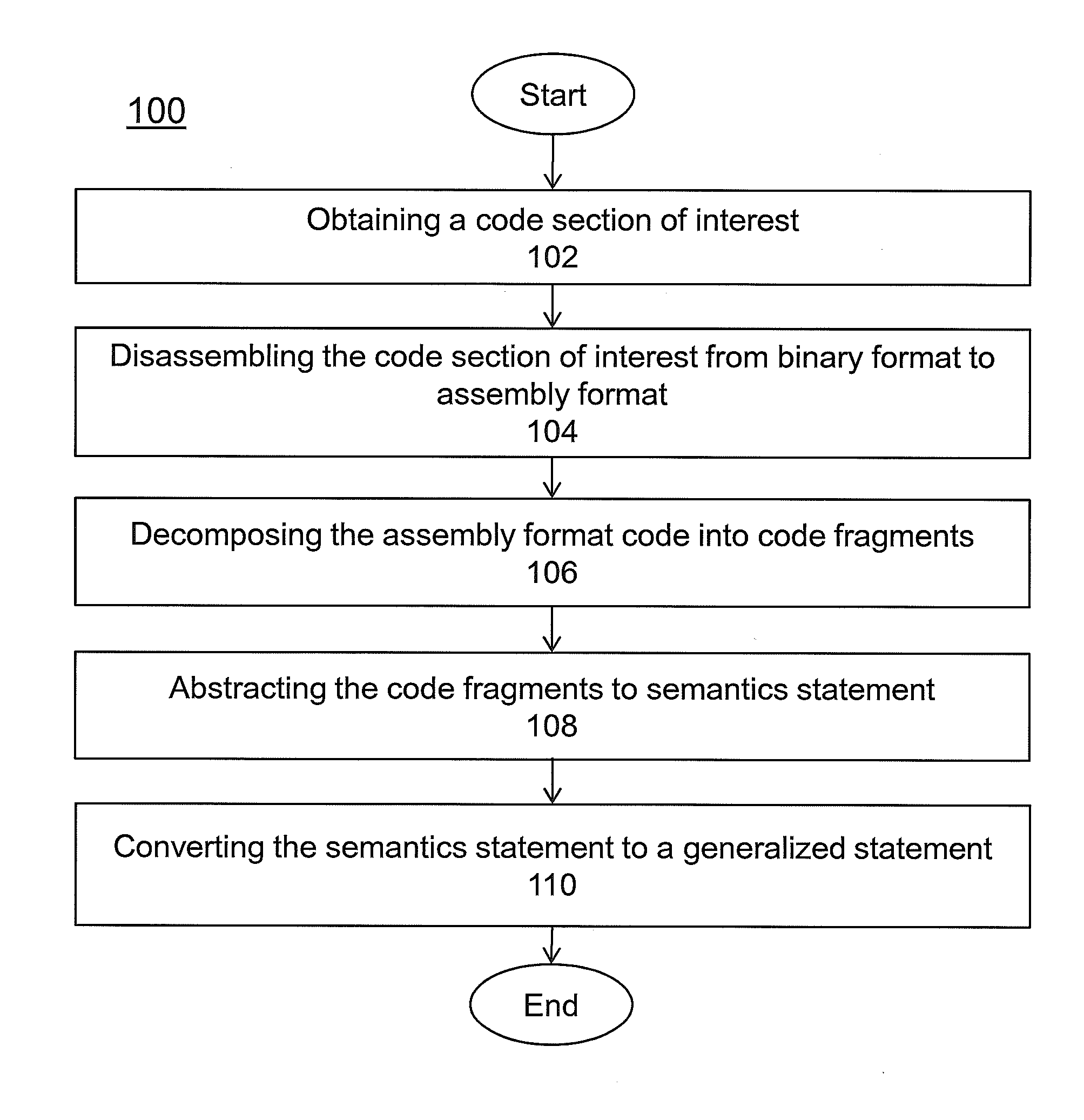

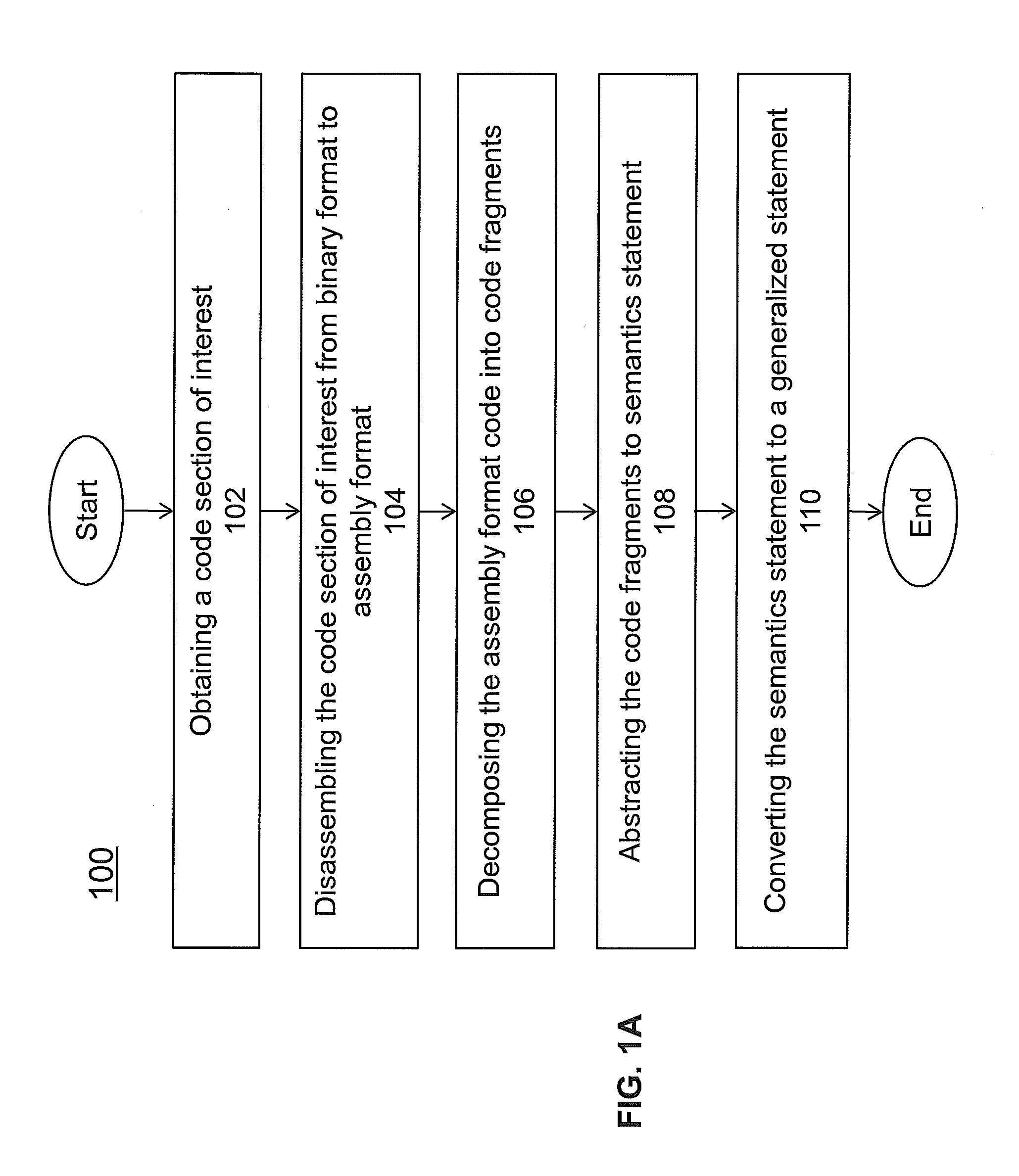

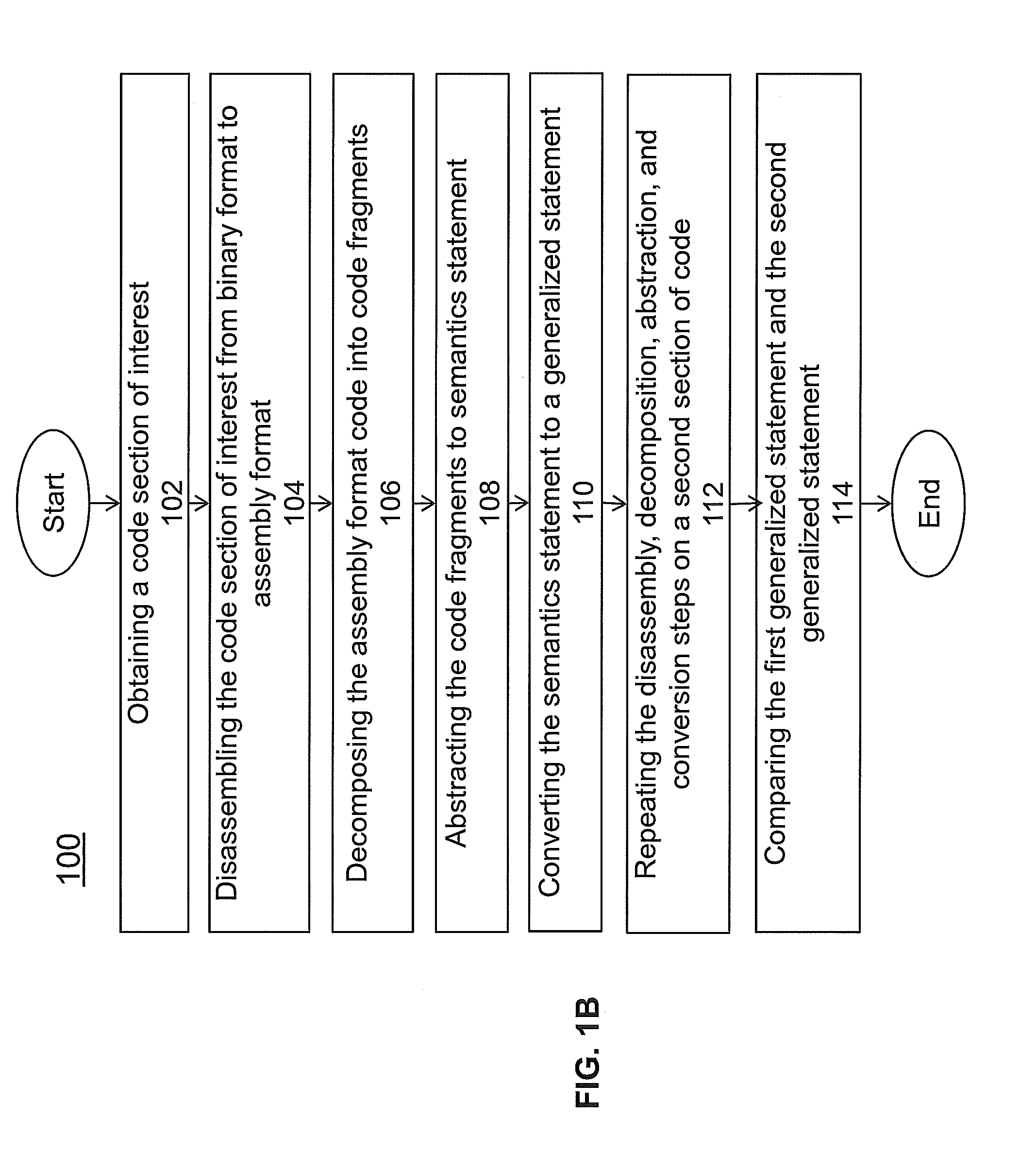

System and method for identifying and comparing code by semantic abstractions

ActiveUS20150186648A1Efficient analysisFast and accurate searchMemory loss protectionError detection/correctionParallel computingInstruction selection

Certain embodiments of the present invention are configured to facilitate analyzing computer code more efficiently. For example, by conducting a first level abstraction (e.g., symbolic interpretation and algebraic simplification) and a second level abstraction (e.g., generalization) of the computer code, the analysis may more accurately account for variations in the code that may occur as a result of register renaming, instruction reordering, choice of instructions, etc. while minimizing the cost of computations required to perform the analysis.

Owner:THE UNIV OF LOUISIANA AT LAFAYETTE

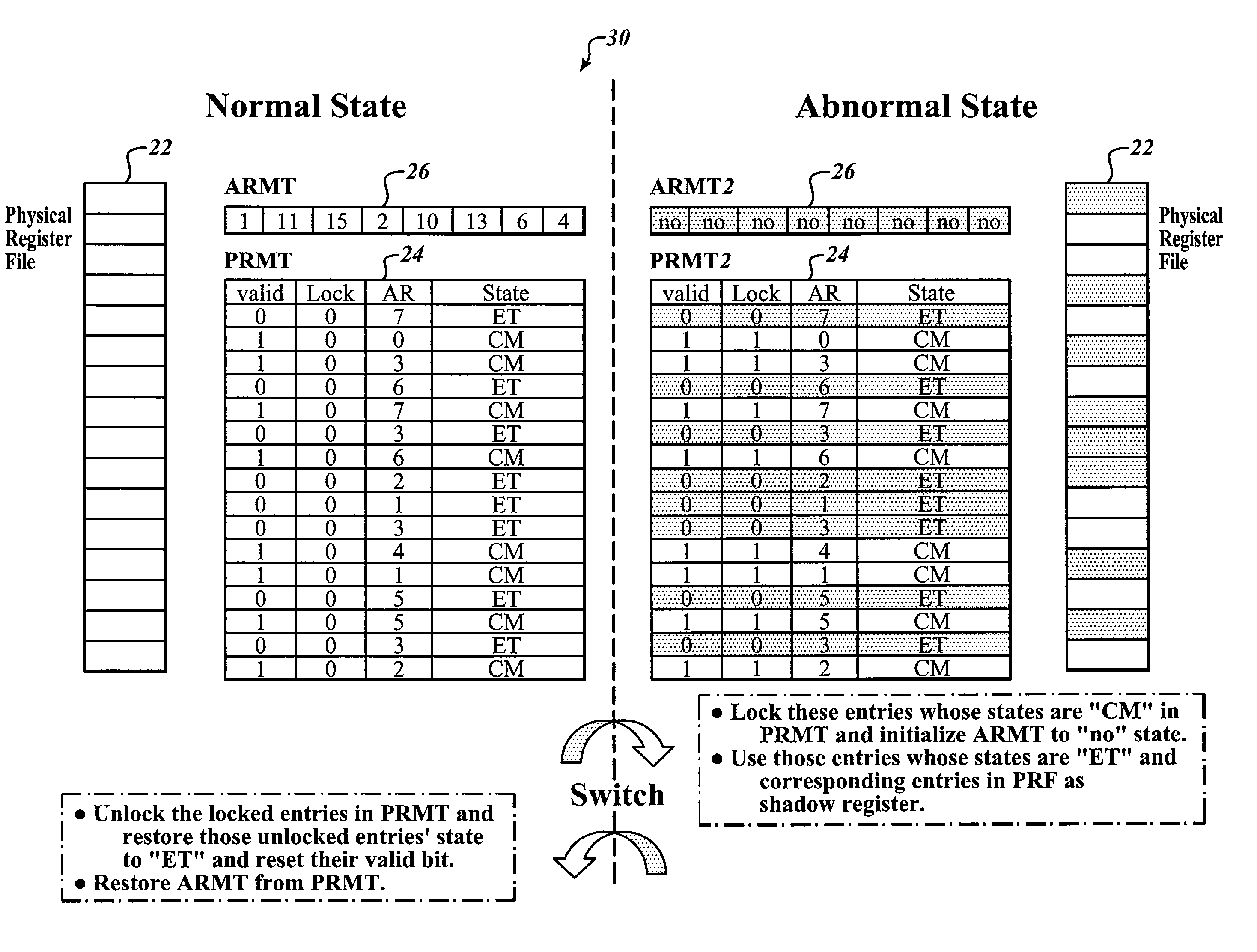

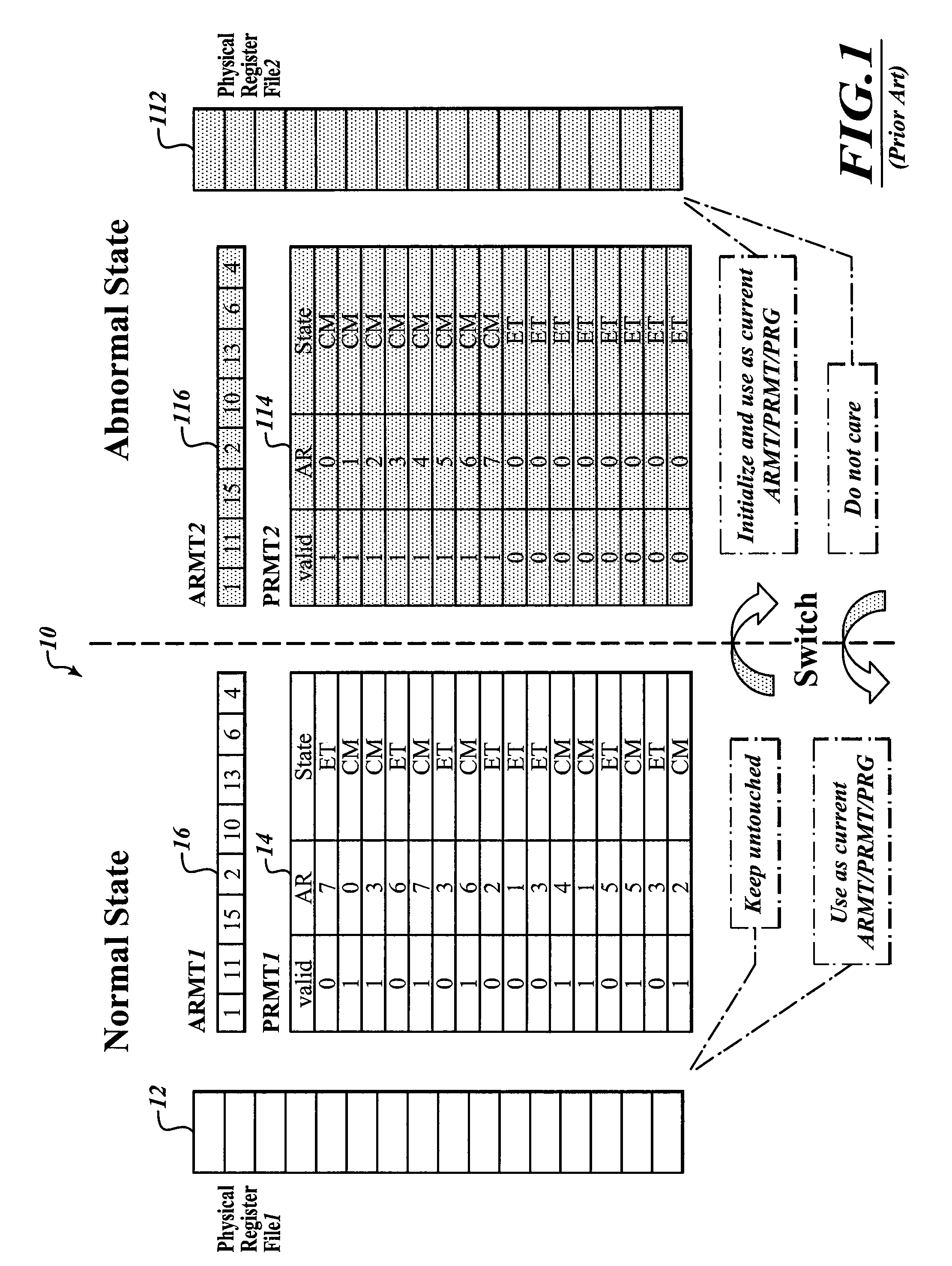

Apparatus utilizing efficient hardware implementation of shadow registers and method thereof

ActiveUS9015450B2Digital computer detailsConcurrent instruction executionParallel computingHardware implementations

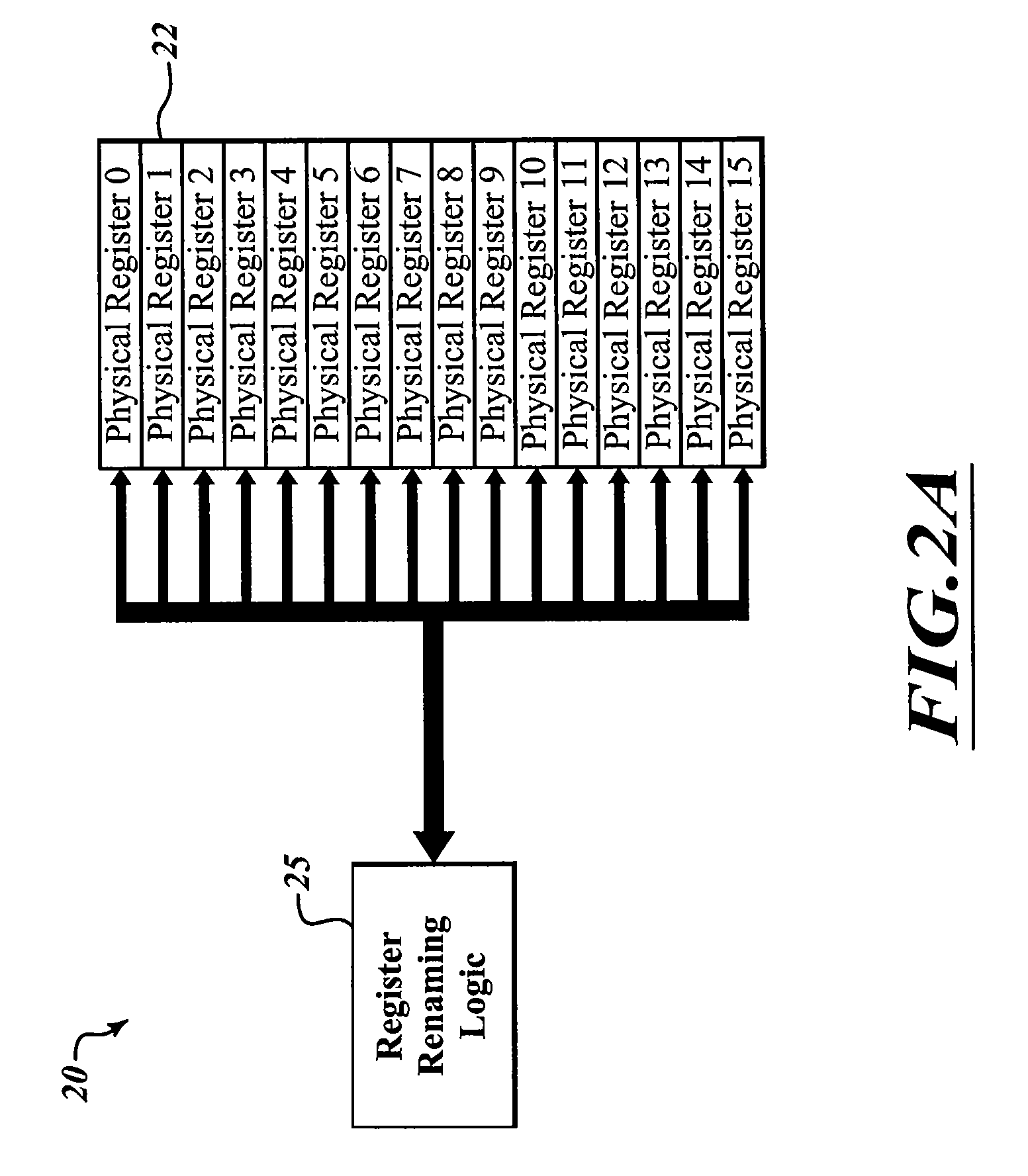

Embodiments of a processor architecture efficiently implement shadow registers in hardware. A register system in a processor includes a set of physical data registers coupled to register renaming logic. The register renaming logic stores data in and retrieves data from the set of physical registers when the processor is in a first processor state. The register renaming logic identifies ones of the set of physical registers that have a first operational state as a first group of registers and identifies the remaining ones of the set of physical registers as a second group of registers in response to an indication that the processor is to enter a second processor state from the first processor state. The register renaming logic stores data in and retrieves data from the second group of registers but not the first group of registers when the processor is in the second processor state.

Owner:STMICROELECTRONICS BEIJING R& D

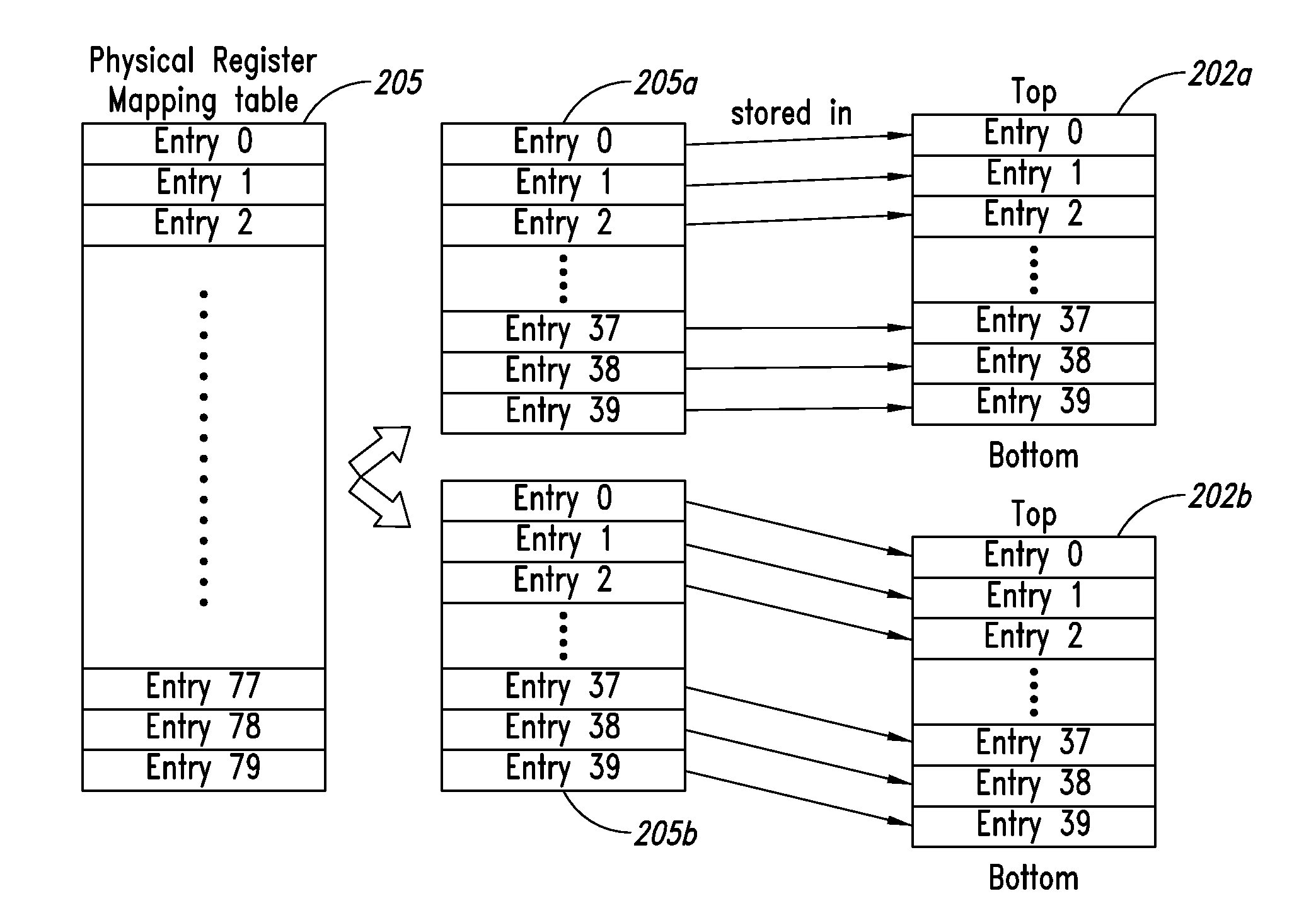

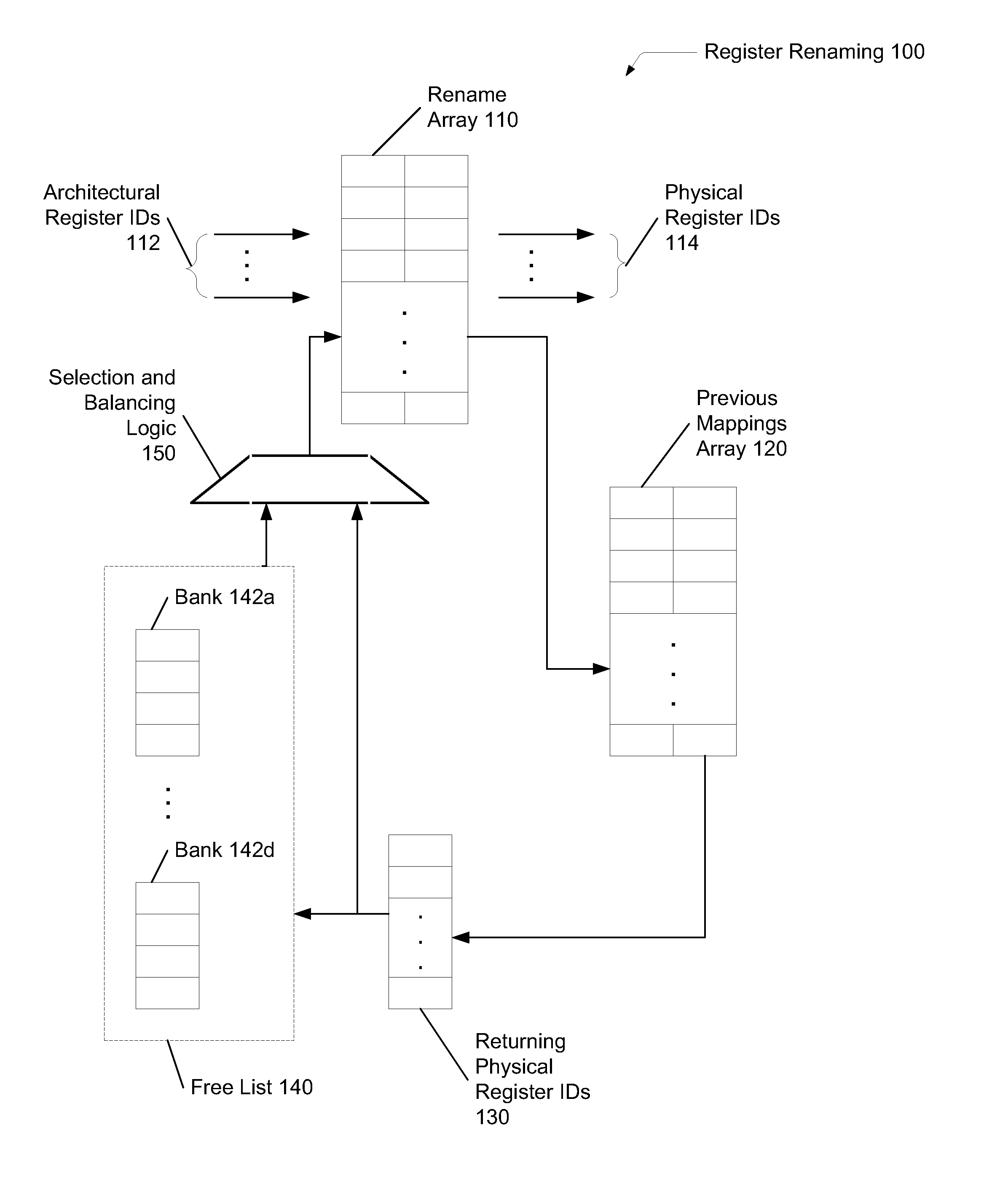

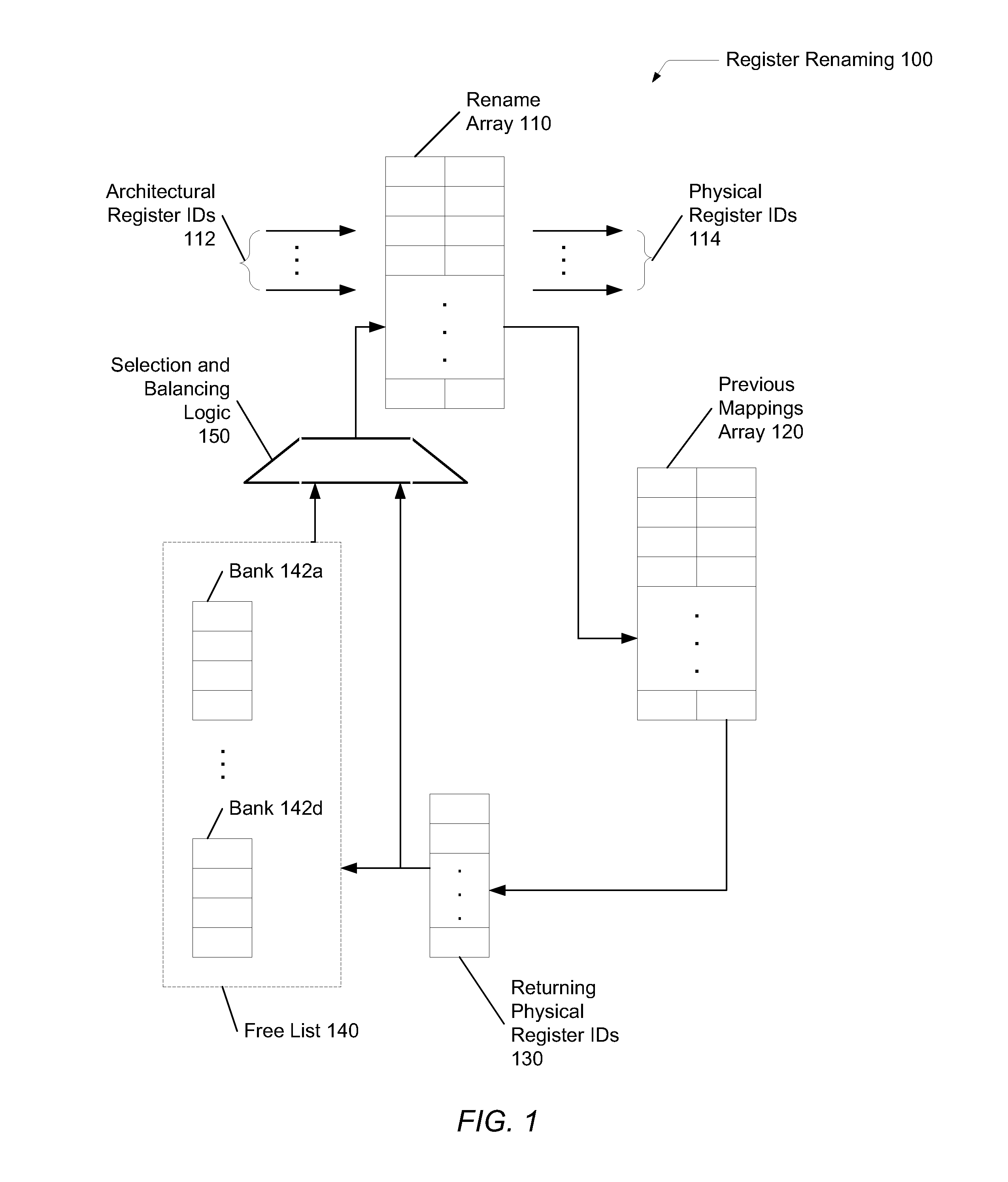

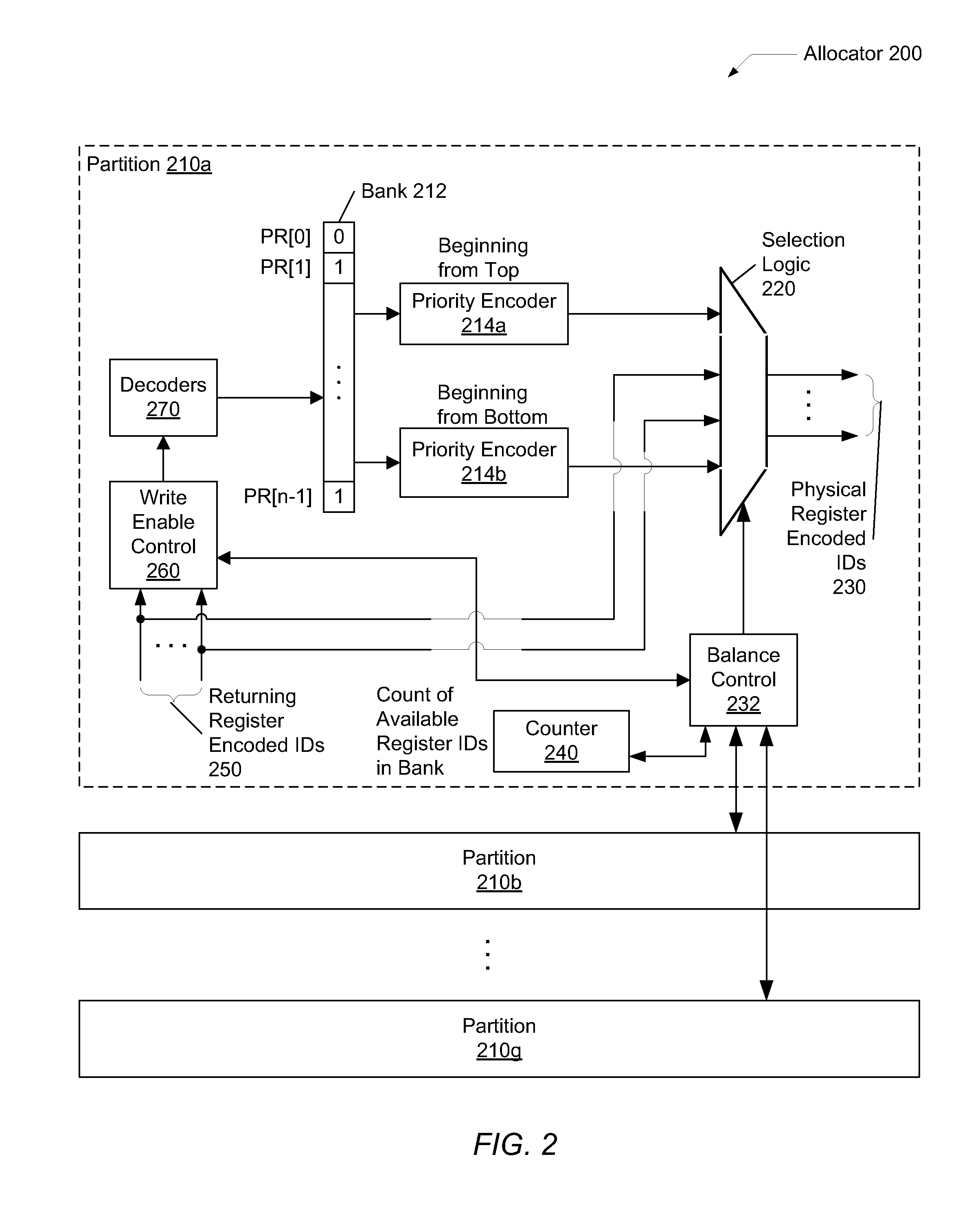

Novel register renaming system using multi-bank physical register mapping table and method thereof

ActiveUS20100205409A1Register arrangementsDigital computer detailsParallel computingRegister renaming

Embodiments of a processor architecture utilizing multi-bank implementation of physical register mapping table are provided. A register renaming system to correlate architectural registers to physical registers includes a physical register mapping table and a renaming logic. The physical register mapping table has a plurality of entries each indicative of a state of a respective physical register. The mapping table has a plurality of non-overlapping sections each of which having respective entries of the mapping table. The renaming logic is coupled to search a number of the sections of the mapping table in parallel to identify entries that indicate the respective physical registers have a first state. The renaming logic selectively correlates each of a plurality of architectural registers to a respective physical register identified as being in the first state. Methods of utilizing the multi-bank implementation of physical register mapping table are also provided.

Owner:MICROELECTRONIC INNOVATIONS LLC

Low power and high performance physical register free list implementation for microprocessors

ActiveUS20140013085A1Reduce latencyReduce total powerRegister arrangementsDigital computer detailsParallel computingLow power dissipation

A system and method for reducing latency and power of register renaming. A free list in processor includes multiple banks for indicating availability of register identifiers used for register renaming. A register rename unit receives one or more destination architectural registers to rename with physical register identifiers. Responsive to determining the multiple banks within the free list are unbalanced with available physical register identifiers, one or more returning physical register identifiers are assigned to the destination architectural registers before assigning any physical register identifiers from any bank of the multiple banks with a lowest number of available physical register identifiers. A returning physical register identifier is a physical register identifier that is available again for assignment to a destination architectural register but not yet indicated in the free list as available. Each of the banks includes a single bit width decoded vector for indicating availability of given physical register identifiers.

Owner:APPLE INC

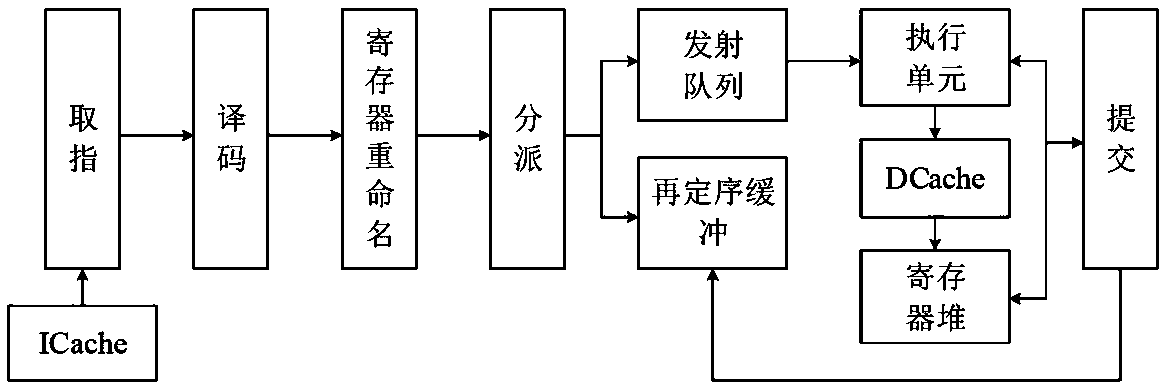

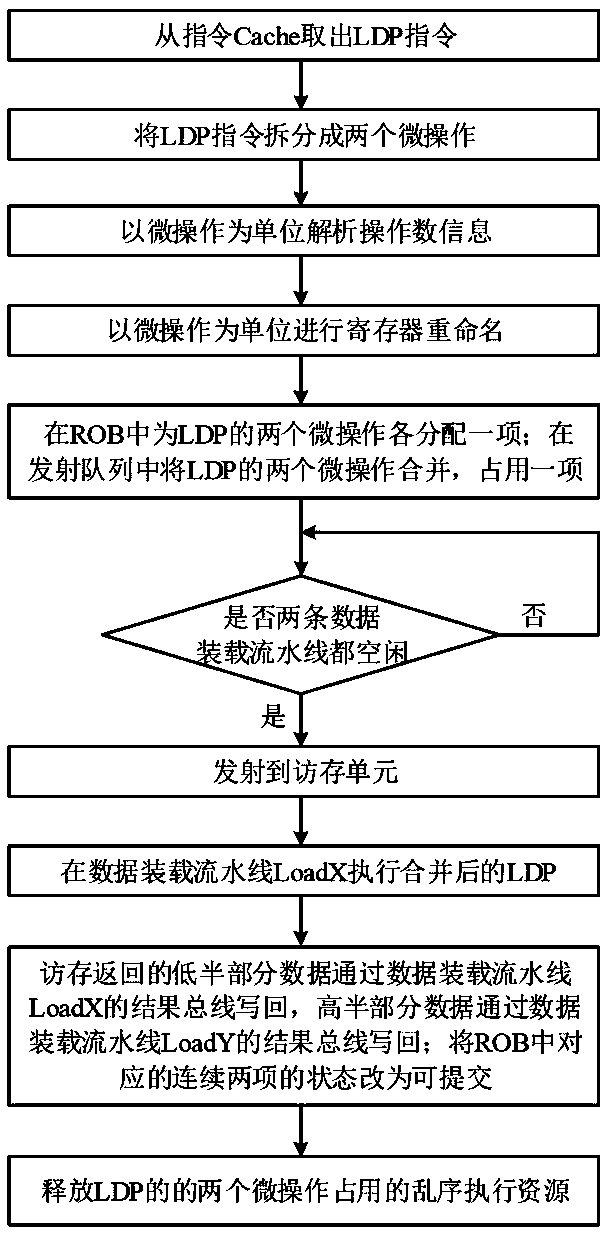

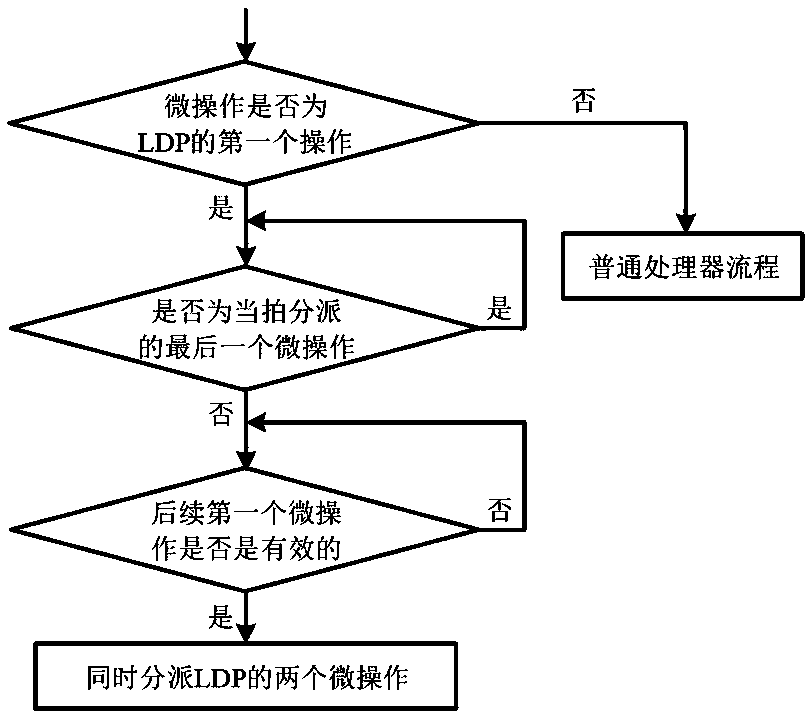

Execution method for logarithmic loading instruction

ActiveCN108845830AReduce the number of memory accessesReduce the numberMachine execution arrangementsMicro-operationAccess time

The invention discloses an execution method for a logarithmic loading instruction. The method comprises the steps of extracting an LDP instruction, splitting the LDP instruction into two micro-operations with destination registers, performing decoding, register renaming and assignment by taking the micro-operations as units, assigning items for the two micro-operations in a reorder buffer during assignment, and combining the two micro-operations in a transmission queue; if two data loading pipelines are available, transmitting an LDP after combination to an memory access unit, and performing execution in the first data loading pipeline; after the execution, writing back a low half part of obtained data to the first destination register through a result bus of the first data loading pipeline, and writing back a high half part to the second destination register through a result bus of the second data loading pipeline; and finally submitting the two micro-operations to release resources.On the premise that data access times are not increased, the number of destination register channels can be reduced, the design complexity can be lowered, and the area expenditure can be reduced.

Owner:NAT UNIV OF DEFENSE TECH